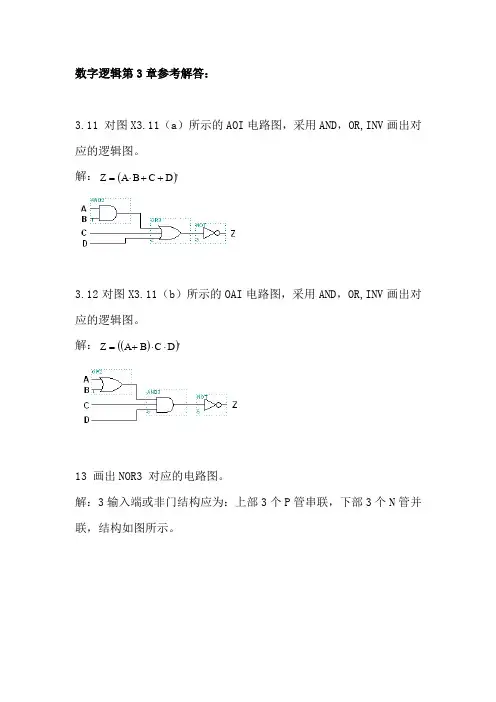

数字逻辑设计及应用 专科3 答案

- 格式:pdf

- 大小:224.43 KB

- 文档页数:3

------------------------------------------------------------------------------------------------------------------------------ (单选题) 1: 状态si和sj等介的条件是A: 只要到达的次态相同B: 只要在相同输入时有相同的输出C: 只要si的次态是sj,sj的次态是siD: 同时具备A和B正确答案:(单选题) 2: 两个与非门交叉耦合构成的SR锁存器(基本RS触发器),当加入后,触发器的状态将是A: Q=0,Q'=1B: Q=Q'=1C: Q=1,Q'=0D: Q=Q'=0正确答案:(单选题) 3: 欲比较两个多位二进制数的大、小抑或相等,应选用A: 编码器B: 译码器C: 加法器D: 数值比较器正确答案:(单选题) 4: 逻辑式A'+B(C'+DE)的对偶式是A: A'B+C'D+EB: A'[B+C'(D+E)]C: AB'+CD'+E'D: A[B'+C(D'+E')]正确答案:(单选题) 5: 下列数中最大的是A: (101101)2B: (55)8C: (45)10D: (2E)16正确答案:(单选题) 6: 参考书第254页图P5.18中,在Q9~Q12中,是翻转触发器的是A: Q9B: Q10C: Q11D: Q12正确答案:(单选题) 7: 一块八选一的数据选择器,其选择(地址)输入有A: 1位B: 3位C: 5位D: 8位正确答案:------------------------------------------------------------------------------------------------------------------------------ (单选题) 8: 某符号二进制数的原码是10110101,则其补码是A: 11001011B: 11001010C: 110101D: 1001010正确答案:(单选题) 9: n级触发器构成的扭环形计数器,其有效循环内的状态数有A: n个B: 2n个C: 2n-1个D: 2n个正确答案:(单选题) 10: 逻辑式A'+AB=A: A'+BB: A'+AC: A'D: AB正确答案:(单选题) 11: 逻辑式A'(B+C'D)的反演式是A: A(B'+CD')B: A+B'(C+D')C: A+B'C+D'D: A'+B(C'+D)正确答案:(单选题) 12: 一片存储容量为1024×8位的ROM,其地址码有A: 8位B: 1024位C: 10位D: 82位正确答案:(单选题) 13: TTL电路使用的电源电压Vcc=A: 0.2VB: 1.4VC: 3.4VD: 5V正确答案:(单选题) 14: 十六进制数(FF)16对应的十进制数是A: 1515B: 255C: 256D: 225正确答案:(单选题) 15: 逻辑式A'(B+C'D)的反演式是------------------------------------------------------------------------------------------------------------------------------ A: A(B'+CD')B: A+B'(C+D')C: A+B'C+D'D: A'+B(C'+D)正确答案:(单选题) 16: 一个T触发器,在T=1时,来一个时钟脉冲后,则触发器()。

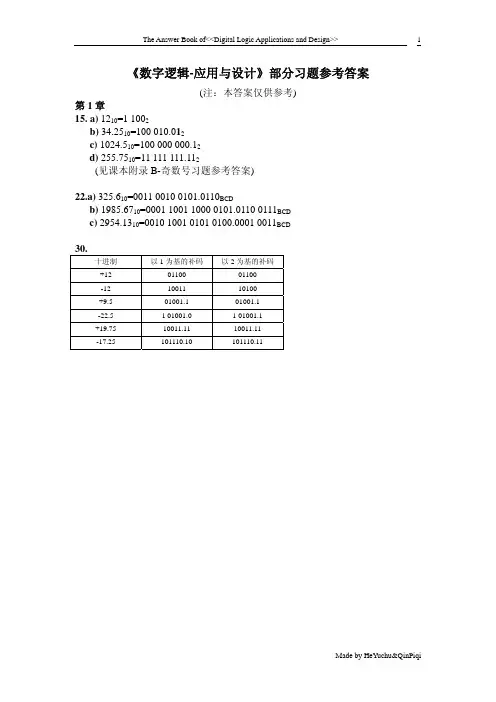

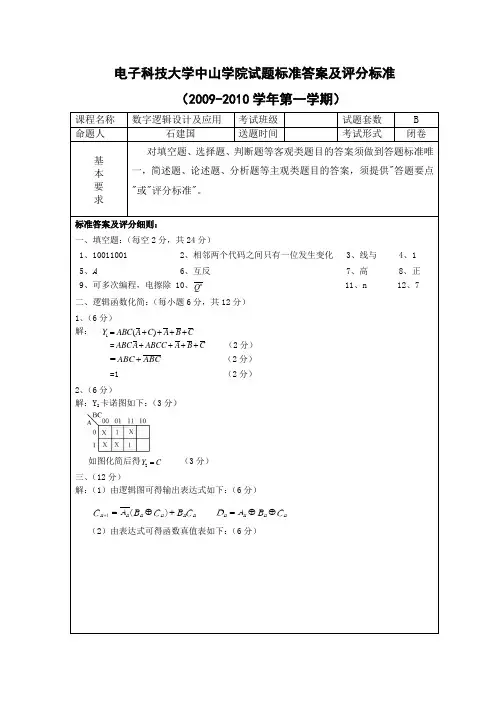

2012-2013-2《数字逻辑设计及应用》期末考试题-A参考解答------------------------------------------作者------------------------------------------日期电子科技大学2012 -2013学年第二学期期末考试 A 卷课程名称:♉数字逻辑设计及应用♉♉ 考试形式: 闭卷 考试日期: 年 月 日考试时长:♉♉♉♉分钟课程成绩构成:平时 , 期中 , 实验 , 期末 本试卷试题由♉♉♉七♉♉部分构成,共♉♉♉♉♉页。

✋ ☞♓●● ☐◆♦ ⍓☐◆❒ ♋⏹♦♦♏❒♦ ♓⏹ ♦♒♏ ♌●♋⏹♦ ☎❼ ✠ ❼✆ ✋♐ ♋ ⌧ ♌♓⏹♋❒⍓ ♎♏♍☐♎♏❒ ♒♋♦ ☐⏹ ♓♦♦ ♓⏹☐◆♦♦ ✌ ♦♒♏ ♋♍♦♓❖♏ ☹ ☐◆♦☐◆♦ ✡ ♦♒☐◆●♎ ♌♏ ☎ ☐❒ ♒♓♑♒ ✆ ✋♐ ♦♒♏ ⏹♏⌧♦ ♦♦♋♦♏ ☐♐ ♦♒♏ ◆⏹◆♦♏♎ ♦♦♋♦♏♦ ♋❒♏ ❍♋❒♏♎ ♋♦ ❽♎☐⏹❼♦♍♋❒♏♦❾ ♦♒♏⏹ ♎♏♦♓♑⏹♓⏹♑ ♋ ♐♓⏹♓♦♏ ♦♦♋♦♏ ❍♋♍♒♓⏹♏ ♦♒♓♦ ♋☐☐❒☐♋♍♒ ♓♦ ♍♋●●♏♎ ❍♓⏹♓❍♋● ☎ ♍☐♦♦ ✆ ♋☐☐❒☐♋♍♒❆♒♏ ♉☹ ☐♐ ♌♓♦ ♍☐◆⏹♦♏❒ ⌧ ♓♦ ☎ ☐❒ ●☐♦ ✆ ♦♒♏⏹ ♍☐◆⏹♦♓⏹♑ ♦☐ ♓⏹ ♎♏♍❒♏♋♦♓⏹♑ ☐❒♎♏❒ ❆☐ ♎♏♦♓♑⏹ ♋ ✂✂ ♦♏❒♓♋● ♦♏❑◆♏⏹♍♏ ♑♏⏹♏❒♋♦☐❒ ♌⍓ ♦♒♓♐♦ ❒♏♑♓♦♦♏❒♦ ♦♒♏ ♦♒♓♐♦ ❒♏♑♓♦♦♏❒ ♦♒☐◆●♎ ⏹♏♏♎☎ ✆ ♌♓♦ ♋♦ ●♏♋♦♦ ⏹♏ ♦♦♋♦♏ ♦❒♋⏹♦♓♦♓☐⏹ ♏❑◆♋♦♓☐⏹ ♓♦ ✈✉☺✈❼❼✈ ✋♐ ♦♏ ◆♦♏ ❆ ♐●♓☐♐●☐☐ ♦♓♦♒ ♏⏹♋♌●♏ ♦☐ ♍☐❍☐●♏♦♏ ♦♒♏ ♏❑◆♋♦♓☐⏹,♦♒♏ ♏⏹♋♌●♏ ♓⏹☐◆♦ ☐♐ ❆ ♐●♓☐♐●☐☐ ♦♒☐◆●♎ ♒♋❖♏ ♦♒♏ ♐◆⏹♍♦♓☐⏹ ☜☠☎ ☺✈❼✈ ✆ ✌ ♌♓♦ ♓⏹♋❒⍓ ♍☐◆⏹♦♏❒ ♍♋⏹ ♒♋❖♏ ☎ ✆ ⏹☐❒❍♋● ♦♦♋♦♏♦ ♋♦ ❍☐♦♦ ♌♓♦ ☺☐♒⏹♦☐⏹ ♍☐◆⏹♦♏❒ ♦♓♦♒ ⏹☐ ♦♏●♐♍☐❒❒♏♍♦♓☐⏹ ♍♋⏹ ♒♋❖♏ ☎ ✆ ⏹☐❒❍♋● ♦♦♋♦♏♦ ♌♓♦ ●♓⏹♏♋❒ ♐♏♏♎♌♋♍ ♦♒♓♐♦❒♏♑♓♦♦♏❒ ☎☹☞✆ ♍☐◆⏹♦♏❒ ♦♓♦♒ ♦♏●♐♍☐❒❒♏♍♦♓☐⏹ ♍♋⏹ ♒♋❖♏ ☎ ✆ ⏹☐❒❍♋● ♦♦♋♦♏♦ ✋♐ ♦♏ ◆♦♏ ♋ ♦♒☐♦♏ ♍♋☐♋♍♓♦⍓ ♓♦ ♌♓♦♦ ♦☐ ♍☐⏹♦♦❒◆♍♦ ♋ ♌♓♦ ♌♓⏹♋❒⍓ ♍☐♎♏ ♦☐ ♑❒♋⍓ ♍☐♎♏ ♍☐⏹❖♏❒♦♏❒ ♦♒♏⏹ ♦♒♏ ♋♎♎❒♏♦♦ ♓⏹☐◆♦♦ ♋❒♏ ☎ ✆ ♦♓●● ♌♏ ♦♒♏ ☐◆♦☐◆♦ ♒♏⏹ ♦♒♏ ♓⏹☐◆♦ ♓♦ ☐♐ ♋⏹ ♌♓♦ ✌ ♦♒♏ ♍☐❒❒♏♦☐☐⏹♎♓⏹♑ ☐◆♦☐◆♦ ❖☐●♦♋♑♏ ♓♦ ✞ ❆♒♏ ☐◆♦☐◆♦ ❖☐●♦♋♑♏ ♓♦ ☎ ✆ ✞ ♦♒♏⏹ ♦♒♏ ♓⏹☐◆♦ ♓♦ ✋✋ ●♏♋♦♏ ♦♏●♏♍♦ ♦♒♏ ☐⏹●⍓ ☐⏹♏ ♍☐❒❒♏♍♦ ♋⏹♦♦♏❒ ♓⏹ ♦♒♏ ♐☐●●☐♦♓⏹♑ ❑◆♏♦♦♓☐⏹♦☎❼ ✠ ❼✆ ✋♐♋ ⌧ ❍♋♑⏹♓♦◆♎♏ ♍☐❍☐♋❒♋♦☐❒ ♒♋♦ ✌☹❆✋☠ ✌☝❆✋☠ ✌☜✈✋☠ ✌✌✌✌ ☐⏹ ♓♦♦ ♓⏹☐◆♦♦ ♦♒♏ ☐◆♦☐◆♦♦ ♋❒♏ ☎ ✆✌✆ ✌☹❆✞❆ ✌☜✈✞❆ ✌☝❆✞❆ ✆ ✌☹❆✞❆ ✌☜✈✞❆ ✌☝❆✞❆✆ ✌☹❆✞❆ ✌☜✈✞❆ ✌☝❆✞❆✆ ✌☹❆✞❆ ✌☜✈✞❆ ✌☝❆✞❆ ✌♦ ♦♒☐♦⏹ ♓⏹ ☞♓♑◆❒♏ ♦♒♋♦ ♦☐◆●♎ ♦♒♏ ☐◆♦☐◆♦♦ ☐♐ ♦♒♏ ♌♓♦ ♋♎♎♏❒ ⌧ ♌♏ ☎ ✆ ♦♒♏⏹ ✌✌ ✌✌ ♋⏹♎ ✌✌✆ ✆ ✆ ✆ ☞♓♑◆❒♏ ♒♓♍♒ ☐♐ ♦♒♏ ♐☐●●☐♦♓⏹♑ ♦♦♋♦♏❍♏⏹♦♦ ♓♦ ✋☠☜❆✍ ☎ ✌ ✆✌✆ ✌ ●♋♦♍♒ ♓♦ ♏♎♑♏ ♦❒♓♑♑♏❒♏♎ ♋⏹♎ ♓♦ ♦♓●● ♐☐●●☐♦ ♦♒♏ ♓⏹☐◆♦ ♋♦ ●☐⏹♑ ♋♦ ♦♒♏ ♍☐⏹♦❒☐● ♓⏹☐◆♦ ♓♦ ♋♍♦♓❖♏ ●☐♦✆ ✌ ♐●♓☐ ♐●☐☐ ♓♦ ♏♎♑♏ ♦❒♓♑♑♏❒♏♎ ♋⏹♎ ♓♦♦ ☐◆♦☐◆♦ ♦♓●● ⏹☐♦ ♍♒♋⏹♑♏ ◆⏹♦♓● ♦♒♏ ♏♎♑♏ ☐♐ ♦♒♏ ♍☐⏹♦❒☐●●♓⏹♑ ☹ ♦♓♑⏹♋●✆ ✌⏹ ●♋♦♍♒ ❍♋⍓ ♑☐ ♓⏹♦☐ ❍♏♦♋♦♦♋♌●♏ ♦♦♋♦♏ ♓♐ ♌☐♦♒ ♋⏹♎ ♋❒♏ ♍♒♋⏹♑♓⏹♑ ♐❒☐❍ ♦☐ ♦♓❍◆●♦♋⏹♏☐◆♦●⍓✆ ❆♒♏ ☐◆●♦♏ ♋☐☐●⍓♓⏹♑ ♦☐ ♋⏹⍓ ♓⏹☐◆♦ ☐♐ ♋⏹ ●♋♦♍♒ ❍◆♦♦ ❍♏♏♦ ♦♒♏ ❍♓⏹♓❍◆❍ ☐◆●♦♏ ♦♓♎♦♒ ❒♏❑◆♓❒♏❍♏⏹♦ ❆♒♏ ♍♋☐♋♍♓♦⍓ ☐♐ ♋ ❍♏❍☐❒⍓ ♦♒♋♦ ♒♋♦ ♌♓♦♦ ♋♎♎❒♏♦♦ ♌◆♦ ♋⏹♎ ♍♋⏹ ♦♦☐❒♏ ♌♓♦♦ ♋♦ ♏♋♍♒ ♋♎♎❒♏♦♦ ♓♦ ☎ ✆✌✆ ✆ ✆ ✆ ♒♓♍♒ ♦♦♋♦♏ ♓⏹ ☞♓♑◆❒♏ ♓♦ ☠❆ ♋❍♌♓♑◆☐◆♦ ☎ ✆✌✆ ✌ ✆ ✆ ♋⏹♎ ✆ A BCDWXW+YZZ’X’+YYZ1X’Z’☞♓♑◆❒♏ ✋✋✋ ✌⏹♋●⍓♏ ♦♒♏ ♦♏❑◆♏⏹♦♓♋●♍♓❒♍◆♓♦ ♋♦ ♦♒☐♦⏹ ♓⏹ ☞♓♑◆❒♏ ☞●♓☐☞●☐☐ ♦♓♦♒ ♋♦⍓⏹♍♒❒☐⏹☐◆♦ ☐❒♏♦♏♦ ♋⏹♎ ♍●♏♋❒ ♓⏹☐◆♦♦ ☯❼❒♓♦♏ ☐◆♦ ♦♒♏ ♏⌧♍♓♦♋♦♓☐⏹ ♏❑◆♋♦♓☐⏹♦ ♦❒♋⏹♦♓♦♓☐⏹ ♏❑◆♋♦♓☐⏹♦ ♋⏹♎ ☐◆♦☐◆♦ ♏❑◆♋♦♓☐⏹ ☯❼✌♦♦◆❍♏ ♦♒♏ ♓⏹♓♦♓♋● ♦♦♋♦♏ ✈ ✈ ♍☐❍☐●♏♦♏ ♦♒♏ ♦♓❍♓⏹♑ ♎♓♋♑❒♋❍ ♐☐❒ ✈ ✈ ♋⏹♎ ☪ ☯❼☞♓♑◆❒♏ 参考答案:激励方程 ✈ , ✈转移方程:✈ ✉ ✈ ,✈ ✉ ✈输出方程:☪ ☎☹✈ ✆参考评分标准: 个方程正确得 分;每错一个扣 分,扣完 分为止;得分沿和下降沿各 分,错 处扣 分,扣完 分为止。

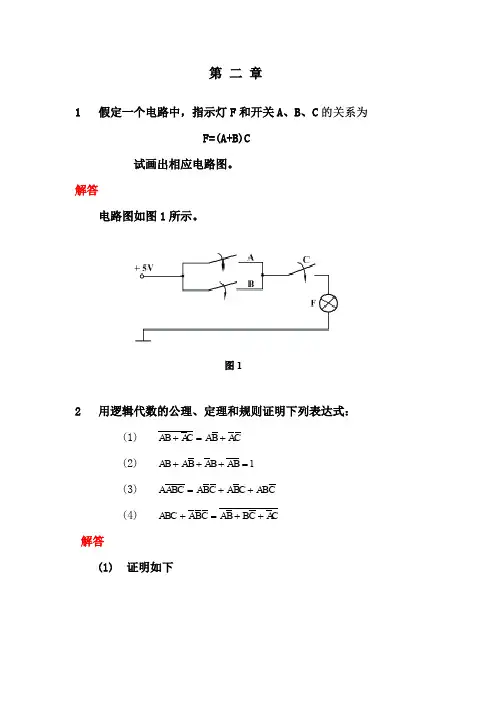

3-1 分析题图3-1所示电路,写出电路输出Y 1和Y 2的逻辑函数表达式,列出真值表,说明它的逻辑功能。

解:由题图3-1从输入信号出发,写出输出Y 1和Y 2的逻辑函数表达式为1Y A B C =⊕⊕ ; 2()()Y A B C AB A B C A =⊕⋅⋅=⊕⋅+B将上式中的A 、 B 、C 取值000~111,分别求出Y 1和Y 2,可得出真值表如题解 表3-1所示。

题解 表3-1ABCA B ⊕()A B C ⊕⋅AB1Y2Y0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 1 1 0 0 1 1 0 0 1 0 0 1 0 1 0 1 1 1 0 0 1 1 1 0 0 0 1 0 1 111111综上,由题解 表3-1可以看出,该电路实现了一位全加器的功能。

其中,A 和B 分别是被加数及加数,C 为相邻低位来的进位数;Y1为本位和数,Y 2为相邻高位的进位数。

3-2 分析题图3-2所示电路,要求:写出输出逻辑函数表达式,列出真值表,画出卡诺图,并总结电路功能。

解:由题图3-2从输入信号出发,写出输出F 的逻辑函数表达式为()()F A B C D =:::将上式中的A 、 B 、C 、D 取值0000~1111,求出F ,可得真值表和卡诺图分别如题解 表3-2和题解 图3-1所示。

题解 表3-2A B C DA B : C D :F0 0 0 0 1 1 1 0 0 0 1 1 0 0 0 0 1 0 1 0 0 0 0 1 1 1 1 1 0 1 0 0 0 1 0 0 1 0 1 0 0 1 0 1 1 0 0 0 1 0 1 1 1 0 1 0 1 0 0 0 0 1 0 1 0 0 1 0 0 11 0 1 0 0 0 1 1 0 1 1 0 1 0 1 1 0 0 1 1 1 1 1 0 1 1 0 0 1 1 1 0 1 0 0 1 1 1 1 1 1 1综上,由题解 表3-2可以看出,当输入A 、 B 、C 、D 中含有偶数个“1”时,输出;否则,当输入A 、 B 、C 、D 中含有奇数个“1”时,输出。

图1-8 图2-5J=K=1 ;的产生,则该移位寄存器中触发器的个数为:2 / 33、如果逻辑AB+AC=1,则A=1;( √ )4、如果逻辑AB+AC=0,则A=0;(Х )5、若干个逻辑信号进行异或操作,如果这些信号中逻辑“1”的个数为奇数,则输出结果为1;(√) 6、A ⊕1=A /;( √ ) 7、A+A+A=A ·A ·A ;( √ )8、对于CMOS 集成门电路而言,与门的结构比与非门的结构更为简单一些;(Х ) 9、TTL 逻辑比CMOS 逻辑的运行功耗更低,所以更利于集成;(Х ) 10、影响CMOS 集成门电路的运行速度主要是传输延迟和转换时间;( √ )四、卡诺图化简(8分)将逻辑F (A,B,C,D )=∑m(0,1,3,4,6,7,14,15)+d(8,9,10,11,12,13)化成最简或与函数式;F=C /D /+B /D+BC答案不唯一五、组合逻辑分析,要求如下(8分)完成图5所示电路的逻辑分析,并写出: 1、 逻辑Y 的函数式 2、 写出该逻辑的真值表 1、 函数式2、 真值表六、时序逻辑分析,要求如下:(14分)请分析图6所示电路的逻辑,并写出: 1、 驱动方程和输出方程; 2、 状态方程;3、 画出状态转换图或者状态转换表;驱动方程:21'⋅=Q X EN ,12Q J =,12=K状态方程:121121111*1Q Q Q X Q Q X Q EN Q EN Q ⋅+⋅'+'⋅'⋅=⋅'+'⋅=122222*2Q Q Q K Q J Q ⋅'=⋅'+'⋅=输出方程:21'⋅+⋅'=Q X Q X Z 状态表:或者状态图:图5图6CB AC B A CB AC B A F //////∙∙+∙∙+∙∙+∙∙=3 / 3七、组合逻辑设计,要求如下:(8分)请利用一块8选1的数据选择器芯片74153来实现如下逻辑:BC AC AB Y ++=;可加一定的门电路来实现。

数字逻辑课程作业_A一、单选题。

1.(4分)如图x1-229(D)。

A. (A)B. (B)C. (C)D. (D)知识点:第五章解析第五章译码器2.(4分)如图x1-82(C)。

A. (A)B. (B)C. (C)D. (D)知识点:第二章解析第二章其他复合逻辑运算及描述3.(4分)N个触发器可以构成最大计数长度(进制数)为(D)的计数器。

A. NB. 2NC. N2次方D. 2N次方知识点:第九章解析第九章计数器4.(4分)n个触发器构成的扭环型计数器中,无效状态有(D)个。

A. A.nB. B.2nC. C.2n-1D. D.2n-2n知识点:第九章解析第九章集成计数器5.(4分)如图x1-293(A)。

A. (A)B. (B)C. (C)D. (D)知识点:第十一章解析第十一章数字系统概述6.(4分)如图x1-317(D)。

A. (A)B. (B)C. (C)D. (D)知识点:第二章解析第二章其他复合逻辑运算及描述7.(4分)EPROM是指(C)。

A. A、随机读写存储器B. B、只读存储器C. C、光可擦除电可编程只读存储器D. D、电可擦可编程只读存储器知识点:第十章解析第十章只读存储器8.(4分)如图x1-407(B)。

A. (A)B. (B)C. (C)D. (D)知识点:第十一章解析第十一章数字系统概述9.(4分)为实现将JK触发器转换为D触发器,应使(A)。

A. J=D,K=D非B. B. K=D,J=D非C. C.J=K=DD. D.J=K=D非知识点:第六章解析第六章各种触发器的比较10.(4分)一位8421BCD码计数器至少需要(B)个触发器。

A. 3B. B.4C. C.5D. D.10知识点:第九章解析第九章计数器11.(4分)为把50Hz的正弦波变成周期性矩形波,应当选用(A)。

A. A、施密特触发器B. B、单稳态电路C. C、多谐振荡器D. D、译码器知识点:第六章解析第六章集成触发器12.(4分)下列描述不正确的是(A)。

《数字逻辑》作业参考答案一、单项选择题1.C 2.B 3.D 4.C 5.A 6.D 7.A 8.A二、请根据真值表写出其最小项表达式1.2.三、用与非门实现1.四、用或非门实现1.五、逻辑电路如图所示,请分析出该电路的最简与或表达式,并画出其真值表。

1真值表略 LCABC AB Y ++=2.六、用与非门设计一个举重裁判表决电路。

设举重比赛有3个裁判,一个主裁判和两个副裁判。

杠铃完全举上的裁决由每一个裁判按一下自己面前的按钮来确定。

只有当两个或两个以上裁判判明成功,并且其中有一个为主裁判时,表明成功的灯才亮。

七、设计一个楼上、楼下开关的控制逻辑电路来控制楼梯上的路灯,使之在上楼前,用楼下开关打开电灯,上楼后,用楼上开关关灭电灯;或者在下楼前,用楼上开关打开电灯,下楼后,用楼下开关关灭电灯。

八、①试分析下图中用何种触发器,并写出该触发器的特性方程。

②分析该时序逻辑电路的功能。

1.有效循环的6个状态分别是0~5这6个十进制数字的格雷码,并且在时钟脉冲CP 的作用下,这6个状态是按递增规律变化的,即:000→001→011→111→110→100→000→…所以这是一个用格雷码表示的六进制同步加法计数器。

当对第6个脉冲计数时,计数器又重新从000开始计数,并产生输出Y =1。

2.当输入X =0时,在时钟脉冲CP 的作用下,电路的4个状态按递增规律循环变化,即:00→01→10→11→00→…当X =1时,在时钟脉冲CP 的作用下,电路的4个状态按递减规律循环变化,即:00→11→10→01→00→…可见,该电路既具有递增计数功能,又具有递减计数功能,是一个2位二进制同步可逆计数器。

3. 在时钟脉冲CP 的作用下,电路的8个状态按递减规律循环变化,即:000→111→110→101→100→011→010→001→000→…电路具有递减计数功能,是一个3位二进制异步减法计数器4.有效循环的6个状态分别是0~5这6个十进制数字的格雷码,并且在时钟脉冲CP的作用下,这6个状态是按递增规律变化的,即:000→001→011→111→110→100→000→…所以这是一个用格雷码表示的六进制同步加法计数器。

数字设计基础与应用第3章答案1. 什么是数字设计?数字设计是指在计算机系统中使用数字电子技术进行的设计。

它涉及到数字电路和系统的设计、实现和分析,以及数字信号处理和通信系统的设计和优化。

数字设计是现代计算机科学和电子工程领域的核心内容,广泛应用于计算机硬件、嵌入式系统、通信网络等领域。

2. 数字设计的基础知识数字设计的基础知识包括布尔代数、逻辑门电路及其应用、数字逻辑电路的组成和实现方法等。

布尔代数布尔代数是一种数学理论,它描述了逻辑关系和运算。

在数字设计中,布尔代数用于描述和分析逻辑电路的运算规则和性质。

布尔代数有四个基本运算:与运算(AND)、或运算(OR)、非运算(NOT)、异或运算(XOR)。

逻辑门电路逻辑门电路是由逻辑门组成的电路,逻辑门包括与门(AND)、或门(OR)、非门(NOT)等。

逻辑门电路通过将不同的逻辑门按照不同的连接方式组合起来,可以实现各种逻辑运算和数据处理功能。

数字逻辑电路的组成和实现方法数字逻辑电路由逻辑门电路组成,它可以实现各种逻辑运算和数据处理功能。

数字逻辑电路有三种基本的组成方式:组合逻辑电路、时序逻辑电路和存储器。

3. 数字设计的应用数字设计的应用非常广泛,包括计算机硬件设计、通信网络设计、嵌入式系统设计等。

以下是一些数字设计的应用领域:计算机硬件设计数字设计在计算机硬件设计中起着关键作用。

计算机的中央处理器(CPU)、存储器、输入输出接口等都是通过数字电路实现的。

数字设计可以帮助设计人员实现高性能、低功耗的计算机硬件。

通信网络设计数字设计在通信网络设计中也非常重要。

数字信号处理和数字通信技术是现代通信网络的核心。

数字设计可以帮助设计人员实现高速、高可靠性的通信网络。

嵌入式系统设计嵌入式系统是指内嵌在其他设备中的计算机系统。

数字设计在嵌入式系统设计中扮演着重要的角色。

数字设计可以帮助设计人员实现低功耗、高性能的嵌入式系统,例如智能手机、汽车电子系统等。

4. 数字设计的发展趋势随着科技的发展,数字设计也在不断演进和发展。

专科《数字电路与逻辑设计》考试答案————————————————————————————————作者:————————————————————————————————日期:专科《数字电路与逻辑设计》一、(共75题,共150分)1. 多少个二进制数字可以组成一位十六进制数字?()(2分)A.2B.3C.4D.5.标准答案:C2. 二进制数(1111101.0101)2转换为八进制为:()(2分)A.037.25B.175.24C.125.3l25D.761.2.标准答案:B3. 十进制数9的8421码为()。

(2分)A.1000B.1011C.1001D.1010.标准答案:C4. 二进制数?0.1011的原码是()。

(2分)A.1.1011B.0.1011C.1.0100D.1.0101.标准答案:A5.逻辑函数=()。

(2分)A.A+ B+ CB.C.1D.0.标准答案:C6. 逻辑函数的F(A,B,C)=的标准与或式为()。

(2分)A.B.C.D..标准答案:D7. 与逻辑函数F=相等的函数为()。

(2分)A.ABB.C.D.AB+C.标准答案:D8. 逻辑函数的反函数为()(2分)A.B.C.D..标准答案:B9. 在下列三个逻辑函数表达式中,哪一个是最小项表达式?()(2分)A.B.C.D..标准答案:A10. 逻辑函数式F=等于()。

(2分)A.0B.1C.AD..标准答案:B11. 下列几种TTL电路中,输出端可实现线与功能的电路是()。

(2分)A.或非门B.与非门C.异或门D.OC门.标准答案:D12. 典型的TTL与非门电路使用的电源电压为()。

(2分)A.5 VB.3.6 VC.0.35 VD.3—18 V.标准答案:A13. 基本RS触发器在正常工作时,它的约束条件是,则它不允许输入S和R 的取值分别为()。

(2分)A.0,0B.0,1C.1,0D.1,1.标准答案:D14. 若JK触发器的J=0,K=0,在CLK触发后,输出Q的状态为( )。

电子科技大学《数字逻辑设计及应用》20春期末考试红字部分为答案!单选题1.EPROM是指()A.随机读写存储器B.只读存储器C.可擦可编程只读存储器D.电可擦可编程只读存储器2.下面各个组成部分,对于一个时序逻辑来说,不可缺少的是()A.mealy型输出B.输入C.moore型输出D.存储单元3.n级触发器构成的环形计数器,其有效循环的状态数为()A.n个B.2n个C.2n-1个D.2n个4.脉冲异步时序逻辑电路的输入信号可以是()A.模拟信号B.电平信号C.脉冲信号D.以上都不正确5.组合逻辑电路输出与输入的关系可用()描述A.真值表B.状态表C.状态图D.以上均不正确6.一块十六选一的数据选择器,其数据输入端有()个A.16B.8C.4D.27.数字系统中,采用()可以将减法运算转化为加法运算A.原码B.补码C.Gray码D.以上都不正确8.四变量A,B,C,D构成的最小项是()。

A.AB.ABD.ABCD9.移位寄存器T1194工作在并行数据输入方式时,MAMB取值为()A.00B.01C.10D.1110.三个变量A, B, C一共可以构成()个最小项A.8B.6C.4D.211.用ROM实现四位二进制码到四位循环码的转换,要求存储器的容量为()。

A.8B.16C.32D.6412.下列哪个不是基本的逻辑关系()。

A.与B.或C.非D.与非13.下列逻辑门中,()不属于通用逻辑门A.与非门B.或非门C.或门D.与或非门14.一块数据选择器有三个地址输入端,则它的数据输入端应有()。

A.3B.6C.8D.115.实现同一功能的Mealy型同步时序电路比Moore型同步时序电路所需要的()A.状态数目更多B.状态数目更少C.触发器更多D.触发器一定更少16.74LS160十进制计数器它含有的触发器的个数是()A.1个B.2个C.4个17.电平异步时序逻辑电路不允许两个或两个以上输入信号()A.同时为0B.同时为1C.同时改变D.同时出现18.八路数据选择器应有()个选择控制器A.2B.3C.6D.819.实现两个4位二进制数相乘的组合电路,其输入输出端个数应为()A.4入4出B.8入8出C.8入4出D.8入5出20.下列电路中,是组合电路的是()。