STM32F103VE-中文

- 格式:pdf

- 大小:615.94 KB

- 文档页数:30

stm32f103vet bootloader例程摘要:1.STM32F103vet Bootloader 简介2.Bootloader 例程的作用3.Bootloader 例程的结构和主要功能4.Bootloader 例程的编写方法5.Bootloader 例程的应用实例6.总结正文:【1.STM32F103vet Bootloader 简介】STM32F103vet Bootloader 是一款基于STM32F103 微控制器的嵌入式系统引导程序。

Bootloader,意为“引导程序”,在嵌入式系统中主要用于初始化硬件、加载操作系统等。

STM32F103vet Bootloader 例程则是实现Bootloader 功能的具体代码示例。

【2.Bootloader 例程的作用】Bootloader 例程的主要作用包括以下几个方面:1) 硬件初始化:对嵌入式系统的硬件进行初始化,如时钟、串口等。

2) 软件配置:配置Bootloader 运行时的软件环境,如内存分配、外设配置等。

3) 加载操作系统:将操作系统从存储器中读取到内存中并执行。

4) 诊断与测试:对嵌入式系统进行自检和诊断,确保系统正常运行。

【3.Bootloader 例程的结构和主要功能】STM32F103vet Bootloader 例程主要包括以下几个部分:1) 系统初始化:初始化硬件、时钟、串口等。

2) 系统配置:配置内存分配、外设、时钟等。

3) 操作系统加载:将操作系统从存储器中读取到内存中并执行。

4) 诊断与测试:对嵌入式系统进行自检和诊断。

【4.Bootloader 例程的编写方法】编写Bootloader 例程需要对STM32F103 微控制器的架构和外围设备有一定了解。

以下是编写Bootloader 例程的基本步骤:1) 配置开发环境:搭建针对STM32F103 微控制器的开发环境,包括编译器、调试器等。

2) 编写代码:按照Bootloader 例程的结构和功能,编写相应的代码。

数据手册STM32F103x6STM32F103x8 STM32F103xB 增强型,32位基于ARM核心的带闪存、USB、CAN的微控制器7个16位定时器、2个ADC 、9个通信接口功能■内核:ARM 32位的Cortex™-M3 CPU− 72MHz,1.25DMips/MHz(Dhrystone2.1),0等待周期的存储器−单周期乘法和硬件除法■存储器−从32K字节至128K字节的闪存程序存储器−从6K字节至20K字节的SRAM■时钟、复位和电源管理− 2.0至3.6伏供电和I/O管脚−上电/断电复位(POR/PDR)、可编程电压监测器(PVD)−内嵌4至16MHz高速晶体振荡器−内嵌经出厂调校的8MHz的RC振荡器−内嵌40kHz的RC振荡器− PLL供应CPU时钟−带校准功能的32kHz RTC振荡器■低功耗−睡眠、停机和待机模式−V BAT为RTC和后备寄存器供电■2个12位模数转换器,1us转换时间(16通道) −转换范围:0至3.6V−双采样和保持功能−温度传感器■DMA−7通道DMA控制器−支持的外设:定时器、ADC、SPI、I2C和USART■多达80个快速I/O口− 26/37/51/80个多功能双向5V兼容的I/O口−所有I/O口可以映像到16个外部中断■调试模式−串行线调试(SWD)和JTAG接口■多达7个定时器−多达3个16位定时器,每个定时器有多达4个用于输入捕获/输出比较/PWM或脉冲计数的通道− 16位6通道高级控制定时器−多达6路PWM输出−死区控制、边缘/中间对齐波形和紧急制动−2个看门狗定时器(独立的和窗口型的)−系统时间定时器:24位自减型■多达9个通信接口−多达2个I2C接口(SMBus/PMBus)−多达3个USART接口,支持ISO7816,LIN,IrDA接口和调制解调控制−多达2个SPI同步串行接口(18兆位/秒)− CAN接口(2.0B 主动)− USB 2.0全速接口■ECOPACK®封装(兼容RoHS)表一 器件列表参考基本型号STM32F103x6 STM32F103C6,STM32F103R6,STM32F103T6STM32F103x8 STM32F103C8, STM32F103R8,STM32F103V8, STM32F103T8 STM32F103xB STM32F103RB, STM32F103VB,STM32F103C8数据手册1 介绍 (3)2 规格说明 (3)2.1 器件一览 (4)2.2 概述 (5)3 管脚定义 (11)4 存储器映像 (19)5 电气特性 (20)6 封装参数 (20)7 订货代码 (20)7.1 后续的产品系列 (21)8 版本历史 (21)附录A 重要提示 (22)A.1PD0和PD1在输出模式下 (22)A.2ADC自动注入通道 (22)A.3ADC的混合同步注入+交替模式 (22)A.4ADC通道0 (22)1介绍本文给出了STM32F103xx增强型的订购信息和器件的机械特性。

![stm32f103中文手册[13]](https://uimg.taocdn.com/c309dec9f80f76c66137ee06eff9aef8951e4847.webp)

stm32f103中文手册一、概述高性能的ARM 32位Cortex-M3CPU,主频可达72MHz,具有单周期乘法和硬件除法指令,支持嵌套向量中断控制器(NVIC)和嵌入式跟踪宏单元(ETM)。

高密度的存储器资源,包括64KB至512KB的闪存,20KB至64KB的SR AM,以及可选的2KB的备份SRAM。

丰富的外设资源,包括12个通用定时器,2个高级定时器,3个同步串行接口(SPI),2个I2C接口,5个USART接口,1个USB全速设备接口,1个CAN接口,2个DAC转换器,2个12位ADC转换器,以及多达80个G PIO引脚。

灵活的时钟控制系统,支持4种内部时钟源和4种外部时钟源,以及多种预分频器和倍频器。

低功耗模式,包括睡眠模式、停止模式和待机模式,以及电压监测和温度传感器功能。

先进的调试和编程功能,支持JTAG和SWD接口,以及串行线调试(SWV)和串行线跟踪(SWO)功能。

二、引脚定义stm32f103的引脚定义如下图所示:其中:VDDA和VSSA分别为模拟电源正负极。

VDD和VSS分别为数字电源正负极。

NRST为复位引脚。

BOOT0和BOOT1为启动模式选择引脚。

PA0至PA15为端口A的16个GPIO引脚。

PB0至PB15为端口B的16个GPIO引脚。

PC0至PC15为端口C的16个GPIO引脚。

PD0至PD15为端口D的16个GPIO引脚(仅144引脚封装有)。

PE0至PE15为端口E的16个GPIO引脚(仅144引脚封装有)。

OSC_IN和OSC_OUT为外部晶振输入输出引脚。

JTMS/SWDIO、JTCK/SWCLK、JTDI、JTDO/TRACESWO、JNTRST分别为JTAG/SWD接口的5个信号线。

PB6/PB7/PB8/PB9/PB10/PB11分别可作为I2C1/I2C2接口的SCL/SDA 信号线。

PA4/PA5/PA6/PA7/PB12/PB13/PB14/PB15分别可作为SPI1/SPI2接口的NSS/SCK/MISO/MOSI信号线。

stm32f103vet6结构-回复stm32f103vet6是一款嵌入式系统的微控制器,广泛应用于各种电子设备中。

它具有丰富的外设和强大的性能,被许多开发者和制造商所青睐。

本文将详细介绍stm32f103vet6的结构,带你一步一步了解它的各个部分及其功能。

stm32f103vet6是意法半导体公司(STMicroelectronics)推出的一款32位ARM Cortex-M3内核的微控制器。

它采用了高性能的Flash和SRAM存储器,并配备了多个外设,适用于各种不同的应用场景。

现在,我们将深入探讨stm32f103vet6的结构。

1. ARM Cortex-M3内核:stm32f103vet6采用了ARM Cortex-M3内核,这是一种32位处理器架构。

它具有高性能和低功耗的特点,为处理器提供了强大的计算能力。

Cortex-M3内核还支持多种指令集,并且具有多层中断处理和低功耗模式。

这些特性使stm32f103vet6成为一款功能强大且适用于多种应用的微控制器。

2. Flash存储器:stm32f103vet6配备了512KB的Flash存储器,用于存储程序代码和数据。

Flash存储器具有非易失性的特点,当断电时,存储的数据仍然保持不变。

对于微控制器而言,Flash存储器起到了存储程序代码和数据的关键作用。

3. SRAM存储器:stm32f103vet6还具备96KB的静态随机存储器(SRAM)。

与Flash存储器不同,SRAM是易失性的,即当断电时,存储的数据会丢失。

SRAM 存储器对于临时存储数据起到了重要的作用,例如变量、中间计算结果等。

4. 外设:stm32f103vet6内置了许多外设,为开发者提供了丰富的接口和功能。

其中一些外设包括:- GPIO(通用输入/输出):用于与其他外设或传感器进行通信和数据交换。

- USART(通用同步/异步收发器):用于实现串行通信,例如与计算机或其他设备进行通信。

stm32f103芯片手册STM32F103是一款Cortex-M3内核的32位MCU芯片,由意法半导体(STMicroelectronics)公司生产。

该芯片具有低功耗、高计算性能和丰富的外设接口的特点,被广泛应用于各种应用领域。

下面是对STM32F103芯片手册的1000字简要介绍。

首先,STM32F103芯片具有强大的计算能力和丰富的存储器资源。

它采用了ARM Cortex-M3内核,主频可高达72MHz,同时支持单周期乘法和硬件除法指令,可快速执行复杂的算法。

此外,芯片内置了128KB或256KB的闪存和20KB的静态RAM,可以存储大量的程序代码和数据。

其次,STM32F103芯片提供了丰富的外设接口,能够满足各种应用需求。

它包括多个通用输入/输出(GPIO)引脚,可用于连接外部设备和传感器。

同时,芯片还提供了多个串行通信接口,如USART、SPI和I2C,可以与其他设备进行高速数据传输。

此外,芯片还支持多个定时器/计数器,用于实现精确的计时和定时功能。

第三,STM32F103芯片具有低功耗特性和丰富的电源管理功能。

它采用了多种节能技术,如待机模式、休眠模式和停机模式,可以最大限度地降低功耗。

同时,芯片还内置了多个电源管理模块,例如低功耗时钟、电压调整器和电池备份电源,以提供稳定可靠的电源供应。

最后,STM32F103芯片还提供了完善的开发工具和支持资源。

意法半导体提供了一整套的软件开发工具,包括Keil MDK和IAR Embedded Workbench等,可简化开发流程。

此外,芯片手册还详细介绍了芯片的引脚定义、寄存器配置、时钟设置、中断管理、外设控制等内容,为开发者提供了全面的技术支持。

综上所述,STM32F103芯片手册详细介绍了该芯片的技术规格、外设接口、低功耗特性和开发支持资源。

它具有强大的计算能力、丰富的存储资源和多样化的外设功能,适用于各种应用领域,如工业控制、智能家居、医疗设备等。

数据手册STM32F103x6STM32F103x8 STM32F103xB 增强型,32位基于ARM核心的带闪存、USB、CAN的微控制器7个16位定时器、2个ADC 、9个通信接口功能■内核:ARM 32位的Cortex™-M3 CPU− 72MHz,1.25DMips/MHz(Dhrystone2.1),0等待周期的存储器−单周期乘法和硬件除法■存储器−从32K字节至128K字节的闪存程序存储器−从6K字节至20K字节的SRAM■时钟、复位和电源管理− 2.0至3.6伏供电和I/O管脚−上电/断电复位(POR/PDR)、可编程电压监测器(PVD)−内嵌4至16MHz高速晶体振荡器−内嵌经出厂调校的8MHz的RC振荡器−内嵌40kHz的RC振荡器− PLL供应CPU时钟−带校准功能的32kHz RTC振荡器■低功耗−睡眠、停机和待机模式−V BAT为RTC和后备寄存器供电■2个12位模数转换器,1us转换时间(16通道) −转换范围:0至3.6V−双采样和保持功能−温度传感器■DMA−7通道DMA控制器−支持的外设:定时器、ADC、SPI、I2C和USART■多达80个快速I/O口− 26/37/51/80个多功能双向5V兼容的I/O口−所有I/O口可以映像到16个外部中断■调试模式−串行线调试(SWD)和JTAG接口■多达7个定时器−多达3个16位定时器,每个定时器有多达4个用于输入捕获/输出比较/PWM或脉冲计数的通道− 16位6通道高级控制定时器−多达6路PWM输出−死区控制、边缘/中间对齐波形和紧急制动−2个看门狗定时器(独立的和窗口型的)−系统时间定时器:24位自减型■多达9个通信接口−多达2个I2C接口(SMBus/PMBus)−多达3个USART接口,支持ISO7816,LIN,IrDA接口和调制解调控制−多达2个SPI同步串行接口(18兆位/秒)− CAN接口(2.0B 主动)− USB 2.0全速接口■ECOPACK®封装(兼容RoHS)表一 器件列表参考基本型号STM32F103x6 STM32F103C6,STM32F103R6,STM32F103T6STM32F103x8 STM32F103C8, STM32F103R8,STM32F103V8, STM32F103T8 STM32F103xB STM32F103RB, STM32F103VB,STM32F103C8数据手册1 介绍 (3)2 规格说明 (3)2.1 器件一览 (4)2.2 概述 (5)3 管脚定义 (11)4 存储器映像 (19)5 电气特性 (20)6 封装参数 (20)7 订货代码 (20)7.1 后续的产品系列 (21)8 版本历史 (21)附录A 重要提示 (22)A.1PD0和PD1在输出模式下 (22)A.2ADC自动注入通道 (22)A.3ADC的混合同步注入+交替模式 (22)A.4ADC通道0 (22)1介绍本文给出了STM32F103xx增强型的订购信息和器件的机械特性。

![stm32f103中文手册[7]](https://uimg.taocdn.com/38586d2658eef8c75fbfc77da26925c52cc59127.webp)

stm32f103中文手册1. 概述stm32f103是一款高性能、低功耗、高集成度的32位微控制器,基于ARM Cortex-M3内核,支持Thumb-2指令集,具有72MHz的主频和64KB至512KB的闪存。

stm32f103具有丰富的外设资源,包括多种通信接口、定时器、模数转换器、DMA控制器、触摸感应控制器等,能够满足各种复杂的应用需求。

stm32f103还具有多种低功耗模式,能够实现动态电源管理,降低系统功耗。

stm32f1 03采用多种封装形式,适用于不同的应用场合。

2. 引脚定义stm32f103的引脚定义如图1所示。

stm32f103的引脚分为四类:电源引脚、复位引脚、晶振引脚和功能引脚。

电源引脚包括VDD、VSS、V DDA和VSSA,分别提供数字电源、数字地、模拟电源和模拟地。

复位引脚包括NRST和BOOT0,分别用于复位芯片和选择启动模式。

晶振引脚包括OSC_IN和OSC_OUT,分别连接外部晶振的输入和输出端。

功能引脚包括多达80个可编程的通用输入输出(GPIO)引脚,以及一些专用功能引脚,如JTAG/SWD调试接口、USB接口等。

图1 stm32f103引脚定义3. 系统架构ARM Cortex-M3内核:是stm32f103的核心部分,负责执行程序指令,处理数据和中断等。

存储器:包括闪存(Flash)、静态随机存储器(SRAM)和备份寄存器(Backupregisters),分别用于存储程序代码、数据和备份数据等。

外设总线:包括总线矩阵(Bus matrix)、总线桥(Bus bridge)和外设总线(Peripheralbus),分别用于连接内核、存储器和外设等。

时钟和复位控制:包括时钟树(Clocktree)、复位控制器(Reset controller)和电源管理单元(Power managementunit),分别用于提供时钟信号、复位信号和电源管理等。

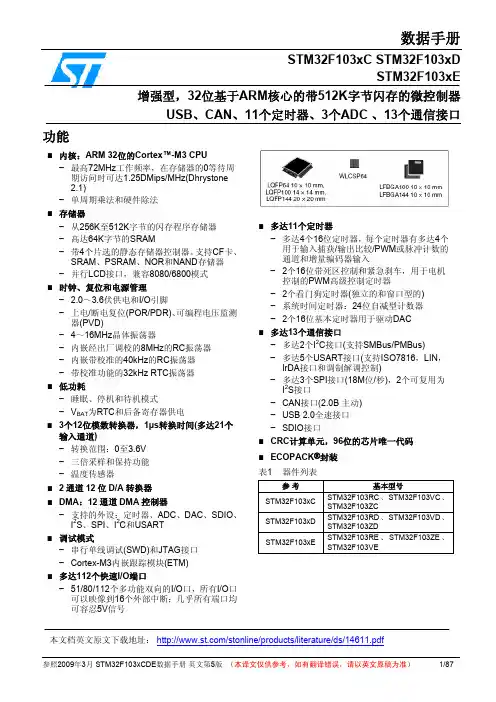

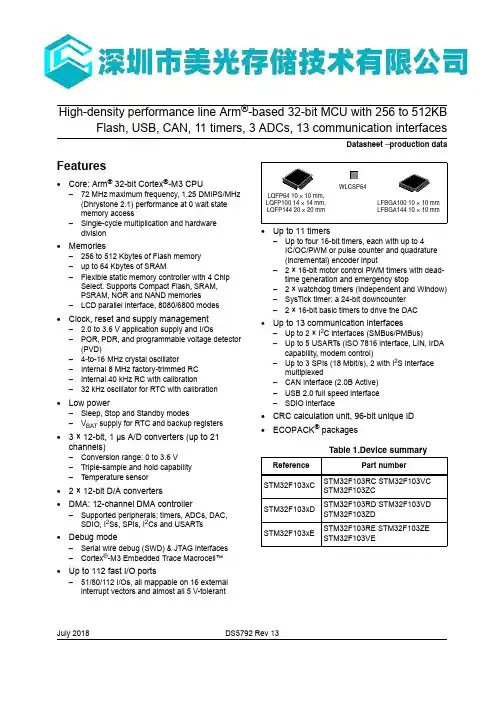

High-density performance line Arm®-based 32-bit MCU with 256 to 512KB Flash, USB, CAN, 11 timers, 3 ADCs, 13 communication interfacesDatasheet − production data Features•Core: Arm® 32-bit Cortex®-M3 CPU–72 MHz maximum frequency, 1.25DMIPS/MHz(Dhrystone 2.1) performance at 0 wait statememory access–Single-cycle multiplication and hardwaredivision•Memories–256 to 512 Kbytes of Flash memory–up to 64 Kbytes of SRAM–Flexible static memory controller with 4 Chip Select. Supports Compact Flash, SRAM,PSRAM, NOR and NAND memories–LCD parallel interface, 8080/6800 modes •Clock, reset and supply management – 2.0 to 3.6V application supply and I/Os–POR, PDR, and programmable voltage detector (PVD)–4-to-16 MHz crystal oscillator–Internal 8 MHz factory-trimmed RC–Internal 40 kHz RC with calibration–32 kHz oscillator for RTC with calibration •Low power–Sleep, Stop and Standby modes–V BAT supply for RTC and backup registers • 3 × 12-bit, 1 µs A/D converters (up to 21channels)–Conversion range: 0 to 3.6 V–Triple-sample and hold capability–Temperature sensor• 2 × 12-bit D/A converters•DMA: 12-channel DMA controller–Supported peripherals: timers, ADCs, DAC, SDIO, I2Ss, SPIs, I2Cs and USARTs •Debug mode–Serial wire debug (SWD) & JTAG interfaces–Cortex®-M3 Embedded Trace Macrocell™•Up to 112 fast I/O ports–51/80/112 I/Os, all mappable on 16 external interrupt vectors and almost all 5V-tolerant •Up to 11 timers–Up to four 16-bit timers, each with up to 4IC/OC/PWM or pulse counter and quadrature(incremental) encoder input– 2 × 16-bit motor control PWM timers with dead-time generation and emergency stop– 2 × watchdog timers (Independent and Window)–SysTick timer: a 24-bit downcounter– 2 × 16-bit basic timers to drive the DAC•Up to 13 communication interfaces–Up to 2 × I2C interfaces (SMBus/PMBus)–Up to 5 USARTs (ISO 7816 interface, LIN, IrDA capability, modem control)–Up to 3 SPIs (18 Mbit/s), 2 with I2S interface multiplexed–CAN interface (2.0B Active)–USB 2.0 full speed interface–SDIO interface•CRC calculation unit, 96-bit unique ID •ECOPACK® packagesTable 1.Device summary Reference Part numberSTM32F103xCSTM32F103RC STM32F103VCSTM32F103ZCSTM32F103xDSTM32F103RD STM32F103VDSTM32F103ZDSTM32F103xESTM32F103RE STM32F103ZESTM32F103VEJuly 2018DS5792 Rev 13STM32F103xC, STM32F103xD, STM32F103xE Description modes2.3.10 BootAt startup, boot pins are used to select one of three boot options:•Boot from user Flash: you have an option to boot from any of two memory banks. By default, boot from Flash memory bank 1 is selected. You can choose to boot from Flashmemory bank 2 by setting a bit in the option bytes.•Boot from system memory•Boot from embedded SRAMThe boot loader is located in system memory. It is used to reprogram the Flash memory byusing USART1.2.3.11 Power supply schemes•V DD = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator.Provided externally through V DD pins.•V SSA, V DDA = 2.0 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL (minimum voltage to be applied to VDDA is 2.4 V when the ADCor DAC is used). V DDA and V SSA must be connected to V DD and V SS, respectively.•V BAT = 1.8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V DD is not present.For more details on how to connect power pins, refer to Figure12: Power supply scheme.2.3.12 Power supply supervisorThe device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It isalways active, and ensures proper operation starting from/down to 2 V. The device remainsin reset mode when V DD is below a specified threshold, V POR/PDR, without the need for anexternal reset circuit.The device features an embedded programmable voltage detector (PVD) that monitors theV DD/V DDA power supply and compares it to the V PVD threshold. An interrupt can begenerated when V DD/V DDA drops below the V PVD threshold and/or when V DD/V DDA ishigher than the V PVD threshold. The interrupt service routine can then generate a warningmessage and/or put the MCU into a safe state. The PVD is enabled by software. Refer toTable12: Embedded reset and power control block characteristics for the values ofV POR/PDR and V PVD.2.3.13 VoltageregulatorThe regulator has three operation modes: main (MR), low-power (LPR) and power down.•MR is used in the nominal regulation mode (Run)•LPR is used in the Stop modes.•Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of theregisters and SRAM are lost)This regulator is always enabled after reset. It is disabled in Standby mode.DS5792 Rev 13Description STM32F103xC, STM32F103xD, STM32F103xEDS5792 Rev 132.3.14 Low-power modesThe STM32F103xC, STM32F103xD and STM32F103xE performance line supports threelow-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:•Sleep modeIn Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.•Stop modeStop mode achieves the lowest power consumption while retaining the content ofSRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm or the USB wakeup.•Standby modeThe Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm occurs.Note:The RTC, the IWDG , and the corresponding clock sources are not stopped by entering Stop or Standby mode.2.3.15 DMAThe flexible 12-channel general-purpose DMAs (7 channels for DMA1 and 5 channels for DMA2) are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The two DMA controllers support circular buffer management,removing the need for user code intervention when the controller reaches the end of the buffer.Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.The DMA can be used with the main peripherals: SPI, I 2C, USART, general-purpose, basic and advanced-control timers TIMx, DAC, I 2S, SDIO and ADC.2.3.16 RTC (real-time clock) and backup registersThe RTC and the backup registers are supplied through a switch that takes power either on V DD supply when present or through the V BAT pin. The backup registers are forty-two 16-bit registers used to store 84 bytes of user application data when V DD power is not present. They are not reset by a system or power reset, and they are not reset when the device wakes up from the Standby mode.The real-time clock provides a set of continuously running counters which can be used with suitable software to provide a clock calendar function, and provides an alarm interrupt and aSTM32F103xC, STM32F103xD, STM32F103xEDescriptionDS5792 Rev 13Description STM32F103xC, STM32F103xD, STM32F103xEAdvanced-control timers (TIM1 and TIM8)The two advanced-control timers (TIM1 and TIM8) can each be seen as a three-phasePWM multiplexed on 6 channels. They have complementary PWM outputs withprogrammable inserted dead-times. They can also be seen as a complete general-purposetimer. The 4 independent channels can be used for:•Input capture•Output compare•PWM generation (edge or center-aligned modes)•One-pulse mode outputIf configured as a standard 16-bit timer, it has the same features as the TIMx timer. Ifconfigured as the 16-bit PWM generator, it has full modulation capability (0-100%).In debug mode, the advanced-control timer counter can be frozen and the PWM outputsdisabled to turn off any power switch driven by these outputs.Many features are shared with those of the general-purpose TIM timers which have thesame architecture. The advanced-control timer can therefore work together with the TIMtimers via the Timer Link feature for synchronization or event chaining.General-purpose timers (TIMx)There are up to 4 synchronizable general-purpose timers (TIM2, TIM3, TIM4 and TIM5)embedded in the STM32F103xC, STM32F103xD and STM32F103xE performance linedevices. These timers are based on a 16-bit auto-reload up/down counter, a 16-bit prescalerand feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input captures / output compares / PWMs on thelargest packages.The general-purpose timers can work together with the advanced-control timer via the TimerLink feature for synchronization or event chaining. Their counter can be frozen in debugmode. Any of the general-purpose timers can be used to generate PWM outputs. They allhave independent DMA request generation.These timers are capable of handling quadrature (incremental) encoder signals and thedigital outputs from 1 to 3 hall-effect sensors.Basic timers TIM6 and TIM7These timers are mainly used for DAC trigger generation. They can also be used as ageneric 16-bit time base.Independent watchdogThe independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It isclocked from an independent 40 kHz internal RC and as it operates independently from themain clock, it can operate in Stop and Standby modes. It can be used either as a watchdogto reset the device when a problem occurs, or as a free running timer for application timeoutmanagement. It is hardware or software configurable through the option bytes. The countercan be frozen in debug mode.Window watchdogThe window watchdog is based on a 7-bit downcounter that can be set as free running. Itcan be used as a watchdog to reset the device when a problem occurs. It is clocked fromDS5792 Rev 13。

stm32f103vet bootloader例程【原创实用版】目录1.STM32F103vet Bootloader 简介2.Bootloader 例程的作用3.Bootloader 例程的结构和主要功能4.Bootloader 例程的编写和调试5.Bootloader 例程的应用场景正文【1.STM32F103vet Bootloader 简介】STM32F103vet 是一款由 STMicroelectronics 公司推出的高性能微控制器,广泛应用于各种嵌入式系统中。

Bootloader 是嵌入式系统中的一个关键组件,主要用于烧写固件到芯片中,从而实现对微控制器的控制。

STM32F103vet Bootloader 例程则是针对这款微控制器的 Bootloader程序,可以帮助开发者快速实现固件烧写功能。

【2.Bootloader 例程的作用】Bootloader 例程在嵌入式系统开发中具有重要作用,主要表现在以下几个方面:1.烧写固件:Bootloader 例程可以将编译好的固件烧写到STM32F103vet 微控制器中,从而实现对微控制器的控制。

2.诊断和测试:Bootloader 例程可以用于对微控制器进行诊断和测试,以确保微控制器的功能正常。

3.系统初始化:Bootloader 例程可以对微控制器进行初始化,包括时钟设置、GPIO 配置等,为后续应用程序的运行做好准备。

【3.Bootloader 例程的结构和主要功能】STM32F103vet Bootloader 例程主要包括以下几个部分:1.启动代码:包括复位、时钟设置等初始化操作。

B 通信:Bootloader 例程需要通过 USB 与上位机通信,以接收固件文件和发送烧写进度等信息。

3.固件烧写:将固件文件烧写到微控制器的闪存中。

4.诊断和测试:对微控制器进行诊断和测试,确保功能正常。

5.系统初始化:配置 GPIO、时钟等,为应用程序的运行做好准备。

STM32F10xxx参考手册参考手册小,中和大容量的STM32F101xx, STM32F102xx和STM32F103xxARM内核32位高性能微控制器导言本参考手册针对应用开发,提供关于如何使用小容量、中容量和大容量的STM32F101xx、STM32F102xx或者STM32F103xx微控制器的存储器和外设的详细信息。

在本参考手册中STM32F101xx、STM32F102xx和STM32F103xx被统称为STM32F10xxx。

STM32F10xxx系列拥有不同的存储器容量,封装和外设配置。

关于订货编号、电气和物理性能参数,请参考STM32F101xx、STM32F102xx和STM32F103xx 的数据手册。

关于芯片内部闪存的编程,擦除和保护操作,请参考STM32F10xxx闪存编程手册。

关于ARM Cortex™-M3内核的具体信息,请参考Cortex™-M3技术参考手册。

相关文档● Cortex™-M3技术参考手册,可按下述链接下载:/help/topic/com.arm.doc.ddi0337e/DDI0337E_cortex_m3_r1p1_trm.pdf下述文档可在ST网站下载(/mcu/):● STM32F101xx、STM32F102xx和STM32F103xx的数据手册。

● STM32F10xxx闪存编程手册。

* 感谢南京万利提供原始翻译文档目录1文中的缩写 161.1寄存器描述表中使用的缩写列表 161.2术语表161.3可用的外设16 2存储器和总线构架 172.1系统构架172.2存储器组织182.3存储器映像192.3.1嵌入式SRAM 202.3.2位段202.3.3嵌入式闪存 212.4启动配置23 3CRC计算单元(CRC) 253.1CRC简介253.2CRC主要特性253.3CRC功能描述253.4CRC寄存器263.4.1数据寄存器(CRC_DR) 263.4.2独立数据寄存器(CRC_IDR) 263.4.3控制寄存器(CRC_CR) 273.4.4CRC寄存器映像 27 4电源控制(PWR) 284.1电源284.1.1独立的A/D转换器供电和参考电压 284.1.2电池备份区域 294.1.3电压调节器 294.2电源管理器294.2.1上电复位(POR)和掉电复位(PDR) 294.2.2可编程电压监测器(PVD) 304.3低功耗模式304.3.1降低系统时钟 314.3.2外部时钟的控制 314.3.3睡眠模式 314.3.4停止模式 324.3.5待机模式 334.3.6低功耗模式下的自动唤醒(AWU) 344.4电源控制寄存器 354.4.1电源控制寄存器(PWR_CR) 354.4.2电源控制/状态寄存器 364.4.3PWR寄存器地址映像 37 5备份寄存器(BKP) 385.1BKP简介385.2BKP特性385.3BKP功能描述385.3.1侵入检测 385.3.2RTC校准 395.4BKP寄存器描述 395.4.1备份数据寄存器x(BKP_DRx) (x = 1 … 10) 395.4.2RTC时钟校准寄存器(BKP_RTCCR) 395.4.3备份控制寄存器(BKP_CR) 405.4.4备份控制/状态寄存器(BKP_CSR) 405.4.5BKP寄存器映像 42 6复位和时钟控制(RCC) 456.1复位456.1.1系统复位 456.1.2电源复位 456.1.3备份域复位 466.2时钟466.2.1HSE时钟 486.2.2HSI时钟 486.2.3PLL 496.2.4LSE时钟 496.2.5LSI时钟496.2.6系统时钟(SYSCLK)选择 506.2.7时钟安全系统(CSS) 506.2.8RTC时钟 506.2.9看门狗时钟 506.2.10时钟输出 506.3RCC寄存器描述 516.3.1时钟控制寄存器(RCC_CR) 516.3.2时钟配置寄存器(RCC_CFGR) 526.3.3时钟中断寄存器 (RCC_CIR) 546.3.4APB2外设复位寄存器 (RCC_APB2RSTR) 566.3.5APB1外设复位寄存器 (RCC_APB1RSTR) 586.3.6AHB外设时钟使能寄存器 (RCC_AHBENR) 606.3.7APB2外设时钟使能寄存器(RCC_APB2ENR) 616.3.8APB1外设时钟使能寄存器(RCC_APB1ENR) 626.3.9备份域控制寄存器 (RCC_BDCR) 656.3.10控制/状态寄存器 (RCC_CSR) 666.3.11RCC寄存器地址映像 68 7通用和复用功能I/O(GPIO和AFIO) 697.1GPIO功能描述697.1.1通用I/O(GPIO) 707.1.2单独的位设置或位清除 717.1.3外部中断/唤醒线 717.1.4复用功能(AF) 717.1.5软件重新映射I/O复用功能 717.1.6GPIO锁定机制 717.1.7输入配置 717.1.8输出配置 727.1.9复用功能配置 737.1.10模拟输入配置 737.2GPIO寄存器描述 757.2.1端口配置低寄存器(GPIOx_CRL) (x=A..E) 757.2.2端口配置高寄存器(GPIOx_CRH) (x=A..E) 757.2.3端口输入数据寄存器(GPIOx_IDR) (x=A..E) 767.2.4端口输出数据寄存器(GPIOx_ODR) (x=A..E) 767.2.5端口位设置/清除寄存器(GPIOx_BSRR) (x=A..E) 777.2.6端口位清除寄存器(GPIOx_BRR) (x=A..E) 777.2.7端口配置锁定寄存器(GPIOx_LCKR) (x=A..E) 777.3复用功能I/O和调试配置(AFIO) 787.3.1把OSC32_IN/OSC32_OUT作为GPIO 端口PC14/PC15 787.3.2把OSC_IN/OSC_OUT引脚作为GPIO端口PD0/PD1 787.3.3CAN复用功能重映射 797.3.4JTAG/SWD复用功能重映射 797.3.5ADC复用功能重映射 807.3.6定时器复用功能重映射 807.3.7USART复用功能重映射 817.3.8I2C 1 复用功能重映射 827.3.9SPI 1复用功能重映射 827.4AFIO寄存器描述 837.4.1事件控制寄存器(AFIO_EVCR) 837.4.2复用重映射和调试I/O配置寄存器(AFIO_MAPR) 837.4.3外部中断配置寄存器1(AFIO_EXTICR1) 867.4.4外部中断配置寄存器2(AFIO_EXTICR2) 867.4.5外部中断配置寄存器3(AFIO_EXTICR3) 877.4.6外部中断配置寄存器4(AFIO_EXTICR4) 877.5GPIO 和AFIO寄存器地址映象 88 8中断和事件 898.1嵌套向量中断控制器 898.1.1系统嘀嗒(SysTick)校准值寄存器 898.1.2中断和异常向量 898.2外部中断/事件控制器(EXTI) 918.2.1主要特性 918.2.2框图928.2.3唤醒事件管理 928.2.4功能说明 928.2.5外部中断/事件线路映像 948.3EXTI 寄存器描述 958.3.1中断屏蔽寄存器(EXTI_IMR) 958.3.2事件屏蔽寄存器(EXTI_EMR) 958.3.3上升沿触发选择寄存器(EXTI_RTSR) 968.3.4下降沿触发选择寄存器(EXTI_FTSR) 968.3.5软件中断事件寄存器(EXTI_SWIER) 978.3.6挂起寄存器(EXTI_PR) 978.3.7外部中断/事件寄存器映像 98 9DMA 控制器(DMA) 999.1DMA简介999.2DMA主要特性999.3功能描述1009.3.1DMA处理 1009.3.2仲裁器1009.3.3DMA 通道 1019.3.4可编程的数据传输宽度,对齐方式和数据大小端 1029.3.5错误管理 1039.3.6中断1039.3.7DMA请求映像 1049.4DMA寄存器1079.4.1DMA中断状态寄存器(DMA_ISR) 1079.4.2DMA中断标志清除寄存器(DMA_IFCR) 1089.4.3DMA通道x配置寄存器(DMA_CCRx)(x = 1…7) 1089.4.4DMA通道x传输数量寄存器(DMA_CNDTRx)(x = 1…7) 1109.4.5DMA通道x外设地址寄存器(DMA_CPARx)(x = 1…7) 1109.4.6DMA通道x存储器地址寄存器(DMA_CPARx)(x = 1…7) 1109.4.7DMA寄存器映像 111 10模拟/数字转换(ADC) 11310.1ADC介绍11310.2ADC主要特征11310.3ADC功能描述11410.3.1ADC开关控制 11510.3.2ADC时钟 11510.3.3通道选择 11510.3.4单次转换模式 11510.3.5连续转换模式 11610.3.6时序图11610.3.7模拟看门狗 11610.3.8扫描模式 11710.3.9注入通道管理 11710.3.10间断模式 11810.4校准11910.5数据对齐11910.6可编程的通道采样时间 12010.7外部触发转换12010.8DMA请求12110.9双ADC模式12110.9.1同步注入模式 12210.9.2同步规则模式 12310.9.3快速交替模式 12310.9.4慢速交替模式 12410.9.5交替触发模式 12410.9.6独立模式 12510.9.7混合的规则/注入同步模式 12510.9.8混合的同步规则+交替触发模式 12510.9.9混合同步注入+交替模式 12610.10温度传感器12610.11ADC中断12710.12ADC寄存器描述 12810.12.1ADC状态寄存器(ADC_SR) 12810.12.2ADC控制寄存器1(ADC_CR1) 12910.12.3ADC控制寄存器2(ADC_CR2) 13110.12.4ADC采样时间寄存器1(ADC_SMPR1) 13310.12.5ADC采样时间寄存器2(ADC_SMPR2) 13310.12.6ADC注入通道数据偏移寄存器x (ADC_JOFRx)(x=1..4) 13410.12.7ADC看门狗高阀值寄存器(ADC_HTR) 13410.12.8ADC看门狗低阀值寄存器(ADC_LRT) 13410.12.9ADC规则序列寄存器1(ADC_SQR1) 13510.12.10ADC规则序列寄存器2(ADC_SQR2) 13510.12.11ADC规则序列寄存器3(ADC_SQR3) 13610.12.12ADC注入序列寄存器(ADC_JSQR) 13610.12.13ADC 注入数据寄存器x (ADC_JDRx) (x= 1..4) 13710.12.14ADC规则数据寄存器(ADC_DR) 13710.12.15ADC寄存器地址映像 138 11数字/模拟转换(DAC) 14011.1DAC简介14011.2DAC主要特征14011.3DAC功能描述14111.3.1使能DAC通道 14111.3.2使能DAC输出缓存 14111.3.3DAC数据格式 14211.3.4DAC转换 14211.3.5DAC输出电压 14311.3.6选择DAC触发 14311.3.7DMA请求 14411.3.8噪声生成 14411.3.9三角波生成 14511.4双DAC通道转换 14511.4.1无波形生成的独立触发 14511.4.2带相同LFSR生成的独立触发 14611.4.3带不同LFSR生成的独立触发 14611.4.4带相同三角波生成的独立触发 14611.4.5带不同三角波生成的独立触发 14611.4.6同时软件启动 14711.4.7不带波形生成的同时触发 14711.4.8带相同LFSR生成的同时触发 14711.4.9带不同LFSR生成的同时触发 14711.4.10带相同三角波生成的同时触发 14711.4.11带不同三角波生成的同时触发 14811.5DAC寄存器14911.5.1DAC控制寄存器(DAC_CR) 14911.5.2DAC软件触发寄存器(DAC_SWTRIGR) 15111.5.3DAC通道1的12位右对齐数据保持寄存器(DAC_DHR12R1) 15211.5.4DAC通道1的12位左对齐数据保持寄存器(DAC_DHR12L1) 15211.5.5DAC通道1的8位右对齐数据保持寄存器(DAC_DHR8R1) 15211.5.6DAC通道2的12位右对齐数据保持寄存器(DAC_DHR12R2) 15311.5.7DAC通道2的12位左对齐数据保持寄存器(DAC_DHR12L2) 15311.5.8DAC通道2的8位右对齐数据保持寄存器(DAC_DHR8R2) 15311.5.9双DAC的12位右对齐数据保持寄存器(DAC_DHR12RD) 15411.5.10双DAC的12位左对齐数据保持寄存器(DAC_DHR12LD) 15411.5.11双DAC的8位右对齐数据保持寄存器(DAC_DHR8RD) 15411.5.12DAC通道1数据输出寄存器(DAC_DOR1) 15511.5.13DAC通道2数据输出寄存器(DAC_DOR2) 15511.5.14DAC寄存器映像 156 12高级控制定时器(TIM1和TIM8) 15712.1TIM1和TIM8简介 15712.2TIM1和TIM8主要特性 15712.3TIM1和TIM8功能描述 15812.3.1时基单元 15812.3.2计数器模式 16012.3.3重复计数器 16712.3.4时钟选择 16812.3.5捕获/比较通道 17112.3.6输入捕获模式 17312.3.7PWM输入模式 17412.3.8强置输出模式 17412.3.9输出比较模式 17512.3.10PWM模式 17612.3.11互补输出和死区插入 17812.3.12使用刹车功能 17912.3.13在外部事件时清除OCxREF信号 18012.3.14产生六步PWM输出 18112.3.15单脉冲模式 18212.3.16编码器接口模式 18312.3.17定时器输入异或功能 18512.3.18与霍尔传感器的接口 18512.3.19TIMx定时器和外部触发的同步 18712.3.20定时器同步 19012.3.21调试模式 19012.4TIM1和TIM8寄存器描述 19112.4.1控制寄存器1(TIMx_CR1) 19112.4.2控制寄存器2(TIMx_CR2) 19212.4.3从模式控制寄存器(TIMx_SMCR) 19312.4.4DMA/中断使能寄存器(TIMx_DIER) 19512.4.5状态寄存器(TIMx_SR) 19612.4.6事件产生寄存器(TIMx_EGR) 19712.4.7捕获/比较模式寄存器1(TIMx_CCMR1) 19812.4.8捕获/比较模式寄存器2(TIMx_CCMR2) 20012.4.9捕获/比较使能寄存器(TIMx_CCER) 20212.4.10计数器(TIMx_CNT) 20312.4.11预分频器(TIMx_PSC) 20412.4.12自动重装载寄存器(TIMx_ARR) 20412.4.13重复计数寄存器(TIMx_RCR) 20412.4.14捕获/比较寄存器1(TIMx_CCR1) 20512.4.15捕获/比较寄存器2(TIMx_CCR2) 20512.4.16捕获/比较寄存器3(TIMx_CCR3) 20512.4.17捕获/比较寄存器(TIMx_CCR4) 20612.4.18刹车和死区寄存器(TIMx_BDTR) 20612.4.19DMA控制寄存器(TIMx_DCR) 20812.4.20连续模式的DMA地址(TIMx_DMAR) 20812.4.21TIM1和TIM8寄存器图 209 13通用定时器(TIMx) 21113.1TIMx简介21113.2TIMx主要功能21113.3TIMx功能描述21213.3.1时基单元 21213.3.2计数器模式 21313.3.3时钟选择 22113.3.4捕获/比较通道 22313.3.5输入捕获模式 22513.3.6PWM输入模式 22513.3.7强置输出模式 22613.3.8输出比较模式 22613.3.9PWM 模式 22713.3.10单脉冲模式 22913.3.11在外部事件时清除OCxREF信号 23113.3.12编码器接口模式 23113.3.13定时器输入异或功能 23313.3.14定时器和外部触发的同步 23313.3.15定时器同步 23513.3.16调试模式 23913.4TIMx寄存器描述 24013.4.1控制寄存器1(TIMx_CR1) 24013.4.2控制寄存器2(TIMx_CR2) 24113.4.3从模式控制寄存器(TIMx_SMCR) 24213.4.4DMA/中断使能寄存器(TIMx_DIER) 24313.4.5状态寄存器(TIMx_SR) 24413.4.6事件产生寄存器(TIMx_EGR) 24513.4.7捕获/比较模式寄存器1(TIMx_CCMR1) 24613.4.8捕获/比较模式寄存器2(TIMx_CCMR2) 24913.4.9捕获/比较使能寄存器(TIMx_CCER) 25113.4.10计数器(TIMx_CNT) 25213.4.11预分频器(TIMx_PSC) 25213.4.12自动重装载寄存器(TIMx_ARR) 25213.4.13捕获/比较寄存器1(TIMx_CCR1) 25213.4.14捕获/比较寄存器2(TIMx_CCR2) 25313.4.15捕获/比较寄存器3(TIMx_CCR3) 25313.4.16捕获/比较寄存器4(TIMx_CCR4) 25313.4.17DMA控制寄存器(TIMx_DCR) 25413.4.18连续模式的DMA地址(TIMx_DMAR) 25413.4.19TIMx寄存器图 255 14基本定时器(TIM6和TIM7) 25714.1TIM6和TIM7简介 25714.2TIM6和TIM7的主要特性 25714.3TIM6和TIM7的功能 25814.3.1时基单元 25814.3.2计数模式 25914.3.3时钟源26114.3.4调试模式 26214.4TIM6和TIM7寄存器 26214.4.1控制寄存器1(TIMx_CR1) 26214.4.2控制寄存器2(TIMx_CR2) 26314.4.3DMA/中断使能寄存器(TIMx_DIER) 26314.4.4状态寄存器(TIMx_SR) 26414.4.5事件产生寄存器(TIMx_EGR) 26414.4.6计数器(TIMx_CNT) 26414.4.7预分频器(TIMx_PSC) 26514.4.8自动重装载寄存器(TIMx_ARR) 26514.4.9TIM6和TIM7寄存器图 266 15实时时钟(RTC) 26715.1RTC简介26715.2主要特性26715.3功能描述26715.3.1概述26715.3.2复位过程 26815.3.3读RTC寄存器 26815.3.4配置RTC寄存器 26915.3.5RTC标志的设置 26915.4RTC寄存器描述 27015.4.1RTC控制寄存器高位(RTC_CRH) 27015.4.2RTC控制寄存器低位(RTC_CRL) 27015.4.3RTC预分频装载寄存器(RTC_PRLH/RTC_PRLL) 27115.4.4RTC预分频器余数寄存器(RTC_DIVH / RTC_DIVL) 27215.4.5RTC计数器寄存器 (RTC_CNTH / RTC_CNTL) 27215.4.6RTC闹钟寄存器(RTC_ALRH/RTC_ALRL) 27315.4.7RTC寄存器映像 275 16独立看门狗(IWDG) 27616.1简介27616.2IWDG主要性能27616.3IWDG功能描述27616.3.1硬件看门狗 27616.3.2寄存器访问保护 27616.3.3调试模式 27616.4IWDG寄存器描述 27716.4.1键寄存器(IWDG_KR) 27716.4.2预分频寄存器(IWDG_PR) 27816.4.3重装载寄存器(IWDG_RLR) 27816.4.4状态寄存器(IWDG_SR) 27916.4.5IWDG寄存器映像 279 17窗口看门狗(WWDG) 28017.1WWDG简介28017.2WWDG主要特性 28017.3WWDG功能描述 28017.4如何编写看门狗超时程序 28117.5调试模式28217.6寄存器描述28217.6.1控制寄存器(WWDG_CR) 28217.6.2配置寄存器(WWDG_CFR) 28317.6.3状态寄存器(WWDG_SR) 28317.6.4WWDG寄存器映像 284 18灵活的静态存储器控制器(FSMC) 28518.1FSMC功能描述28518.2框图28518.3AHB接口28618.3.1支持的存储器和操作 28618.4外部设备地址映像 28718.4.1NOR和PSRAM地址映像 28818.4.2NAND和PC卡地址映像 28818.5NOR闪存和PSRAM控制器 28918.5.1外部存储器接口信号 29018.5.2支持的存储器及其操作 29118.5.3时序规则 29118.5.4NOR闪存和PSRAM时序图 29118.5.5同步的成组读 30418.5.6NOR闪存和PSRAM控制器寄存器 30818.6NAND闪存和PC卡控制器 31318.6.1外部存储器接口信号 31318.6.2NAND闪存/PC卡支持的存储器及其操作 31418.6.3NAND闪存、ATA和PC卡时序图 31418.6.4NAND闪存操作 31518.6.5NAND闪存预等待功能 31618.6.6NAND闪存的纠错码ECC计算(NAND闪存) 31718.6.7NAND闪存和PC卡控制器寄存器 31718.7FSMC寄存器地址映象 324 19SDIO接口(SDIO) 32519.1SDIO主要功能32519.2SDIO总线拓扑32519.3SDIO功能描述32819.3.1SDIO适配器 32919.3.2SDIO AHB接口 33619.4卡功能描述33619.4.1卡识别模式 33619.4.2卡复位33619.4.3操作电压范围确认 33719.4.4卡识别过程 33719.4.5写数据块 33819.4.6读数据块 33819.4.7数据流操作,数据流写入和数据流读出(只适用于多媒体卡) 33819.4.8擦除:成组擦除和扇区擦除 33919.4.9宽总线选择和解除选择 34019.4.10保护管理 34019.4.11卡状态寄存器 34219.4.12SD状态寄存器 34419.4.13SD I/O模式 34719.4.14命令与响应 34819.5响应格式35019.5.1R1(普通响应命令) 35119.5.2R1b 35119.5.3R2(CID、CSD寄存器) 35119.5.4R3(OCR寄存器) 35119.5.5R4(快速I/O) 35219.5.6R4b 35219.5.7R5(中断请求) 35219.5.8R6(中断请求) 35319.6SDIO I/O卡特定的操作 35319.6.1使用SDIO_D2信号线的SDIO I/O读等待操作 35319.6.2使用停止SDIO_CK的SDIO读等待操作 35319.6.3SDIO暂停/恢复操作 35419.6.4SDIO中断 35419.7CE-ATA特定操作 35419.7.1命令完成指示关闭 35419.7.2命令完成指示使能 35419.7.3CE-ATA中断 35419.7.4中止CMD61 35419.8硬件流控制35419.9SDIO寄存器35519.9.1SDIO电源控制寄存器(SDIO_POWER) 35519.9.2SDIO时钟控制寄存器(SDIO_CLKCR) 35519.9.3SDIO参数寄存器(SDIO_ARG) 35619.9.4SDIO命令寄存器(SDIO_CMD) 35619.9.5SDIO命令响应寄存器(SDIO_RESPCMD) 35719.9.6SDIO响应1..4寄存器(SDIO_RESPx) 35719.9.7SDIO数据定时器寄存器(SDIO_DTIMER) 35819.9.8SDIO数据长度寄存器(SDIO_DLEN) 35819.9.9SDIO数据控制寄存器(SDIO_DCTRL) 35819.9.10SDIO数据计数器寄存器(SDIO_DCOUNT) 36019.9.11SDIO状态寄存器(SDIO_STA) 36019.9.12SDIO清除中断寄存器(SDIO_ICR) 36119.9.13SDIO中断屏蔽寄存器(SDIO_MASK) 36219.9.14SDIO FIFO计数器寄存器(SDIO_FIFOCNT) 36419.9.15SDIO数据FIFO寄存器(SDIO_FIFO) 36419.9.16SDIO寄存器映像 365 20USB全速设备接口(USB) 36620.1USB简介36620.2USB主要特征36620.3USB功能描述36720.3.1USB功能模块描述 36820.4编程中需要考虑的问题 36920.4.1通用USB设备编程 36920.4.2系统复位和上电复位 36920.4.3双缓冲端点 37220.4.4同步传输 37320.4.5挂起/恢复事件 37420.5USB寄存器描述 37520.5.1通用寄存器 37520.5.2端点寄存器 38020.5.3缓冲区描述表 38220.5.4USB寄存器映像 385 21控制器局域网(bxCAN) 38721.1bxCAN简介38721.2bxCAN主要特点 38721.2.1总体描述 38821.3bxCAN工作模式 38921.3.1初始化模式 39021.3.2正常模式 39021.3.3睡眠模式(低功耗) 39021.3.4测试模式 39021.3.5静默模式 39021.3.6环回模式 39121.3.7环回静默模式 39121.4bxCAN功能描述 39221.4.1发送处理 39221.4.2时间触发通信模式 39321.4.3接收管理 39321.4.4标识符过滤 39521.4.5报文存储 39821.4.6出错管理 39921.4.7位时间特性 40021.5bxCAN中断40221.6CAN 寄存器描述 40321.6.1寄存器访问保护 40321.6.2控制和状态寄存器 40321.6.3邮箱寄存器 41121.6.4CAN过滤器寄存器 41521.6.5bxCAN寄存器列表 419 22串行外设接口(SPI) 42222.1SPI简介42222.2SPI和I2S主要特征 42222.2.1SPI特征42222.2.2I2S功能42322.3SPI功能描述42422.3.1概述42422.3.2SPI从模式 42622.3.3SPI主模式 42722.3.4单工通信 42822.3.5状态标志 42822.3.6CRC计算 42922.3.7利用DMA的SPI通信 42922.3.8错误标志 43022.3.9关闭SPI 43022.3.10SPI中断43022.4I2S功能描述43122.4.1I2S功能描述 43122.4.2支持的音频协议 43222.4.3时钟发生器 43722.4.4I2S主模式 43822.4.5I2S从模式 43922.4.6状态标志位 44022.4.7错误标志位 44122.4.8I2S中断44122.4.9DMA功能 44122.5SPI和I2S寄存器描述 44222.5.1SPI控制寄存器1(SPI_CR1)(I2S模式下不使用) 44222.5.2SPI控制寄存器2(SPI_CR2) 44322.5.3SPI 状态寄存器(SPI_SR) 44422.5.4SPI 数据寄存器(SPI_DR) 44522.5.5SPI CRC多项式寄存器(SPI_CRCPR) 44622.5.6SPI Rx CRC寄存器(SPI_RXCRCR) 44622.5.7SPI Tx CRC寄存器(SPI_TXCRCR) 44622.5.8SPI_I2S配置寄存器(SPI_I2S_CFGR) 44722.5.9SPI_I2S预分频寄存器(SPI_I2SPR) 44822.5.10SPI 寄存器地址映象 449 23I2C接口45023.1I2C简介45023.2I2C主要特点45023.3I2C功能描述45123.3.1模式选择 45123.3.2I2C从模式 45223.3.3I2C主模式 45423.3.4错误条件 45623.3.5SDA/SCL线控制 45723.3.6SMBus 45723.3.7DMA请求 45923.3.8包错误校验(PEC) 46023.4I2C中断请求46123.5I2C调试模式46223.6I2C寄存器描述46223.6.1控制寄存器1(I2C_CR1) 46223.6.2控制寄存器2(I2C_CR2) 46423.6.3自身地址寄存器1(I2C_OAR1) 46523.6.4自身地址寄存器2(I2C_OAR2) 46523.6.5数据寄存器(I2C_DR) 46523.6.6状态寄存器1(I2C_SR1) 46623.6.7状态寄存器2 (I2C_SR2) 46823.6.8时钟控制寄存器(I2C_CCR) 46923.6.9TRISE寄存器(I2C_TRISE) 47023.6.10I2C寄存器地址映象 471 24通用同步异步收发器(USART) 47224.1USART介绍47224.2USART主要特性 47224.3USART功能概述 47324.3.1USART 特性描述 47424.3.2发送器47524.3.3接收器47724.3.4分数波特率的产生 48024.3.5多处理器通信 48124.3.6校验控制 48224.3.7LIN(局域互联网)模式 48324.3.8USART 同步模式 48524.3.9单线半双工通信 48724.3.10智能卡48724.3.11IrDA SIR ENDEC 功能块 48824.3.12利用DMA连续通信 49024.3.13硬件流控制 49124.4USART中断请求 49224.5USART模式配置 49324.6USART寄存器描述 49424.6.1状态寄存器(USART_SR) 49424.6.2数据寄存器(USART_DR) 49524.6.3波特比率寄存器(USART_BRR) 49624.6.4控制寄存器1(USART_CR1) 49624.6.5控制寄存器2(USART_CR2) 49824.6.6控制寄存器3(USART_CR3) 49924.6.7保护时间和预分频寄存器(USART_GTPR) 50124.6.8USART寄存器地址映象 502 25器件电子签名 50325.1存储器容量寄存器 50325.1.1闪存容量寄存器 50325.2产品唯一身份标识寄存器(96位) 503 26调试支持(DBG) 50526.1概况50526.2ARM参考文献50626.3SWJ调试端口(serial wire and JTAG) 50626.3.1JTAG-DP和SW-DP切换的机制 50726.4引脚分布和调试端口脚 50726.4.1SWJ调试端口脚 50726.4.2灵活的SWJ-DP脚分配 50726.4.3JTAG脚上的内部上拉和下拉 50826.4.4利用串行接口并释放不用的调试脚作为普通I/O口 50826.5STM32F10xxx JTAG TAP 连接 50926.6ID 代码和锁定机制 50926.6.1微控制器设备ID编码 50926.6.2边界扫描TAP 51026.6.3Cortex-M3 TAP 51026.6.4Cortex-M3 JEDEC-106 ID代码 51126.7JTAG调试端口51126.8SW调试端口51226.8.1SW协议介绍 51226.8.2SW协议序列 51226.8.3SW-DP状态机(Reset, idle states, ID code) 51326.8.4DP和AP读/写访问 51326.8.5SW-DP寄存器 51326.8.6SW-AP寄存器 514 26.9对于JTAG-DP或SWDP都有效的AHB-AP (AHB 访问端口) 514 26.10内核调试515 26.11调试器主机在系统复位下的连接能力 515 26.12FPB (Flash patch breakpoint) 515 26.13DWT(data watchpoint trigger) 516 26.14ITM (instrumentation trace macrocell) 51626.14.1概述51626.14.2时间戳包,同步和溢出包 516 26.15MCU调试模块(MCUDBG) 51726.15.1低功耗模式的调试支持 51726.15.2支持定时器、看门狗、bxCAN和I2C的调试 51826.15.3调试MCU配置寄存器 518 26.16TPIU (trace port interface unit) 52026.16.1导言52026.16.2跟踪引脚分配 52026.16.3TPUI格式器 52226.16.4TPUI帧异步包 52226.16.5同步帧包的发送 52226.16.6同步模式 52226.16.7异步模式 52326.16.8TRACECLKIN在STM32F10xxx内部的连接 52326.16.9TPIU寄存器 52326.16.10配置的例子 524 26.17DBG寄存器地址映象 5241 文中的缩写1.1 寄存器描述表中使用的缩写列表在对寄存器的描述中使用了下列缩写:read / write (rw) 软件能读写此位。

stm32f103中文手册第一章综述1.1 STM32F103系列微控制器概述1.2 STM32F103系列微控制器特性1.3 STM32F103系列微控制器产品线第二章存储器2.1 存储器映射2.2 Flash存储器2.3 系统存储器2.4 备份寄存器2.5 静态随机存取存储器(SRAM)第三章外设3.1 复位和时钟控制(RCC)3.2 独立看门狗(IWDG)3.3 窗口看门狗(WWDG)3.4 嵌套向量中断控制器(NVIC)3.5 系统定时器(SysTick)...第一章综述1.1 STM32F103系列微控制器概述STM32F103系列微控制器是基于ARM® Cortex®-M3内核的高性能、低功耗、增强型单片机。

它们提供了从64KB到512KB Flash存储器和从20KB到64KBSRAM存储器的不同容量选择。

它们还集成了丰富的外设资源,包括USB 、CAN、11个定时器、3个ADC、13个通讯接口等。

STM32F103系列微控制器采用了先进的90nmNVM工艺技术,具有出色的电源效率。

它们支持多种低功耗模式,包括停机模式、待机模式、睡眠模式和停止模式。

它们还支持动态电压调节和动态频率调节,以进一步降低功耗。

STM32F103系列微控制器具有高度灵活性和可扩展性。

它们支持多种封装类型,从36引脚到144引脚不等。

它们还支持多种内部和外部时钟源,包括高速内部振荡器(HSI)、低速内部振荡器(LSI)、高速外部振荡器(HSE)、低速外部振荡器(LSE)和相位锁定环(PLL)。

它们还支持多种外部存储器接口,包括NOR Flash、SRAM、NAND Flash、SDIO等。

1.2 STM32F103系列微控制器特性---特性 ---描述 -------:-----:---------内核 ---ARM® 32位 Cortex®-M3CPU,最高72MHz运行频率,单周期乘法和硬件除法,嵌套向量中断控制器(NVIC)和系统定时器(SysTick) -------存储器 ---64KB到512KB Flash存储器,20KB到64KBSRAM存储器,512字节备份寄存器,可选的2KB系统存储器 -------电源管理 ---1.65V到3.6V电源电压范围,7uA待机模式,36uA停机模式,动态电压调节和动态频率调节 -------外设 ---USB 2.0全速设备接口,CAN2.0B接口,11个通用定时器,3个高级定时器,3个12位ADC,2个DAC,13个通讯接口(3个USART、4个UART、2个I2C、3个SPI、1个I2S),CR C计算单元,96位唯一ID -------调试和编程 ---SWD和JTAG接口,支持串行线调试(SWD)和串行线跟踪(SWO),支持Flash编程和调试 -------封装 ---36引脚到144引脚不同封装类型 ----1.3 STM32F103系列微控制器产品线STM32F103x8/xB:中等容量增强型单片机,具有64KB或128KB Flash存储器和20KBSRAM存储器。

STM32F103VET6参考《STM32F10x-英文参考手册》《零死角玩转STM32—F103指南者》秉火视频教程简介•Analog to Digital(模拟数字转换器)•三个独立ADC通道(STM32F103系列均有)•精度为12位(STM32F103系列均有)•ADC1,ADC2有18个通道(16个为内部);ADC3有根据F103系列的引脚不同而变化,一般有8个外部通道功能框图Figure 2-1 电压输入范围Figure 2-2Figure 2-A指南者开发板中,VREF+与VREF-分别连接到了3V3和地输入通道Figure 2-3输入通道分为规则通道和注入通道规则通道:平时使用,正常转换通道(16)注入通道:在规则转换时插队(4)转换顺序•规则序列寄存器 SQR1.2.3•注入序列寄存器 JSQR•注入序列寄存器JSQR 只有一个,最多支持4 个通道,具体多少个由JSQR 的JL[2:0]决定。

如果JL 的值小于4 的话,则JSQR 跟SQR决定转换顺序的设置不一样,第一次转换的不是JSQR1[4:0],而是JCQRx[4:0] ,x = (4-JL),跟SQR 刚好相反。

如果JL=00(1 个转换),那么转换的顺序是从JSQR4[4:0]开始,而不是从JSQR1[4:0]开始,触发源•软件触发•外部事件触发转换时间Figure 2-4•ADCCLK最大为14MHZ;一般经过ADC预分频器6分频得12MHZ数据寄存器规则数据寄存器•DR•16位有效•两个16位•DMA•中断读取数据(少用)注入数据寄存器•JDR•16位有效中断•EOC——end of complete•JEOC•AWD 模拟看门狗事件。

新一代嵌入式微处理器STM32F103开发与应用一、本文概述随着科技的快速发展,嵌入式系统已成为现代社会不可或缺的一部分,广泛应用于智能设备、工业自动化、航空航天等众多领域。

STM32F103作为新一代嵌入式微处理器,凭借其高性能、低功耗、易于开发等优点,在众多微处理器中脱颖而出,成为众多工程师和开发者的首选。

本文将对STM32F103的开发与应用进行深入探讨,旨在帮助读者更好地理解和应用这一强大的微处理器。

本文首先将对STM32F103的基本特性进行概述,包括其架构、内核、外设接口等关键要素。

接着,文章将详细介绍STM32F103的开发环境搭建,包括所需的硬件和软件工具,以及具体的配置步骤。

在开发环境搭建完毕后,本文将通过实例演示,带领读者逐步掌握STM32F103的编程技巧和实际应用。

这些实例将覆盖STM32F103的基本功能,如GPIO控制、定时器使用、串口通信等,以及更高级的应用,如嵌入式操作系统移植、网络通信等。

本文还将对STM32F103在不同领域的应用案例进行分析,展示其在智能设备、工业自动化等领域的广泛应用。

通过这些案例,读者可以深入了解STM32F103在实际项目中的表现和应用价值。

本文将对STM32F103的未来发展趋势进行展望,探讨其在嵌入式领域的发展趋势和潜在应用。

本文旨在为广大嵌入式开发者提供一份全面、深入的STM32F103开发与应用指南,帮助读者更好地掌握这一强大的微处理器,推动嵌入式技术的发展和应用。

二、STM32F103微处理器基础STM32F103是STMicroelectronics公司推出的一款基于ARM Cortex-M3核心的高性能、低功耗、32位Flash嵌入式微处理器。

它继承了ARM Cortex-M3内核的低功耗、高性能和实时性强的特点,并在此基础上加入了众多的增强功能和外设接口,使得STM32F103在嵌入式系统设计中表现出色。

STM32F103采用了ARM Cortex-M3 32位RISC内核,支持Thumb-2指令集,提供了高性能的运算能力和紧凑的代码大小。