基于QuartusⅡ的多种EDA工具协同设计的研究

- 格式:pdf

- 大小:130.48 KB

- 文档页数:4

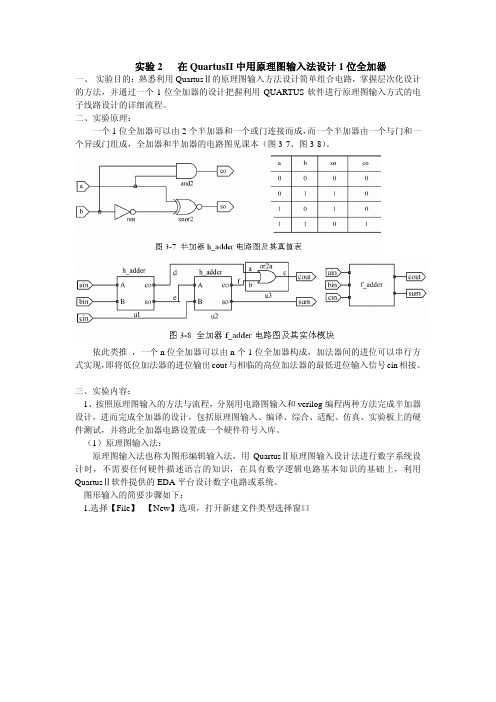

实验2 在QuartusII中用原理图输入法设计1位全加器一、实验目的:熟悉利用QuartusⅡ的原理图输入方法设计简单组合电路,掌握层次化设计的方法,并通过一个1位全加器的设计把握利用QUARTUS软件进行原理图输入方式的电子线路设计的详细流程。

二、实验原理:一个1位全加器可以由2个半加器和一个或门连接而成,而一个半加器由一个与门和一个异或门组成,全加器和半加器的电路图见课本(图3-7、图3-8)。

依此类推,一个n位全加器可以由n个1位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相临的高位加法器的最低进位输入信号cin相接。

三、实验内容:1、按照原理图输入的方法与流程,分别用电路图输入和verilog编程两种方法完成半加器设计,进而完成全加器的设计,包括原理图输入、编译、综合、适配、仿真、实验板上的硬件测试,并将此全加器电路设置成一个硬件符号入库。

(1)原理图输入法:原理图输入法也称为图形编辑输入法,用QuartusⅡ原理图输入设计法进行数字系统设计时,不需要任何硬件描述语言的知识,在具有数字逻辑电路基本知识的基础上,利用QuartusⅡ软件提供的EDA平台设计数字电路或系统。

图形输入的简要步骤如下:1.选择【File】--【New】选项,打开新建文件类型选择窗口2.选择Block Diagram/Schematic File打开图形编辑输入窗口3.在图形编辑窗口中任一个位置双击鼠标,或点击图中的“符号工具”按钮,或选择菜单Edit下的Insert Symbol命令,弹出下图所示的元件选择窗口:4. 通过选取元件,便可在工作区中完成电路的设计输入。

2、引脚约束:键1、键2、键3(PIO 0/1/2)分别接ain、bin、cin;发光管D2、D1(PIO9/8)分别接cout和sum。

ain:pin233bin:pin234cin:pin235sum:pin2cout:pin13、下载试验箱验证,模式开关选5。

quartus ii实验报告Quartus II实验报告引言:Quartus II是一款由Intel公司开发的集成电路设计软件,广泛应用于数字逻辑设计和FPGA开发领域。

本实验报告旨在介绍Quartus II的基本功能和使用方法,并通过实际案例展示其在数字逻辑设计中的应用。

一、Quartus II概述Quartus II是一款功能强大的集成电路设计软件,它提供了从设计到验证的全套工具。

Quartus II支持多种编程语言,如VHDL和Verilog,使得用户可以根据自己的需求选择适合的语言进行设计。

此外,Quartus II还提供了丰富的库和模块,方便用户进行快速原型开发和验证。

二、Quartus II的基本功能1. 设计入口Quartus II提供了多种设计入口,包括图形界面、命令行和脚本等方式。

用户可以根据自己的习惯和需求选择适合的方式进行设计。

图形界面友好易用,适合初学者;命令行和脚本则更适合有一定经验和需求的用户。

2. 设计编辑Quartus II提供了强大的设计编辑功能,用户可以在其中创建和编辑设计模块、信号线和电路连接等。

设计编辑界面清晰简洁,用户可以方便地进行设计布局和调整。

3. 仿真和验证Quartus II内置了仿真和验证工具,用户可以通过仿真来验证设计的正确性和性能。

仿真工具支持波形查看和信号分析等功能,帮助用户进行设计调试和优化。

4. 综合和优化Quartus II具备强大的综合和优化功能,可以将设计代码转化为硬件描述,进而生成逻辑电路。

综合工具会根据用户的约束条件和优化目标,自动进行逻辑优化和资源分配,提高设计的性能和效率。

5. 布局和布线Quartus II提供了先进的布局和布线工具,可以将逻辑电路映射到实际的FPGA芯片上。

布局工具可以根据用户的约束条件和性能要求,自动进行电路元件的位置分配;布线工具则负责将电路元件之间的连接线路进行规划和布线。

6. 下载和调试Quartus II支持将设计文件下载到目标FPGA芯片上,并提供了调试工具来验证和调整设计的正确性。

EDA 设计(Ⅱ)学号:姓名:院系:指导:谭雪琴时间:2011年4月8日目录1.引言 (03)2.正文 (03)2.1.设计要求 (03)2.2.整体电路工作原理 (04)2.3.子模块设计原理与仿真 (04)2.3.1.脉冲发生电路 (04)2.3.2.计时电路 (07)2.3.3.译码显示电路 (10)2.3.4.报时电路 (15)2.3.5.校时、保持以及清零电路 (16)2.3.6.总功能电路连接 (20)2.4.整体电路下载 (21)2.5.扩展闹铃功能设计 (21)2.5.1.闹铃时间设定功能 (21)2.5.2.闹铃显示功能 (22)2.5.3.闹铃响铃功能 (23)2.5.4.闹铃总电路连接 (24)3.结论 (25)4.致谢 (26)5.参考资料 (26)多功能数字钟设计(南京理工大学)摘要:本文详细介绍了多功能数字钟的工作原理及设计过程。

首先利用quartus2软件,采用模块化设计方法,分别设计分频器、模计数器、动态显示电路、清零校时电路和报时电路等功能模块,然后观察仿真波形,确认功能实现后进行封装与调用。

最后将各功能模块整合起来构成整体电路,仿真和调试通过后下载到EDA实验箱,观察实际运行结果。

此外,本文还描述了附加闹铃功能的设计过程,并记述了实验过程中出现的一些问题及解决方案,以及对这次设计的一些经验教训的反思。

关键词:数字钟;校时报时;闹铃;动态显示;消颤;仿真;下载1、引言该数字钟功能丰富、操作简单,可使人们方便的获取时间信息及相关提醒,在实际生活中广泛应用,具有显著的实用价值。

其构成虽较简单,但融合了组合逻辑电路和时序逻辑电路,包括了分频器、计数器、数据选择器、编码器译码器以及锁存器等几乎所有数字逻辑电路的所学内容,是理论联系实际,提高知识技能的绝佳途径。

2、正文2.1 设计要求利用quartus2软件设计一个数字钟,并下载到EDA实验系统中。

要求可以完成00:00:00到23:59:59的计时功能,并在控制电路的作用下具有保持、清零、快速校时、快速校分、整点报时(当时钟计到59’53”时开始报时,在59’53”, 59’55”,59’57”时报时频率为512HZ,59’59”时报时频率为1KHZ)等功能。

软件开发与设计SOFTWARE DEVELOPMENT AND DESIGNQuartusII在EDA技术中的应用程继航,黄飞,石静苑(空军航空大学,长春 130022)摘 要:简要介绍了电子设计自动化(EDA)技术的设计流程及其常用开发软件QuartusII的特点,并通过实例介绍了QuartusII在EDA技术中的应用。

关键词:EDA技术;QuartusII设计软件The application of QuartusII in the EDACHENG Jihang,HUANG Fei,SHI Jingyuan(Air Force Aviation University, Changchun 130022)Abstract: This text describe the design process of electronic design automation (EDA) and Characteristics of designsoftware QuartusII. In this paper, give examples that the application of the design software QuartusII in the EDA.Key words: EDA Technalogy; design software QuartusII1 前言电子设计自动化(Electronic Design Automation,EDA)技术是以微电子技术发展为物理层面,现代电子设计技术为灵魂,计算机软件技术为手段,最终形成集成电子系统或专用集成电路ASIC(Application Integrated Circuit)为目的的一门新兴技术。

简单地说,EDA技术可概括为以大规模可编程逻辑器件CPLD/FPGA为设计载体,通过硬件描述语言输入给相应开发软件,经过编译和仿真,最终下载到设计载体中,从而完成系统电路设计任务的一门新技术。

在集成电路设计领域中,各类微处理器已经成为了整个芯片系统的核心。

运算器作为其核心部件,得到广泛的发展。

与此同时,为了增加电子产品产出效率,降低制造成本,诸如Quartus II9.0等电子仿真软件相继出现,为产品开发提供了良好的开发平台。

本文根据运算器具有物美价廉、使用方便、功能性强等特点,分别对半加器、全加器、乘法器、除法器进行了仿真设计。

首先本文介绍了课题的背景、意义、发展现状及未来走向,并对研究内容及设计方案进行了简单介绍。

其次对设计环境QuartusⅡ平台及VHDL做了介绍。

之后对半加器、全加器、乘法器、除法器的设计进行了详细描述,包括工作原理、真值表及流程图,还把乘法器分成各个模块,并对各个模块进行了详细的介绍与设计分析。

随后对半加器、全加器、乘法器、除法器进行了编程、仿真以及在QuartusⅡ平台上对仿真结果进行验证。

从而做到了从理论到实践,学以致用。

关键词:运算器;QuartusⅡ;VHDLIn the field of integrated circuit design, all kinds of microprocessors has become the core of the whole chip system. Unit as its core component, is widely development.At the same time, in order to increase the electronic products output efficiency, reduce manufacturing cost, such as the QuartusII 9.0 electronic simulation software appeared, such as for product development provides a good development platform.Based on the arithmetic unit has the good and inexpensive, easy to use, functional characteristics, respectively, half adder, full adder, multiplier and divider design has carried on the simulation. First this article introduces the topic background, significance, status quo and future development, and research contents and the design scheme of a simple introduction. Secondly on the design environment QuartusII platform and VHDL is presented. After full adder and full adder, multiplier and divider design are described in detail, including the working principle, the truth table and flow chart, also the multiplier is divided into various modules, and each module are analyzed in detail and design. Then half adder, full adder, multiplier and divider for programming, simulation, and in the QuartusII platform of simulation results to validate. Thus did it from theory to practice, to practice.Keywords: Arithmetic unit;VHDL;QuartusII1 引言 (1)1.1 课题背景及意义 (1)1.2 课题的现状与发展 (1)1.3 研究内容与设计方案 (1)2 开发环境 (3)2.1 Quartus II平台介绍 (3)2.1.1 Quartus II简介 (3)2.1.2 Quartus II总体设计 (4)2.1.3 Quartus II总体仿真 (8)2.2 VHDL语言介绍 (9)2.2.1 VHDL语言概述 (9)2.2.2 VHDL语言介绍 (10)2.2.3 VHDL应用开发介绍 (12)3 基于Quartus II的半加、全加器的设计与实现 (13)3.1 基于Quartus II的半加器运算 (13)3.1.1 半加器的原理与真值表 (13)3.1.2 半加器的设计与实现 (13)3.2 基于Quartus II的全加器运算 (22)3.2.1 全加器的原理、真值表和原理图 (22)3.2.2全加器的设计与实现 (24)4 基于Quartus II的乘法、除法器的设计与实现 (25)4.1 基于Quartus II的乘法器运算 (25)4.1.1 乘法器的原理和流程图 (25)4.1.2 四位二进制加法器模块 (28)4.1.3 八位二进制加法器模块 (29)4.1.4 一位乘法器模块 (31)4.1.5 8位右移寄存器模块 (33)4.1.6 乘法器的其他模块 (34)4.2 基于Quartus II的除法器运算 (39)4.2.1 除法器的原理与流程图 (39)4.2.2 除法器的设计与实现 (40)结论 (43)致谢 (44)参考文献 (45)附录A 英语原文 (46)附录B 汉语翻译 (56)1 引言1.1 课题背景及意义Quartus II具有界面友好、操作简单的特点,作为高效的EDA设计工具集合,与第三方软件扬长补短,使软件功能越来越强大,为用户提供了更加丰富的Quartus II平台。

学号~~~~~~~~~~~~~~密级公开北京师范大学本科毕业论文基于QuartusII的四组智力抢答器的设计与仿真学院名称:电子工程学院专业名称:电子设计学生姓名:~~~指导教师:~~ 教授二○一三年五月郑重声明本人呈交的学位论文,是在导师的指导下,独立进行研究工作所取得的成果,所有数据、图片资料真实可靠。

尽我所知,除文中已经注明引用的内容外,本学位论文的研究成果不包含他人享有著作权的内容。

对本论文所涉及的研究工作做出贡献的其他个人和集体,均已在文中以明确的方式标明。

本学位论文的知识产权归属于培养单位。

本人签名:日期:摘要本设计实现了四组智力抢答器的逻辑功能,主要由抢答鉴别模块、计分模块、7段译码显示模块、顶层模块等部分组成。

采用VHDL语言编写代码,并在Quartus II6.0环境进行编译仿真,通过分析仿真结果,可以很好的完成抢答器的预定功能和要求。

关键词:VHDL;Quartus II6.0;抢答器ABSTRACTThis design implements the logic function of the four-group intelligence Responder. It is mainly composed of the identification module of answering machine, scoring module, 7-segment decode display module, top-level module and so on. The whole code is described in the VHDL Hardware Description Language, and carried on the compiling and testing in the Quartus||6.0. By analyzing the results of simulation ,it shows that the answering machine has meet the expected functions and requirements . Key words: VHDL;Quartus II6.0;Responder目录第1章绪论 (1)1.1研究背景 (1)1.2研究目的 (1)第2章 EDA简介 (3)2.1 EDA技术介绍 (3)2.2 VHDL简介 (3)2.3 Quartus II简介 (4)2.4 可编译逻辑器件 FPGA/CPLD简介 (5)第3章四组智力抢答器的设计 (6)3.1系统设计要求 (6)3.2顶层模块的设计 (6)3.3抢答判别模块的设计 (10)3.4计分模块的设计 (13)3.5 7段LED显示驱动模块的设计 (14)第4章四组智力抢答器的仿真结果 (16)4.1顶层模块的仿真结果 (16)4.2 抢答判别模块的仿真结果 (16)4.3 计分模块的仿真结果 (17)4.4 7段LED显示驱动模块的仿真结果 (17)总结 (19)参考文献 (20)致谢 (21)附录 (22)第1章绪论1.1研究背景人类社会进入到高度发达的信息化社会,信息社会的发展离不开电子产品的进步。

Quartus II 9.0软件的使用1.实验目的和要求本实验为验证性实验,其目的是熟悉Quartus II 9.0软件的使用,学会利用Quartus II 9.0软件来完成整个EDA开发的流程。

2.实验原理利用VHDL完成电路设计后,必须借助EDA工具中的综合器、适配器、时序仿真器和编程器等工具进行相应的处理后,才能使此项设计在FPGA上完成硬件实现,并得到硬件测试,从而使VHDL设计得到最终的验证。

Quartus II是Altera提供的FPGA/CPLD开发集成环境,包括模块化的编译器,能满足各种特定设计的需要,同时也支持第三方的仿真工具。

3.主要仪器设备(实验用的软硬件环境)实验的硬件环境是:微机一台GW48 EDA实验开发系统一套电源线一根十芯JTAG口线一根USB下载线一根USB下载器一个实验的软件环境是:Quartus II 9.0软件4.操作方法与实验步骤利用Quartus II 9.0软件实现EDA的基本设计流程:创建工程、编辑文本输入设计文件、编译前设置、全程编译、功能仿真。

利用Quartus II 9.0软件实现引脚锁定和编译文件下载。

利用Quartus II 9.0软件实现原理图输入设计文件的编辑和产生相应的原理图符号元件。

5.实验内容及实验数据记录1)新建工程(文本输入法)2)新建工程(原理图输入法)3)编译工程选择如上菜单栏中的选项或者可通过Processing->Start Complacation进行编译工程。

4)时序仿真选择如上菜单栏中的选项或者可通过Processing->Start Complacation进行编译工程。

5)下载程序Tools-〉Programmer6.实验数据处理与分析1)任何一项设计都是一项工程(实验三中半加器、一位全加器以及8位全加器的设计都应该新建工程,不可在同一个工程中进行设计),不同的设计项目最好放在不同的文件夹中,而同一工程的所有文件都必须放在同一文件夹中。

实验一:应用QuartusⅡ完成基本组合电路设计一、实验目的1.了解并熟悉世界最大的可编程逻辑器件供应商之一—Altera的EDA集成开发工具QuartusII。

2.熟悉杭州康芯电子有限公司的GW48 系列SOPC/EDA 实验开发系统(GW48-PK2/CK)结构与使用方法。

3.通过2选1数据选择器的设计与实现来掌握QuartusII的文本输入法设计的操作步骤。

4、进一步熟悉QuartusⅡ的VHDL 文本设计流程全过程,学习多层次组合电路的设计、仿真和硬件测试。

二、实验内容1、使用QuartusII6.0来完成2选1数据选择器的文本输入、编译综合、仿真测试、引脚锁定及下载测试。

(可编程目标芯片见实验箱上的芯片,可能是Altera的ACEX1K(ACEX)系列中的EP1K30TC144-3)三、实验程序程序一:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX21A ISPORT(a,b,s:IN STD_LOGIC;y:OUT STD_LOGIC);END ENTITY MUX21A;ARCHITECTURE one OF MUX21A ISBEGINPROCESS(a,b,s) BEGINIF s='0' THEN Y<=a;ELSE y<=b;END IF;END PROCESS;END ARCHITECTURE one;程序二:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux22a ISPORT(a1,a2,a3,s0,s1:IN STD_LOGIC;outy:OUT STD_LOGIC); END ENTITY mux22a; ARCHITECTURE one OF mux22a IS SIGNAL y:STD_LOGIC;BEGINPROCESS(s0,a1,a2,a3) BEGINCASE s0 ISWHEN'0' => y <= a2;WHEN'1' => y <= a1;WHEN OTHERS=>NULL;END CASE;END PROCESS;PROCESS(s1,a1,a2,a3,y) BEGINCASE s1 ISWHEN'0' => outy <= a1;WHEN'1' => outy <= y;WHEN OTHERS=>NULL;END CASE;END PROCESS;END ARCHITECTURE one;四、实验仿真结果程序一:程序二:五、心得①在做实验之前要熟悉怎样创建工程,熟悉各个操作步骤,才能顺利,有效的完成实验。

一 用译码器74138和与非门实现下述表达式的逻辑功能。

要求,在QUARTUS Ⅱ软件中,按照基于FPGA 的EDA 设计流程来完成设计过程,包括创建工程、原理图输入、全程编译、时序仿真、波形仿真、引脚锁定、编程下载等过程,完成硬件测试。

1()(1,3,5,6,7)F A B C m =∑、、 2()(3,6,7)F A B C m =∑、、二 用两片7485设计一个8位比较器。

按照下图所示的电路,用两片4位二进制数制比较器7485串联扩展为8位比较器。

使用QUARTUS Ⅱ完成全部设计和测试,包括创建工程、编辑电路图、全程编译、时序仿真及说明此电路的功能、引脚锁定、编程下载,并进行硬件测试。

三 设计8位十进制数动态扫描显示控制电路。

AB C DS0S1S21 根据电路图,利用QUARTUSⅡ,用7448和74138宏功能元件设计实现8位十进制数动态扫描显示控制电路,并在实验系统上控制七段数码管。

位选信号S2、S1、S0可以用三个键控信号手动控制。

给出时序仿真波形并说明之、引脚锁定编译、编程下载于FPGA中进行硬件测试。

2 给出真值表,以上所有控制电路用同一CASE语句表达出来,然后硬件实现。

四设计一个十六进制七段显示译码器。

用HDL的CASE语句设计一个可以控制显示共阴七段数码管的十六进制七段显示译码器。

首先给出此译码器的真值表,此译码器有4个输入端:D、C、B、A。

D是最高位,A 是最低位;输出有8位:p、g、f、e、d、c、b、a,其中p和a分别为最高和最低位,p控制小数点。

对于共阴控制,如果要显示‘A’,输入DCBA=1010;若小数点不亮,则输出pgfedcba=01110111=77H。

给出时序仿真波形并说明之、引脚锁定、编程下载于FPGA中,对共阴数码管进行硬件测试。

五设计一个5人表决器。

1 用CASE语句设计一个5人表决电路,参加表决者5人,同意为1,不同意为0,同意者过半则表决通过,绿指示灯亮;表决不通过则红指示灯亮。

《FPGA系统设计》实验报告》QuartusII软件入门及组合逻辑电路设计实验

一.实验目的

(1)熟悉QuartusII的原理图设计流程的全过程。

(2)学习简单组合电路的设计方法、输入步骤。

(3)掌握原理图层次化设计方法。

(4)学习EDA设计的仿真和硬件测试方法。

二.实验要求

十进制计数器的设计

设计含有时钟使能的两位十进制计数器,主要通过十进制计数器74160和其他辅助元件来完成,如图1.1所示为两位十进制计数器。

图1.1 用74160设计一个有时钟使能的两位十进制计数器

三.实验操作步骤

(1). 新建项目工程:COUNTER

(2). 新建设计文件:File——New——Block Diagram/Schematic

(3). 工程的编译和综合:通过编译来检查设计文件是否存在错误。

(4). 管脚的分配与下载:在Location中分别将引脚分配芯片引脚并进行全编译,将USB-Blaster下载器与电脑相连,安装好驱动程序,将编译好的文件下载到芯片中,点击Programmer—Hardware Setup设置下载器的驱动程序,在Hardware Setup对话框中选择USB-Blaster0,点击start可完成程序下载,Progress中显示“100%successful”即为下载成功。

四.实验数据结果。

实验一:QuartusII软件的使用一、实验目的1、了解和学习Quartus II 7.2软件设计平台。

2、了解EDA的设计过程。

3、通过实例,学习和掌握Quartus II 7.2平台下的文本输入法。

4、学习和掌握D触发器的工作和设计原理。

5、初步掌握该实验的软件仿真过程。

二、实验仪器PC机,操作系统为Windows7/XP,本课程所用系统均为WindowsXP(下同),Quartus II 7.2设计平台。

三、实验步骤1、创建工程,在File菜单中选择New Project Wizard,弹出对话框如下图所示在这个窗口中第一行为工程保存路径,第二行为工程名,第三行为顶层文件实体名,和工程名一样。

2、新建设计文本文件,在file中选择new,出现如下对话框:选择VHDL File 点击OK。

3、文本输入,在文本中输入如下程序代码: library ieee;Use ieee.std_logic_1164.all;entity men isport(a,b:in std_logic;c:out std_logic);end men;architecture rt1 of men isbeginc<=a AND b;end rt1;然后保存到工程中,结果如下图所示:4、编译,如果有多个文件要把这个文件设为当前顶层实体,这样软件编译时就只编译这个文件。

点击projet->Set as Top-level EntityCtrl+Shift+J接下来进行编译,点击processing->Start Compilation ,见下图5、仿真验证,打开波形编辑器,新建一个波形仿真文件,如下图:然后选择菜单“View”→“Utility”→“Node Finder”出现如下对话框,在“Filter”中选择“Pins:all”,再点击“List”即在下边的“Node Found”框中出现本设计项目中所有端口引脚列表,从端口列表中选择所需要的,并逐个拖到波形编辑器窗口中。

Quartus2的原理图设计及应用1. 介绍Quartus2是一款由Intel(原Altera)公司开发的用于FPGA(现场可编程逻辑门阵列)设计的集成开发环境(IDE)。

它提供了丰富的工具和功能,使得原理图设计和FPGA应用开发变得更加易于实现。

本文将介绍Quartus2的原理图设计流程以及其在实际应用中的一些常见用途。

2. Quartus2的原理图设计流程Quartus2的原理图设计流程主要包括项目创建、电路图绘制、电路仿真和综合、布局与布线以及生成最终的比特流文件等步骤。

2.1 项目创建在Quartus2中创建一个项目是第一步,可以通过选择项目名称、项目文件夹路径等信息来进行项目设置。

在项目创建时,需要选择目标FPGA器件的型号和设计目标等参数,以便Quartus2能够进行正确的综合和布局布线。

2.2 电路图绘制在项目创建完成后,可以使用Quartus2提供的电路图设计工具来进行电路图绘制。

电路图设计工具提供了丰富的元件库和线连接工具,可根据需求绘制各种逻辑电路和模块。

2.3 电路仿真与综合完成电路图绘制后,可以使用Quartus2提供的仿真工具对设计的电路进行仿真,并验证其功能和性能。

通过仿真结果,可以进一步调整和优化电路设计。

在电路仿真验证通过后,可以进行综合操作,将电路转化为FPGA的可编程逻辑。

Quartus2的综合工具会根据目标FPGA器件的特性和约束,生成逻辑元件的门级描述。

2.4 布局与布线综合完成后,需要进行布局和布线,将逻辑元件映射到FPGA的实际物理位置上,并通过连线完成逻辑之间的连接。

Quartus2的布局布线工具会根据目标FPGA 器件的布局规则和约束,自动完成布线。

2.5 生成比特流文件布局布线完成后,最后一步是生成最终的比特流文件(bitstream),该文件包含了FPGA的配置信息。

生成比特流文件后,可以通过下载到目标FPGA器件上进行验证和调试。

3. Quartus2在实际应用中的常见用途3.1 数字逻辑设计Quartus2广泛应用于数字逻辑设计领域,可用于设计各种逻辑电路,如加法器、多路选择器、寄存器等。

《EDA技术及应用》QuartusII 原理图设计实验

课程名称: EDA技术及应用实验类型:设计性

实验项目名称: QuartusII 原理图设计

一、实验目的和要求

1.学习EDA集成工具软件Quartus II的使用;

2.2. 熟悉基于PLD的EDA设计流程;

3.3. 学会使用原理图设计半加器、全加器电路;

4.4. 掌握对设计进行综合、仿真、指定引脚和配置下载的方法。

二、实验内容和原理

三、实验步骤及结果

半加器原理图及编译结果半加器波形

半加器原理图及编译结果

全加器波形

四、讨论和心得

在这次实验中,要求使用原理图设计半加器、全加器电路,建立原理图,在图中加入输入、输出、与门、异或门等来搭建电路是实现半加器、全加器的功能。

通过这次实验,让我学会了如何使用原理图来设计半加器和全加器,如何生成半加器的原理图符号,并在全加器的原理图中使用,同时创建波形图,来进行功能仿真和时序仿真,观察波形来看是否正确。

专业班级:学号:姓名:EDA 技术实验报告实验项目名称:应用QuartusⅡ完成基本组合电路设计实验日期:2012.05.21 实验成绩:实验评定标准:一、实验目的熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

二、实验器材FPGA实验箱、PC机、QuartusⅡ软件三、实验内容(实验过程)实验内容1:首先利用QuartusⅡ完成2选1多路选择器的文本编辑输入(mux21a.vhd)和仿真测试等步骤,给出仿真波形图。

最后在实验系统上进行硬件测试,验证本项设计的功能。

实验内容2:将此多路选择器看成是一个元件mux21a,利用元件例化语句描述此程序,并将此文件放在同一目录中。

对此顶层文件进行编译、综合、仿真。

并对其仿真波形作出分析说明。

实验内容 3:引脚锁定以及硬件下载测试。

若选择目标器件是EP1K30,建议选试验电路模式5,用键1控制s0,用键2控制s1;a3、a2、a1分别接clock5、clock0和clock2;输出信号outy仍接扬声器speaker。

四、实验程序(1)二选一选择器的实验程序library ieee;use ieee.std_logic_1164.all;entity mux31a isport (a1,a2,a3,s0,s1:in bit;outy:out bit);end mux31a;architecture one of mux31a iscomponent mux21aport(a,b,s:in bit;y:out bit);end component;signal tmp:bit;beginu1:mux21a port map(a=>a2,b=>a3,s=>s0,y=>tmp); u2:mux21a port map(a=>a1,b=>tmp,s=>s1,y=>outy); end one;(2)三选一选择器的实验程序library ieee;use ieee.std_logic_1164.all;entity mux21a isport (a,b,s:in bit;y:out bit);end mux21a;architecture one of mux21a isbeginprocess (a,b,s)beginif s ='0' then y<=a; else y<=b;end if;end process;end one;五、实验仿真、结果及分析<一>试验仿真:(1)书中仿真图双2选择器如图。

基于QuartusII的多种EDA工具协同设计的研究王美妮(大连水产学院信息工程学院)摘要:在FPGA开发的各个阶段,研发者为我们提供了很多优秀的EDA工具。

如何充分利用各种工具的特点,并规划好各种工具的协同使用,对FPGA开发极其重要。

@文将通过开发实例来介绍基于多种EDA工具——QllartusH、FPGACompilerll、Modelsim的FPGA协同设计。

、/关键词:QuartusII;EDA;协同设计0引言EDA技术在当今迅猛发展,同时各种EDA软件也如雨后春笋股呈现在用户面前。

它们一般分为两种:一种是专业的芯片制造商为推广自己的芯片而开发的专业EDA软件,如Altera公司推出的MAX+PLUSⅡ就在其列萁他如:ispDesigoEXPERT、Q12al伽¥Ⅱ;另—种是EDA软件商提供的第三方软件,如知名的Synplify、Synopsys、Viewlogic、Cadence等,这种可以支持大部分芯片公司的PLD器件。

1FPGA的开发流程及实例目前在FPGA开发方面的EDA工具尤其繁多,各自侧重点不同,性能也不一样。

在当今变化的市场环境中,产品是否便予现场升级,是否便于灵活使用成为产品能否进入市场的关键因素。

为了加速FPGA的开发,选择并协调好各种EDA工具显得非常重要。

本文以Altera公司的FPGA为目标器件,通过开发实椤|I介绍FPGA开发的完整的流程及开发过程中使用到的开发工具,包括QuartuslI等EDA设计软件。

由于FPGA具有高速陛、高可靠性、开发周期短的特点,并可以根据现场的需要编程,因而具有极大的方便性,利于研究和广泛开发。

FPGA的开发分为没汁输入、功能仿真、设计综合、前仿真、布局布线、时序仿真、时序分析和编程下载几个步骤。

通过不断研究,分析的实例是‘嘲匾序选择和奇偶检验的串并数据转换接口”。

接口电路可以实现数据的串并转换,并根据控制信号确定输出的并行数据的顺序,以及输出奇偶检验位。

开发实例是用来说明FPGA的开发流程和各种EDA工具的协同设计.因此这里的描述重点并在设计本身。

开发实例使用的目标器件是Altera公司FLEKIOK系列的EPFl0K20TCl44-4:开发软件有QuarmslJ20等。

MAX+PLUSⅡ是MultipleArmyMah-ixandProgrammableLogkUserSys_【emⅡ的英文缩写,它的中文全称是复阵列矩阵及可编程逻辑用户系统。

MAX+PLUSⅡ是Altera公司专为本公司生产的PLD的研制和应用而开发的软件.它随着器件的El益高度集成而迅速发展。

1988年,Altera公司推出了MAX系列器件和专门为开发这一系列器件的软件~A+PLUS.这就是MAX+PLUSⅡ的前身。

随着器件的发展,出现了第二代的开发软件一MAX+PLUS。

QuanusU是Altera公司的第四代可编程逻辑器件集成开发环境.提供从设计输入到器件编程的全部功能。

QuartusII可以产生并识别EDIF网表文件、VHDL网表文件和VerilogI-IDL网表文件,为其他EDA工具提供了方便的接口,可以在QuartusⅡ集成环境中自动运行其他EDA工具。

(1)基于QuartusⅡ的FPGA的开发利用QuartusⅡ软件的开发流程可概括为以下几步:设计输入、设计编译、设计时序分析、设计仿真和器件编程。

・设计输人QuaItusⅡ软件在Flk菜单中提伏烈ewProjectWizard…”向导,Bl导设计者完成项目的刨建。

当设计者需要向项目中添加新的VHDL文件时,可以通过‘'New’’选项选择添加。

在这里我们创建项目‘'sxl”,编写‘'sxl.vM文件”,并将文件添加到项目中。

・设计编译Quartus1I编译器完成的功能有:检查设计错误、对逻辑进行综合、提取定时信息、在指定的Altera系列器件中进行适配分割,产生的输出文件将用于设计仿真、定时分析及器件编程。

●设计定时分析单击Froject菜单下的‘"rimingSettings…”选项,可以方便地完成时间参数的设定。

QuartosⅡ软件的时序分析功能在编译过程结束之后自动运行,并在编译报告的TmfmgAnalyses文件夹中显示。

・设计仿真在Processing菜单下选择“SimulateMode'’选项进入仿真模式,选择“SimulatorSettings…”对话框进行仿真设置。

在这里可以选择激勖文件、仿真模式(功能仿真或时序仿真)等,我们选择时序仿真,单-/t/‘'RunSimulator'’即开始仿真过程。

完成仿真后,我们可以通过时序仿真得到的波形判断系统设计是否达到要求。

●器件编程利用QmaXusⅡ软件给器件编程或配置时,首先需要打开编程器(在New菜单选项中选择打开ChainDescriptionF-ale),在编程器中可以进行编程模式设置(Mode下拉框)、硬件配置(ProgrammingHardware对话框)及编程文件选择(AddFile…按钮),将以上配置存盘产生cdf文件.其中存储了器件的名称、器件的设计及硬件设置等编翟}f富息。

当以上过程正确无误后,单击Start按钮即可开始对器件进行编程配置,(2)多种FA)A工具协同设计在FPGA设计的各个环节都有不同公司提供不同的EDA工具。

每个EDA工具都有自己的特点。

一般情况,由FPGA厂商提供的集成开发环境,如QuartusⅡ,在设计综合和设计仿真环节都不是非常优秀,因此一般都会提供第三方EDA工具的接口,让用户更方便地利用其他EDA工具。

在这方面,作为EDA集成开发环境的QuartusⅡ做得很好,不仅可以产生并识别EDIF网表文件、VFKDL网表文件和VefilogHDL网表文件,为其他EDA工具提供了方便的接口,而且可以在QuartusⅡ集成环境中自动运行其他EDA工具。

在PPGA的开发中,如果选用Altera公司器件的话,QuartusI]+FPGACompilerl/+Modelsim的工具组合是非常理想的选择。

●设计输入和综合在FPGACompiler/I中编辑“sxl.vhd”设计文件,并进行逻辑分析、综合和优化。

使用FPGACompiler1I综合时,我们能够设置综合的各种约束条件及优化重点,并选择不同厂家的器件。

在设计中,我们使用File菜单中的‘'DesignWizard'’,刨建项目,添加‘'sxl.vhd'’设计文件,并选择Altera公司FLEXl0K系列型号为EPFl0K20TCl44-4的器件为目标器件,在设置完成后.软件将自动开始综合和优化。

接着,在Synthesis菜单中选择‘'ExportNetlist..."打开导出网表的对话框。

在这里,可以设置和导出用于布局布线和前仿真的网表。

・功能仿真和前仿真使用Modelsim来进行功能仿真和前仿真。

在Modelsim进行功能仿真和前仿真的操作相同,只是输入的源程序不同罢了。

首先,我们要创建项目,选择对应的工作库,并将源文件加入到项目中。

接着选择Compile菜单中的‘'Compile…”对源文件进行编译,并编写测试台(可以是Macro文件,也可以是TestBench)。

最后,选择Simulate菜单中的‘'Simulate…”,在“Simulate’对话框中选择仿真需要实体,采用对应的测试台进行仿真,验证系统的逻辑功能及综合后的逻辑功能的正确性。

・布局布线和时序分析如果仿真结果没有问题,接下来的工作就是布局布线。

在布局布线之前,先对Quartus11的设计环境进行设置。

在P嘲ect菜单中选择‘'EDAToolSetting…”,打开EDA工具设置对话框。

在这里.我们能选择设计输入和综合工具,仿真工具,时序分析工具和版图级工具。

在对应的列表框中选择FPGACompiler11和Modelsim,注意仿真工具还要确定输出语言。

布局布线的输入源文件是经FPGACompilern综合、优化的输出文件。

在这里,FPGACompilerⅡ的输出文件‘‘sxl.甜f’即是Q∞a咖sⅡ布局布线的输入文件。

观察编译结果,发现时序分析中fa_la.x为204.08MHz,大于只采用QuartusII的fmaxl98.48Mnz。

就这个指标而言,采用FPGACompilerII综合、优化显然比采用QuartusII综合的效果要好。

・时序仿真进行时序仿真前,我们要确定已经获得针对特定FPGA输出网表文件,对应延时标准格式文件,以及厂家提供的与特定FPGA对应的库文件。

其中网表文件和标准延时格式文件是布局布线时产生的文件,而库文件则是由厂商提供,在Qllartus11软件的安装目录中可以找到。

本设计中,网表文件时“sxl.vho'’,延时标准格式文件是“sxlvhd.sdo”。

确定输人文件后,我们就能利用Modelsim进行时序仿真。

首先,建立项目,将上述文件添加到项目中去,并在“work")荤中新建“flexlok"’库。

接着,打开‘'compile'’对话框,先在‘'flexlok”库中编译文件‘'flexlokatoms.vhd”和‘'flexlok_componmets.vhd'’,再在“work'库中编译文件‘‘sxlvhd’。

编译完成之后。

我们就可以进行仿真了。

时序仿真与功能仿真和前仿真不同的是时乎仿囊需要加入廷口韩i准格式文件。

●编程下载利用集成开发环境QuartusⅡ中的编程工具,根据外围硬件电路的情况,设置编程模式,我们能很方便地完成编程下载工作,在硬件上对设计进行验证。

2结论在实际的FPGA的开发中,选用Quartos//+FPGACompilerll+Modelsim的EDA工具组合能很好地规划设计流程。

充分利用各EDA工具的优点,提高开发效率。

参考文献1王志华,邓仰东.数字集成系统的结构化设计与高层次综合一E京:清华大学出版社,20002薛宏熙,边十年,苏明.数字系统设计自动化.北京:清华大学出版社,19963赵雅兴.FPGA原理、设计与应用.天津:天津大学出版社.19994甘学温激字CMOSVLSt分析与设计基础.j0京:北京大学出版社,1999。