实时图像处理系统中EDMA实现数据搬移

- 格式:pdf

- 大小:184.49 KB

- 文档页数:4

摘要:增强型直接内存访问EDMA 是DSP 中一种高效的数据传输模块,能够不依赖CPU 进行数据的搬移,是在高速接口的使用中,十分重要的设备。

与之前的EDMA 模块相比,EDMA3在传输的同步方式、地址跳变、触发方式上都变得更为灵活。

在TI 的新型DSP 中,外设根据数据传输是否依赖EDMA3 而分成了2 种。

AIF 是一种高速接口模块,用于基带模块与射频模块间数据的传输。

该接口需要EDMA3 为其提供待传输的数据及搬移已接收的数据。

本文介绍了TI DSP 中的新一代EDMA3 模块的结构及参数配置,并结合多核心DSP TMS320C6474 中的高速AIF 接口,给出了一种EDMA3 的配置方式,为高速接口模块的使用,打下基础。

关键词:DSP;EDMA3;TMS320C6474;AIF0 引言TMS320C6474 是TI 推出的推出的一款高性能多核心DSP,基于65nm 工艺,在单一的裸片上集成了3 个1GHz 的C64x+内核,实现了3GHz 的原始DSP 性能。

显著降低了成本和功耗,并节省板级空间,使设计人员不必在电路板上集成多个数字信号处理器就能完成诸如同时执行多通道处理任务或同时执行多软件应用等高强度、高性能任务。

在TMS320C6474 DSP 中,C64x+核心、EDMA3 及片上外设是通过2 种交换网络互连的。

交换网络使主从器件间能够进行低延时的多路数据传输。

通过交换网络,CPU 能够向VCP2 发送数据而不影响RAC 与DDR2 内存控制器间的数据传输。

当对系统中的从设备进行访问时,交换网络能够对多个主设备进行仲裁。

片上外设可以分为两类:主设备及从设备。

主设备是指能够不使用EDMA3 就能在系统中进行读写操作的设备;从设备指必须使用EDMA3 才能进行数据传输的设备。

AIF 接口(Antenna Interface)是TMS320C6474 中的一种高速接口,是一种从设备,用于基带模块与射频模块间天线数据的传输,在使用OBSAI 协议时,单条链路速率最高可达4x 即3.072Gbps。

一、概述TMS320DM6437是TI 公司推出的新McBSP 实时音频数据传输的EDMA3配置张洲初 深圳市长龙铁路电子工程有限公司 518031一代DaVinci 数字媒体处理器,具有高达5600MIPS 的峰值速度,广泛用于数字媒体、网络媒体编/解码和视频图像处理等领域。

本文介绍McBSP 和EDMA3外设在音频处理应用中的设置方法。

二、硬件特性介绍2.1 多通道缓冲串口McBSPDM6437的McBSP 可以与工业标准的编解码器(C O D E C s )、模拟接口芯片(AICs )、串行连接A/D 和D/A 设备直接接口;能够直接同E1/T1帧设备、I2S 兼容设备、AC97兼容设备、SPI 接口设备等接口。

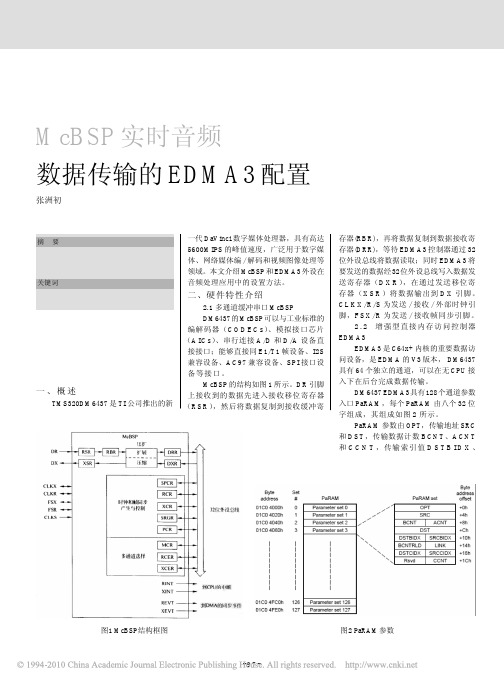

McBSP 的结构如图1所示。

DR 引脚上接收到的数据先进入接收移位寄存器(RS R ),然后将数据复制到接收缓冲寄存器(RBR),再将数据复制到数据接收寄存器(DRR),等待EDMA3控制器通过32位外设总线将数据读取;同时EDMA3将要发送的数据经32位外设总线写入数据发送寄存器(D X R ),在通过发送移位寄存器(X S R )将数据输出到D X 引脚。

C L K X /R /S 为发送/接收/外部时钟引脚,F S X /R 为发送/接收帧同步引脚。

2.2 增强型直接内存访问控制器EDMA3EDMA3是C64x+内核的重要数据访问设备,是EDMA 的V3版本, DM6437具有64个独立的通道,可以在无CPU 接入下在后台完成数据传输。

DM6437 EDMA3具有128个通道参数入口PaRAM ,每个PaRAM 由八个32位字组成,其组成如图2所示。

PaRAM 参数由OPT ,传输地址SRC 和DST ,传输数据计数BCNT 、ACNT 和C C N T ,传输索引值D S T B I D X 、图1 McBSP 结构框图图2 PaRAM 参数SRCBIDX 、DSTCIDX 和SRCCIDX ,传输BCNT 重调值BCNTRLD 和本通道的连接通道参数入口地址LINK 组成。

使用图像处理技术实现图片风格迁移的方法图片风格迁移是一种利用图像处理技术,将一幅图像的艺术风格应用于另一幅图像的方法。

通过这种技术,可以将一个图像的艺术风格转移到另一个图像上,实现有趣且独特的效果。

在本文中,将介绍使用图像处理技术实现图片风格迁移的方法。

了解一下图像风格迁移的基本原理。

图像风格迁移基于神经网络技术,通过训练一个深度神经网络模型,来捕捉图像的艺术风格。

这个模型通常由两部分组成:一个称为内容损失网络的子网络,用于提取图像的内容信息;另一个称为风格损失网络的子网络,用于提取图像的风格信息。

通过运用这两个子网络,可以将图像的内容和风格进行分离,并将风格应用于另一幅图像。

接下来,将详细介绍实现这一过程的具体方法。

需要准备训练数据。

为了训练风格迁移模型,需要大量的图像数据集。

数据集应包括具有不同风格和内容的图像。

可以从公开数据集中获取图像,或者根据自己的需要自行收集。

确保数据集包含足够多样化的图像,以便训练出具有泛化能力的模型。

接下来,搭建神经网络模型。

可以使用深度学习框架,如TensorFlow或PyTorch来构建模型。

模型通常由卷积神经网络(CNN)组成,其中包含用于提取图像特征的卷积层和池化层。

模型还应包括用于风格转移的损失函数,如内容损失和风格损失。

进行模型训练。

使用准备好的图像数据集和搭建好的模型,开始进行训练。

通过内容损失网络来提取图像的内容特征,并计算内容损失函数。

通过风格损失网络来提取图像的风格特征,并计算风格损失函数。

模型的目标是最小化总损失函数,从而使风格迁移效果更好。

训练过程可能需要较长时间,具体视数据集大小和模型复杂度而定。

训练完成后,可以应用模型进行图像风格迁移。

为了风格迁移,需要提供两幅输入图像:源图像(包含待转换的内容)和风格图像(包含风格转移的目标)。

将这两幅图像输入已经训练好的模型中,模型将自动提取源图像和风格图像的内容特征和风格特征,并将风格特征迁移到源图像上。

DSP(TMS320C6713)入门之旅四、edma的理解和使用EDMA的全称是:Enhanced Direct Memory Access(增强型dma),增强型直接内存存取(EDMA)是数字信号处理器(DSP)中用于快速数据交换的重要技术,具有独立于CPU的后台批量数据传输的能力,能够满足实时图像处理中高速数据传输的要求。

以TI公司的TMS320C6713型DSP为例,介绍EDMA控制器的特点。

结合实例给出EDMA在数据实时传输中的具体控制和实现方法。

实验结果表明,通过灵活控制EDMA不仅能够提高数据的传输效率,而且能够充分发挥:DSP的高速性能。

也就是在我们一般的dma的基础上做了一下加工以完成特定的功能。

比如我们dma传送数据一般是连续的一片数据块,但是我们想间隔着传送就不行了。

还有就是增强型的dma可以实现二维的传送和一个事件可以发起两次传送,这样就可以很好的服务我们的数据传送要求!如图EDMA结构图:可以看到我们配置自己的edma之后,就等待传送事件的到来,当传送事件到来的时候edma的控制器就接受到一个触发信号,就进入传送过程。

传送的规则定义在edma的每一个通道的参数设置里面,我们可以通过控制传送的参数来达到我们要传送的数据的控制的目的!传送参数表如图:第一个双字就是控制edma传送的规则,比如:一维单元同步,一维帧同步,二维等等。

这些控制属性得在这个域里面对其进行说明。

第二个双字就是告诉edma要传送数据的源地址,第三个双字的帧的数目和单元的数目,第四个双字就是告诉edma要传送数据的目的地址。

第五个双字告诉edma下一次触发时地址的偏移量的量。

第六个双字就是当前的单元传送完成之后的单元数目的重载值和是否edma是否需要要链接到下一个edma(注意:这儿是通道链接)我们先来理解几个概念:事件链接:实质就是想一个事件触发之后引起两次edma的搬移,当然这两次搬移不是同一个edma通道,如果是同一个edma通道,相当于同样的数据搬移两次,这样不仅没有意义,还会占用内部总线带宽,印象片内数据的流动的速度。

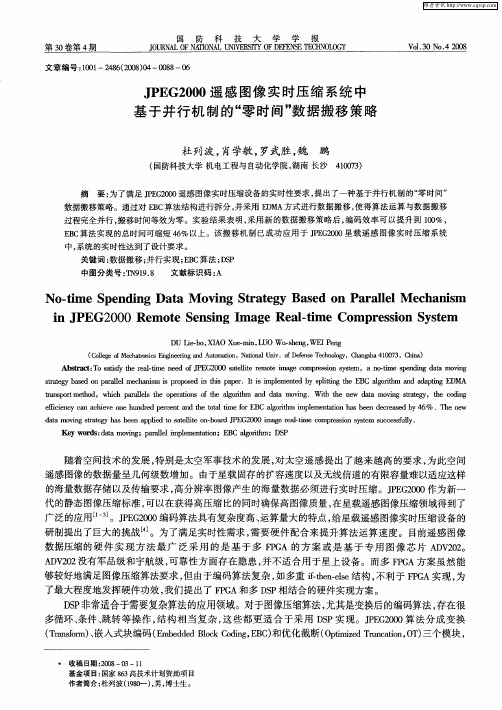

&Informationcommunications信息通信摘 要:TI公司的TMS320C64x DSP系列图像多媒体处理的DSP芯片强大的处理能力为H.264复杂编码算法的实时实现提供了可能。

作为对x.264编码器基于DM642平台优化编码效率的一个环节,文章在分析DM642中EDM A硬件结构以及参数空间的基础上讨论了基于该平台的EDMA技术的设计思路,并以一帧视频源图像由外存搬移到内存为例说明具体的实现方法,最后对完成EDMA通道的配置后,在实际编码过程中的EDMA数据传输过程进行描述。

关键字:H.264协议,视频编码,DM642,EDMA 中图分类号:TN919.81 文献标识码:A 文章编号:1673-1131(2009)01-024-03一、引言新一代视频压缩编码标准H.264以高压缩率,在低码率下具有更优良的图像主客观质量而成为目前视频应用领域的首选压缩方式。

但是由于它的算法复杂度较高。

所以在资源有限的嵌入式设备上实现实时编码需要相应硬件平台的支持,TI公司的TMS320C64x DSP系列芯片是专门用于图像多媒体处理的DSP芯片。

其强大的处理能力为H.264的实时编码提供了可能。

TMS320DM642是TI推出的一款面向数字多媒体应用的DSP,它在TI的C64x DSP内核的基础上进一步集成了完备的视频/音频输入/输出接口、以太网接口、PCI-66总线等片上外设,不仅能是用户很方便地对音频/视频等各种复杂地运算进行高速处理,还能方便、无缝的接口视频/音频编解码器件和以太网/PCI总线等数据传输接口。

本文所做的工作都是基于H.264算法标准的软件模型x.264。

x.264在程序结构和算法方面和JM模型相比,在不明显降低编码性能的前提下,x.264努力降低编码的计算复杂度。

二、基于DM642的EDMA 技术在基于DSP平台的视频应用中,庞大的数据量意味着要求DSP芯片具有大容量快速存储空间。

2005年第9期信息技术 中图分类号:TP317.4 文献标识码:A 文章编号:1009-2552(2005)09-0035-03实时图像处理系统中EDMA实现数据搬移李宝林,黄席樾,杨尚罡,刘 欣(重庆大学自动化学院导航制导研究室,重庆400044)摘 要:实时视频图像处理系统对图像处理的实时性要求很高,而且图像处理系统处理的数据量大。

为了解决上述问题,除了要有优化的算法之外,还要充分利用DSP处理器的一切可用的硬件资源。

本文阐述了基于TI公司T MS320C6713DSP的实时视频图像处理系统通过E DMA提高数据搬移速度的方法。

关键词:E DMA;数据搬移;CPU;DSP;图像处理Data transit achieved by E DMA in real-timeim age processing systemLI Bao2lin,HUANG X i2yue,Y ANG Shang2gang,LI U X in(N avigation and G uide Laboratory,College of Autom ation,Chongqing U niversity,Chongqing400044,China) Abstract:Real-time image processing system is strict with real-time capability,as well as,image pro2 cessing system has to process mass data.In order to s olve the problem,besides optimized alg orithm is needed, hardware res ources in DSP must be utilized fully.This article expounds that data transit speed is im proved by using E DMA in real-time image processing system based on T MS320C6713DSP which is made by TI corpo2 ration.K ey w ords:E DMA;data transit;CPU;DSP;image processing 实时图像处理系统处理的数据量大,要求数据的处理速度足够快,在有限时间内完成大量的数据运算,因此实时图像处理系统由高速的数字信号处理器及外设构成。

本系统采用的是TI公司高性能的T MS320C6713DSP,充分利用DSP的E DMA在片内高速存储区与片外低速存储区之间进行数据交换,以提高数据处理速度。

1 T MS320C6713及其EDMA简介T MS320C6713是TI公司在T MS320C6711的基础上新近推出的C6000系列新一代浮点DSP芯片,是目前为止C6000系列DSP芯片中性能较高的一种。

它可在255MH z的时钟频率下实现1800MIPSΠ1350MF LOPS的定点和浮点运算,外部存储器访问和片上外设的访问则完全通过E DMA来完成,极大程度上满足了图像压缩算法对计算速度的要求。

直接存储器访问(DMA)是C6000DSPs中一种重要的数据访问方式,它可以在没有CPU参与的情况下,由DMA控制器完成DSP存储空间内的数据搬移。

E DMA(Enhanced Direct Mem ory Access)是C671x 特有的访问方式。

E DMA控制器由事件和中断处理寄存器、事件编码器、参数RAM以及硬件地址产生几部分构成。

E DMA控制器和DMA控制器在结构上有很大不同,增强之处包括提供了16个通道、通道间的优先级可设置和支持不同机构数据传输的链接。

E DMA的参数RAM的容量为2K B,总共可以存放85组E DMA 传输控制参数。

多组参数还可以彼此连接起来,从而实现某些复杂数据流的传输。

图1给出了1组E DMA传输参数的内部结构。

事件寄存器控制对E DMA事件进行捕获。

一个事件相当于一个同步信号,由它触发一个E DMA通收稿日期:2005-03-08作者简介:李宝林(1979-),男,硕士研究生,研究方向为数字信号处理及其应用、模式识别。

图1 E DM A 的参数存储结构道开始数据传输。

如果有多个事件同时发生,则由事件编码器对它们进行分辨。

E DMA 的参数RAM中存放了有关的传输参数,这些参数会被送入地址发生器硬件,进而产生读写操作所需要的地址。

2 实时图像处理系统EDMA 实现数据搬移实时图像处理系统在两处数据传输中采用了E DMA 传输方式:外部S DRAM 到DSP 内部L2Cache的数据传输;McBSP0到显示终端的数据传输。

E D 2MA 实现数据搬移的工作流程如图2所示。

图2 E DM A 实现数据搬移的工作流程2.1 S DRAM 到L2Cache 的数据搬移搬移的数据为2维图像数据,图像来自视频采集板卡的数字图像(图像大小为320×240),该图像存储在S DRAM 中,因此DSP 是通过E DMA 从S DRAM 中将数据传输到DSP 内部存储器(L2Cache ),然后DSP 进行相应的图像处理。

因此E D 2MA 采用2-D 数据传输方式。

其中,S DRAM 地址空间分配在T MS320C6713E MIF 的CE0空间。

2.1.1 E DMA 的参数设置DSP 通过E DMA 实现从S DRAM 中将图像数据搬移到DSP 内部的L2Cache 中,而S DRAM 又被分配到DSP 的CE0空间。

因此,E DMA 参数中的可选参数OPT 设置为0x2DBD0001,源地址SCR 设置为0x80000000,帧Π阵列计数FRMC NT 设置为0x00EF ,数据单元计数E LEC NT 设置为0x0140,目的地址DST 设置为0x0001FFFF ,帧Π阵列索引FRMI DX 设置为0x0280,数据单元索引E LEI DX 设置为0x01DE (EIX =F ×S =0x00EF ×0x2=0x01DE ),数据计数重加载E LER LD 设置为0x0140,连接地址LI NK 设置为NU LL 。

2.1.2 同步传输模式E DMA 有两种同步传输模式(1)读Π写同步在2-D 传输中,E DMA 通道读Π写同步事件将触发1个阵列的传输。

(2)帧Π块同步在2-D 传输中,帧同步将导致整个数据块被传输。

这里的2-D 是指数据块的列和排。

图3给出了每一个同步事件E DMA 传输的一帧图像的示意,其中AIX (Array Index )是E DMA 参数中的阵列索引,每一个方块表示一个像素。

图3 一帧图像在帧Π块同步下的2-D E DM A 传输2.1.3 地址更新方式E DM A 的地址更新是指一个数据块的传输过程中源Π目的地址的修正(即修改源地址更新(S UM )和目的地址更新(DUM )字段),该操作由E DM A 控制器自动完成。

需要地址更新的地方有两个:E DM A 的通道参数内的SRC ΠDST 处和地址的产生Π传输逻辑处。

只要源Π目的任何一方是2-D 结构,并且传输是帧同步的(FS =1),则整个数据块都会在帧同步事件的控制下进行传输。

本系统中传输的数据块采用2-D 方式传输且为帧同步,所以E DMA 参数中的源—63—地址和目的地址均采用自动增址方式。

2.2 E DMA 控制器中断CPUT MS320C6713的16个E DMA 通道共享一个E D 2MA -I NT ,因此发生E DMA 中断时,CPU 的中断服务程序需要读CIPR 寄存器,判断是否有通道事件发生,以及是哪一个事件,然后转入相应的中断服务程序执行。

另外,ISR (中断服务寄存器)的CIPR (Chan 2nel Interrupt Pending Register )中的中断标志位必须手工清除,以保证可以捕获后续发生的中断。

E DMA 通道触发CPU 中断的参数设置由以下语句实现:(unsigned 3)01A0FFE8=0x00002000;(unsigned 3)01A00060=0x2DBD0001;上面的语句实质上是对E DMA 的寄存器进行了下面的设置:(1)CIER (Channel Interrupt Enable Register )寄存器中CIE13位设为1;(2)通道可选参数中T CI NT 设为1;(3)通道可选参数中的传输结束代码设为D 。

E DMA 结束后,E DMA 控制器根据传输结束代码(D )将通道未处理中断标志寄存器(CIPR )的CIPR13位置1。

如果对应的CIE13位使能,该通道将触发E DMA-I NT 中断,从而使DSP 转入到中断服务程序执行程序。

这样就实现了E DMA 从S DRAM 中将采集的图像数据搬移到L2Cache 中后产生E D 2MA -I NT ,通知CPU ,从而执行图像处理的中断服务子程序即图像处理程序。

2.3 E DMA 实现McBSP 与外设之间的数据传输处理完的图像数据通过McBSP0传输给显示终端,选用DSP 的E DMA 方式传输数据。

这里采用E DMA 的通道12和通道13实现DSP 的McBSP0与显示终端的数据实时传输。

2.3.1 乒-乓缓冲在CPU 读取一帧图像数据进行处理之前,E D 2MA 的通道13已经完成了将一帧图像数据从S DRAM 中传送到DSP 内部的L2Cache 中,而在E D 2MA 的通道12将处理完的这一帧图像图像出具通过McBSP0传输给显示终端之前,CPU 必须提供出处理后的图像数据。

如果在E DMA 向显示终端传输之前CPU 还没有处理完要传输的图像,就会使得传输的结果出现错误或者不可预料的结果。

为了避免这种情况的发生,T MS320C6713的E DMA 提供了一种叫做乒-乓的缓冲方式,这种缓冲方式类似打乒乓球,因之得名。

乒-乓缓冲方式如图4所示。

图4 M cBSP 数据的乒-乓缓冲 在乒-乓缓冲方式中,存在乒和乓两个用于输入输出数据流的缓冲区。

其中,E DMA 对乒缓冲区进行数据的输入和输出,CPU 处理乓缓冲区的数据。

当E DMA 将数据传输和CPU 将数据处理都完成之后,乒缓冲区的数据就和乓缓冲区的数据进行交换。

因此E DMA 输入的数据被CPU 处理之后交换到乒缓冲区(覆盖了乒缓冲区原来的数据),使得E DMA 传输给显示终端的数据就是CPU 处理后的正确的数据。

2.3.2 乒-乓缓冲的参数设置由乒-乓缓冲的原理,可知乒-乓缓冲必须分别对乒和乓缓冲区进行相应的参数设置。