Cyclone_III配置

- 格式:pdf

- 大小:170.16 KB

- 文档页数:6

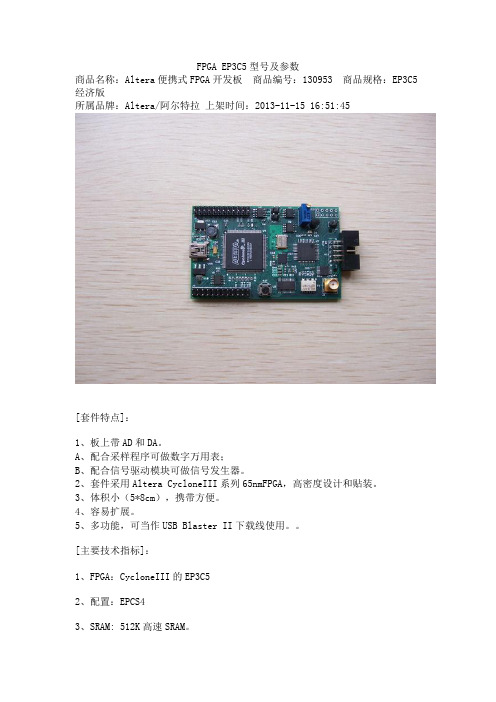

FPGA EP3C5型号及参数

商品名称:Altera便携式FPGA开发板商品编号:130953 商品规格:EP3C5经济版

所属品牌:Altera/阿尔特拉上架时间:2013-11-15 16:51:45

[套件特点]:

1、板上带AD和DA。

A、配合采样程序可做数字万用表;

B、配合信号驱动模块可做信号发生器。

2、套件采用Altera CycloneIII系列65nmFPGA,高密度设计和贴装。

3、体积小(5*8cm),携带方便。

4、容易扩展。

5、多功能,可当作USB Blaster II下载线使用。

[主要技术指标]:

1、FPGA:CycloneIII的EP3C5

2、配置:EPCS4

3、SRAM: 512K高速SRAM。

4、常用电压型DA :1 路10Bit,1.25 MHz maximum update rate

5、AD :1 路10Bit,1.25 MSPS

6、1个LED指示

7、1个复位按钮

8、24M有源晶振

9、2个24针扩展座,支持20个扩展IO,4个CLK输入。

10、四层板,通过全板EMC/EMI和SI仿真。

11、高速电流型DA:可选1 路14Bit 165MSPS(完全版才有此项)。

ETL-002 Altera Cyclone III系列FPGA开发板简介概述ETL-002 FPGA开发板是以Altera公司的最新系列Cyclone III中的3C10为主芯片,并提供了极为丰富的芯片外围接口资源以及下载线,数据线以及资料光盘等。

除了这些硬件外,我们还提供了十多个接口实验,并公开了电路原理图和实验的Verilog源代码,以便于大家对照学习,并可以在该开发板上进行二次开发。

单板描述主芯片EP3C10提供了10320个逻辑单元(LE),46块SRAM(每块9K bits), 23个18*18的乘法器。

开发板自带USB供电电路:您只需将USB线插上您的USB端口,无需外接+5V直流电源,开发板即可工作。

开发板同时支持AS模式下载和JTAG模式下载。

程序固化既可通过JTAG口也可直接对板上的FLASH进行编程。

丰富的外围接口可满足常用的外设的人机交互,我们还将剩下未用的40个用户I/O引脚全部引出,使得您可以通过这些信号对本开发板进行电路扩展。

这些接口主要包括:PS2鼠标接口:可以将PS2鼠标的任何移动的信息反应在数码管上PS2键盘接口:可以将PS2键盘上的任意按键以16进制的信息反应在数码管上VGA显示器接口:可以将FPGA产生的信息反映在VGA显示器上。

开发板自带了动态彩条显示的功能双串口接口:可以与任何的串口设备相接。

开发板自带的演示程序是将PC上的超级终端中输入的任何信息返回PC 4位数码管:可以实时显示任何的数字信息。

开发板自带的演示程序实时地显示分钟和秒钟的信息。

4位LED灯:用于指示状态。

开发板自带了跑马灯实验。

4位按键开关:可用于复位等作用。

4位拨码开关:可用于电路的选择作用教学实验除了开发板的丰富的硬件资源外,我们还提供了数十个学习实验。

通过这些实验,您可以学习FPGA芯片,Quartus II软件和设计仿真和下载等FPGA的设计流程,然后将试验中程序执行的信息通过数码管,LED 灯,串口等板上的硬件直观的显示出来。

Cyclone III原型开发调试转载:/ilove314/1819329/Message.aspx 最近设计的Cyclone III原型板是特权同学第一次接触Cyclone III的器件。

原理图、PCB绘制、管脚分配上都碰到了一些问题,这些问题或多或少都是由于个人对新器件不熟悉、设计的时候有一些粗心大意造成的。

主要针对板级的硬件设计,这里凌乱的罗列一下,做一点总结,今后要多吸取教训,低级的失误要尽量避免。

1. 首先要提一个没有解决的问题,EP3C5E144/EP3C10E144/ EP3C16E144/ EP3C 25E144(是管脚完全兼容的不同资源的器件,Altera在这一点上是非常值得称道的)器件的PIIN11和PIN12存在不可同时使用的问题,这个问题出现在架构了一个NIOS2系统里集成了EPCS控制器的时候,在Cyclone II中是不需要分配这个EPCS控制器的管脚的(内部自动映射),而Cyclone III则需要手动分配(事先需要到Setting里动动手脚)。

EPCS的DCLK需要分配到PIN12上,工程中分配了一个SDRAM的D0脚给PIN11,编译到Fitting阶段就Error了。

在handbook里海找没什么成效,求助于搜索引擎,最终看到有人遇到相同的问题,但是给出的却是不是办法的解决办法:不用PIN11或者不用PI N12。

这个问题上特权同学也很是无可奈何,估计是Cyclone III器件的这两个脚做了一些信号耦合之类的检查,也不知道是否在工具选项里做一些设置可以取消此类检查。

也很期待有相同遭遇的朋友现身说法,告诉特权如何解决问题。

2. 再说两个很低级的错误,错的很傻,没有什么技术含量,只能给自己敲个警钟:干活的时候脑子一定要清醒。

两个错误分别和BOM表和网络标号有关。

先说和BOM表有关的,这个错误源于原理图上两个三端稳压器-1.2和-2.5的标示刚好反过来了,因为管脚定义和封装都一样所以也没留意,好在最后只影响BOM表的标示,但这也导致了第一块样板焊接的时候出现了1.2V和2.5V互换位置的惨剧,结果可想而知,EP3C10E144C7就这样挂了,非常的心疼。

Cyclone III的LVDS接口注意事项对于Cyclone III器件,handbook中明确提到了以下的一些注意事项:1.对于作为LVDS传输的bank必须接2.5V的VCCIO。

2.左右bank(即1/2/5/6bank)的LVDS发送差分对信号无需外接匹配电阻,上下bank(即3/4/7/8bank)则需要。

3.分配管脚时,左右bank的LVDS差分信号在IO分配时选择IO标准为LVDS;上下bank的LVDS差分信号在IO分配时选择IO标准为LVDS_E_3R,好像没什么特殊含义,应该是帮助开发工具识别是哪个bank上的LVDS信号而已吧。

多谢网友iampeter在博文中提到这一点,帮助没太认真消化handbook的特权同学解决了这个问题。

除此以外,还有其它的一些技巧和注意事项,特权同学做了一点归纳:1.在分配管脚时,只要指定LVDS信号的p端(+),则n端(-)自动匹配;实际在verilog 中只要一个信号接口即可,无需一个差分对接口定义在源代码中。

2.可以使用MegaWizard中的IP核ALTLVDS实现并串转换的LVDS传输。

具体配置和说明建议参考相关手册。

3.接收部分没有进行测试和实验,不做归纳和整理。

4. 图1是一个7位并行输入的LVDS数据发送采集的波形,可以看到在默认输出时钟相位情况下,最高位bit6置1时为时钟上升沿后的第一个数据。

数据传送的效果大体如图2所示。

实际传输的相位是可以根据需要调整的。

图1 (上为时钟,下位数据)参考资料:1. /iampeter/240246/Message.aspx#2. Cyclone III handbook。

一、只使用FPGA硬件资源,不使用NIOS的时候

需要将nCEO引脚设为用户引脚,注意:一般编译器是默认它为程序下载的引脚的

将nCEO设为用户IO,其它的保留原样

二、使用NIOS的时候

由于CD0板子上没有设计FLASH。

所以在使用NIOS的时候,需要把程序存在EPCS器件中。

CYCLONE III器件跟其它器件的EPCS使用方法不同。

将DEVICE AND PIN OPTIONS页全部置为USER IO

在SOPC中添加epcs_flash_controller

在FPGA工程的顶层模块中添加EPCS控值器的接口

在NIOS的FLASH PROGRAMMER中做如下设置

将FPGA的SOF文件用QUARTUS的通过JTAG下载到FPGA后,

在NIOS的FLASH PROGRAMMER中点这时,NIOS的FLASH

PROGRAMMER会把.SOF文件和NIOS生成的.ELF文件合在一起,生成另一个配置文件下载到板子上的EPCS芯片中

重新上电,FPGA就以正常运行NIOS+FPGA的程序了

注意:在使用NIOS的时候FPGA的PIN_22因为太靠近PIN_23:DCLK(FPGA提供给EPCS 芯片的时钟)而不能再使用(使用时QUARTUS编译器会报错)。

PIN_22对应了CD0板子上的GPIO1[13],

所以在有NIOS的工程中都没有使用这一个引脚,对应的有NIOS的FPGA顶层也写成了如下:

跳过了…[12]这个引脚。

Cyclone III 的配置

全文翻译自Altera公司Cyclone III的器件手册。

所有表格与图标标号与手册原文一致,以便于查对。

出于个人需要,仅翻译了AS与JTAG配置两部分,且仅都配置一片FPGA芯片。

可以通过压缩数据的方法以节约存储空间,并节省程序load时间(page 220);

9通过Remote System Upgrade方式可以减少新产品面市的时间(page 221);

9AS Configuration(Serial Configuration Devices)

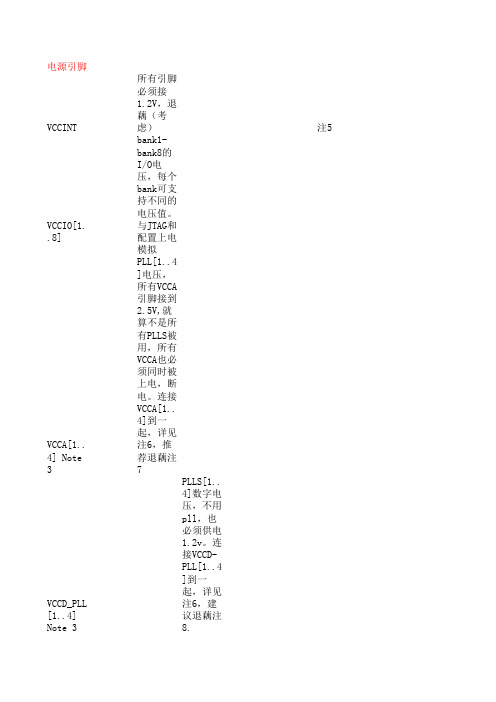

¾表10-6显示的是对各种配置电平来说,MSELx管脚的接法

¾单一器件配置

四个接口管脚包含了串口时钟(DCLK),串行数据输出(DATA),AS 数据输入(ASDI),以及低电平有效的片选信号(nCS)。

注:

1)上拉一个电阻,连接到该管脚所在的bank的VCCIO;

2)Cyclone III器件通过DATA[1]-to-ASDI路径控制配置芯片;

3)nCEO管脚浮空,或者当没有连接到另一个器件的nCE管脚时,可以当作通用IO使用;

4)MSEL管脚的设置,用于选择不同的电平标准和不同的POR时间;参考表10-6,选择

接法;

5)这些是复用管脚。

FLASH_nCE管脚在AS配置电路图中当作nCSO功能使用,DATA[1]

管脚当作ASDO功能使用;

6)这些串接的电阻尽可能靠近配置芯片

当连接一个配置芯片到Cyclone III器件时,DATA[0]管脚必须串一个电阻,并应接近配置芯片。

配置器件和Cyclone III芯片间连线的长度应符合表10-8所推荐的值。

当选择AS配置方式的时候,BAMK 1的IO电压必须是3.3,3.0或2.5。

上电以后,CIII器件有一个POR时间的延迟,在此期间,nSTATUS和CONF_DONE 会一直为低,所有的IO也都是三态输出。

芯片配置的三个阶段分别是复位,配置和初始化。

当nCONFIG或者nSTATUS为低,芯片处于复位状态,经过POR时间后,CIII释放nSTATUS,进入配置模式。

(为开始配置,所有配置管脚和JTAG管脚所在的BANK的VCCINT,VCCA和VCCIO必须成功上电)。

CIII器件生成的串口时钟(DCLK)控制整个配置周期并为串口提供时序。

CIII利用每步40MHz的晶振生成DCLK。

在AS配置模式下,配置芯片在DCLK的上升沿锁存输入和控制信号,并在下降沿送出数据;而CIII会在DCLK的下降沿发出控制信号并在DCLK的下降沿锁存配置数据。

CIII接收完所有的配置信息后,释放开环输出的CONF_DONE。

只有当CONF_DONE 变成高电平时,CIII才开始初始化。

如果在配置期间出现了错误,CIII会将nSTATUS信号拉低,表示有一个数据帧错误,CONF_DONE信号保持为低。

如果Auto-restart configuration after error 选项选中的话,CIII 会复位配置信号,通过向FLASH_NCE发一个脉冲,经过复位时间后释放nSTATUS的状态(最大230us)。

注:

1)所有这些管脚连接到所在BANK的VCCIO;

2)nCEO管脚可以悬空,或者当没有被连接到另外一个器件的nCE管脚时当作一个通用管

脚使用;

3)为USB下载线提供3.3V电源

4)MSEL管脚的设置,用于选择不同的电平标准和不同的POR时间;参考表10-6,选择

接法;

5)这些是复用管脚。

FLASH_nCE管脚在AS配置电路图中当作nCSO功能使用,DATA[1]

管脚当作ASDO功能使用;

6)这些二极管和电容必须靠近CIII芯片,必须保证二极管和电容可以容忍4.1V的交流电

压。

外接的二极管和电容用于保护CIII AS配置输入管脚,因为当使用下载线对器件进行编程时会可能overshoot。

Altera推荐使用Schottky二极管,而不是Zener二极管。

7)当CIII工作于multi-device AS配置模式,在CIII主机和从机只基恩连接repeater 缓存。

¾JTAG配置

CIII的JTAG配置优先级超过其它所有配置方式,因此,在进行其它方式配置时,JTAG 配置方式可以立即启动而不用等其它方式配置结束。

当CIII的MSEL管脚设置成AS模式,当JTAG配置发生时,CIII器件不会发出DCLK信号。

用于JTAG配置的4个管脚是TDI,TDO,TMS和TCK。

TCK管脚有内部弱上拉电阻,而TDI和TMS则需要外部上拉一个电阻(通常为25K)。

TDO输出管脚是由BANK1的VCCIO供电。

所有的JTAG输入管脚都是由VCCIO驱动的,且仅仅支持LVTTL I/O标准,在JTAG配置期间,所有用户I/O管脚都是三态。

VCCIO为2.5V,3.0V或3.3V的器件的JTAG配置,参考图10-24。

所有的I/O管脚都维持在最大4.1V交流电压。

由于JTAG管脚没有内部PCI过压保护二极管,因此必须用VCCA 的2.5V给下载电缆供电。

注:

1)所有这些管脚连接到所在BANK的VCCIO;

2)把nCONFIG和MSEL[3..0]管脚连接成一个非JTAG配置的模式。

如果仅仅使用JTAG

模式,则把nCONFIG拉高,并把MSEL[3..0]接到地上,除此以外,得把DCLK和DATA[0]拉高或拉低;

3)插头的6脚是下载电缆输出驱动的参考电压,VIO需要符合VCCA;

4)为成功进行JTAG配置,nCE必须连到地上或拉低;

5)nCEO管脚浮空或者当作一个通用I/O使用;

6)用来自VCCA的2.5-V给下载电缆供电,插头上的4脚给MasterBlaster电缆供电,

MasterBlaster电缆可以接收板子上的5.0V或者3.3V电压。

进行JTAG配置的时候,必须考虑CIII的一些专用配置管脚,见表10-17:

表10-7:JTAG配置时,其它专用配置管脚的连接

Signal Description

nCE nCE必须接到地上,或者通过一电阻拉低,或者由其它控制电路驱动。

如器件还由AS,PS,AP,PP配置链,则进行JTAG配置时,nCE需要连到地上nCEO 该chain上的所有CIII器件的CEO必须浮空,或者连到另一个器件的nCE MSEL[3..0] 不能浮空,应该按照其它配置模式去接这几个管脚

nCONFIG 通过一个电阻拉高,或者由其它控制电路驱动

nSTATUS 通过一个10k的电阻连接到该管脚所在bank的VCCIO,如果有多个芯片,则必须每个都上拉电阻

CONF-DONE 通过一10k的电阻上拉到VCCIO。

JTAG配置完成后,CONF-DONE为高DCLK 不能浮空,根据板子的要求,拉高或拉低。