单片机七人表决器

- 格式:doc

- 大小:155.00 KB

- 文档页数:11

课程设计课程名称硬件描述语言与EDA技术课程设计题目名称学生学院材料与能源学院专业班级学号学生姓名指导教师陈先朝2017年6 月10日目录一、设计目的 (1)二、设计内容 (1)三、设计思路 (1)四、Verilog源程序 (1)五、管脚分配 (3)六、总结设计与体会 (3)七、参考文献 (4)七人表决器设计一、设计目的1.熟悉Quartus II软件的使用。

2..熟悉七人表决器的工作原理3.熟悉EDA开发的基本流程。

二、设计内容基础功能:设计一个七人表决器,当赞成人数大于等于四时显示表决通过,同时分别将投票中赞成人数和反对人数在数码管显示出来。

新加:清零键和通过时蜂鸣器响。

三、设计思路(1)使用一个模块完成所有功能。

(2)用alawys语句检测赞同和反对人数信号(A和B),再用两个独立共阴极数码管显示人数0到7。

(3)用if语句判断总人数是否超出7人(s)(4)用另一个clk实现蜂鸣器,因为原来的clk信号频率过低。

四、Verilog源程序module biaojue(clk_1,clk_2,yes,no,clear,buzz,A,B,result);input clk_1,clk_2,yes,no,clear;reg [4:0] s1,s2,s;output reg [7:0] A,B;output reg result,buzz;always @(posedge clk_1)begins=s1+s2;if(clear) begin s1=0; s2=0; result=0; endelse if (s>4'b0111) begin s1=0; s2=0; result=0; endelse if (yes) s1=s1+1;else if (no) s2=s2+1;else if (s1>=4'b0100) begin result=1 ; endelse begin s1=s1; s2=s2; result=result; endendalways @(clk_2)begin if (result) buzz=~clk_2;endalways @(s1)begincase(s1)4'b0000:A=8'h3f;4'b0001:A=8'h06;4'b0010:A=8'h5b;4'b0011:A=8'h4f;4'b0100:A=8'h66;4'b0101:A=8'h6d;4'b0110:A=8'h7d;4'b0111:A=8'h07;default:A=8'h00;endcaseendalways @(s2)begincase(s2)4'b0000:B=8'h3f;4'b0001:B=8'h06;4'b0010:B=8'h5b;4'b0011:B=8'h4f;4'b0100:B=8'h66;4'b0101:B=8'h6d;4'b0110:B=8'h7d;4'b0111:B=8'h07;default:B=8'h00;endcaseendendmodule五、管脚分配错误!六、总结设计与体会七、参考文献(1)自编指导书;(2)Verilog与EDA相关教程:a)王金明等编著,EDA技术与Verilog HDL设计,电子工业出版社,2013年;b)艾明晶编著,EDA技术实验教程,清华大学出版社,2014年;c)潘松等编著,EDA技术与Verilog HDL ,清华大学出版社,2013年;d)张春晶等编著,现代数字电子技术及Verilog设计,清华大学出版社,2014年;e)刘靳等编著,Verilog程序设计与EDA ,西安电子科技大学出版社,2012年;f)刘福奇主编,Verilog HDL 应用程序设计实例精讲,电子工业出版社,2012年;g)周润景等主编,基于Quartus Ⅱ的数字系统Verilog HDL设计实例详解,电子工业出版社,2010年。

河北科技大学实验报告2013级电信专业132 班学号130701213 2016年5月23日姓名田继辉同组人指导教师于国庆实验名称实验一七人表决器成绩实验类型设计型批阅教师一、实验目的(1)掌握MUXPLUS II语言输入的设计过程。

(2)初步了解VHDL语言。

(3)熟悉FPGA项目设计的基本流程。

二、实验原理:用七个开关作为表决器的7个输入变量,输入变量为逻辑“1”时表示表决者“赞同”;输入变量为逻辑“0”时表示表决者“不赞同”;输出逻辑“1”时,表示表决“通过”;输出逻辑“0”时,表示表决“不通过”;当表决器的七个输入变量中有4个及以上为“1”时,则表决器输出为“1”,否则为“0”。

表决器输入采用试验箱K1~K16,输出采用试验箱L15、L16指示;同意红灯亮,否则黄灯亮。

三、实验内容及步骤1.打开MUXPLUS II VHDL编辑器,完成七人表决器的设计。

包括VHDL程序输入、编译、综合。

实验程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;ENTITY vote7 ISPORT( men : IN std_logic_vector(6 downto 0);pass,stop : buffer std_logic);END vote7;ARCHITECTURE behave OF vote7 ISBEGINstop<=not pass;PROCESS (men)variable temp:std_logic_vector(2 downto 0);BEGINtemp:="000";for i in 0 to 6 loopif(men(i)='1') thentemp:=temp+1;elsetemp:=temp+0;end if;end loop;pass<=temp(2);END PROCESS;END behave;2、建立仿真波形文件,使用MAXPLUS II Simulator功能进行功能仿真。

--------------------------------------- Title: 七人表决器---- Author:Pan hongtao ---- Data: 2006-10-1 ------------------------------------------library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;--------------------------------------------------------------------entity exp12 isport(k1,K2,K3,K4,K5,K6,K7 : in std_logic; --输入:7个人ledag : out std_logic_vector(6 downto 0); --数码管显示m_Result : out std_logic --表决结果);end exp12;--------------------------------------------------------------------architecture behave of exp12 issignal K_Num : std_logic_vector(2 downto 0);signal K1_Num,K2_Num: std_logic_vector(2 downto 0);signal K3_Num,K4_Num: std_logic_vector(2 downto 0);signal K5_Num,K6_Num: std_logic_vector(2 downto 0);signal K7_Num : std_logic_vector(2 downto 0);beginprocess(K1,K2,K3,K4,K5,K6,K7) --计算表决同意人数beginK1_Num<='0'&'0'&K1;K2_Num<='0'&'0'&K2;K3_Num<='0'&'0'&K3;K4_Num<='0'&'0'&K4;K5_Num<='0'&'0'&K5;K6_Num<='0'&'0'&K6;K7_Num<='0'&'0'&K7;end process;process(K1_Num,K2_Num,K3_Num,K4_Num,K5_Num,K6_Num,K7_Num)beginK_Num<=K1_Num+K2_Num+K3_Num+K4_Num+K5_Num+K6_Num+K7_Num;end process;process(K_Num) --根据人数输出结果beginif(K_Num>3) thenm_Result<='1';elsem_Result<='0';end if;end process;process(K_Num) --根据人数数码管显示表决通过人数begincase K_Num iswhen "000"=>ledag<="0111111";when "001"=>ledag<="0000110";when "010"=>ledag<="1011011";when "011"=>ledag<="1001111";when "100"=>ledag<="1100110";when "101"=>ledag<="1101101";when "110"=>ledag<="1111101";when "111"=>ledag<="0000111";when others=>ledag<="0000000";end case;end process;end behave;。

实验五七人表决器的设计一、实验目的1、掌握VHDL程序设计。

二、实验内容设计七人表决器,并在数码管上显示赞成票数。

三、实验仪器1、ZY11EDA13BE型实验箱通用编程模块,配置模块,开关按键模块,数码显示模块。

2、并口延长线,JTAG延长线。

3、安装MAX+PLUSII 10.2软件的PC机。

四、实验原理表决器是统计选票结果的工具,投票者通过拨位开关投票,表示赞成或反对,用循环语句完成赞成票计数过程,统计出赞成的票数之后,用CASE控制数码管显示赞成票数。

五、实验步骤:步骤1:输入VHDL程序,编译,仿真,锁定引脚并下载到目标芯片。

步骤2:验证设计结果。

六、实验报告1、列出数码管控制接口表(列出数码管显示数字的每段控制电平)。

七、思考题记录实验数据,列出七人表决器的真值表。

VHDL程序:library ieee;use ieee.std_logic_1164.all;ENTITY eda3 isPORT (men:in std_logic_vector(6 downto 0);a,b,c:out std_logic;output:out std_logic_vector(6 downto 0)); END entity eda3;ARCHITECTURE behave OF eda3 ISBEGINPROCESS(men)variable temp: integer range 0 to 7;BEGINtemp:=0;for i in 0 to 6 loopif(men(i)='1')thentemp:=temp+1;end if;end loop;case temp iswhen 0 => output <="1111110";when 1 => output <="0110000";when 2 => output <="1101101";when 3 => output <="1111001";when 4 => output <="0110011";when 5 => output <="1011011";when 6 => output <="1011111";when 7 => output <="1110000";when others => output <="0000000";end case;a <='1';b <='1';c <='1';END PROCESS;END architecture behave;。

河北科技大学实验报告2010级电信专业101 班学号13年4月1日姓名同组人指导教师于国庆实验名称实验一七人表决器成绩实验类型设计型批阅教师一、实验目的(1)掌握MUXPLUS II语言输入的设计过程。

(2)初步了解VHDL语言。

(3)熟悉FPGA项目设计的基本流程。

二、实验原理:用七个开关作为表决器的7个输入变量,输入变量为逻辑“1”时表示表决者“赞同”;输入变量为逻辑“0”时表示表决者“不赞同”;输出逻辑“1”时,表示表决“通过”;输出逻辑“0”时,表示表决“不通过”;当表决器的七个输入变量中有4个及以上为“1”时,则表决器输出为“1”,否则为“0”。

表决器输入采用试验箱K1~K16,输出采用试验箱L15、L16指示;同意红灯亮,否则黄灯亮。

三、实验内容及步骤1.打开MUXPLUS II VHDL编辑器,完成七人表决器的设计。

包括VHDL程序输入、编译、综合。

实验程序如下:library ieee;use ieee.std_logic_1164.ALL;entity GSL isport(a:in std_logic_vector(6 downto 0);b:out std_logic;c:out std_logic);end entity GSL;architecture number of GSL isbeginprocess(a)variable cnt:integer range 0 to 7;begin cnt:=0;for i in 6 downto 0 loopif a(i)='1'thencnt:=cnt+1;end if;end loop;if cnt>3 then b<='1';c<='0';else b<='0';c<='1';end if;end process;end architecture number;2、建立仿真波形文件,使用MAXPLUS II Simulator功能进行功能仿真。

一、实验目的1、掌握VHDL设计流程2、熟悉应用型电路设计方法二、实验内容设计七人表决器电路,系统有七个输入,每个输入端输入‘1’为通过,‘0’为不通过,七个输入中通过者超过半数输出为‘1’。

三、实验设备1、硬件:PC机一台2、软件:Maxplus2环境四、实验设计程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DFF1 ISPORT (A1,A2,A3,A4,A5,A6,A7:IN STD_LOGIC;Y:OUT STD_LOGIC);END;ARCHITECTURE bhv OF DFF1 ISBEGINPROCESS(A1,A2,A3,A4,A5,A6,A7)VARIABLE SUM:INTEGER RANGE 0 TO 7;BEGINSUM:=0;IF A1='1'THEN SUM:=SUM+1;END IF;IF A2='1'THEN SUM:=SUM+1;END IF;IF A3='1'THEN SUM:=SUM+1;END IF;IF A4='1'THEN SUM:=SUM+1;END IF;IF A5='1'THEN SUM:=SUM+1;END IF;IF A6='1'THEN SUM:=SUM+1;END IF;IF A7='1'THEN SUM:=SUM+1;END IF;IF SUM>3 THEN Y<='1';ELSE Y<='0';END IF;END PROCESS;END;实验思路分析:在实体H_7中定义端口A1,A2,A3,A4,A5,A6,A7 和GAIN,其中A1,A2,A3,A4,A5,A6,A7为七位标准逻辑向量,用于表示七个人,GAIN为标准逻辑输出。

昆明理工大学信息工程与自动化学院学生实验报告(2012———2013 学年第 2 学期)课程名称:可编程逻辑器件开课实验室:信自楼504 2013年4 月19日一.实验要求、本实验要求编写一个七人表决器,描述为:总共有7个人进行投票选择,只有达到4人或者4人以上才能够通过。

二.实验过程:输入为2进制7位的VOTE,输出为2进制4位的SUM,当SUM得第三位为1时,即SUM>=4,即通过PASS!三.实验代码:在本次试验中,我通过观察实验代码,自己编写了11人表决器:module vote_11(pass,vote);output pass;reg pass;input [10:0] vote;reg[3:0]sum;integer i;always@(vote)beginsum=0;for(i=0;i<=10;i=i+1)if(vote[i]) sum=sum+1;if(sum[3]) if(sum[2]) pass=1;else pass=0;endendmodule四.实验截图:五.实验总结:通过上次对Quartus Ⅱ环境的熟悉,这次的试验速度上就要比上次好得多,这也是上次试验多次实践讨论改错的功劳,这次我对于VERILOG HDL 的模拟功能有了一定的理解,通过对试验代码的调试,我发现了代码中存在很多的问题,查资料、与同学老师讨论使我最终解决了一个个问题和错误,在仿真后我得到了仿真波形,完成了这次试验任务。

通过这次试验,我发现对Quartus Ⅱ环境的熟悉是一个长期试验使用的过程,结果了两次的试验,我了解的知识微小的那一小部分。

我需要学习的还很多。

同时课本上的理论知识也是很重要的,扎实的基础使我们进一步提高自己的基础。

我们要扎住在校的学习时间为以后的工作打好基础。

摘要7人表决控制电路是一简单的输入信号检测与处理、产生输出控制信号的逻辑电路。

本文详细介绍了依据功能要求进行控制电路方案设计的过程,并在此基础上将整体电路分为输入信号处理模块,计时模块,译码模块,比较模块,显示模块等主要功能模块。

实现中采用Verilog HDL描述、ModelSim进行功能仿真、ISE进行逻辑综合和适配下载,最后在Altera的CycloneⅡ芯片EP2C8Q208C8上实现并完成测试。

在此过程中,完整地建立了测试平台,完成了功能和时序仿真,从而保证了设计的功能与时序的正确性。

关键词Verilog HDL;FPGA;仿真;综合;动态扫描目录引言 (1)1 总体电路结构设计 (2)1.1电路功能与性能 (2)1.2主要调度算法 (2)1.3电路接口 (3)1.4电路功能框图 (4)1.5验证方案 (5)2 模块设计 (6)2.1输入信号处理模块设计 (6)2.2计时模块设计 (8)2.3译码模块设计 (8)2.4比较模块设计 (9)2.5显示模块设计 (10)3 设计仿真与测试 (11)3.1仿真与测试的功能列表 (11)3.2仿真平台构建和仿真结果 (11)3.2.1 顶层仿真平台与激励 (11)3.2.2 电路功能仿真结果 (12)3.2.3 电路后仿真结果 (13)3.3测试环境的搭建与测试结果 (13)3.3.1 测试环境模拟 (13)3.3.2 电路测试结果 (14)4 电路约束与综合实现 ........................................................................ 错误!未定义书签。

4.1时序约束 (15)4.2引脚锁定约束 (16)4.3电路综合报告 (17)4.4设计实现与下载 (17)结论 (21)参考文献 (22)引言随着可编程器件FPGA/CPLD成本的逐渐降低,以及开发测试技术的日益普及,FPGA/CPLD以其较好的集成度和稳定性、可编程实现与升级的特点,在电子设计领域得到了越来越多的应用。

七人表决器VHDL语言代码大连海事大学信息工程学院EDA课程设计实验模块一【BCD译码器】:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY BCDDECODER ISPORT(BCD :IN STD_LOGIC_VECTOR(3 DOWNTO 0);SEGOUT :OUT STD_LOGIC_VECTOR(0 TO 6));END BCDDECODER;ARCHITECTURE a OF BCDDECODER ISBEGINPROCESS(BCD)BEGINCASE BCD ISWHEN"0000"=>SEGOUT<="1111110";WHEN"0001"=>SEGOUT<="0110000";WHEN"0010"=>SEGOUT<="1101101";WHEN"0011"=>SEGOUT<="1111001";WHEN"0100"=>SEGOUT<="0110011";WHEN"0101"=>SEGOUT<="1011011";WHEN"0110"=>SEGOUT<="1011111";WHEN"0111"=>SEGOUT<="1110000";WHEN"1000"=>SEGOUT<="1111111";WHEN"1001"=>SEGOUT<="1111011";WHEN OTHERS=>SEGOUT<="0000000";END CASE;END PROCESS;END a;模块二【7人表决器】:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity biaojue isport(a:in std_logic_vector(6 downto 0);b:out std_logic;p1:out std_logic_vector(3 downto 0));end biaojue;architecture one of biaojue isbeginprocess(a)variable i: std_logic_vector(2 downto 0); begini:="000";for j in 0 to 6 loopif(a(j)='1') then i:=i+1;else i:=i+0;end if;end loop;if i>3 then b<='1';else b<='0';end if;case i iswhen "000"=>p1<="0000";when "001"=>p1<="0001";when "010"=>p1<="0010";when "011"=>p1<="0011";when "100"=>p1<="0100";when "101"=>p1<="0101";when "110"=>p1<="0110";when "111"=>p1<="0111";when others=>null;end case;end process;end one;注:水平有限,有错难免,多包涵。

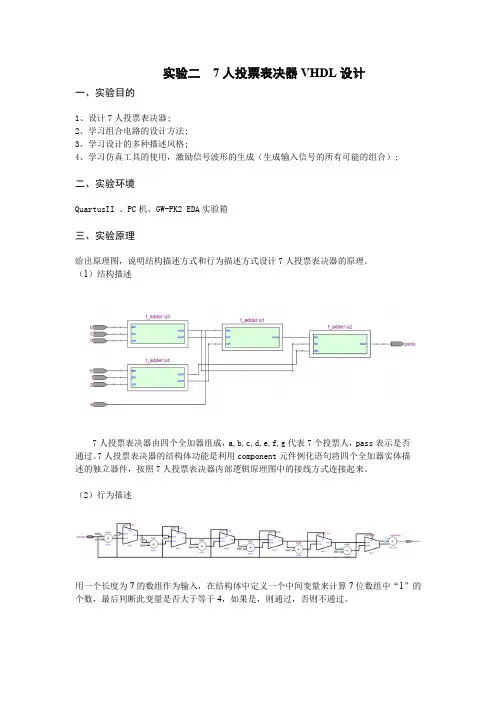

实验二7人投票表决器VHDL设计一、实验目的1、设计7人投票表决器;2、学习组合电路的设计方法;3、学习设计的多种描述风格;4、学习仿真工具的使用,激励信号波形的生成(生成输入信号的所有可能的组合);二、实验环境QuartusII 、PC机、GW-PK2 EDA实验箱三、实验原理给出原理图,说明结构描述方式和行为描述方式设计7人投票表决器的原理。

(1)结构描述7人投票表决器由四个全加器组成,a,b,c,d,e,f,g代表7个投票人,pass表示是否通过。

7人投票表决器的结构体功能是利用component元件例化语句将四个全加器实体描述的独立器件,按照7人投票表决器内部逻辑原理图中的接线方式连接起来。

(2)行为描述用一个长度为7的数组作为输入,在结构体中定义一个中间变量来计算7位数组中“1”的个数,最后判断此变量是否大于等于4,如果是,则通过,否则不通过。

四、实验内容及要求利用QuartusII完成7人投票表决器的VHDL设计及仿真测试,给出仿真波形,进行引脚锁定,并在实验箱上进行硬件验证。

五、实验步骤(1)用文本方式输入设计文件并存盘①创建工程,利用“New Preject Wizard”创建此设计工程。

选择菜单“File” “New Preject Wizard”,点击Next,即可弹出工程设置对话框点击此框最上一栏右侧的按钮“…”,设置工程路径,找到文件夹D:\Quartus8\vhdl_code\two,填写工程名和顶层文件名称后,点击Next 按钮进行下一步。

②将全加器设计文件加入③选择目标芯片。

首先在“Family”栏选芯片系列,在此选“ACEX1K”系列,选择此系列的具体芯片:EP1K30TC144-3。

④选择仿真器和综合器类型。

点击上图的Next按钮,这时弹出的窗口是选择仿真器和综合器类型的,如果都是选默认的“NONE”,表示都选QuartusII中自带的仿真器和综合器,因此,在此都选默认项“NONE”。

写出了综合设计的第一个实验的详细步骤,主要是介绍用QuartusII软件设计由多个模块构成的数字系统的主要步骤,及注意事项。

希望对前几个实验未能完全掌握的同学有所帮助。

3.3.2实验内容基于QuartusII软件及VHDL语言实现七人表决器。

当参与表决的7人中有4个或4个以上赞同时,表决器输出“1”表示通过,否则输出“0”表示不通过,并显示赞成和反对的人数。

用7个电平开关作为表决器的7个输入变量,数码管显示人数,LED灯显示是否通过。

本实验4学时。

3.3.3实验仪器ZY11EDA13BE型实验箱。

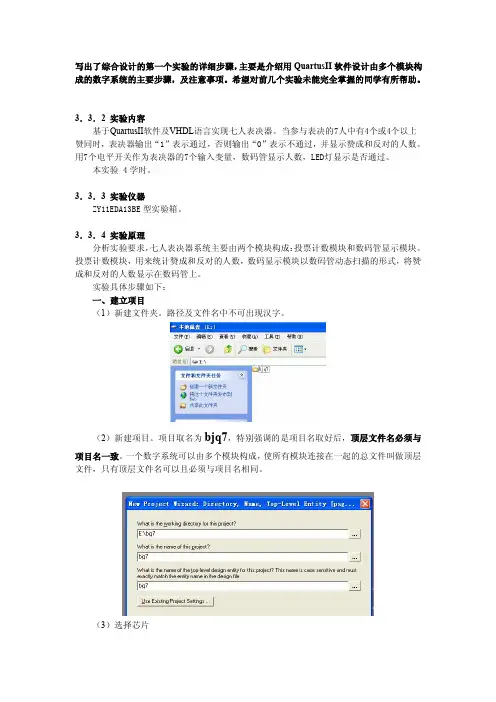

3.3.4实验原理分析实验要求,七人表决器系统主要由两个模块构成:投票计数模块和数码管显示模块。

投票计数模块,用来统计赞成和反对的人数,数码显示模块以数码管动态扫描的形式,将赞成和反对的人数显示在数码管上。

实验具体步骤如下:一、建立项目(1)新建文件夹。

路径及文件名中不可出现汉字。

(2)新建项目。

项目取名为bjq7,特别强调的是项目名取好后,顶层文件名必须与项目名一致。

一个数字系统可以由多个模块构成,使所有模块连接在一起的总文件叫做顶层文件,只有顶层文件名可以且必须与项目名相同。

(3)选择芯片二、建立文件1.建立投票计数模块。

(1)新建VHDL文件(2)编辑VHDL程序。

投票计数模块输入为七个电平开关input,输出为同意的人数agree,反对的人数disagree,是否通过指示灯y,程序清单如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity BJQ isport(input:in std_logic_vector(6downto0);agree:out std_logic_vector(3downto0);disagree:out std_logic_vector(3downto0);y:out std_logic);end;architecture one of BJQ isbeginprocess(input)variable cnt:integer range0to7;variable cnt0:integer range0to7;begincnt:=0;for i in6downto0loopif input(i)='1'thencnt:=cnt+1;end if;end loop;cnt0:=7-cnt;if cnt>3then y<='1';else y<='0';end if;case cnt iswhen0=>agree<="0000";when1=>agree<="0001";when2=>agree<="0010";when3=>agree<="0011";when4=>agree<="0100";when5=>agree<="0101";when6=>agree<="0110";when7=>agree<="0111";when others=>agree<="0000";end case;case cnt0iswhen0=>disagree<="0000";when1=>disagree<="0001";when2=>disagree<="0010";when3=>disagree<="0011";when4=>disagree<="0100";when5=>disagree<="0101";when6=>disagree<="0110";when7=>disagree<="0111";when others=>disagree<="0000";end case;end process;end;程序输入完成后进行保存,名字与实体名一致BJQ。

电子技术课程设计课题:表决器电路设计系别:电气与电子工程系专业:电气工程及其自动化姓名: AAA学号: 09AAA河南城建学院2012年 06 月 21 日成绩评定·一、指导教师评语二、评分课程设计成绩评定一、设计目的1.本课程设计是在前导验证性认知实验基础上,进行更高层次的命题设计实验,要求学生在教师指导下独立查阅资料、设计、安装和调试特定功能的电子电路。

培养学生利用模拟、数字电路知识,解决电子线路中常见实际问题的能力,使学生积累实际电子制作经验,目的在于巩固基础、注重设计、培养技能、追求创新、走向实用。

2.用已学过的知识和对数字电子技术的基本理论,基本概念,基本方法和单元电路,逻辑部件的深入认识,而拓宽思路,扩大视野,进一步巩固,扩充所学知识,提高分析问题和解决问题的能力。

二、设计题目和内容题目:表决器电路设计1) 用于七人以下会议表决。

半数以上人同意通过。

2)应考虑弃权情况,有三人以上弃权,推迟会议再议。

3)根据表决情况显示“否决”“通过”“再议”字样。

显示方式自己设计。

三、电路比较方案一:用数据选择器分别将通过、否决、弃权的高低电平进行选择,之后将七人的选择结果用T触发器构成的同步二进制加法计数器进行累加。

然后用数字比较器进行比较,如果弃权的票数大于等于3,则输出为“再议”。

如果弃权的票数小于3且通过的票数大于3,则显示为“通过”。

其余的则显示为“否决”。

方案二:将七人的通过、否决票数用移位寄存器进行寄存,弃权的票数用另一组移位寄存器进行寄存,然后用CLK脉冲信号使其移位寄存器进行右移,用T触发器构成的同步二进制加法计数器进行累加,如果弃权的票数大于等于3,则输出为“再议”。

如果弃权的票数小于3且通过的票数大于3,则显示为“通过”。

其余的则显示为“否决”。

方案对比:方案一用的数据选择器比较多而且反应速度较慢,方案二用器件较少,比较好一些。

方案二:电路的总体结构 1、电路的总体原理框图图1 总体电路原理框图2、工作原理工作原理如图:投票按键部分每人有三个按键,总共21个按键,投票时按下相应的键就可以将相应的信号送入输入转换部分,输入转换部分主要由移位寄存器组成,它的作用是将投票时并行输入的数据串行输出,在控制电路的作用下,数据在这里逐个输出进入票数统计部分,这部分主要是由三个JK 触发器组成的三位二进制计数器。

一、实验目的1、掌握VHDL设计流程2、熟悉应用型电路设计方法二、实验内容设计七人表决器电路,系统有七个输入,每个输入端输入‘1’为通过,‘0’为不通过,七个输入中通过者超过半数输出为‘1’。

三、实验设备1、硬件:PC机一台2、软件:Maxplus2环境四、实验设计程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DFF1 ISPORT (A1,A2,A3,A4,A5,A6,A7:IN STD_LOGIC;Y:OUT STD_LOGIC);END;ARCHITECTURE bhv OF DFF1 ISBEGINPROCESS(A1,A2,A3,A4,A5,A6,A7)VARIABLE SUM:INTEGER RANGE 0 TO 7;BEGINSUM:=0;IF A1='1'THEN SUM:=SUM+1;END IF;IF A2='1'THEN SUM:=SUM+1;END IF;IF A3='1'THEN SUM:=SUM+1;END IF;IF A4='1'THEN SUM:=SUM+1;END IF;IF A5='1'THEN SUM:=SUM+1;END IF;IF A6='1'THEN SUM:=SUM+1;END IF;IF A7='1'THEN SUM:=SUM+1;END IF;IF SUM>3 THEN Y<='1';ELSE Y<='0';END IF;END PROCESS;END;实验思路分析:在实体H_7中定义端口A1,A2,A3,A4,A5,A6,A7 和GAIN,其中A1,A2,A3,A4,A5,A6,A7为七位标准逻辑向量,用于表示七个人,GAIN为标准逻辑输出。

总成绩:

一、设计任务

①有七人参与表决,显示赞同者个数。

②当赞同者达到及超过4人时,绿灯显示表示通过。

二、设计条件

本设计基于学校实验室的环境,根据实验室提供的实验条件来完成设计任务。

三、设计要求

①熟悉74LS161,74LS151,数码管的工作原理。

②设计相应的电路图,标注元件参数,并进行仿真验证。

四、设计内容

1.电路原理图(含管脚接线)

本实验主要用74LS161、74LS151实现。

74LS161管脚及功能表如下图所示:

74LS161芯片管脚功能图

74LS161功能表如下:

74LS151的管脚分布及功能表如下图所示:

七人表决器的表决信息作为74LS151的输入信号。

当第一个计数器从1计到7,数据选择器分别吧7路输入输出给第二个计数器,以统计同意的人的个数,若大于等于4人,则绿灯发亮,同时第二个计数器输出端接数码管以显示统一的人数。

下图为表决器电路原理图:

2.电路仿真

调试流程

4.

5.设计和使用说明

七个人对应七个开关,当七人表决结束后,闭合控制开关key,,电路将其人表决信息统计,结果输出在法光二极管及数码管中。

断开key开关进行清零,进行下一轮的投票。

六、设计参考资料

(1)杨世彦《电工学(中册)电子技术(第二版)》机械工业出版社2008.5

(2)吴建强《电工学新技术实践(第二版)》机械工业出版社2009.8。

实验报告七人表决器摘要所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于4人时,则认为同意;反之,当否决的票数大于或者等于4人时,则认为不同意。

实验中用7个拨挡开关来表示七个人,当对应的拨挡开关输入为‘1’时,表示此人同意;否则若拨挡开关输入为‘0’时,则表示此人反对。

表决的结果用一个LED 表示,若表决的结果为同意,则LED被点亮;否则,如果表决的结果为反对,则LED不会被点亮。

流程图:根据电路状态转换表→设计数值输出→运用门电路设计电路图→仿真运行→实现七人多数表决器的设计一、实验目的1.熟悉VHDL编程2.熟悉七人表决器工作原理3.进一步了解实验系统的硬件结构二、实验设备1.PC机2.THGSC-3型实验箱3.Altera Blaster 下载器三、设计要求用七个开关作为表决器的七个输入变量,逻辑“1”时表示“赞同”,逻辑“0”时表示“不赞同”,用发光二极管作为输出指令,输出逻辑“1”表示“通过”;输出逻辑“0”时表示“不通过”。

当表决器的七个输入变量中的4个以上(包含4个)为“1”时,则表决器输出为“1”;否则为“0”。

四、实验内容1.电路状态转换图:2.编写实验代码及注释如下图4.管脚分配说明:(1)清零端设置为按键S1(2)置数端设置为拨动开关SW8 (3)七个输入SW1~SW7(4)七个led输出D1~D7(5)数码管显示a~g5.分配图。

一.方案设计 1.设计题目:七人表决器。 2.实训要求 利用AT89S51单片机设计并制作会议表决计票器电路。具体要求如下: 1、可供57个人进行表决,每个人有一个“同意”和一个“反对”按键,表决时两个键先按下的一个有效,若再按另一个键将清楚前一次按键的效能;每次表决每个按键只能是第一次按的有效,多按的次数无效,除非前一次按键的效能已被清楚或没有生效。 2、会议主持人可利用按键控制表决开始和结束;开始表决后,点亮黄色指示灯,表示可以进行表决,同时清楚原来的表决结果;结束表决后显示表决结果;“同意”多于“反对”点亮绿色指示灯,反之点亮红色指示灯。 3、在实现上述功能的基础上增加“同意”数和“反对”数的显示。 二.硬件电路设计和原理。 1.硬件设计思路: 设计题目为5—7人表决器,题目选为七人表决器,七个按键表示同意,七个按键表示反对,各按键与单片机的输入端口相连,因此可选用单片机的四个I/O口,因为在单片机内部P1和P2都有上啦电阻,而P0没有上啦电阻,要在外部加上一个上拉电阻,为了简化电路,把P1和P2口选为按键同意和反对的输入端,因为表决考试和结束要利用主持人按键来控制,我采用外部中断0和外部中断一来控制其开始和结束;设计要求中需要四张灯,分别为2个红灯,一个黄灯,一个绿灯,其中三个灯用于输出显示,可用单片机的I/O口,另外一个红灯作为电源灯来显示,判断是否通电,因为P1口和P2口用做按键的同意和反对,把P2剩余的I/O口与三个灯连接,分别连接在P2.3,P2.4,P2.5口,因为P0口是低电平有效所以我的P0口与LED现实器相连用于显示反对与同意的人数的多少,采用动态显示的方式,为了保证两个显示器不再相同时间显示相同的数字,所以LED显示器的公共端受另外一组信号的控制,采用延时的方式让它们分别显示出来。 2.元件参数确定: 设计中需要四盏灯,分别为两个红灯,一个绿灯,一个黄灯,P0口的输出端输出高电平一般为5伏左右,最大电流为五毫安,因此必须加上限流电阻,我选用的是470欧的电阻,然后将单片机的最小系统加入此次的电路中。 3.元件清单: 14个开关用于7人同意与反对按键,另外两个开关用做控制投票开始和结束的总开关。 电容:用于单片机的最小系统。 发光二极管:用于表示投票开始与结束,和最后同意与反对票数的对比情况。 电阻:用于限流。 单片机8051芯片:用于编程。 电源接头:提供电源。 LED显示器:用于显示投票中同意与反对票数的多少。 4.电路工作原理简述。 当主持人按下开始键,外部中断0响应后,黄灯亮起,到外部中断服务程序,开始进行投票,7人开始表决,7个人分别按下同意或反对,然后有团建来处理和分析“同意”和“反对”的人数的多少,当主持人按下结束键时,停止投票。当最后结果“同意”人数多于“反对”人数时,亮起绿灯,当最后结果“同意”人数少于“反对”人数时,亮起红灯,把其最后的结果显示在两个LED显示器上面,最终达到设计的基本目标。 5.电路工作原理图: 6.电路实物图: 三.内容 1.软件设计思路: 1).软件初始化: 根据硬件开关与显示灯的接法对单片机进行初始值的设计,因为是低电平有效,故初始化设置为高电平有效。 2.)模块设计思路与各模块之间的联系: 用查询的方式来看按键是否被按下,若按下,点亮黄灯,开始表决,若同意或反对就在其对应的寄存器中自加一,知道总开关呢按键结束后,在比较其大小,并把最后结果存放在LED显示器当中。

2.软件总体功能: 1)用于检测开始键是否被按下,按下时表决器才有用才开始表决。 2)开始表决后循环检测对应的同意和反对是否被按下,并统计其同意总数和反对总数。 3)等待中断若结束按键被按下,在中断处理中比较,并点亮相应的显示灯。 4)把同意的票数和反对的票数分别显示在LED显示器上。 3.程序: ORG 0000H AJMP MAIN ORG 0003H SETB F0 SETB TR0 RETI ORG 000BH AJMP INTT0 ORG 001BH AJMP INTT1 ORG 0030H MAIN: MOV SP,#60H MOV TMOD,#11H MOV TL0,#0B0H MOV TH0,#03CH MOV R1,#20 MOV R2,#5 CLR P3.0 SETB EA SETB ET0 SETB EX0 SETB IT0 INDEX:MOV A,P1 ANL A,#0FH MOV 28H,A LCALL DELAY MOV A,P1 ANL A,#0FH CJNE A,28H,RETURN KEY: CJNE A,#0EH,KEY2 CLR P1.0 JB F0,DD SETB P3.0 LCALL SIXUNHUAN DD: LCALL AST KEY2: CJNE A, #0DH,KEY3 CLR P1.1 JB F0,DD1 SETB P3.0; LCALL SIXUNHUAN DD1: LCALL AST KEY3: CJNE A,#0BH,KEY4 CLR P1.2 JB F0,DD2 SETB P3.0 LCALL SIXUNHUAN DD2: LCALL AST KEY4: CJNE A,#07H,KEY5 CLR P1.3 JB F0,DD3 SETB P3.0 LCALL SIXUNHUAN DD3: LCALL AST KEY5: CJNE A, #0DH,KEY6 CLR P1.4 JB F0,DD4 SETB P3.0; LCALL SIXUNHUAN DD4: LCALL AST KEY6: CJNE A, #0DH,KEY7 CLR P1.5 JB F0,DD5 SETB P3.0; LCALL SIXUNHUAN DD5: LCALL AST KEY7: CJNE A, #0DH, RETURN CLR P1.6 JB F0,DD6 SETB P3.0; LCALL SIXUNHUAN DD6: LCALL AST RETURN:NOP AJMP INDEX DELAY:MOV R6,#13 DELAY1:MOV R5,#250;250 DELAY2:NOP DJNZ R5,DELAY2 DJNZ R6,DELAY1 RET AST: CLR ET0 SETB ET1 MOV TL1,#0E0H MOV TH1,#03CH SETB TR1 MOV R4,#20 MOV R3,#9 AJMP $ SIXUNHUAN:CLR EA SJMP $ INTT0:MOV TL0,#0B0H MOV TH0,#03CH DJNZ R1,LOOP1 MOV R1,#20 DJNZ R2,LOOP2 MOV A,#0 MOV DPTR,#TBB MOVC A,@A+DPTR MOV P2,A CLR EA SJMP $ LOOP2:MOV A,R2 MOV DPTR,#TBB MOVC A,@A+DPTR MOV P2,A LOOP1:RETI INTT1:MOV TL1,#0B0H MOV TH1,#03CH DJNZ R4,LOOP4 MOV R4,#20 DJNZ R3,LOOP MOV A,#0 MOV DPTR,#TAB MOVC A,@A+DPTR MOV P2,A CLR EA SJMP $ LOOP: MOV A,R3 MOV DPTR,#TBB MOVC A,@A+DPTR MOV P2,A LOOP4:RETI TAB: DB 3FH,06H,5BH,4FH,66H,6DH,7DH,07H,7FH,6FH DB 77H,7CH,39H,5EH,79H,71H END 四.心得体会 课程设计,我认为最重要的就是做好设计的预习,认真的研究老师给的题目,老师对实验的讲解要一丝不苟的去听去想。要重视程序的模块化,修改的方便,也要注重程序的调试,掌握其方法。硬件的设计跟焊接都要我们自己动手去焊,软件的编程也要我们不断的调试,最终一个能完成课程设计的劳动成果出来了。 在实训过程中,也暴露了许多问题. 不够细心焊错了线,由于对课本理论的不熟悉导致编程出现错误等等.但我们必须有有足够的挑战困难的勇气. 通过这两周的实训,我学习到了很多从前没有接触过的知识,使我眼界打开,感受颇深。基本的动手能力是一切工作和创造的基础和必要条件。 通过实训,同学们的友谊也增进了不少,很多不太懂的地方在同学们的帮助下完成了。 我们兢兢业业的老师,他们也顶着酷热和我们一起忙活,看着围在他身边的那一圈圈的人,他也总会耐心的为我们讲解,直到我们听懂为止。 最后我希望我们班能在以后的生活、学习中表现得更出色,更团结。老师们能够笑脸常开,万事如意!