锁相技术 第3章

- 格式:ppt

- 大小:3.19 MB

- 文档页数:79

摘要随着通信及电子系统的飞速发展,促使集成锁相环和数字锁相环突飞猛进。

本次毕业设计的主要任务是,采用0.18μm CMOS工艺,设计实现一个基于改进的鉴频鉴相器,压控振荡器,环路滤波器的全集成的CMOS PLL锁相环电路,设计重点为PLL锁相环电路的版图设计,设计工具为Laker。

本论文介绍了PLL锁相环电路的基本原理以及其完整的版图设计结果。

本次设计表明,采用该方案实现的锁相环电路主要功能工作正常,初步达到设计要求。

关键词:PLL锁相环电路,鉴频鉴相器,压控振荡器,环路滤波器,版图设计,0.18μm CMOS工艺AbstractWith the development of the communications and electronic systems, the technology of the integrated PLL and digital PLL develops rapidly.The main task of graduation is to design and realize a fully integrated CMOS PLL circuit which is based on an improved phase detector, VCO, loop filter using the 0.18μm CMOS technology. The design focus on the layout of the PLL circuit, and the design tools is the Laker.This paper introduces the basic principles of PLL phase locked loop circuit and its comprehensive layout results. This design shows that the program implemented by the main function of PLL circuit is working well, and it meets the design requirements.Key words:PLL phase locked loop circuits, popularly used phase detectors, discrimination, VCO loop filter, layout design, 0.18 μm CMOS process目录摘要 (1)Abstract (2)第1章绪论 (4)1.1 锁相技术的发展 (4)1.2 锁相环路的主要特性 (4)1.3 PLL锁相环的应用领域 (5)第2章基于CMOS锁相环的电路设计 (7)2.1 锁相环的基本组成 (7)2.2 锁相环工作原理 (7)2.3 鉴相器 (8)2.3.1 鉴频鉴相器(PFD) (9)2.3.2 鉴频鉴相器设计 (10)2.4 环路滤波器 (10)2.5 压控振荡器 (11)第3章关于COMS锁相环的版图设计 (12)3.1 电路设计 (12)3.2 版图设计 (12)3.2.1 版图设计规则检查 (13)3.2.2 注意事项 (13)3.3 锁相环的版图设计 (15)第4章结束语 (17)参考文献 (18)致谢 (19)第1章绪论1.1锁相技术的发展锁相技术起源于20世纪30年代,提出无线电调幅信号的锁相同步检波技术。

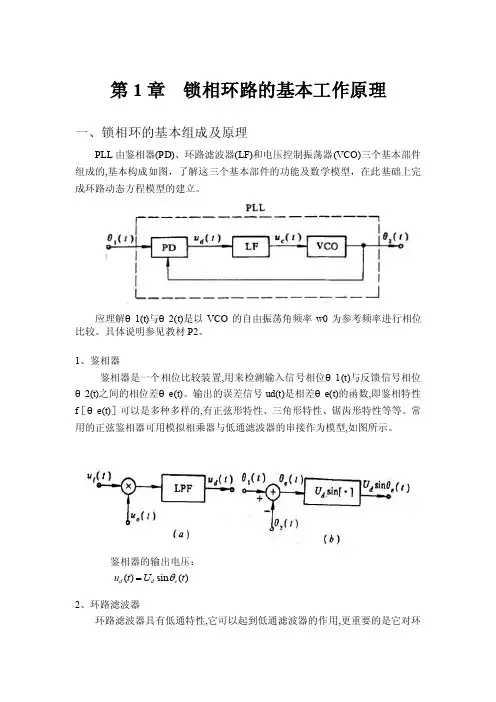

第1章 锁相环路的基本工作原理一、锁相环的基本组成及原理PLL 由鉴相器(PD)、环路滤波器(LF)和电压控制振荡器(VCO)三个基本部件组成的,基本构成如图,了解这三个基本部件的功能及数学模型,在此基础上完成环路动态方程模型的建立。

应理解θ1(t)与θ2(t)是以VCO 的自由振荡角频率w0为参考频率进行相位比较。

具体说明参见教材P2。

1、鉴相器鉴相器是一个相位比较装置,用来检测输入信号相位θ1(t)与反馈信号相位θ2(t)之间的相位差θe(t)。

输出的误差信号ud(t)是相差θe(t)的函数,即鉴相特性f [θe(t)]可以是多种多样的,有正弦形特性、三角形特性、锯齿形特性等等。

常用的正弦鉴相器可用模拟相乘器与低通滤波器的串接作为模型,如图所示。

鉴相器的输出电压:2、环路滤波器环路滤波器具有低通特性,它可以起到低通滤波器的作用,更重要的是它对环()sin ()d d e u t U t θ=路参数(如环路稳定性、环路单边噪声带宽、环路捕获时间等)调整起着决定性的作用。

环路滤波器是一个线性电路,在时域分析中可用一个传输算子F(p)来表示,其中p(≡d /dt)是微分算子;在频域分析中可用传递函数F(s)表示,其中s(a+j Ω)是复频率;若用s=j Ω代入F(s)就得到它的频率响应F(j Ω)。

主要了解RC 积分滤波器、无源比例积分滤波器及有源比例积分滤波器这三类环路滤波器的电路形式及传输函数。

a 、 R C 积分滤波器:式中τ1=RC 是时间常数,这是这种滤波器唯一可调的参数。

滤波器的频率特 性b 、无源比例积分滤波器式中τ1=(R1+R2)C ;τ2=R2C 。

这是两个独立的可调参数,其频率响应为c 、有源比例积分滤波器式中τ1=(R1+AR1+R2)C ;τ2=R2C ;A 是运算放大器无反馈时的电压增益。

若A 很大则有不考虑负号的影响,因为负号表示,鉴相器工作在鉴相器特性曲线斜率为负的那一段。

基于Matlab的锁相环设计摘要随着现代集成电路技术的发展,锁相环已经成为集成电路设计中非常重要的一个部分,所以对锁相环的研究具有积极的现实意义。

锁相环电路是一种输出信号在频率和相位上能够与输入参考信号同步的电路,锁相环由于其具有一系列独特的优良性能,它已经成为通信、雷达、导航、电子仪器仪表等设备中不可缺少的一部分。

所以这些年来锁相环的设计与研究工作也越来越受到人们的重视,人们开始利用人工计算或计算机软件来分析锁相环的性能。

在研究大量资料的基础之上,先对锁相系统的基本工作原理进行了分析,以传统模拟锁相环的结构为基础,分析了锁相环的数学模型,详细描述了锁相环的整体电路以及鉴相器、环路滤波器、压控振荡器等电路模块。

并以此为出发点对锁相环的锁定性能、及稳定性能、等各种性能进行了分析。

在分析和设计的同时,也采用Matlab软件对锁相环电路进行了仿真。

首先分析了一阶锁相环和二阶锁相环的锁定性能,并进行了比较。

其次分析了阻尼系数 对环路稳定性能的影响。

最后介绍了锁相环的调制作用。

从锁相环的仿真结果可知,我们的理论研究结果和实验结果相符,锁相环电路达到了设计指标要求。

关键词锁相环;Matlab;仿真Phase-Locked Loop Design Based on MatlabAbstractWith the development of modern integrated circuit technology, phase locked loop has become a significant component of integrated circuit, which makes the research of phase-locked loop valuable. Phase-locked loop is a kind of circuit that an output signal in the frequency and phase reference signal can be synchronized with the input. Because of a series of uniquely excellent performances, it is becoming an indispensable part of the equipments such as communication, radar, airmanship, electronic instrument etc. People realize the importance of the design and study of PLL , they come to use artificially calculation or software to analyze the property of PLL.After a deep study of the materials about PLL, this thesis starts with the analysis of the fundamental principles of a phase-locked system , then we build the mathematical model based on the traditional of the PLL, describes the overall PLL circuit and phase detector, loop filter, VCO circuit module, etc, and afterwards investigate some of its characters such as locking performance and stability.In the analysis and design, but also we conducted a phase locked loop circuit simulation by Matlab software. First of all, we analyzed the first-order phase lock loop and a second order phase-locked loop lock performance, and on the basis of the comparison. Secondly we analyzed the damping how to stability of the loop. Finally we introduced the modulation of the phase locked loop. From the simulation results, we know that the theory conclusions and the simulation results fit well phase-locked loop circuit to the design requirements.Keywords PLL, simulation, Matlab目录摘要 (I)Abstract (II)第1章绪论 (1)1.1 课题背景及研究意义 (1)1.2 发展历程 (2)1.3 国内外发展现状 (3)1.4 锁相环的应用 (4)1.4.1 频率合成 (5)1.4.2 时钟产生器 (5)1.4.3 时钟恢复电路 (5)1.4.4 偏移减小 (6)1.5 本文的章节安排及主要内容 (6)第2章锁相环理论 (7)2.1 基本理论 (7)2.2 基本模块 (8)2.2.1 鉴相器 (8)2.2.2 环路滤波器 (10)2.2.3 压控振荡器 (11)2.3 环路的相位模型及基本方程 (12)2.4 环路性能 (12)2.4.1 线性化相位模型和传递函数 (13)2.4.2 锁定状态下锁相环的动态特性 (14)2.5 本章小结 (16)第3章锁相环仿真 (17)3.1 Matlab软件介绍 (17)3.2 锁定性能 (18)3.2.1 一阶锁相环 (18)3.2.2 二阶锁相环 (19)3.2.3 一阶锁相环与二阶锁相环比较 (21)3.3 环路性能 (21)3.3.1 鉴相器的输出 (22)3.3.2 低通滤波器的输出 (23)3.3.3 压控振荡器的输出 (24)3.4 稳定性能 (25)3.5 调制作用 (27)3.6 本章小结 (28)结论 (29)致谢 (30)参考文献 (31)附录A (33)附录B (36)第1章绪论1.1课题背景及研究意义在现代集成电路中,锁相环(Phase Locked Loop)是一种广泛应用于模拟、数字及数模混合电路系统中的非常重要的电路模块。

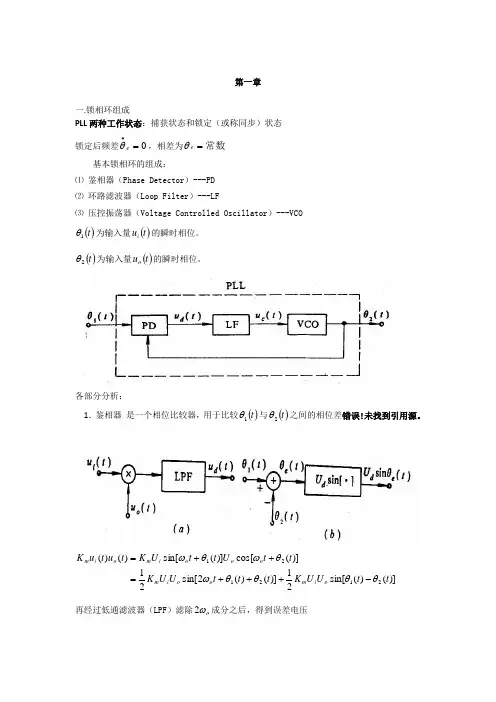

第一章一.锁相环组成PLL 两种工作状态:捕获状态和锁定(或称同步)状态 锁定后频差0=∙e θ,相差为常数=e θ基本锁相环的组成:⑴ 鉴相器(Phase Detector )---PD ⑵ 环路滤波器(Loop Filter )---LF⑶ 压控振荡器(Voltage Controlled Oscillator )---VCO()t 1θ为输入量()t u i 的瞬时相位。

()t 2θ为输入量()t u o 的瞬时相位。

各部分分析:1.鉴相器 是一个相位比较器,用于比较()t 1θ与()t 2θ之间的相位差错误!未找到引用源。

)]()(sin[21)]()(2sin[21)](cos[)](sin[)()(212121t t U U K t t t U U K t t U t t U K t u t u K o i m o o i m o o o i m o i m θθθθωθωθω-+++=++= 再经过低通滤波器(LPF )滤除o ω2成分之后,得到误差电压)]()(sin[21)(21t t U U K t u o i m d θθ-=令 o i m d U U K U 21=为鉴相器的最大输出电压,得到)](sin[)(t U t u e d d θ= 2.环路滤波器及其传输函数环路滤波器是一个线性电路,在时域分析中可用一个传输算子)(p F 来表示,其中)(dt d p ≡是微分算子;在频域分析中可用传递函数)(s F 表示,其中)(Ω+=j s α是复频率;若用Ω=j s 代入就得到它的频率响应)(Ωj F ,故环路滤波器模型可表示为图定义控制电压 ()()()p F t u t u d c =(1)RC 积分滤波器这是结构最简单的低通滤波器, 传输算子:111)(τp p F +=,RC =1τ是时间常数,这是这种滤波器唯一可调的参数。

令p=j Ω,并代入(1-18)式,即可得滤波器的频率特性:111)(τΩ+=Ωj j F低通特性,相位滞后。

第一章 绪论1.1 锁相环路锁相环路(PLL)是一个能够跟踪输入信号相位的闭环自动控制系统,它在无线电 技术的各个领域得到了很广泛的应用。

锁相环路有其独特的优良性能,它具有载波跟踪特 性,作为一个窄带跟踪滤波器,可提取淹没在噪声之中的信号;用高稳定的参考振荡器锁 定,可作提供一系列频率高稳定的频率源;可进行高精度的相位与频率测量等等。

它具有 调制跟踪特性,可制成高性能的调制器和解调器。

它具有低门限特性,可大大改善模拟信 号和数字信号的解调质量。

70 年代以来,随着集成电路技术的发展,逐渐出现了集成的 环路部件、通用单片集成锁相环路以及多种专用集成锁相环路,锁相环路逐渐变成了一个 成本低、使用简便的多功能组件,这就为锁相技术在更广泛的领域应用提供了条件。

锁相环是一个相位误差控制系统。

它比较输入信号和振荡器输出信号之间的相位差, 从而产生误差控制信号来调整振荡器的频率,以达到与输入信号同频同相。

所谓全数字锁 相环路(DPLL)就是环路部件全部数字化, 采用数字鉴相器 (DPD)、 数字环路滤波器(DLF)、 数控振荡器(DCO)构成的锁相环路。

本文采用锁相式频率合成的实现方法, 实现中必须解决的关键技术问题是减小相位噪 声,以满足用户提出的较为苛刻的相位噪声指标。

本课题是设计一个由单片机、 定时计数器及单片机集成锁相环路组成的可程控频率合 成器,所以设计过程会涉及到锁相环路、频率合成器和单片机方面的知识。

1.2 锁相技术发展锁相原理在数学理论方面,早在 30 年代无线电技术发展的初期就己出现。

1930 年 己建立了同步控制理论的基础。

1932 年贝尔赛什(Bellescize)第一次公开发表了锁相环路的 数学描述,用锁相环路提取相干载波来完成同步检波。

到了 40 年代,电视接收机的同步 扫描电路中开始广泛地应用锁相技术,使电视图像的同步性能得到很大改善。

进入 50 年 代,随着空间技术的发展,由杰斐(Jaffe)和里希廷(Rechtin)利用锁相环路作为导弹信标的 跟踪滤波器获得成功,并首次发表了包含噪声效应的锁相环路线性理论分析的文章,同时 解决了锁相环路最佳化设计问题。

北 京 大 学硕士研究生学位论文CMOS锁相环和延迟锁环设计与研究*名:***学号: ********系别:计算机科学与技术系专业:微电子学与固体电子学研究方向:专用集成电路设计导师:吉利久教授二〇〇二年五月声明著作权声明任何收存和保管本论文各种版本的单位和个人,未经本论文作者授权,不得将本论文转借他人并复印、抄录、拍照、或以任何方式传播。

否则,引起有碍作者著作权益之问题,将可能承担法律责任。

原创性声明本人郑重声明:所呈交的学位论文,是本人在导师的指导下,独立进行研究工作所取得的成果。

除文中已经注明引用的内容外,本论文不包含任何其他个人或集体已经发表或撰写过的作品成果。

对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。

本人完全意识到本声明的法律结果由本人承担。

作者:窦训金日期:2002年5月12日摘要锁相环作为现代时钟电路的重要组成部分,已经成为超大规模集成电路中必不可少的一个模块,几乎所有的数字集成电路中都采用锁相时钟产生电路来提供片内高速时钟。

随着SoC技术的出现,作为IP建库的重要内容,对锁相环电路的研究和设计也具有了更加重要的意义。

本文首先简要介绍了锁相技术的历史和发展,及其现状与研究方向。

第二章中对锁相环的原理和各种特性进行了详细的介绍,主要包括相位/频率响应、稳定性和噪声特性等方面的分析。

第三章给出了各种典型的锁相环子模块电路和系统结构,重点介绍了鉴频鉴相器、电荷泵和压控振荡器这三个主要模块。

第四章中,提出了几种新型锁相环子模块电路结构,包括改进的双边鉴频鉴相器、新型电流型压控振荡器和新型延迟锁环频率合成电路,同时分别对它们的性能进行了分析,并将之与典型电路结构加以比较。

最后,对整个锁相环的设计和研究进行了总结。

本文设计的锁相频率合成器采用上海贝岭1.2µm CMOS工艺实现,完成了全部电路的设计、仿真及版图的设计,并通过了版图提取和后仿真。

关键词:锁相环、时钟产生、频率合成、鉴频鉴相器、电荷泵、压控振荡器、相位噪声、延迟锁环AbstractAs one important part of modern clock generator circuits, PLL (Phase Locked Loop) has played an extremely important role in VLSI circuits. Today, in most digital ICs, PLL clock generators are used to provide on-chip high-speed clock. For recently-emerged SoC (System on a Chip) technology, PLL circuit, as an important IP block, is well worthy of further design and research.In this paper, we firstly introduce the history and evolution of phase locked technologies as well as the state of the art in it. The second chapter presents the principle and main features of PLL, including the analysis of phase/frequency response, stability and phase noise, etc. Some typical sub-circuit blocks are described in chapter three, mainly on PFD (Phase/Frequency Detector), CP (Charge Pump) and VCO (V oltage-Controlled Oscillator). In chapter four, novel sub-circuit blocks are presented, including an improved biPFD, a new current-mode VCO and a new DLL (Delay-Locked Loop) frequency synthesizer. Their operations and features are also analyzed as well as compared with other typical circuits. At last, a conclusion is followed.All the design is based on Shanghai Belling 1.2µm CMOS technology. We have finished the circuits design, simulation and layout design, also passed DRC, ERC, LVS and post-simulation on design corners.Key Words:Phase Locked Loop、Clock Generator、Frequency Synthesizer、Phase/Frequency Detector、Charge Pump、V oltage-ControlledOscillator、Phase Noise、Delay-Locked Loop目录第一章引言 (1)§1锁相技术的基本概念 (1)§2锁相技术的历史和发展 (1)§3锁相环路的基本特征 (2)§4锁相技术的现状和研究方向 (3)第二章锁相环路基本原理与分析 (5)§1锁相环的组成 (5)1.1 基本结构 (5)1.2 鉴相器 (5)1.3 环路滤波器 (7)1.4 压控振荡器 (7)§2环路相位模型和基本方程 (9)§3锁相环路的频率响应和稳态相差 (10)3.1 频率响应 (10)3.2 稳态相差 (10)3.3 不同环路的频率响应和稳态相差 (12)§4锁相环路的同步、跟踪和捕捉 (17)4.1 同步过程 (17)4.2 捕捉过程 (18)§5 锁相环稳定性分析 (20)5.1 锁相环稳定性的概念 (20)5.2 稳定性判据 (20)5.3 几种环路的稳定性条件 (22)§6锁相环噪声分析 (24)6.1 环路噪声的概念 (24)6.2 环路噪声注入模型 (25)6.3 减小环路噪声的措施 (25)§7电荷泵锁相环 (26)7.1 电荷泵锁相环结构 (26)7.2 环路基本方程 (26)7.3 环路稳定性分析 (27)§8延迟锁环 (30)§9小结 (31)第三章锁相环子模块电路结构 (34)§1鉴频鉴相器 (34)1.1 基于触发器型的鉴频鉴相器 (34)1.2 预充电式鉴频鉴相器(ptPFD) (35)1.3 nc-级鉴频鉴相器(ncPFD) (37)§2电荷泵 (39)2.1 传统电荷泵结构 (39)2.2 差分式电荷泵 (41)2.3 对称负载的电荷泵结构 (42)§3各种压控振荡器结构 (43)3.1 反相器型压控振荡器 (43)3.2 电流模压控振荡器 (43)3.3 差分型压控振荡器 (45)§4小结 (49)第四章锁相环和延迟锁环电路设计 (51)§1鉴频鉴相器设计 (51)1.1 单边鉴频鉴相器和双边鉴频鉴相器电路结构 (51)1.2 upPFD、dnPFD和biPFD鉴相特性比较 (53)1.3 upPFD、dnPFD和biPFD的优缺点 (54)1.4 改进的双边鉴频鉴相器 (55)1.5 新型biPFD和原有biPFD仿真结果比较 (60)§2电荷泵设计 (62)§3环路滤波器设计 (65)§4压控振荡器设计 (66)4.1 简单电流型压控振荡器 (66)4.2 电流型压控振荡器结构改进 (68)§5环路仿真结果 (71)§6延迟锁环频率合成研究 (74)6.1 延迟锁环(DLL)频率合成原理 (74)6.2 频率合成电路结构 (75)6.3 新型频率合成电路 (78)§7小结 (79)第五章结论 (82)致谢 (83)第一章引言§1锁相技术的基本概念锁相是相位锁定的简称,其具体含义是相位同步的自动控制,或者说是利用相位自动调节的方法实现两个信号的相位同步。

锁相技术复习要点第1章 锁相环路的基本工作原理一、考核知识点(一)锁相环路的基本工作原理;(二)锁相环路的相位数字模型及其微分方程;(三)锁相环路的基本性能。

二、考核要求(一)锁定与跟踪的概念1、识记:(1)相位的概念;(2)锁相环路的定义;(3)环路的捕获带(4)环路的同步带。

2、领会:(1)锁相环路是一个相位跟踪系统,它建立了输出信号瞬时相位与输入信号瞬时相位的控制关系(2)几个重要参数:载波相位、瞬时相位、自由振荡角频率、瞬时相差、移稳态相差;(3)环路的两种基本工作状态:捕获过程、锁定状态。

3、应用:(1)环路是处于锁定状态的判定依据;(2)一阶环稳态相差的计算。

(二)环路组成1、识记:(1)环路的基本部件;(2)鉴相器的作用与数学模型;(3)鉴相器的分类:模拟乘法器鉴相器、序列电路(数字鉴相器);(4)环路滤波器的作用与数学模型;(5)压控振荡器的作用与数学模型;(6)压控灵敏度;(7)压控振荡器的种类。

2、领会:(1)锁相环路的组成及框图;(2)正弦鉴相器及数学模型;(3)几种常用的环路滤波器及传递函数;(4)锁相环路的相位数学模型。

3、应用;(1)理想积分滤波器分析;(2)非常用环路滤波器的传递函数求解。

(三)环路的动态方程1、 识记:(1)瞬时频差;(2)控制频差;(3)固有频差;(4)环路增益K。

2、 领会:(1)锁相环路动态方程3、应用:(1)锁相环路动态方程的含意;(2)稳态相差的求解。

(四)一阶环路的捕获、锁定与失锁。

1、识记:(1)一阶环路;(2)相点;(3)相轨迹(4)相平面。

2、领会:(1)一阶环路的非线性微分方程;(2)相轨迹上相点的含义。

3、应用:(1)频率牵引现象;(2)一阶环路的捕获带、同步带、快捕带。

第二章 环路跟踪性能一、考核知识点(一)锁相环路的线性相位模型及传递函数;(二)锁相环路的性能指标;(三)二阶环路在典型输入下的响应;(四)环路的频率响应。

第一章 锁相环路的基本工作原理1-3 已知一阶环的 U =2V , K =15KHz/V , / 2 =2MHz ,问当输入频率分别为 d 0 0 1.98MHz 和 2.04MHz 的载波信号时,环路能否锁定?稳定相差多大? 解:U 2V , K 0 d15k rad s V 2 , 2 2M rad/s2 1.98M rad/s , 2 2.04M rad/s1 2 环路能够锁定的条件是 K固有频差 1: 2 ( 0.02)M 2 20k rad/s 01 1 0 固有频差 2: 2 0.04M 2 40k rad/s 02 2 0 环路增益: K U K 2 2 15k 2 30k rad/s d 0 对 处于同步带内,即 K ,环路锁定。

01 01 对 处于同步带外,即 K ,环路失锁。

02 02 01 arcsin 2 41.8 稳态相差 arc sine42。

K 3 1-4 已知一阶环的U =0.63V , K =20kHz/V , f =2.5MHz ,在输入载波信号作用下环 d 0 0 路锁定,控制频差等于 10KHz 。

问:输入信号频率 为多大?环路控制电压u (t ) =?稳态 i c 相差 ( ) =?e解: K 0220k rad/ s V , 控制 2 10k rad/s ,环路增益 K U K 0.63 2 20K 2 12.6k rad/s d 0环路锁定时,固有频差等于控制频差,即 = 控制 2 10 k rad/s =f 0 2.5MHz , = 2 2500K rad/s固有频差 0 0 i= 2 2500k+2 10K = 2 2510k =5.02 10 6rad/si 0 0f 2.51MHzi2 10K 0.5V2 20K因为 控制 u t K 0 控制电压u t Kc c 02 10k 10sin e 2 12.6k 0.790 K 12.6 稳态相差earcsin 0.79 52.5 1-5 一阶环,设开环时u i (t ) 0.2sin 2 10 t (V ),u (t ) cos 2 10 t (V )3 4 i 0式中 、 为常数。

第一章锁相环路的基本工作原理:1.锁相环路是一个闭环的相位控制系统;锁相环路(PLL)是一个相位跟踪系统,它建立了输出信号顺时相位与输入信号瞬时相位的控制关系。

2. 若输入信号是未调载波,θi(t)即为常数,是u i(t)的初始相位;若输入信号时角调制信号(包括调频调相),θi(t)即为时间的函数。

3.ωo是环内被控振荡器的自由振荡角频率;θo(t)是以自由振荡的载波相位ωo t为参考的顺时相位,在未受控制以前它是常数,在输入信号控制之下,θo(t)即为时间的函数。

4. 输入信号频率与环路自由振荡频率之差,称为环路的固有频率环路固有角频差:输入信号角频率ωi与环路自由振荡角频率ωo之差。

瞬时角频差:输入信号频率ωi与受控压控振荡器的频率ωv之差。

控制角频差:受控压控振荡器的频率ωv与自由振荡频率ωo之差。

三者之间的关系:瞬时频差=固有频差-控制频差。

5. 从输入信号加到锁相环路的输入端开始,一直到环路达到锁定的全过程,称为捕获过程。

6. 对一定环路来说,是否能通过捕获而进入同步完全取决于起始频差。

7. 锁定状态又叫同步状态:①同频②相位差固定8. 锁定之后无频差,这是锁相环路独特的优点。

9. 捕获时间T p的大小除决定于环路参数之外,还与起始状态有关。

10.若改变固有频差∆ωo,稳定相差θe(∞)会随之改变。

11.锁相环路基本构成:由鉴相器(PD)、环路滤波器(LF)和电压控制振荡器(VCO)组成。

12.鉴相器是一个相位比较装置,鉴相器的电路总的可以分为两大类:第一类是相乘器电路,第二类是序列电路。

13.环路滤波器具有低通特性。

常见的环路滤波器有RC积分滤波器、无源比例积分滤波器和有源比例积分滤波器三种。

(会推导它们的传输算子)14.电压振荡器是一个电压-频率变换装置,它的振荡频率应随输入控制电压u c(t)线性的变化。

15.压控振荡器应是一个具有线性控制特性的调频振荡器。

要求压控振荡器的开环噪声尽可能低,设计电路时应注意提高有载品质因素和适当增加振荡器激励功率,降低激励级的内阻和振荡管的噪声系数。