YCL-DSP2812-Pro硬件电路详解

- 格式:pdf

- 大小:1.53 MB

- 文档页数:17

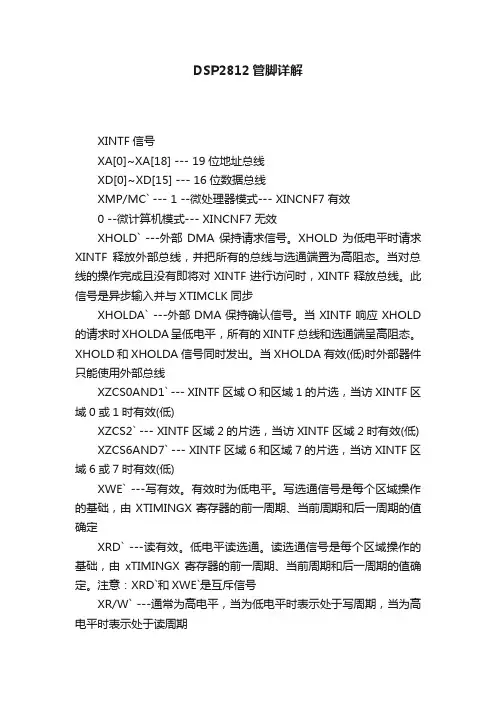

DSP2812管脚详解XINTF信号XA[0]~XA[18] --- 19位地址总线XD[0]~XD[15] --- 16位数据总线XMP/MC` --- 1 --微处理器模式--- XINCNF7有效0 --微计算机模式--- XINCNF7无效XHOLD` ---外部DMA保持请求信号。

XHOLD为低电平时请求XINTF释放外部总线,并把所有的总线与选通端置为高阻态。

当对总线的操作完成且没有即将对XINTF进行访问时,XINTF释放总线。

此信号是异步输入并与XTIMCLK同步XHOLDA` ---外部DMA保持确认信号。

当XINTF响应XHOLD 的请求时XHOLDA呈低电平,所有的XINTF 总线和选通端呈高阻态。

XHOLD和XHOLDA信号同时发出。

当XHOLDA有效(低)时外部器件只能使用外部总线XZCS0AND1` --- XINTF区域O和区域1的片选,当访XINTF区域0或1时有效(低)XZCS2` --- XINTF区域2的片选,当访XINTF区域2时有效(低) XZCS6AND7` --- XINTF区域6和区域7的片选,当访XINTF区域6或7时有效(低)XWE` ---写有效。

有效时为低电平。

写选通信号是每个区域操作的基础,由XTIMINGX寄存器的前一周期、当前周期和后一周期的值确定XRD` ---读有效。

低电平读选通。

读选通信号是每个区域操作的基础,由xTIMINGX寄存器的前一周期、当前周期和后一周期的值确定。

注意:XRD`和XWE`是互斥信号XR/W` ---通常为高电平,当为低电平时表示处于写周期,当为高电平时表示处于读周期XREADY ---数据准备输入,被置1表示外设已为访问做好准备。

XREADY可被设置为同步或异步输入。

在同步模式中,XINTF接口块在当前周期结束之前的一个XTIMCLK时钟周期内要求XREADY有效。

在异步模式中,在当前的周期结束前XINTF接口块以XTIMCLK的周期作为周期对XREADY采样3次。

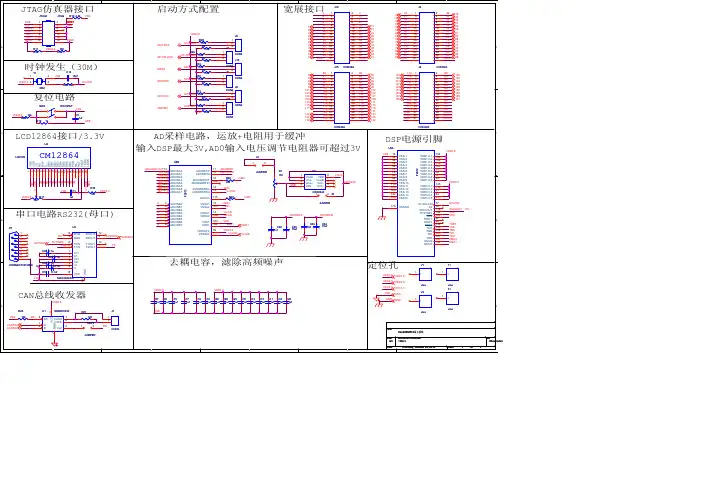

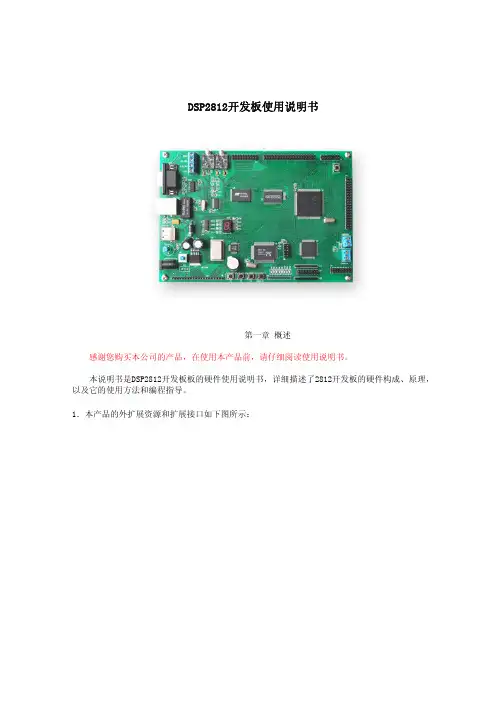

开发板DSP2812原理框图及各部分分析开发板DSP2812原理框图及各部分分析T-DSP2812开发板主要集成了RS232接口、CAN 接口、网络接口、PS2接口、12864液晶接口、ADC 接口、EEPROM 、蜂鸣器、1×4键盘、流水灯等电路,囊括了几乎所有的常用接口和应用电路。

基本单元测试程序包括以下几个部分:1.蜂鸣器程序。

2 流水灯程序;3 1×4独立式按键输入显示程序;4 DSP 通过PS2端口接收显示键盘输入数据程序;5 SO12864液晶显示画面程序;6 DSP 通过RS232接口与PC 机通信程序;7 DSP 通过USB 接口与PC 机通信程序;8 PC 机通过网络接口(RJ45)和DSP 通信程序;9 256K × 16 SRAM 读写程序;10 读写EEPROM 程序开发板DSP2812原理框图如图1所示:LED 显示液晶显示10K*8 UART图1 DSP2812原理框图一.电源电路TMS320F2812采用高性能静态CMOS技术,I/O供电电压及FLASH编程电压为3.3V,内核供电电压降为1.8V(135MHz)或1.9V(150MHz),故本开发板选用TI公司的双路输出低压降(LDO)稳压器TPS767D318,将输入的5V 直流电压稳压输出一路为3.3V,一路为1.8V,每路最大输出电流为1A。

为了抑制电源线上的高频噪声和尖峰干扰,降低数字噪声对模拟电路的干扰,模拟电源和数字电源、模拟地和数字地都采用磁珠隔离。

同时板上5V、3.3V、1.8V电压都采用发光二极管指示电源状态,方便用户使用。

二.按键电路TMS320F2812采用高性能静态CMOS技术,I/O供电电压及FLASH编程电压为3.3V,内核供电电压降为1.8V(135MHz)或1.9V(150MHz),故本开发板选用TI公司的双路输出低压降(LDO)稳压器TPS767D318,将输入的5V 直流电压稳压输出一路为3.3V,一路为1.8V,每路最大输出电流为1A。

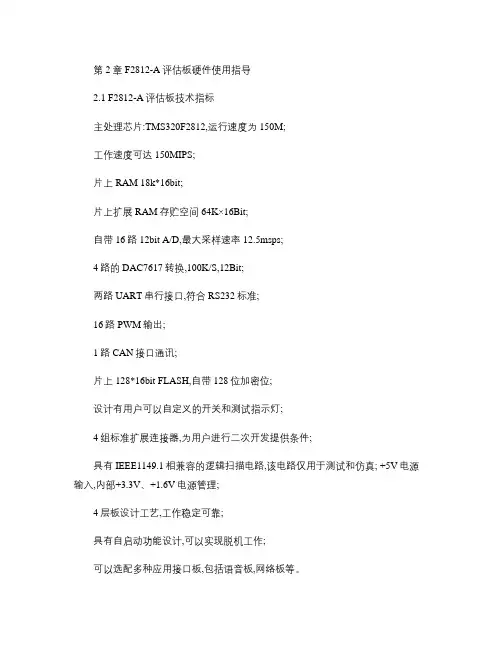

第2章F2812-A评估板硬件使用指导2.1 F2812-A评估板技术指标主处理芯片:TMS320F2812,运行速度为150M;工作速度可达150MIPS;片上RAM 18k*16bit;片上扩展RAM存贮空间64K×16Bit;自带16路12bit A/D,最大采样速率12.5msps;4路的DAC7617转换,100K/S,12Bit;两路UART串行接口,符合RS232标准;16路PWM输出;1路CAN接口通讯;片上128*16bit FLASH,自带128位加密位;设计有用户可以自定义的开关和测试指示灯;4组标准扩展连接器,为用户进行二次开发提供条件;具有IEEE1149.1相兼容的逻辑扫描电路,该电路仅用于测试和仿真; +5V电源输入,内部+3.3V、+1.6V电源管理;4层板设计工艺,工作稳定可靠;具有自启动功能设计,可以实现脱机工作;可以选配多种应用接口板,包括语音板,网络板等。

2.2 F2812 –A 评估板原理图和实物图一. F2812-A 评估板实物图图2.2.2 F2812-A 器件分布图图2.2.1 F2812-A 评估板实物图二. F2812-A 器件分布图图1.2 ICETEK-F2812-A 器件分布图三.F2812-A评估板原理框图图2.2.3 F2812-A评估板原理框图2.3 F2812-A评估板接口说明以下将详细说明这些外围接口的功能和特征定义。

首先,表2-3-1 归纳总结了这些跳线和功能分类,接口位置请参考图2.2.1表2-3-1:接口和功能分类下面将分别介绍这些接口:1. +5v 电源插座: 这个接口用于接入为整个板子供电的电源,电源电压为+5V ,标准配置的电源电流为1A ,如果不使用随板提供的电源,请注意电源的正负极性和电流的大小。

下面是这个接口的插孔示意图:+5V地(GND图2.3.1 电源插孔示意图2. 标准RS-232: 9针D 型连接器,异步串口连接器,符合RS-232规范,输出电平为正负12V .下面是9针连接器的管脚定义:图2.3.2 异步串口连接器示意图3.P1扩展插座:34芯扩展总线接口。

DSP2812程序运⾏过程学习总结DSP2812程序运⾏过程学习总结⼀、2812的上电运⾏过程以下是2812上电(复位)后运⾏过程的描述:1:上电运⾏时根据MP/MC引脚的状态决定是从⽚外的3fffc0处读取复位向量或者时从⽚内的rom的3fffc0处读取复位向量。

MC ⽅式下从⽚内读取,MP⽅式下从⽚外读取。

2:⼀般我们⽤的是MC⽅式,即从⽚内读取复位向量,在⽚内的rom 3fffc0处有⼀个地址为3ffc00。

3:复位后处理器从3fffc0处读取3ffc00这个地址,所以程序从3ffc00处开始执⾏4:3ffc00处开始的就是initboot过程,根据IO管教的状态判断该进⼊那⼀种引导⽅式5:在SCITXA引脚为⾼电平时就是flash boot⽅式,此时置PC=3F7FF6SCITXA引脚有内部上拉,所以只要没有强制下拉的话,DSP检测的都是⾼电平。

对于通讯不影响。

SCITXA不⽤在外部上拉。

不能直接接到⾼电平上。

6:在⽚内flash的3F7FF6和3F7FF7处有⼀个跳转指令,该跳转指令就是LB _c_int007:执⾏这个跳转指令后程序就开始运⾏c_int00这个函数了8:这个函数就是建⽴⼀个c程序的运⾏环境,等建⽴完c运⾏环境后c_int00调⽤main函数9:main函数开始就是我们⾃⼰编写的应⽤程序了。

⼆、CMD⽂件介绍DSP开发过程中,编译器⽣成的代码和数据要由链接器分配到合适的存储空间,通常链接器的命令⽂件.cmd⽂件是由⽤户⾃⼰编写的,编写不当,就会使仿真开发不能进⾏。

1存储空间的配置TMS320F2812的DSP存储器分为三个独⽴选择的空间-程序空间、数据空间和I/O空间,其中程序存储器存放待执⾏的指令和执⾏中所⽤的系数(常数),可使⽤⽚内或⽚外的RAM、ROM或EPROM等来构成;数据存储器存放指令执⾏中产⽣的数据,可使⽤⽚内或⽚外的RAM和ROM来构成;I/O存储器存放与映象外围接⼝相关的数据,也可以作为附加的数据存储空间使⽤。

DSP2812教程(8)第4课F2812⽚内资源、存储器映射以及CMD⽂件的编写作者:顾卫钢谢芬(HELLODSP资深会员)从今天开始,我们的课程终于进⼊F2812的核⼼了,呵呵。

在今天的课程中,我们将带领⼤家⼀起学习2812的⽚内资源,初步了解它究竟有哪些本事,能拿来⼲些什么,然后⼀起了解2812存储器的结构,统⼀编址的⽅式、存储器映射关系,并重点分析CMD⽂件,以期望消除⼤家对CMD⽂件的迷惑,在⾃⼰编写程序的时候会修改CMD⽂件中的部分内容,从⽽满⾜⾃⼰设计时的需求。

1.F2812的⽚内资源我们知道,TMS320F2812是32位的定点DSP,它既具有数字信号的处理能⼒,⼜具有强⼤的事件管理能⼒和嵌⼊式控制功能,特别适合⽤于需要⼤批量数据处理的测控领域,例如⾃动化控制、电⼒电⼦技术、智能化仪表、电机伺服控制。

下⾯是F2812的内部资源框图。

图1 TMS320F2812内部资源框图2812采⽤了⾼性能的静态CMOS技术,时钟频率可达150MHZ(6.67ns),其核⼼电压为1.8V,I/O⼝电压3.3V,Flash编程电压也为3.3V,所以我们在设计2812电源部分的时候,需要将常⽤的5V电压转换成1.8V和3.3V的电压之后,才能供给2812。

具体的设计我们将会在以后的硬件设计内容⾥进⾏探讨。

让我们⼀起来看看图1,最左边的A(18-0)和D(15-0)是表⽰2812外扩存储器的能⼒,2812外扩的存储空间最⼤是219*16 bit,就是说最多只能扩512K个存储单元,每⼀个存储单元的位数为16位。

从图中我们也可以看到,F2812⽀持JTAG边界扫描(Boundary Scan),这也是为什么我们的仿真器都是采⽤JTAG⼝的原因了,在这⾥,提醒⼤家⼀点的就是,仿真的时候,JTAG⼝的⽅向不能插反,如果插反的话会将仿真器烧坏。

我们所使⽤的14针JTAG⼝的第6针是空脚,所以⼀般情况下仿真器JTAG线的第6针是填针的,同时在板⼦上的第6脚是拔空的,这样可以防⽌您插反JTAG⼝,以避免不必要的损失。

1

TTL 3.3V

CMOS5V

1.1.关于电平转换及兼容性问题

1.1.1.各种电平特性

1.1.

2.电平的兼容性问题

●相同供电电压的TTL器件驱动CMOS器件

×

●相同供电电压的CMOS器件驱动TTL器件

●不同供电电压的TTL器件驱动CMOS器件

●不同供电电压的CMOS器件驱动TTL器件,

不同供电电压的TTL器件在输入端具有5V容限的情况下可以直接接口;不同供电电压的CMOS器件由于电平不匹配不能直接接口。

1.1.3.电平转换常用方法

逻辑电平转换芯片74LVX4245

,

.

3.35, 3.3,

,5

3.3V5V

1.2.LDO电源电路

V333

●电源可由外部电源插孔提供,其中电源插孔5V Power标识为内正外负。

电压为直流5V,提供电流1A以上。

●AMS1117-3.3或AMS1084-3.3电源转换芯片(UP1)作为5V转3.3V的高性能稳压芯片,为这个开发板提供稳定可靠的主电源3.3V,由指示灯DP1指示。

●AMS1117-1.8电源转换芯片(UP3)提供的1..8V给DSP内核使用,由指示灯DP3指示。

该指示灯相对DP1和DP2要暗一点。

●AMS1117-3.3电源转换芯片(UP2)提供A3.3V是提供给F2812的AD 等模拟部分和AIC23的模拟部分使用的。

由指示灯DP2指示。

●其中的B100是500mA的自恢复保险,在过大电流的时候断开,可以自恢复。

●由于本开发板电流消耗比较大,建议用外部电源供电

1.3.MAX811复位电路

R10710K

VCC3V3

●芯片上电后自动输出最少140mS 低电平复位脉冲●复位按钮S100保证手工复位●当电压低于3.08V 时自动复位

●复位信号提供给F2812、CPLD EPM3128等1.4.时钟电路及PLL 模块

●锁相环(PLL )模块主要用来控制DSP 内核的工作频率,外部提供一个参考时钟输入,经过PLL 倍频或分频后提供给DSP 内核。

●2812 DSP 有4位倍频位,能够实现0.5~10倍的倍频。

●本开发板上采用的电路,采用的内部振荡器方式。

选用的外部晶振为20M 。

●内核工作频率由PLLCR 寄存器的bits [3:0]位确定。

对应的PLL 倍频或分频系数见下表

1.5.AD输入电路

AD

●DSP内置16通道12位ADC,可配置为2个独立的8通道模块,分别服务于事件管理器A和B

●DSP能接受的AD信号在0~3V,注意:外部输入电压值不能超出这个范围,否则很容易烧毁F2812

●ADC时钟可配置为25MHz,最高采样带宽为12.5MHz

●实验中,ADCLO电压可以接地或其他参考电压,ADINA0的输

入电压可以使SPI DA TLV5616输出或是可变电位器输入,或者是外部输入

P780

1-2ADINA0DA OUT

2-3ADINA0R780

1.6.SPI串行12位D/A转换电路

D/A TI SPI TLV561612D/A

DSP SPI MASTER DACS DAFS SPI_CS CPLD:

1.7.SPI 数码管电路

SPI

-SN74HC595

DSP SPI

MASTER

LED_CS#

SPI_CS

CPLD

VCC3V3

C751

104

VCC3V3

1.8.SPI 方式的SD 卡接口电路

●SD 卡工作模式为兼容的SPI 模式,工作在SLA VE 模式●DSP 的SPI 控制器对其进行控制,工作在MASTER 模式

VCC3V3

1.9.SCI 串行通讯电路

RS-232MAX3232 3.3V

-2-23-35-5

VCC3V3

1.10.485通讯电路

3.3V

MAX3485

485

/485CS

CPLD

IO

1.11.蜂鸣器电路

P730

VCC3V3

1.1

2.CAN 通讯电路

DSP

CAN2.0

3.3V

CAN

SN65HVD230

CANTX,CANRX

CANH,CANL

CAN 1MBPS

RS SN65HVD230RS=0

;RS=1; RS

R

R70510 k to achieve a

15 V/

s slew

rate,100 k to achieve a

2.0 V/s slew rate

1.13.DSP 和PLD 的JTAG 接口电路

V C C 3V 3

202

0K V C C 3V 3

V3

1.14.外扩512K字节SRAM电路

SRAM IS61LV25616-1010nS256K 16bit512K16bit IS61LV51216F2812XINTF

/XZCS20x08 0000

3

1.15.外扩1M 字节NOR FLASH 电路

NOR FLASH

SST39VF800A 70nS

512K 16bit 256K 16bit SST39VF400A

F2812

XINTF

/XZCS6

0x10 0000

VCC3V3

1.16.走马灯与按键电路

8

LED 4

8

LED

CPLD

IO

4

V

V

1.17.PWM直流电机和步进电机驱动电路

●PWM直流电机控制实验针对5V微型直流电机。

DSP的PWM1和PWM2信号驱动4个NPN的三极管。

●当PWM1为高电平,PWM2为低电平,Q800导通,同时Q803导通,电流从MOTA向MOTB流动,假设这时电机正转。

●当PWM2为高电平,PWM1为低电平,Q802导通,同时Q801导通,电流从MOTB向MOTA流动,这时电机反转。

MOT5V

●步进电机由DSP的PWM3—PWM6信号驱动ULN2003驱动,ULN2003再驱动步进电机。

ULN2003和电机接口PMOT2之间的电阻是防止过流。

1.18.字符型和图形LCD接口电路

LCD

CPLD

●支持字符型LCD 接口,推荐型号为1602A ,12864

●支持图形汉字LCD 接口

1.19.TLV320AIC23音频电路及McBSP 多路复用电路

●本音频电路采用TI 公司的TLV320AIC23B 。

具有放音和录音功能。

●TLV320AIC23B 的控制接口采用SPI 方式

A3V3

1.20.CPLD 电路

CPLD

Altera

MAX3000A

CPLD EPM3128ATC144-10

B

2.0高速USB SLA VE (CY7C68013A )接口

Cypress

CY7C68013A-56

USB 2.0

Slave FIFO

1.2

B2.0全速USB HOST (SL811HST )接口

Cypress

SL811HST

USB 2.0USB HOST USB HOST

U

U 256M 512M 1G 2G 4G 8G

120G

30G

VCC3V3

1.23.以太网(RTL8019)接口

16

8019RST。