原理图+PCB图

- 格式:pdf

- 大小:1.03 MB

- 文档页数:2

pcb板电路原理图分模块解析1 pcb板电路原理图分模块解析————————————————————————————————作者:————————————————————————————————日期:PCB板电路原理图分模块解析前面介绍了电路图中的元器件的作用和符号。

一张电路图通常有几十乃至几百个元器件,它们的连线纵横交叉,形式变化多端,初学者往往不知道该从什么地方开始,怎样才能读懂它。

其实电子电路本身有很强的规律性,不管多复杂的电路,经过分析可以发现,它是由少数几个单元电路组成的。

好象孩子们玩的积木,虽然只有十来种或二三十种块块,可是在孩子们手中却可以搭成几十乃至几百种平面图形或立体模型。

同样道理,再复杂的电路,经过分析就可发现,它也是由少数几个单元电路组成的。

因此初学者只要先熟悉常用的基本单元电路,再学会分析和分解电路的本领,看懂一般的电路图应该是不难的。

按单元电路的功能可以把它们分成若干类,每一类又有好多种,全部单元电路大概总有几百种。

下面我们选最常用的基本单元电路来介绍。

让我们从电源电路开始。

一、电源电路的功能和组成每个电子设备都有一个供给能量的电源电路。

电源电路有整流电源、逆变电源和变频器三种。

常见的家用电器中多数要用到直流电源。

直流电源的最简单的供电方法是用电池。

但电池有成本高、体积大、需要不时更换(蓄电池则要经常充电)的缺点,因此最经济可靠而又方便的是使用整流电源。

电子电路中的电源一般是低压直流电,所以要想从220 伏市电变换成直流电,应该先把220 伏交流变成低压交流电,再用整流电路变成脉动的直流电,最后用滤波电路滤除脉动直流电中的交流成分后才能得到直流电。

有的电子设备对电源的质量要求很高,所以有时还需要再增加一个稳压电路。

因此整流电源的组成一般有四大部分,见图 1 。

其中变压电路其实就是一个铁芯变压器,需要介绍的只是后面三种单元电路。

二、整流电路整流电路是利用半导体二极管的单向导电性能把交流电变成单向脉动直流电的电路。

原理图和PCB中元器件标注规范画原理图时,只能使用中海达元件库(ZHD.LIB)中的元件和对应封装,开始项目前从硬件项目主管处获取最新的库。

如有新添加的元件,应创建原理图符号和对应的封装,及时向硬件项目主管汇报整理归库。

特殊封装应以ZHD_X_NNN的格式命名,其中X电容类为C,电阻类为R,电感类为L等(类型命名表格),NNN为序号,从000开始,向上增加。

芯片、GPS模块、GPRS 模块等模块型元件可以按模块名称命名封装。

对外发出制作PCB前必须在硬件项目主管和采购处记录备案,由硬件项目主管分配PCB年份序号,并且按格式标注到PCB显眼位置上。

原理图标注规则:1)、通用元件只标注序号和标称值,如R1 100K, C1 0.1UF等。

2)、特殊要求在标称值后用括号标注,如R1 100K(1%), C1 10UF(50V)等。

3)、一个项目中同类元件序号从1开始增加,中间不应有跳空。

4)、单位全部用大写,如K,UF,MH,UH等。

5)、原理图必须标有日期和版本,便于升级和管理。

6)、原理图必须使用审核框,图纸应由硬件主管或总工审核。

1、电阻类电阻在电路图中的流水号统一以Rx标注(x表示1,2,3,4……);元器件类型以电阻阻值大小为标注,如:1000Ω标注为1K,100Ω标注为100,1000 000Ω标注为1M。

以此类推。

2、电容类电容在电路图中的流水号统一以Cx标注(x表示1,2,3,4……);元器件类型以电容容量大小为标注,如:105 标为1UF,104标为0.1UF。

3、电感类电感在电路图中的流水号统一以Lx标注(x表示1,2,3,4……);元器件类型以电感大小为标注。

4、二极管类电感在电路图中的流水号统一以Dx标注(x表示1,2,3,4……);元器件类型以二极管型号为标注。

5、三极管类电感在电路图中的流水号统一以Qx标注(x表示1,2,3,4……);元器件类型以三极管型号为标注。

如:Q1 90126、晶振类晶振在电路图中的流水号统一以Xx标注(x表示1,2,3,4……);元器件类型以晶振频率为标注。

原理图的绘制A、新建工作空间和原理图项目是每项电子产品设计的基础,在一个项目文件中包括设计中生成的一切文件,比如原理图文件、PCB图文件、以及原理库文件和PCB库文件。

在项目文件中可以执行对文件的各种操作,如新建、打开、关闭、复制与删除等。

但是需要注意的是,项目文件只是起到管理的作用,在保存文件时项目中的各个文件是以单个文件的形式存在的。

所以每完成一个库就保存一次。

新建工作区间1、在菜单栏中选择File-New-Project-PCB Project.2、形成一个PCB-Project1.PriPCB面板然后重命名最后分别添加scematic sheet形成Sheet.SchDoc文件保存后面一次添加形成PCB.PcbDoc、Pcblib.Pcblib、schlib.schlib文件分别进行保存。

3、在schlib.schlib文件里面添加你需要的库文件进行保存这时候要区分引脚与网口标号,特别是引脚一定要放置正确按照所发的书上进行标号,创建一个库就保存一次直到你需要的几个模块的器件你都画好了。

4、然后找到库文件将你画好的东西放置到Sheet.SchDoc原理图上面这时候再来放置网口标号用线将该连接的地方连接起来画好了看看自己的和书上的区别检查是否有错误的地方,最后将文件进行保存。

点击Libraries面板,点左上角Libraries按钮,如果你想在所有工程里都用就在Imstalled里点Install添加,如果只想在当前工程里使用就在Projiect里面点Add Library。

5、画封装图。

根据我们焊电路板的板子来测量距离将需要的器件进行封装,封装的过程中那一页会出现一个十字号将焊盘放置在十字号上确保第一个焊盘的x、y值都为零然后按照自己测量的数据一次拍好焊盘在一个在Top Layer这一层上放置,防止完成后切换到Top Overlay上面进行划线封装。

对于LED灯要表明它的正极同样的道理没画好一个库进行一次保存直到最终完成了。

一、原理图和PCB图的常见错误1.原理图常见错误:(1)ERC报告管脚没有接入信号:a. 创建封装时给管脚定义了I/O属性;b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.2.PCB中常见错误:(1)网络载入时报告NODE没有找到:a. 原理图中的元件使用了pcb库中没有的封装;b. 原理图中的元件使用了pcb库中名称不一致的封装;c. 原理图中的元件使用了pcb库中pin number不一致的封装。

如三极管:sch中pin numb er 为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:a. 创建pcb库时没有在原点;b. 多次移动和旋转了元件,pcb板界外有隐藏的字符。

选择显示所有隐藏的字符,缩小p cb, 然后移动字符到边界内。

(3)DRC报告网络被分成几个部分:表示这个网络没有连通,看报告文件,使用选择CONNECTED COPPER查找。

另外提醒朋友尽量使用WIN2000, 减少蓝屏的机会;多几次导出文件,做成新的DDB文件,减少文件尺寸和PROTEL僵死的机会。

如果作较复杂得设计,尽量不要使用自动布线。

在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的,在整个PCB中,以布线的设计过程限定最高,技巧最细、工作量最大。

PCB布线有单面布线、双面布线及多层布线。

布线的方式也有两种:自动布线及交互式布线,在自动布线之前,可以用交互式预先对要求比较严格的线进行布线,输入端与输出端的边线应避免相邻平行,以免产生反射干扰。

必要时应加地线隔离,两相邻层的布线要互相垂直,平行容易产生寄生耦合。

一、绘制原理图和P CB图的过程中常遇到的一些问题(请结合上机验证以加深体会)1、放置元件时,光标在图纸中心,元件却在图纸外,试分析可能的原因。

答:这是由于创建元件库时,没有在元件库图纸中心创建元件。

这样,放置元件时,光标所在处是元件库图纸的中心,而元件却距离此中心非常远。

编辑库文件时,元件应该放在原点附近,尽量把元件的第一个管脚放在原点。

2、负电平输入有效的引脚外观如何设置?答:在设置元件属性栏中的D OT项前打勾选中即可。

答:在原理图或元件库的编辑中,遇到需要在网络标号或管脚名等字符上方画横线时,只要在输入这些名字的每个字母后面再补充输入一个“\”符号,Protel即可自动把“\”转化为前一字母的上画线。

4、为什么导线明明和管脚相连,ERC却报告说缺少连线?答:可能的原因有:(1)该问题可能是由于栅格(Grids)选项设置不当引起。

如果捕捉栅格精度(Snap)取得太高,而可视栅格(Visibl e)取得较大,可能导致绘制导线(wire)时,在导线端点与管脚间留下难以察觉的间隙。

例如:当Snap取为1,Visibl e取为10,就容易产生这种问题;(2)另外在编辑库元件、放置元件管脚时,如果把捕捉栅格精度取得太高,同样也会使得该元件在使用中出现此类似问题。

所以,进行库编辑时最好取与原理图编辑相同的栅格精度。

5、ERC报告管脚没有接入信号,试分析可能的原因。

答:可能的原因有:a、创建封装时给管脚定义了I/O属性;b、创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;c、创建元件时,管脚方向反向,使得原理图中是“pin name”端与导线相连。

6、网络载入时报告NODE没有找到,试分析可能的原因。

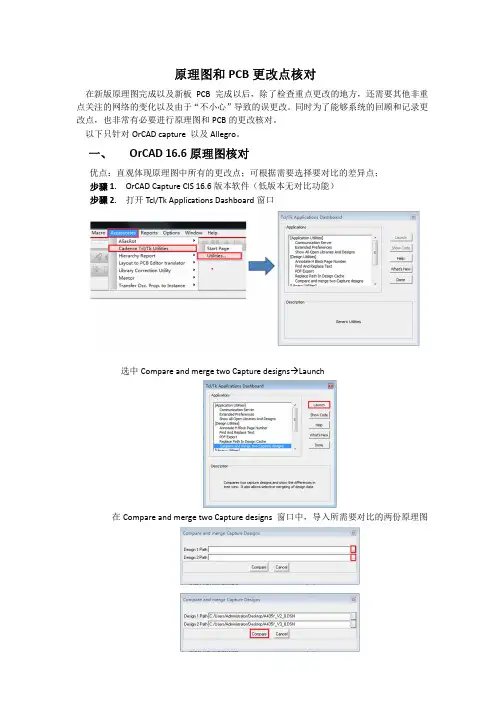

原理图和PCB更改点核对在新版原理图完成以及新板PCB完成以后,除了检查重点更改的地方,还需要其他非重点关注的网络的变化以及由于“不小心”导致的误更改。

同时为了能够系统的回顾和记录更改点,也非常有必要进行原理图和PCB的更改核对。

以下只针对OrCAD capture 以及Allegro。

一、 OrCAD 16.6原理图核对优点:直观体现原理图中所有的更改点;可根据需要选择要对比的差异点;步骤1. OrCAD Capture CIS 16.6版本软件(低版本无对比功能)步骤2. 打开Tcl/Tk Applications Dashboard窗口选中Compare and merge two Capture designs Launch在Compare and merge two Capture designs 窗口中,导入所需要对比的两份原理图单击Compare后弹出对比界面后,步骤3-2 的Tcl/Tk Applications Dashboard窗口可以关掉步骤3.对比界面,单击箭头处三角号可展开各页的对比情况在页列表,可以选中页(页码前方框打勾),直接弹出所选页原理图对比对比结果1)当页原理图中,不同处自动高亮显示(如下图A435C V2.0)2)当页原理图中,不同处自动高亮显示(如下图A435C V3.0)在页列表,单击展开页,显示当前页有变动的网络及器件• 网络走线位置变动;• 器件属性如值\封装\位置等等变更;• 标识文字,标题栏;如下setting菜单栏可进行不同点颜色设定、过滤不需要对比的选项等二、 基于Allegro PCB Design的PCB修改点核对优点:可直观对比显示不同的网络点;不足:若修改点较多的话,核对的时间较长;且需要返回原理图查看修改点;仅对网表进行核对;步骤1. 打开旧版本PCB导出XML文档步骤2. 在新版本PCB中,打开Design Compare窗口(同步骤1)步骤3. 新版本PCB的Design Compare窗口中导入旧版本PCB的XML文档;步骤4. 导入旧版本PCB的XML文档后界面如下• 左侧一列为当前PCB的网络表,右侧一列为导入的网络表;• Netlist前面的黄色圆圈表示两份PCB有网络连接不一致步骤5. 单击Netlist前面的圆点可以将网络展开;• 黄色圆圈表示新旧版本中该网络连接有不一致的;• 绿色圆圈表示新旧版本中该网络连接一样;• 红色圆圈表示该网络当前PCB有,而所对比的PCB没有;• 继续展开可显示该网络所连接的器件位号及Pin号三、 采用UltraEdit的PCB网表核对优点:直观显示不同网络;不足:有变更的网络中,无法直观区分增删的器件;仅对网表进行核对;步骤1. 打开旧版本PCB导出Net List Report步骤2. 打开新版本PCB导出Net List Report(同步骤1)步骤3.在UltraEdit软件中,打开步骤2-1及步骤2-2导出的.htm文件步骤4.在UltraEdit软件中比较两份.htm文档步骤5. 对比界面• 下图左右两列中红色字体为不同网络的部分;• 单击红圈中的向下键可以看其他不同的网络。