基于VHDL语言的数字电路设计

- 格式:pdf

- 大小:238.77 KB

- 文档页数:3

vhdl实验报告VHDL实验报告引言:VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于数字电路设计和仿真。

本篇实验报告将介绍我在VHDL实验中的学习和实践经验,包括实验目的、实验过程、实验结果以及对VHDL的理解和展望。

一、实验目的VHDL实验的主要目的是让我们掌握VHDL语言的基本语法和使用方法,能够利用VHDL描述数字电路,并通过仿真和综合工具进行验证和实现。

通过这些实验,我们可以深入了解数字电路的原理和设计方法,提高我们的逻辑设计能力和工程实践能力。

二、实验过程在实验过程中,我们首先学习了VHDL的基本语法,包括实体声明、端口声明、信号声明等。

然后,我们通过实例学习了VHDL的建模方法,包括组合逻辑电路的建模和时序逻辑电路的建模。

在组合逻辑电路的建模中,我们学习了使用逻辑运算符和条件语句描述电路的功能;在时序逻辑电路的建模中,我们学习了使用过程语句和时钟信号描述电路的状态转换。

在学习了VHDL的基础知识后,我们开始进行实验设计。

我们选择了一个简单的数字电路,如4位加法器,来进行实验验证。

首先,我们通过VHDL语言描述了加法器的功能和结构,包括输入端口、输出端口和中间信号。

然后,我们使用仿真工具进行了功能仿真,验证了加法器的正确性。

接着,我们使用综合工具将VHDL代码综合成门级电路,并进行了时序仿真和时序优化,验证了加法器的时序正确性和性能。

三、实验结果通过实验,我们成功地实现了4位加法器的功能,并验证了其正确性和性能。

在功能仿真中,我们输入了不同的测试数据,观察了输出结果,发现加法器能够正确地进行加法运算,并得到了正确的结果。

在时序仿真中,我们观察了电路的时序行为,包括输入信号的变化、输出信号的响应和中间信号的传播延迟等,发现加法器能够在时序上满足要求,并且具有较好的性能。

毕业设计vhdl毕业设计:VHDL的应用与挑战在计算机科学与技术领域中,VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,用于描述和设计数字电路。

作为一门重要的课程,毕业设计是学生们在大学期间的重要任务之一。

本文将探讨毕业设计中VHDL的应用与挑战。

VHDL是一种用于描述和设计数字电路的语言,它具有丰富的语法和强大的功能。

通过使用VHDL,设计师可以描述数字电路的结构和行为,从而实现复杂的功能。

VHDL具有模块化的特性,可以将电路划分为不同的模块,每个模块负责特定的功能。

这种模块化的设计方法使得电路的设计更加灵活和可维护。

在毕业设计中,VHDL的应用广泛而深入。

首先,VHDL可以用于设计和实现各种数字电路,如加法器、乘法器、寄存器等。

这些电路是计算机系统的基础组成部分,通过使用VHDL进行设计和实现,可以提高电路的性能和可靠性。

其次,VHDL还可以用于设计和实现数字信号处理(DSP)算法。

DSP算法在音频、视频等领域中具有广泛的应用,通过使用VHDL进行设计和实现,可以实现高效的算法并提高系统的性能。

然而,毕业设计中使用VHDL也面临一些挑战。

首先,VHDL的学习曲线较陡峭。

对于初学者来说,掌握VHDL的语法和规范需要一定的时间和精力。

其次,VHDL的调试和验证也是一个复杂的过程。

由于VHDL是一种硬件描述语言,无法直接运行和调试,需要使用仿真工具进行验证。

这个过程需要设计师具备一定的专业知识和技巧。

最后,VHDL的设计和实现也需要考虑到电路的性能和资源占用。

设计一个高效的电路需要综合考虑电路的结构和算法,以及资源的利用和分配。

为了克服这些挑战,毕业设计中可以采取一些策略。

首先,学生可以通过参加相关的课程和培训来提高对VHDL的理解和掌握。

这些课程和培训可以帮助学生了解VHDL的语法和规范,以及设计和实现电路的方法和技巧。

其次,学生可以利用仿真工具进行调试和验证。

vhdl设计实验报告VHDL设计实验报告引言VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于数字电路设计和验证。

本实验旨在通过设计一个简单的电路来熟悉VHDL语言的基本语法和设计流程。

一、实验背景数字电路是现代电子系统的基础,而VHDL则是描述和设计数字电路的重要工具。

VHDL可以帮助工程师们以一种形式化的语言来描述电路的功能和结构,从而实现电路的模拟和验证。

二、实验目的本实验的目的是通过使用VHDL语言设计一个简单的电路,加深对VHDL语言的理解,并掌握基本的电路设计流程。

三、实验步骤1. 确定电路功能在设计电路之前,首先需要明确电路的功能。

本实验中,我们选择设计一个4位加法器电路。

2. 设计电路结构根据电路功能的要求,设计电路的结构。

在本实验中,我们需要设计一个4位加法器,因此需要使用4个输入端口和一个输出端口。

3. 编写VHDL代码使用VHDL语言编写电路的描述代码。

在代码中,需要定义输入和输出端口的类型和位宽,并实现电路的功能。

4. 进行仿真使用仿真工具对设计的电路进行仿真,以验证电路的功能是否符合预期。

通过输入不同的测试数据,观察输出是否正确。

5. 下载到FPGA开发板将设计好的电路代码下载到FPGA开发板上进行验证。

通过连接输入信号和观察输出信号,验证电路在实际硬件上的运行情况。

四、实验结果与分析经过仿真和实际验证,我们设计的4位加法器电路在功能上符合预期。

输入不同的数据进行加法运算时,输出结果都正确。

五、实验总结通过本次实验,我们深入了解了VHDL语言的基本语法和设计流程。

通过设计一个简单的电路,我们掌握了VHDL的应用方法,并通过仿真和实际验证,加深了对电路设计的理解。

六、实验心得本实验让我对VHDL语言有了更深入的认识。

通过实际操作,我更加熟悉了VHDL的编写和仿真流程。

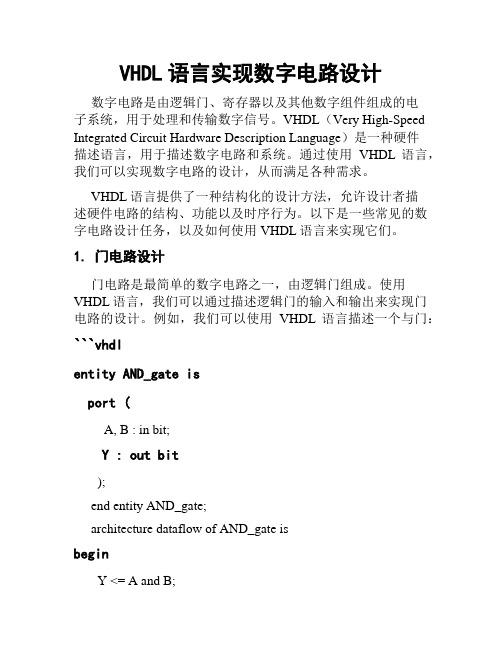

VHDL语言实现数字电路设计数字电路是由逻辑门、寄存器以及其他数字组件组成的电子系统,用于处理和传输数字信号。

VHDL(Very High-Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,用于描述数字电路和系统。

通过使用VHDL语言,我们可以实现数字电路的设计,从而满足各种需求。

VHDL语言提供了一种结构化的设计方法,允许设计者描述硬件电路的结构、功能以及时序行为。

以下是一些常见的数字电路设计任务,以及如何使用VHDL语言来实现它们。

1. 门电路设计门电路是最简单的数字电路之一,由逻辑门组成。

使用VHDL语言,我们可以通过描述逻辑门的输入和输出来实现门电路的设计。

例如,我们可以使用VHDL语言描述一个与门:```vhdlentity AND_gate isport (A, B : in bit;Y : out bit);end entity AND_gate;architecture dataflow of AND_gate isbeginY <= A and B;end architecture dataflow;```在这个例子中,我们定义了一个输入端口A和B,以及一个输出端口Y。

在architecture部分,我们使用VHDL语言描述了Y的逻辑值为A和B的逻辑与。

2. 时序逻辑电路设计时序逻辑电路是根据时钟信号进行操作和状态转换的电路。

使用VHDL语言,我们可以描述时序逻辑电路的行为和状态变化。

例如,我们可以使用VHDL语言描述一个触发器:```vhdlentity D_flip_flop isport (D, CLK : in bit;Q : out bit);end entity D_flip_flop;architecture behavior of D_flip_flop issignal Q_temp : bit;beginprocess(CLK)beginif CLK'event and CLK = '1' thenQ_temp <= D;end if;end process;Q <= Q_temp;end architecture behavior;```在这个例子中,我们定义了一个输入端口D和CLK,以及一个输出端口Q。

基于VHDL的数字电路设计数字电路是电子信息领域中最重要的一部分,控制着现代社会各种各样的设备的运行。

为了满足各种不同的应用需求,数字电路被设计成了多种多样的形态。

其中,基于VHDL的数字电路设计方式得到了广泛的应用。

VHDL是一种硬件描述语言,是用来描述数字电路的语言。

本文将着重探讨基于VHDL的数字电路设计的流程和步骤,以及在实际设计中的应用。

一、VHDL简介VHDL全称是VHSIC硬件描述语言(VHSIC Hardware Description Language),VHSIC即:超高速集成电路(Very-high-speed integrated circuit)。

VHDL是一种硬件描述语言,它是用来描述数字电路的语言,可以描述数字电路功能、电路结构和电路时序特性等。

在数字电路设计中,VHDL是最重要的一种设计语言。

VHDL是一种结构化的硬件描述语言,包括有三个层次:一是建模层次,主要是用户对数字电路的需求,这一层次不直接与具体的电路有关;二是结构化层次,是用户根据需求所建立的结构化的电路模型;三是行为层次,是用户描述数字电路的最终形态。

二、数字电路设计的流程数字电路设计的流程如下:1. 分析功能需求,确定电路功能和处理流程,针对不同的应用要求,从而确定数字电路的类型和规格。

2. 设计实现电路,采用FPGA(Field Programmable Gate Array)或ASIC (Application Specific Integrated Circuit)等芯片,使用VHDL编写代码,使用VHDL进行模拟验证,并对设计进行等效性检查。

3. 对电路进行综合,将VHDL代码转化为对应的生成目标电路的结构级综合器,主要用于对电路进行优化和管脚分配等方面的处理。

4. 进行电路设计验证,生成电路功能模拟信号,通过波形查看器、时钟分析器等工具进行验证测试。

5. 编写VHDL管理器,通过代码编写实现电路的管理和控制,包括对电路的自测试、故障诊断和运行状态监测等。

基于VHDL的矩阵键盘及显示电路设计摘要:为了有效防止机械式键盘按键抖动带来的数据错误,这里在Quartus ?开发环境下,采用VHDL 语言设计了一种能够将机械式4 ×4 矩阵键盘的按键值依次显示到8 个7 段数码管上的矩阵键盘及显示电路。

仿真结果表明,所设计的矩阵键盘及显示电路成功地实现了按键防抖和按键数据的准确显示。

以ACEX1K系列EP1K30QC208 芯片为硬件环境,验证了各项设计功能的正确性。

FPGA/ CPLD 在数字系统设计中的广泛应用,影响到了生产生活的各个方面。

在FPGA/ CPLD 的设计开发中,V HDL 语言作为一种主流的硬件描述语言,具有设计效率高, 可靠性好, 易读易懂等诸多优点。

作为一种功能强大的FPGA/ CPLD 数字系统开发环境,Altera 公司推出的Quart us ?,为设计者提供了一种与结构无关的设计环境,使设计者能方便地进行设计输入、快速处理和器件编程,为使用V HDL 语言进行FPGA/ CPLD 设计提供了极大的便利。

矩阵键盘作为一种常用的数据输入设备,在各种电子设备上有着广泛的应用,通过7 段数码管将按键数值进行显示也是一种常用的数据显示方式。

在设计机械式矩阵键盘控制电路时,按键防抖和按键数据的译码显示是两个重要方面。

本文在Quart us ?开发环境下,采用V HDL语言设计了一种按键防抖并能连续记录并显示8 次按键数值的矩阵键盘及显示电路。

1 矩阵键盘及显示电路设计思路矩阵键盘及显示电路能够将机械式4 ×4矩阵键盘的按键值依次显示到8 个7段数码管上,每次新的按键值显示在最右端的第0 号数码管上,原有第0,6号数码管显示的数值整体左移到第1,7号数码管上显示,见图1 。

总体而言,矩阵键盘及显示电路的设计可分为4 个部分:(1) 矩阵键盘的行及列的扫描控制和译码。

该设计所使用的键盘是通过将列扫描信号作为输入信号,控制行扫描信号输出,然后根据行及列的扫描结果进行译码。

本文由风中思念7贡献pdf文档可能在WAP端浏览体验不佳。

建议您优先选择TXT,或下载源文件到本机查看。

一、概述VHDL与数字电路设计一、概述二、VHDL语言三、用VHDL设计逻辑电路传统数字电路设计方法 EDA设计方法 PLD器件设计流程文本设计输入—VHDL程序设计数字电子技术的基本知识回顾组合逻辑电路编码器、译码器、数据选择器、加法器、数值比较器等传统设计方法传统的设计方法是基于中小规模集成电路器件进行设计(如74系列及其改进系列、CC4000系列、 74HC系列等都属于通用型数字集成电路),而且是采用自底向上进行设计:(1)首先确定可用的元器件;(2)根据这些器件进行逻辑设计,完成各模块;(3)将各模块进行连接,最后形成系统;(4)而后经调试、测量观察整个系统是否达到规定的性能指标。

时序逻辑电路同步时序逻辑电路异步时序逻辑电路寄存器、移位寄存器、计数器、序列信号发生器 EDA设计方法EDA(Electronics Design Automation)即电子设计自动化技术,是利用计算机工作平台,从事电子系统和电路设计的一项技术。

EDA技术为电子系统设计带来了这样的变化:(1)设计效率提高,设计周期缩短;(2)设计质量提高;(3)设计成本降低;(4)能更充分地发挥设计人员的创造性;(5)设计成果的重用性大大提高,省去了不必要的重复劳动。

自顶向下的设计方法数字电路的EDA设计是基于PLD进行设计的,支持自顶向下的设计方法:(1)首先从系统设计入手,在顶层进行功能划分和结构设计;(2)然后再逐级设计底层的结构;(3)并在系统级采用仿真手段验证设计的正确性;(4)最后完成整个系统的设计,实现从设计、仿真、测试一体化。

传统设计方法 vs EDA设计方法传统设计方法自底向上手动设计软硬件分离原理图设计方式系统功能固定不易仿真难测试修改模块难移植共享设计周期长PLD器件设计流程(1)PLD开发系统包括硬件和软件两部分。

VHDL硬件描述语言与数字逻辑电路设计第三版课程设计本次课程设计旨在帮助大家深入理解VHDL硬件描述语言和数字逻辑电路设计的相关知识,提高大家的实践能力和设计能力。

本文将对课程设计的要求和实现方法进行详细说明。

课程设计要求本次课程设计要求大家完成一个基于VHDL的数字逻辑电路设计,包括以下要求:1.手动编写VHDL程序,对指定的数字电路进行仿真分析,并输出相应的波形图。

2.设计一个数字电路,要求该电路可完成特定的逻辑功能,例如加法器、多路选择器等。

3.基于现实的场景需求,完成一个实际的数字电路设计。

例如,实现一个音乐播放器控制器、机器人控制器等。

设计步骤步骤一:了解VHDL语言和数字逻辑电路设计原理在进行数字电路设计之前,需要先理解VHDL语言和数字逻辑电路设计原理。

VHDL语言是一种硬件描述语言,主要用于描述数字逻辑电路。

数字逻辑电路由基本的逻辑单元组成,包括与门、或门、非门等,通过组合这些逻辑单元可以实现更复杂的逻辑电路设计。

步骤二:选择仿真工具选择一款仿真工具进行仿真分析。

常见的仿真工具有ModelSim、Xilinx ISE 等。

步骤三:编写VHDL程序编写VHDL程序,对指定的数字电路进行仿真分析。

根据实际需要,可以选择不同的VHDL语言结构进行编写。

步骤四:仿真分析在仿真工具中进行仿真分析,根据VHDL程序模拟出相应的波形图。

步骤五:设计数字电路基于数字逻辑电路设计原理,设计出特定的数字电路。

需要首先确定电路所需要的逻辑功能,然后根据这个功能设计出合适的电路。

步骤六:实现实际场景需求参考现实的场景需求,设计出一个实际的数字电路,并进行调试测试。

VHDL程序编写规范在编写VHDL程序时,需要遵循一定的编写规范,以保证程序的可读性和可维护性。

1.命名规范:变量和信号的命名应具有较好的描述性,易于理解和记忆。

2.缩进规范:代码缩进应该统一,便于代码的阅读和理解。

3.注释规范:代码中应加入必要的注释,解释各个模块的功能和作用。

西南民族大学学报自然科学版第32卷第4期Jour nal of Sout hw est U ni ver si t y for N at i onal i t i es N at ural Sci ence Edi t i onJ ul y 2006______________________________________________________________________________________________收稿日期2006-03-24作者简介符兴昌(1969-)男四川文理学院物电系讲师研究方向为电子技术与计算机应用.基金项目四川省教育厅自然科学重点项目(2005A186).文章编号1003-2843(2006)04-0778-05基于V H D L 语言在电路设计中的优化探讨符兴昌(四川文理学院物电系四川达州635000)摘要对V H D L 语言在电路设计应用中如何优化电路结构进行一些探讨通过从描述方式算法的改进和优化断言语句的综合优化等几个方面提出了优化方案并结合实例进一步分析V H D L 综合优化的实现效果.关键词V H D L 语言电路设计优化中图分类号TP391文献标识码A1引言V H D L 是随着可编程逻辑器件(PL D )的发展而发展起来的一种超高速集成电路硬件描述语言1987年成为I E E E 标准[1].利用V H D L 数字系统可以从系统行为级寄存器传输级和门级三个不同层次进行设计即从上层到下层(抽象到具体)逐层描述自己的设计思想用一系列分层次的模块来表示极其复杂的数字系统[2].然后利用电子设计自动化(E D A )工具逐层进行仿真验证再把其中需要变为实际电路的模块组合经过自动化综合工具转换到门级电路网表再用专用集成电路(A SI C )或现场可编程门阵列(FPG A )自动布局布线工具[3]把网表转换为要实现的具体电路布线结构.虽然V H D L 语言支持全部的仿真功能但并不是全部可综合的[4]V H D L 程序的许多硬件描述和仿真结构没有对应的数字电路来实现还有些描述在理论上可以映射为对应的数字电路但是却不能保证其精确性比如延时模型.随着综合算法技术水平的提高针对某些寄存器传输级(R T L)电路描述可以进行有效的优化但是对于更普遍的电路描述还不够因此综合结果是否满足给定的时间约束条件和面积约束条件还取决于V H D L 编码方式.由于每个电路工程师对语言规则电路行为的理解程度不同编程风格不同对于同样的系统功能如果描述的方式不一样则综合出来的电路就有可能大相径庭.因此即使最后综合出来的电路都能实现相同的逻辑功能其电路的复杂程度和时延特性都会有很大的差别.本文就V H D L 语言在电路设计中如何简化电路结构达到优化电路的一些问题进行一些探讨.2V H D L 的综合优化设计2.1合理选择描述方法可减小电路的复杂程度在电路设计中V H D L 语言描述方法不同对电路器件布线选择产生直接影响因此不同的语言描述对电路的复杂程度工作速度影响很大.最常见的使电路复杂化的原因之一是设计中存在着许多不必要的结构.而这些结构通常由大量的触发器构成不仅使电路更复杂工作速度降低而且由于时序配合的原因导致不可预料的结果.下面是对同一译码电路的两种V H D L 描述.1i f i ndex =00000t hen s t eps i ze <=0000111;e l si f i ndex =00001t hen779符兴昌基于V H D L语言在电路设计中的优化探讨第4期___________________________________________________________________ s t eps i ze<=0001000;e l sif i ndex=00010t hens t eps i ze<=0001001;e l sest e psi ze<=000000;e nd i f;(2)st epsi ze<=0000111w he n i ndex=00000e l se0001000w hen i ndex=00001el se0001001w hen i ndex=00010el s e0000000;以上两段程序描述同一个译码电路第二段程序由于w hen e l se的语句不能生成锁存器的结构并且el se 后一定要有结果所以不会有问题而第一段程序如果不加el se s t eps i ze<=0000000这句则会生成一个含有7b寄存器的结构虽然都实现相同的译码功能但是程序(1)使电路的复杂程度大大增加.因此在用V H D L进行设计中要注意尽量避免不必要的寄存器描述.另外可以根据实际的设计要求选择合适的描述方式.采用V H D L可以对系统进行不同层次的描述常用的描述方式有四种行为级描述寄存器传输级描述结构描述混合描述等.不同描述各有优缺点行为描述方便易用同时不需要了解系统的实现细节但是会产生占用器件资源过多速度较慢等问题而寄存器传输级描述和结构描述可以减少资源占用提高系统运行速度但要求设计人员必须掌握系统的实现细节例如信号之间的时序关系互连器件的层次放置等.2.2通过改进设计算法达到优化电路的目的用V H D L语言设计电路在进行综合优化时主要有两个目标一是提高目标器件的工作速度二是提高目标器件的利用率.因此可以从算法(电路结构)上对设计进行改进和优化.下面以两种不同的算法设计一个模6计数器并对它们的资源使用情况执行效率和对应的布线图进行比较.该设计方案采用Synopsys公司的FPG A E xpr ess综合器目标器件选用xi l i nx公司的4010X LPC84.表1是两个算法的端口定义和主体部分.表1两个算法的设计比较表算法1算法2端口定义en:i n st d_ul ogi c;cl k:i n s t d_ul ogi c;carr y:out st d_ul ogi c;q:out s t d_ul ogi c_vect or(2dow nt o0)en:i n st d_l ogi c;cl k:i n s t d_l ogi c;carr y:out st d_l ogi c;q:buff er st d_l ogi c_vect or(2dow nt o0)主体部分pr ocess(cl k)vari abl e q6:i nt eger;begi ni f(cl k evt en cl k=1)t heni f(en=0)t henq6:=0;el sei f(q6=5)t henpr ocess(cl k)begi ni f(cl k evt en cl k=1)t heni f(en=0)t henq<=(ot her s=>0);el sei f(q=b101)t henq<=(ot her s=>0);第32卷780西南民族大学学报自然科学版___________________________________________________________________q6:=0;ca<=0;el si f(q6=4)t henq6:=q6+1;ca<=1;el seq6:=q6+1;ca<=0;end i f;end i f;qs<=conv_st d_l ogi c_vect or(q6,3);q<=t o_st dul ogi cvect or(qs);end i f;end process;ca<=0;el si f(q=b100)t henq<=q+1;ca<=1el se;q<=q+1;ca<=0;end i f;end i f;end i f;end process;上述两个算法相比较算法2使用的数据类型更接近硬件的实际应用数据类型并且不需转换而直接进行处理从而在很大程度上提高系统的处理效率和速度而且占用系统资源少具体情况见表2表3.表2两个算法资源使用情况比较表器件主要资源及总量可配置逻辑块(400个)外围可配置I/O块(160个)四输入查找表(800个)三输入查找表(400个)算法1使用(资源情况)算法2使用(资源情况)26个(占6.5%)3个(占0.8%)9个(占5.6%)6个(占3.8%)49个(占6.1%)5个(占0.6%)8个(占2.0%)0个(占0.0%)表3两个算法的执行效率比较表最大可达频率(M H z)最大网络延迟(ns)平均连接延迟(ns)算法141.3799.120 2.778算法2122.459 6.207 1.469同时通过这两个算法所对应的电路布线图(见图1)可以看出算法2要比算法1实现的电路要简单优化.(a)算法1(b)算法2图1两个算法实现的布线图781 ___________________________________________________________________符兴昌基于V H D L语言在电路设计中的优化探讨第4期2.3断言语句的综合优化V H D L语句中提供了断言语句设计者可以利用断言语句对V H D L源描述中的模型增加限制和约束条件.这种限制和约束条件模拟和综合都可以使用.[5]断言语句非常有用尤其是在设计的调试模拟阶段设计者可以通过断言语句报告的有关内容检查限制条件为何得不到满足和V H D L描述是否正确.在有些模拟系统中当一些重要的限制条件没有满足如发现了模型不能处理的错误就会停止模拟过程.断言语句中限制条件的补表达式可作为随意(D on t Car e)条件用于综合时的化简这样可以提高综合的优化程度.例如对下列V H D L源描述EN T I Y Y Exam pl e of A sse r t I SPO RT(x:I N bi t;Y:I N bi t;Z:O U T bi t);EN D Exam pl e of A sse r t;A R C H I T E CT U R E A r ch O F Exam pl e O f A sser t I SBE G I NZ<=(x A N D y)O R(N O T x A N D N O T y);A SSER T N O T x O R y SE V E R I TY E r r or;EN D A r ch;利用其中断言语句的随意条件综合出的实现电路可以得到优化如图2所示.图2-A为没有利用断言语句随意条件的实现电路图2-B为利用断言语句随意条件化简后的实现电路.两者相比较后者得到优化.(A)(B)图2利用断言语句的综合结果比较3结语随着功能强大的E D A开发软件和专业的综合工具的不断发展使PLD设计或A SI C设计过程更简单更快捷.但是要提高设计质量编程方式仍然起着很重要的作用除了上述讨论的几点V H D L语言优化电路结构外另外在用V H D L语言编程时还应注意以下几点(1)在条件允许范围内尽量用集成度高的电路语言直接描述也就是说编写程序时可深入到逻辑电路内部在门级上用V H D L语言来表达.(2)在编写程序前要对整个设计进行深入了解把设计分成若干部分每一部分再分别描述其行为尽量用多个较少位数的单元取代较多位数的单元这样综合出来的电路较简单.(3)在V H D L中无约束整数的范围是-2147483647+2147483647这意味着至少要32b来表示但通常会造成资源浪费有些综合软件会自动进行优化但浪费时间.所以如果需要全范围的整型数据最好指定一个范围.(4)当在V H D L中使用算术逻辑关系逻辑等通用逻辑结构时我们可以选择针对特定工艺的优化宏模块这样可以提高执行效率使得综合结果面积更小效率更高所需编译时间更短.___________________________________________________________________ 782西南民族大学学报自然科学版第32卷(5)由于综合工具只能支持V H D L子集为保证在综合前后的仿真保持相同以下语句在综合中应该避免使用避免使用w a i t f or ns这种语句不会被综合为实际的电路元件避免a f t er ns在综合工具进行综合时会忽略a f t er语句避免在信号和变量声明时赋初值因为大部分综合工具会忽略初始化语句否则综合出来的结果和仿真结果将产生差异.参考文献[1]高书莉罗朝霞.可编程逻辑设计技术及应用[M].北京人民邮电出版社2001.[2]阮忠林金表陈强.综合电子电路应用指南[M].北京机械工业出版社2004(8):208-212.[3]王华王汝传吴凡.基于V H D L语言的FPG A设计[J].微型机与应用2002(11):20-22.[4]刘明业张东晓许庆平.V H D L高级综合系统设计中某些关键问题的技术决策[J].计算机学报1997,20(6):501-509.[5]吴建国孙元刘明业.V H D L语言中断言语句及其综合方法研究[J].计算机学报,1998,21(10):929-932.I nqui r y about m aj or i zat i on of V H D L Language i n c i r cui t des i gnFU X i ng-chang(D epar t m ent of Phys i cs and El ect roni cs,Si chuan Inst i t ut e of H um ani t i es and Sci ences,D azhou635000,P.R.C.)A bst r ac t:I n t hi s t hesi s t he i nqui r y a bout t he m aj or i z at i on of t he c i r cui t st r uct ur e i s m adew hen t he V H D L l anguage i s appl i e d t o t he ci r cui t de si gn.The m aj or i zat i on pr ogr ami s dr aw n on t he bas i s of t he del i nea t i on w ay,t he i m pr ove m ent and m aj or i z at i on of t he al gor i t hm,and t he i nt e gr at ed m aj or i za t i on of t he asse r t st at em ent.The r eal i zat i on ef f ect of t he V H D L Si nt egr at ed m aj or i za t i on i s f ur t he r anal yzed by com bi ni ng t he l i vi ng e xam pl es.K ey w or ds:V H D L Language c i r cui t desi gn m aj or i z t i on。

题目: 基于VHDL的占空比50%的7分频电路设计姓名:学号:班级:指导教师:成绩:摘要:在数字逻辑电路设计中,分频器是一种基本电路,通常用来对某个给定频率的时钟进行分频,得到所需的时钟。

时序电路设计中需要各种各样的分频器来获得不同频率的时钟,其中以整数分频器最为常见。

整数分频可以简单的使用模n计数器实现,即随驱动时钟跳变n 次后就输出一个进位脉冲,然后立即被清零或置位,再开始新一轮的循环的计数。

模n计数器的进位脉冲的宽度一般与驱动时钟相同,这对于边沿驱动的时序逻辑并不会带来什么问题。

但是在某些需要使用电平逻辑的设计中,我们更希望分频时钟拥有50%,或者与驱动时钟相同的占空比。

这时就需要通过另外的逻辑方法来进行分频,或者使用PLL。

在基于CPLD(复杂可编程逻辑器件)/FPGA(现场可编程门阵列)的数字系统设计中,很容易实现由计数器或其级联构成各种形式的偶数分频及非等占空比的奇数分频,但对等占空比的奇数分频及半整数分频的实现较为困难。

本文利用VHDL(超高速集成电路硬件描述语言),通过Quartus II 7.1 开发平台,设计了一种能够实现占空比50%的7分频电路设计,这种设计方法原理简单,可重用性好,而且只需很少的逻辑宏单元。

关键词:VHDL 占空比分频器1、VHDL语言 (3)1.1 、VHDL语言的介绍 (3)1.2 、VHDL语言的特点 (3)2、分频电路的设计 (3)2.1分频电路的分类: (3)2.2 任意奇数倍(2N+1)分频 (4)2.3 占空比为 50%的分频 (4)3、占空比为50%的7分频电路的设计 (4)3.1、7分频电路的RTL视图,如下: (4)3.2、基于VHDL的占空比为50%的7分频电路的代码程序 (5)3.3、占空比为50%的7分频仿真 (6)4、心得体会 (7)5、参考文献 (8)1、VHDL语言1.1 、VHDL语言的介绍VHDL语言是一种用于电路设计的高级语言。

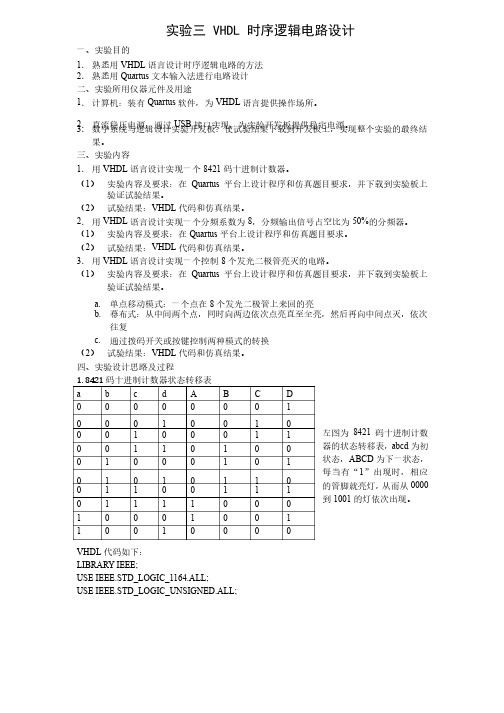

实验三实验三 VHDL VHDL VHDL 时序逻辑电路设计时序逻辑电路设计 一、实验目的一、实验目的1. 熟悉用VHDL 语言设计时序逻辑电路的方法语言设计时序逻辑电路的方法 2. 熟悉用Quartus 文本输入法进行电路设计文本输入法进行电路设计 二、实验所用仪器元件及用途二、实验所用仪器元件及用途 1. 计算机:装有Quartus 软件,为VHDL 语言提供操作场所。

语言提供操作场所。

2. 直流稳压电源:通过USB 接口实现,为实验开发板提供稳定电源。

接口实现,为实验开发板提供稳定电源。

3. 数字系统与逻辑设计实验开发板:使试验结果下载到开发板上,实现整个实验的最终结果。

果。

三、实验内容三、实验内容 1. 用VHDL 语言设计实现一个8421码十进制计数器。

码十进制计数器。

(1) 实验内容及要求:在Quartus 平台上设计程序和仿真题目要求,并下载到实验板上验证试验结果。

验证试验结果。

(2) 试验结果:VHDL 代码和仿真结果。

代码和仿真结果。

2. 用VHDL 语言设计实现一个分频系数为8,分频输出信号占空比为50%的分频器。

的分频器。

(1) 实验内容及要求:在Quartus 平台上设计程序和仿真题目要求。

平台上设计程序和仿真题目要求。

(2) 试验结果:VHDL 代码和仿真结果。

代码和仿真结果。

3. 用VHDL 语言设计实现一个控制8个发光二极管亮灭的电路。

个发光二极管亮灭的电路。

(1) 实验内容及要求:在Quartus 平台上设计程序和仿真题目要求,并下载到实验板上验证试验结果。

验证试验结果。

a. 单点移动模式:一个点在8个发光二极管上来回的亮个发光二极管上来回的亮b. 幕布式:从中间两个点,同时向两边依次点亮直至全亮,然后再向中间点灭,依次往复往复c. 通过拨码开关或按键控制两种模式的转换通过拨码开关或按键控制两种模式的转换 (2) 试验结果:VHDL 代码和仿真结果。