Cyclone II器件中文资料

- 格式:doc

- 大小:352.00 KB

- 文档页数:16

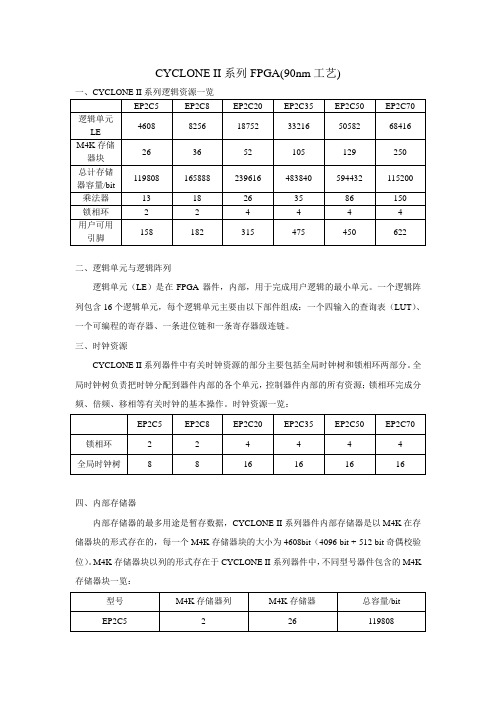

CYCLONE II系列FPGA(90nm工艺)二、逻辑单元与逻辑阵列逻辑单元(LE)是在FPGA器件,内部,用于完成用户逻辑的最小单元。

一个逻辑阵列包含16个逻辑单元,每个逻辑单元主要由以下部件组成:一个四输入的查询表(LUT)、一个可编程的寄存器、一条进位链和一条寄存器级连链。

三、时钟资源CYCLONE II系列器件中有关时钟资源的部分主要包括全局时钟树和锁相环两部分。

全局时钟树负责把时钟分配到器件内部的各个单元,控制器件内部的所有资源;锁相环完成分频、倍频、移相等有关时钟的基本操作。

时钟资源一览:四、内部存储器内部存储器的最多用途是暂存数据,CYCLONE II系列器件内部存储器是以M4K在存储器块的形式存在的,每一个M4K存储器块的大小为4608bit(4096 bit + 512 bit奇偶校验位)。

M4K存储器块以列的形式存在于CYCLONE II系列器件中,不同型号器件包含的M4K 存储器块一览:CYCLONE II 系列器件中的M4K 可以被配置为以下模式:单口模式、简单双口模式、完全双口模式、移位寄存器模式、只读存储器(ROM )模式和先入先出(fifo )模式。

五、FPGA 芯片的配置由于CYCLONE II 系列的FPGA 是基于SRAM 工艺制造的,SRAM 属于易失性的存储媒质,因此FPGA 在每次上电时必须重新配置。

CYCLONE II 系列的FPGA 支持3种配置方式:主动串行(AS )、被动串行(PS )和JATG 模式。

CYCLONE II 器件的配置分为3个阶段:复位阶段、配置阶段和初始化阶段。

六、FPGA 内部资源的使用锁相环(PLL )配置,锁相环一般用于同步输入时钟和输入数据,以及完成时钟综合,包括分频、倍频、移相等操作。

PLL 配置需求:CYCLONE II 系列器件中的M4K 配置为以下模式:单口RAM 模式、移位寄存器模式、只读存储器(ROM )模式和先入先出(fifo )模式。

Cyclone II EP2C5/8 启蒙板说明书 Cyclone II EP2C5/8 Start Board User Manual Version 2.1 Copyright © 线路人生|Circuitry Life 线路人生|Circuitry Life 版本修订记录 Version 1.0 2.0 2.1 2.2 Author zhiyuh zhiyuh zhiyuh Zhiyuh Data 2009‐6‐3 2009‐6‐12 2009‐07‐09 2009‐08‐22 Cyclone II EP2C5/8 Start Board Description First draft. 根据 Rev.B 电路图修改相关内容,并补充各电路 与 FPGA 之间的引脚连接定义。

增加兼容设计方面的解释内容,完善部分 BOM。

修改首页图片,BOM 增加备注。

备注:关于修订的说明 ~ 2 ~ 线路人生|Circuitry Life Cyclone II EP2C5/8 Start Board 目录 1. 模块介绍 ........................................................................................................................... 4 1.1 1.2 模块主要功能 ............................................................................................................ 4 模块适用范围 ............................................................................................................ 4 2. 包装清单 ........................................................................................................................... 4 2.1 2.2 模块包装清单 ............................................................................................................ 4 安装说明 .................................................................................................................... 4 3. 硬件说明 ........................................................................................................................... 5 3.1 电路说明 .................................................................................................................... 5 FPGA 芯片及主要外围电路............................................................................... 5 电源电路 ............................................................................................................ 7 存储器电路 ........................................................................................................ 8 板载 LED 测试电路 .......................................................................................... 13 IO、控制线和总线引出接口 .......................................................................... 14 . 硬件的其它说明 .............................................................................................. 15 3.1.1. 3.1.2. 3.1.3. 3.1.4. 3.1.5. 3.1.6. 3.2 3.3 4. 5. 6. 7. 器件清单(BOM) ................................................................................................. 15 . 电路板相关尺寸参数 .............................................................................................. 17 使用注意事项 ................................................................................................................. 17 技术支持 ......................................................................................................................... 18 硬件原理图 ..................................................................................................................... 18 其它备注 ......................................................................................................................... 18 ~ 3 ~ 线路人生|Circuitry Life Cyclone II EP2C5/8 Start Board 1. 模块介绍 1.1 模块主要功能 数字系统和 SOPC 设计在广大学生和爱好者中已经形成了一定的学习氛围和规模,但市 场上的开发板和学习板良莠不齐,为此线路人生|Circuitry Life 特设计了本模块,中文名为 “Cyclone II EP2C5/8 启蒙板” ,英文名为“Cyclone II EP2C5/8 Start Board” 。

Altera Cyclone II

Altera Cyclone II FPGA 帮助Newtec 实现了灵活的高性能双向卫星宽带终端

在当今高速视频下载和数据传输环境中,互联网已经成为世界上很多家庭

的日常工具。

该技术虽然发展很快,但是欧洲仍有很多农村地区还没有宽带

接入——直到现在。

Altera 公司日前宣布,Newtec 获得大奖的Sat3Play 宽带终端采用了Cyclone II FPGA 来提供宽带服务。

Sat3Play 宽带终端是双向卫星系统的组成部分,支持ISP 和电信公司在还没有实现低成本宽带链接的地区提供语音、数据和电视服务。

Newtec 是卫星通信产品和解决方案的世界级供应商,产品包括DVB 调制器、数字电视、

射频分配网络、电视网络和IP 宽带接入网等。

Altera Cyclone II 器件实现了灵活、可更新的Sat3Play 宽带终端。

在终端中,Cyclone II 器件用作ASSP 协处理器,处理返回通道的上游调制,对协议封装数据进行滤波,传输并接收IP 数据包,同时处理PCI 等关键系统接口。

Newtec 营销副总裁Max d’Oreye 评论说:“多年以来,欧洲的部分互联网用户在宽带接入上一直没有选择余地。

受居住地区的限制,他们不得不使用PSTN 或者ISDN 来接入互联网。

现在,Sat3Play 用户可以随心所欲地随时随地接入互联网。

Altera 的Cyclone II FPGA 为这一大批量应用提供了高性价比解决方案,我们能够更高效地提高宽带终端的带宽,从而使这一接入方式成

为现实。

”。

Cyclone II代芯片分析班级:1211自动化学号:2012118064姓名:英雄有泪Cyclone系列芯片是Altera公司推出的新一代低成本、中等规模的FPGA,其价格仅为Altera现有主流器件的30%~50%。

它通过去掉DSP块,MegaRAM,降低LVDS接口速率等指标后,可适应大多数设计的要求,同时分担用户所面临的成本压力。

该芯片采用0.13μm,全铜SRAM工艺,1.5v内核,同时还拥有2910个逻辑单元到20060个逻辑单元以及59904位RAM到294912位RAM,这使得它可用于实现多种复杂的功能。

此外,该芯片还提供了用于时钟管理的锁相环和用于连接工业标准外部存储器的专用I/O接口;而且,多种IP 核及Altera发布的Nios嵌入式微处理器软核均能在其上实现。

最后,我们具体实现了一个基于Cyclone FPGA的电子时钟的设计。

可编程器件方面,我们选用的是240管脚PQFP封装的EP1C12器件;配置时则是采用主动串行配置方案下的EPCS1器件。

在此,论文主要讲解了板卡的组成、内部设计及仿真,其中内部实现包括:原理图、PCB图的绘制和VHDL程序的编写。

Cyclone系列芯片的结构分析Cyclone现场可编程逻辑阵列芯片系列是一款低价格中等密度的FPGA,采用0.13μm的全铜SRAM工艺,容量从2910个逻辑单元到20060个逻辑单元(LEs:Logic Elements),1.5v内核。

Cyclone的性价比较高,它提供用于时钟控制的锁相环(PLLs:Phase-Locked Loops),同时它还有一个专用的双倍数据传输率(DDR)接口用于满足DDR SDARM和FCRAM(fast cycle RAM)存储器的需要,Cylone器件支持多种I/O标准接口,包括数据传输率可达311Mbps的LVDS(Low Voltage Differential Signaling,低电压差分信号)和66 MHz/32 bits的PCI接口,同时还支持ASSP(Application-specific Standard Products)和ASIC (Application-specific Integrated Circuit)器件。

一、外文资料译文:Cyclone II器件系列简介关键词:cyclone II器件;特点;简介;在非常成功的第一代Cyclone器件系列之后,Altera的Cyclone II FPGA系列扩大低成本的FPGA的密度,最多达68,416个逻辑单元(LE),提供622个可用的输入/输出引脚和1.1M比特的嵌入式寄存器。

Cyclone II器件的制造基于300毫米晶圆,采用台积电90nm、低K值电介质工艺,这种工艺技术是使用低绝缘体过程以确保了快速有效性和低成本。

通过使硅片面积最小化,Cyclone II器件可以在单芯片上支持复杂的数字系统,而在成本上则可以和ASIC竞争。

不像其他用电力功耗和性能来换取低成本的FPGA卖主,Altera 最新一代低价位的FPGA——cyclone II FPGA系列,和同类90nmFPGA器件相比,它提高了百分之六十的性能和降低了一半的功耗。

低成本和优化特征使Cyclone II FPGA系列为各种各样的汽车、消费、通讯、视频处理、测试与测量、和其他最终市场提供理想的解决方案。

在参考设计、系统图,和IP,使用cyclone II FPGA系列可以帮助你迅速实现最总市场方案开发。

低成本的嵌入式解决方案Cyclone II 器件支持Nio s II 嵌入式处理器,能够自己完成自定义的嵌入式处理器。

Cyclone II器件还能够扩展各种外部存储器和I/O口或者嵌入式处理器的性能。

单个或多个NiosII嵌入式系统中嵌入式处理器也可以设计成cyclone II设备以提供一些额外的同时处理的能力或者甚至取代已经在你的系统中存在的嵌入式处理器。

使用cyclone II和nios II 能够拥有成本低和高性能处理方案的共同特点,和普通的产品相比,这个特点能够延长你的产品的生命周期,提高产品进入市场的时间。

低成本DSP方案单独使用cycloneII FPGA 系列或者或者作为数字信号处理(DSP)协处理器以提高数字信号处理(DSP)应用的性价比。

,你用以下cyclone II的特点和设计支持可以实现高性能低成本DSP系统:■150个18 × 18 乘法器■ 1.1 M比特的片内嵌入式存储器■高速的外部寄存器接口■数据处理的知识产权核■Mathworks Simulink 和Matlab设计软件与DSP Builder的接口■DSP 软件开发程序工具, Cyclone II 版本Cyclone II 器件包括一个强大的FPGA特征建立最优的低成本的应用包括广泛的密度,记忆,嵌入式乘数,和包装的选择。

Cyclone II器件支持低成本运用中常见的各种外部寄存器界面和I/O口协议。

来自Altera 和合作伙伴IP核使得Cyclone II界面和协议变的快速和简单。

Cyclone II设备系列拥有以下的特点:■4,608到68,416 LEs 的高密度的结构●M4K的嵌入式寄存器块●不减少逻辑的情况下有1.1M的可用的存储器●每个模块有4096比特寄存器(4,608比特每个模块包括512相同的比特)●可变的配置端口有×1, ×2, ×4, ×8, ×9, ×16, ×18, ×32和×36●×1, ×2, ×4, ×8, ×9, ×16, 和×18 配置的真实的双端口(一个读和一个写, 两个读,或者两个写) 操作●写入操作过程是字节写入●260-MHz 下运行■嵌入式乘法器●多达150名的18 -×18-bit乘数器,并且每个乘法器可配置为两个独立的9×9-bit的250-MHz性能的乘数器●可选的输入和输出的寄存器■先进的I/O口支持●支持高速微分I / O标准,包括LVDS,mini-LVDS,LVPECL,相对、微分HSTL,和差分SSTL●支持单端接地I / O标准,包括2.5-V和1.8-V,SSTL级别一和级别二、1.8-V和1.5-V HSTL级别一和级别二、3.3-V PCI和pci - x的1.0,330 -,2.5 -,1.8 -,和1.5-V LVCMOS,和3.3、2.5 ,1.8-V LVTTL●互连外围设备专业组(PCISIG) PCI 局部总线规格, 版本 3.0 符合 3.3-V的66或者32兆赫的33 -或64位接口的操作●拥有外部TI PHY总线接口和Altera公司PCI Express总线接口Megacore功能的PCI Express总线接口。

●133-MHz pci - x 1.0的规格兼容性●高速外部存储器的支持,包括Altera IP MegaCore 功能支持的外部单倍数据速率(SDR)、双倍数据速率(DDR)、DDR2 SDRAM器件以及第二代四倍数据速率(QDRII)SRAM器件,这些寄存器主要是为了易于使用。

●每个I/O 组成部分(IOE)有三个专用的存储器:一个输入寄存器,一个输出寄存器,和一个输入输出寄存器。

●可编程总线支持的特点●可编程输出设备扩展的特点●对I/O组成部分和逻辑门阵列进行可编程延时●I/O 存储分成单一的VCCIO和/或者VREF存储设置●I/O电压标准支持1.5-, 1.8-, 2.5-, 和3.3-接口●热插拔操作支持●实现了上电之前和上电过程中对器件和三态I/O缓冲的保护●可编程的高端输出●各种样品的终端匹配■灵活的时钟管理电路●层次时钟网路高达402.5-MHz的性能●每个器件多达四个可编程锁相环(PLL)和提供时钟乘法器和除法器,相移,可编程占空比, 和外部时钟输出, 被允许的系统时钟管理和频率合成●贯穿整个设备有多大16个全局时钟线在整个全局时钟网络中■设备的配置●快速系列配置的时间限制在100ms以内●减压的特性实现了更小的程序文件存储和更快的配置时间●支持多种配置模式: 主动配置方式,被动配置方式,和JTAG配置方式●支持低成本的配置设备的配置●设备配置支持多种电压 (包括 3.3, 2.5,或者 1.8 V)■知识产权●支持Altera 宏功能和Altera MegaCore 功能,并且支持Altera合作伙伴计划(AMPPSM)宏功能, 具有广泛的可编程处理器,开芯片和关芯片的接口,强大的功能,DSP功能和通讯功能和协议。

访问的Altera IPMegaStore可以下载IP MegaCore功能●Nios II可编程处理器的支持Cyclone II 的一些快速接通型号具有较短的上电复位(POR)时间。

拥有快速接通特性的器件在订购码中用字母“A‖标出。

例如:EP2C5A, EP2C8A, EP2C15A, 和EP2C20A。

EP2C5A只能提供汽车速度级型。

EP2C8A 和EP2C20A只能提供工业级型。

EP2C15A只能提供快速接通型,并且可以提供商业型的和工业型的。

标注有‖A‖的cyclone II 器件和没有标注‖A‖的器件具有相同的特性和功能,唯一的不同就是它具有较短的上电复位时间。

表格1—1列出了cyclone II 系列器件的特性。

表格1—2列出了cyclone II器件的封装和用户I/O管脚数。

表1注释:1.EP2C15A只能提供快速接通型。

这个器件具有较短的上电复位(POR) 时间,并且可以提供商业型的和工业型的。

2、EP2C5,EP2C8的,EP2C20选择性地支持快速接通的特点,拥有这个特点的型号用‖A‖在订购码中用标注出来。

EP2C5A只能提供汽车速度级型。

EP2C8A 和 EP2C20A只能提供工业级型。

3. 这是18x18个乘法器总的所有乘法器。

每个器件的9x9乘法器的所有数量乘以2等于18x18乘法器的数量。

表1-2注释:(1)在相同的封装下cyclone II 设备支持直接替换(例如:你能够在用484-pin FineLine BGA封装的EP2C20器件和具有相同的封装的EP2C35和EP2C50器件之间替换。

(2)Quartus II 软件I/O管脚数包括额外的管脚,TDI, TDO, TMS, 和TCK,这些管脚被用为通用的I/O管脚。

(3)TQFP = 薄四方扁平封装(4)PQFP = 塑封四方扁平封装(5)EP2C5F256 和EP2C8F256器件支持直接替换。

不过,不是所有的单一数据选通(DQS)管脚和相关数据(DQ)管脚都是支持的。

用F256封装的EP2C5 和EP2C15器件就不支持直接替换。

(6)EP2C5, EP2C8, 和EP2C15A 器件的I/O管脚数包括8个专用时钟管脚,并且这8个管脚能够被用作数据输入引脚。

EP2C20, EP2C35, EP2C50, 和EP2C70 器件的I/O管脚数包括16个专用时钟管脚,并且这16个管脚能够被用作数据输入引脚。

(7)EP2C8A, EP2C15A, 和EP2C20A有快速接通的特性,有较短的上电复位的时间。

EP2C15A只能提供快速接通的型号。

(8)EP2C5选择性地支持快速接通的特点,拥有这个特点的型号用‖A‖在订购码中用标注出来。

EP2C5A只能提供汽车级型号。

参考cyclone II 的汽车级器件手册部分。

在相同的封装下cyclone II 设备支持直接替换(例如:你能够在用672-pin FineLine BGA 封装的EP2C35, EPC50 和EP2C70器件之间移动。

)cyclone II 系列支持的直接替换的例子在表格1-3中标注出来了。

直接替换的意思是你能够替换到某种器件上,这种器件的专门引脚,配置引脚和电源引脚在高密度器件中有着相同的封装。

表格1-3的注释:(1)EP2C5F256 到 EP2C15AF256和EP2C5F256 到 EP2C20F256器件不支持直接替换。

(2)当封装从EP2C20F484器件替换到EP2C50F484器件时,总共有39个I/O引脚的封装没有移动。

(3)当封装从EP2C35F672器件替换 EP2C70F672器件时,总共有56个I/O引脚的封装没有移动(4)除了没有移动的I/O引脚,有34个DQ信号引脚也没有移动。

(5)引脚484 FBGA和 484 UBGA是一样的。

为了确保你的电路板布局能够适应已封装的可移动密度,我们在quartus II软件环境下进行直接替换(选择Assignments 菜单,然后Device,然后点击Migration Devices按钮)。

编译之后,检查I/O, DQ, LVDS和其他引脚的信息清单,这些引脚因为选择的路径而不可用是。

表格1-3列出了cyclone II器件的封装和当封装从一个器件移动到另外一耳光器件的时不能移动的I/O引脚的数量。