OrCAD Capture

- 格式:doc

- 大小:32.50 KB

- 文档页数:4

orcad capture cis使用说明Orcad Capture CIS是一款强大的电路设计软件,它是OrCAD电路设计套件中的一部分。

本文将为您提供Orcad Capture CIS的使用说明,以帮助您更好地掌握该工具的功能和操作方法。

首先,Orcad Capture CIS为电路设计提供了完整的解决方案。

它结合了图形化电路编辑工具和零件库管理系统,可以帮助工程师更轻松地创建和编辑电路图,并自动检查和管理零件库存信息。

在使用Orcad Capture CIS之前,您需要安装并启动软件。

一旦启动,您将看到主界面,其中包括工程管理面板、工具栏和画布区域。

要创建新的电路图,只需点击菜单栏中的“文件”->“新建”->“项目”,然后选择电路图类型。

在编辑电路图时,您可以使用工具栏中的各种功能按钮,包括绘制线条、插入零件、连接线路等。

要插入零件,您可以通过搜索器或库浏览器找到所需的零件,并将其拖放到画布上。

注意,Orcad Capture CIS具有一个庞大的零件库,您可以根据自己的需要进行编辑和定制。

一旦完成电路图的设计,您可以进行进一步的操作。

例如,您可以运行布线操作来确保连接正确,使用网络列表来查看整个电路的信息,并生成报告以进行确认和共享。

除了基本功能外,Orcad Capture CIS还提供了许多高级功能和选项,如导入/导出数据、模拟仿真、错误检查等。

通过这些功能,您可以更精确地分析和改进您的电路图,并确保其性能和可靠性。

综上所述,Orcad Capture CIS是一款功能强大的电路设计软件,它提供了完整的解决方案,帮助工程师轻松地创建和编辑电路图。

通过使用Orcad Capture CIS,您可以更快速、更准确地进行电路设计,并使您的项目得以顺利实施。

请注意,本文中所提供的Orcad Capture CIS使用说明仅为参考。

具体操作和功能可能因软件版本的不同而略有差异。

对于更详细和具体的操作指南,请参考Orcad Capture CIS的官方文档或联系相关技术支持。

orcadcapture学习笔记

1.进行DRC检查完成之后就可以生产网表,操作如下。

图1 图2

2.然后在Rreate Netliset界面下先勾选“Create PCB Editor Netlist”,软件默认这项是勾选上的,然后网表会默认保存在allegro 文件夹下,如果没有该文件夹,软件会自行创建一个文件夹。

然后勾选Create or Update PCB Editor Board(Netrev)创建一个.brd文件,在Output Board中选择.brd保存的位置。

最后选择是否需要打开.brd 文件。

图2

3.生成网表的时候如果出下下面的提示,意思是你的文件夹下没有allegro文件夹,它提示是否要建立一个文件夹,点击“是”即可。

图2

4.网表生成后,一般有这几个文件:pstchip.dat、pstxnet.dat、pstxprt.dat、netlist.log、pxlBA.txt

图2。

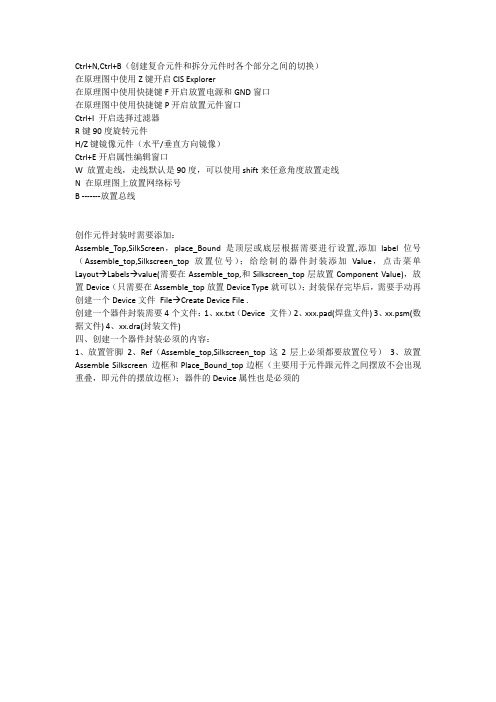

Ctrl+N,Ctrl+B(创建复合元件和拆分元件时各个部分之间的切换)在原理图中使用Z键开启CIS Explorer在原理图中使用快捷键F开启放置电源和GND窗口在原理图中使用快捷键P开启放置元件窗口Ctrl+I 开启选择过滤器R键90度旋转元件H/Z键镜像元件(水平/垂直方向镜像)Ctrl+E开启属性编辑窗口W 放置走线,走线默认是90度,可以使用shift来任意角度放置走线N 在原理图上放置网络标号B -------放置总线创作元件封装时需要添加:Assemble_Top,SilkScreen,place_Bound是顶层或底层根据需要进行设置,添加label位号(Assemble_top,Silkscreen_top放置位号);给绘制的器件封装添加Value,点击菜单Layout→Labels→value(需要在Assemble_top,和Silkscreen_top层放置Component Value),放置Device(只需要在Assemble_top放置Device Type就可以);封装保存完毕后,需要手动再创建一个Device文件File→Create Device File .创建一个器件封装需要4个文件:1、xx.txt(Device 文件)2、xxx.pad(焊盘文件) 3、xx.psm(数据文件) 4、xx.dra(封装文件)四、创建一个器件封装必须的内容:1、放置管脚2、Ref(Assemble_top,Silkscreen_top这2层上必须都要放置位号)3、放置Assemble Silkscreen 边框和Place_Bound_top边框(主要用于元件跟元件之间摆放不会出现重叠,即元件的摆放边框);器件的Device属性也是必须的。

orcad capture cis 磁珠符号

在Orcad Capture CIS中,磁珠的符号通常是一个电感器符号,其中包含一个箭头表示磁通量方向。

磁珠通常用于吸收高频噪声,因此其符号也包括一个噪声抑制符号或类似的标记。

具体来说,磁珠的符号可以表示为一个电感器符号,并在旁边加上一个小的箭头,以指示磁通量方向。

在某些情况下,还可以在磁珠符号旁边添加一个小的横线,表示磁珠的作用范围。

此外,Orcad Capture CIS还提供了多种预定义的元件库,其中包括磁珠元件。

用户可以从库中选择适合的元件符号并将其拖拽到电路图中,也可以使用工具栏中的“Place”按钮来手动绘制磁珠符号。

总之,磁珠的符号在Orcad Capture CIS中通常是表示为一个电感器符号,并添加一些标记来表示其特性和作用。

(完整版)OrCADCaptureCIS(Cadence原理图绘制)OrCAD Capture CIS(Cadence原理图绘制)1.新建原理图 (2)1,打开软件 (2)2,设置标题栏 (2)3,创建⼯程⽂件 (4)4,设置颜⾊ (4)2.制作原理库 (6)1,创建元件库 (6)2,修改元件库位置,新建原理图封库 (6)3,原理封装库的操作 (7)3.绘制原理图 (9)1.加⼊元件库,放置元件 (9)2.原理图的操作 (10)3. browse命令的使⽤技巧 (12)4.元件的替换与更新 (13)4.导出⽹表 (14)1.原理图器件序号修改 (14)2.原理图规则检查 (15)3.显⽰DRC错误信息 (16)4.创建⽹表 (17)5.⽣成元件清单(.BOM) (18)设计⽬的:创建如图RS232转换RS422原理图1.新建原理图1,打开软件2,设置标题栏Options-------DesignTemplate创建完原理图⼯程后,也可以修改标题栏Options--------Schematic Page Properties3,创建⼯程⽂件File------New------Projet4,设置颜⾊Options--------Preferences2.制作原理库1,创建元件库File-------New----Library2,修改元件库位置,新建原理图封库点击如图位置⿏标右击,点击Save As另存为。

New Part新建⼀个封装库。

3,原理封装库的操作Place------Pin 放置管脚选中管脚,按住键盘Ctrl同时⿏标拖动器件完成管脚的复制选中管脚⿏标右击Edit Properties 编辑选中管脚信息,如下图Place------Rectangle 放置矩形Place------line 放置线Place------Text 放置⽂字Place------ellipse 放置椭圆Options-----Part Properties 原理封装库属性Options-----Package Properties 原理封装库信息View------- Package 显⽰这个封装库的所有部分快捷键I-----放⼤O----缩⼩Delete-------删除最终根据操作完成MAX3221ECAE原理图库的编辑3.绘制原理图1.加⼊元件库,放置元件1.打开原理图⼯程,打开原理图2.Place-------Part(快捷键P)添加封装注:软件⾃带库路径,如下图所⽰常⽤到的电容电阻库2.原理图的操作1.快捷键I-----放⼤O----缩⼩Delete-------删除W-------放置⾛线R----旋转⽅向按住Alt键拖动器件可以切断⽹络连接Edit-----Mirror-----Horizontally ⽔平⽅向镜像Edit-----Mirror------ vertically垂直⽅向镜像Edit-----Mirror---------Both整体镜像Edit-----Properties显⽰修改PCB封装信息2.选中器件,按住键盘Ctrl同时⿏标拖动器件完成器件的复制3.放置⾛线 1.⿏标左键双击终⽌布线2.画线时按住键盘Shift 任意⾓度⾛线4.放置电源5.放置地6.放置空⽹络7.放置节点8.相同原理图放置⽹络连接(快捷键N)9. 放置总线10. 总线⼊⼝(F4连续放置总线⼊⼝⽹络等⾃动递增)11. 不同原理图页⾯的⽹络连接12. 放置⽂字13.Options--------Preferences3. browse命令的使⽤技巧1.选中.dsn⽂件如图2.Edit----Browse-----Parts显⽰修改器件信息Edit----Browse-----Nets显⽰修改⽹络信息Edit----Browse-----DRC markers显⽰DRC错误信息Edit----Browse-----off-page connectors显⽰不同原理图页⾯的⽹络连接4.元件的替换与更新1.选中打开原理图⼯程中Design cache,如图⿏标右击Cleanup Cache清除原理图中不存在的元件封装库2.⿏标右击Design cache下所需要更新替换的封装库Replace Cache-------替换元件封装库,如图所⽰Update Cache--------更新封装库最终经过以上操作完成如图所⽰原理图绘制4.导出⽹表注:导⽹表之前的注意事项:1.原理图器件序号修改2.原理图规则检查3.PCB封装库是否正确⽆误,属性是否正确4.⽹络管脚顺序是否准确5.如果建⽴⽹络表时出现错误,查看“Sessions log”中错误信息1.原理图器件序号修改1.选中.dsn⽂件如图2.Tools-------Annotate第⼀步:清除所有器件序号第⼆步:重新增加器件序号2.原理图规则检查Tools-----Design Rules Check3.显⽰DRC错误信息Edit----Browse-----DRC markers4.创建⽹表Tools------Create Netlist如果建⽴⽹络表时出现错误,查看“Sessions.log与netlist.log”中错误信息5.⽣成元件清单(.BOM) 注:⽣成清单前请先创建⽹表1,先选中如图.dsn⽂件2,Tools---------Bill of Materials按照公司规范进⾏元件清单处理:10KMCSY清单.xlsx。

orcad capture 电源引脚连接方法在使用Orcad Capture进行电路设计时,连接电源引脚是非常重要的一步。

正确的引脚连接方法可以确保电路的正常工作和可靠性。

下面我将介绍一种常见的电源引脚连接方法。

首先,打开Orcad Capture软件并创建一个新的电路设计文件。

1. 在元件库中选择所需的电源元件,例如电源模块或电源芯片。

将所选元件拖放到工作区。

2. 拖放元件后,可以看到元件上标有相应的引脚标号。

通常,电源元件具有标有"VCC"和"GND"的引脚,分别代表正电源和地引脚。

为了连接电源引脚,按照以下步骤进行操作:3. 在元件库中选择连接器元件。

连接器元件用于连接电源引脚和其他元件的引脚。

4. 将连接器元件拖放到元件引脚的位置。

确保连接器和电源元件的引脚位置相吻合。

5. 使用线条工具连线连接器和电源元件的引脚。

连接正电源引脚(VCC)到一个单独的连接器引脚,并连接地引脚(GND)到另一个单独的连接器引脚。

6. 连接连接器引脚到其他需要供电的元件引脚。

这些元件可以是IC芯片、传感器、各种电子器件等。

7. 在连接完成后,您可以使用布线工具将线条进行调整,以确保没有交叉或重叠。

在连接电源引脚时,还需要注意以下几点:- 根据您的电路设计需求,保证电源引脚与其他元件的正确连接。

- 确保引脚连接的电路板布局符合您的电路规范和标准。

- 在绘制连接线时,使用合适的线宽和线型,以便于设计中的电流传输和接地。

- 连接引脚时,要小心避免线路之间的短路或过度拥挤。

注意:根据具体的电路设计要求,可能会有其他特殊的电源引脚连接方法。

请在设计过程中参考相关的技术文档、标准和指南,以及遵循电路设计的最佳实践。

总的来说,通过正确连接电源引脚,您可以确保电路的正常供电和工作。

Orcad Capture提供了丰富的工具和选项,帮助您方便地完成电源引脚的连接。

希望以上介绍能够对您的电路设计有所帮助。

orcad capture 层次化设计单模块多次复用功能说明1. 引言1.1 概述本文将介绍OrCAD Capture的层次化设计单模块多次复用功能。

OrCAD Capture是一款电子设计自动化软件,可以帮助工程师进行电路图设计和仿真分析。

在大型电路项目中,经常需要使用相同的电路模块进行多次复用,在这种情况下,OrCAD Capture的层次化设计单模块多次复用功能就起到了重要作用。

1.2 文章结构本文分为以下几个部分来介绍OrCAD Capture的层次化设计单模块多次复用功能。

首先,在正文部分将详细介绍这一功能的使用方法和注意事项。

随后,通过示例案例来演示该功能在实际工程中的应用。

最后,在结论部分对文章进行总结,并展望未来发展。

1.3 目的本文旨在帮助读者更好地理解和掌握OrCAD Capture的层次化设计单模块多次复用功能。

通过详细介绍其功能特点、使用方法和示例案例,读者能够清晰了解该功能在电路设计中的作用和优势,并能够熟练运用该功能进行电路图设计和仿真分析。

以上是“1. 引言”部分内容,请根据需求进一步完善。

2. 正文:在进行电路设计时,OrCAD Capture是一个常用的集成化软件工具,它提供了层次化设计和单模块多次复用功能。

这些功能为电路设计者提供了便利和灵活性。

层次化设计是OrCAD Capture中的一项重要功能。

它使得我们可以将一个大型电路分解为多个子模块进行设计,每个子模块都可以独立开发和测试。

这样做不仅能够提高工作效率,还可以减少错误的发生和修正的难度。

同时,使用层次化设计能够更好地组织和管理复杂的电路图,并且有助于后续的维护和升级。

单模块多次复用是另一个非常实用的功能。

通过使用该功能,我们可以将一个设计好的电路模块保存到库文件中,并在需要使用相同功能或相似结构的情况下直接复用该模块,而不必重新设计整个电路。

这种模块级别的复用极大地提高了工作效率,并且保证了在不同项目之间共享已经验证过并可靠的电路部分。

OrCAD Capture 原理图对话框中英对照OrCAD常用文档类型

收藏

*.opj—项目管理文件

*.dsn—电路图文件

*.olb—图形符号库文件

*.lib—仿真模型描述库文件

*.mnl—网络表文件

*.max—电路板文件

*.tch—技术档文件

*.gbt—光绘文件

*.llb—PCB封装库文件

*.log *.lis—记录说明文件

*.tpl—板框文件

*.sf—策略档文件

系统属性包括(Options>Preferences):

Colors/Print:颜色设置

Grid Display:调整显示网格模式

Pan and Zoom:设置放大与缩小的倍数

Select:鼠标选择模式

Miscellaneous:其它的设置和线、填充样式

Text Editor:set something about text editor

系统设计模板参数包括(Options>Design Template):

Fonts:规定所有种类的字体

Title Block:标题栏内容的设定

Page Size:要绘制的图纸大小

Grid Reference:边框的设定与显示

Hierarchy:设置阶层的属性

SDT Compatibility:与SDT文件兼容性的设置

在菜单栏中选择file>new>Project:

Analog or Mixed-signal Circuit :本工程以后将进行数/模混合仿真

PC Board Wizard :本工程以后将用来进行印刷版图设计

Programmable Logic Wizard :本工程以后将用于可编程器件的设计(在9.2版本已经不支持)

Schematic :本工程只进行原理图设计

Name :项目文件名

Location :项目存盘路径

DRC检测(Tools>Design Rules Check),

Scope:

Check entire design:DRC检查整个原理图

Check Selection:DRC只检查你选择的部分

Mode:

Use instances(preferred):使用当前属性(建议)

Action:

Check design rules:进行DRC检测

Delete existing DRC marker:删除DRC检测标志

Report:DRC检测的内容

Create DRC markers for warnings:在警告的地方放置标志

Check hierarchical port connection:检测阶层端口的连接性

Check off-page connector connection:检测分页图纸间接口的连接性

Report identical part references:报告同样的器件序号

Report invalid packaging:报告无效的封装

Report hierarchical ports and off-page connection:报告阶层端口和分页图纸间接口的连接

Check unconnected net:检测未连接的网络

Check SDT compatibility:检测对于SDT文件的兼容性

Report all net name:报告所有网络名称

自动排序功能(或Tools>Annotate):

Scope:

Update entire design:更新整个设计

Update selection:更新选择的部分

Action:

Incremental reference update:在现有的基础上进行增加排序

Unconditional reference update:无条件进行排序

Reset part reference to “?”:把所有的序号都变成“?”

Add Intersheet References:在分页图纸间的端口的序号加上图纸编号

Delete Intersheet References:删除分页图纸间的端口的序号上的图纸编号Combined property:把对话框中的属性相结合

Reset reference numbers to begin at 1 each page:编号时每张图纸都从1开始Do not change the page number:不要改变图纸编号

自动更新器件或网络的属性(自已定义封装)Tools>Update Properties,

Use case insensitive compares:不考虑器件的灵敏度

Convert the update property to uppercase:把更新的属性转换成大写字母Unconditionally update the property:无条件更新属性

Do not change updated properties visibility:不改变器件更新的属性的可见属性Make the updated property visible:使器件更新的属性可见

Make the updated property invisible:使器件更新的属性不可见

Create a report file:产生报告文件

Property Update:要更新的属性文件

属性文件的格式如下(可以用记事本编辑,存为文本文件即可):

第一行:”{属性栏位名称}”“要置换的属性”

第二行:开始描述

注:需要置换的属性可以有多个。

"{Value}" "PCB Footprint"

"74LS00" "14DIP300"

"74LS138" "16DIP300"

"74LS163" "16DIP300"

"8259A" "28DIP600"

产生交互参考报表(Tools>Cross Reference…)

Sort output by part value, then by reference:先报告Value后报告reference,并按value排序

Sort output by reference designator, then by value:先报告reference后报告V alue,并按reference排序

Report the X and Y coordinates of all parts:报告器件的X、Y坐标

Report unused parts in multiple part packages:报告一个封装里没有使用的器件

产生材料清单(Tools>Bill of Materials…)

Line Item Definition:定义材料清单的内容

Place each part entry on a separate:材料清单中每个器件信息占一行

Include File:在材料清单中是否加入其他文件

建立器件图形符号库File>new>library

Name:器件的名称

Part reference:器件在原理图中编号的首字母

PCB Footprint:器件相对应的封装

Part per:一个器件封装中包含多少个器件

Homogeneous:封装中的器件都一样

Heterogeneous:封装中的器件不一样

Alphabetic:以字母区别封装中的多个器件

Numeric:以数字区别封装中的多个器件

/read-htm-tid-5562.html。