AT24C02中文资料

- 格式:pdf

- 大小:873.02 KB

- 文档页数:7

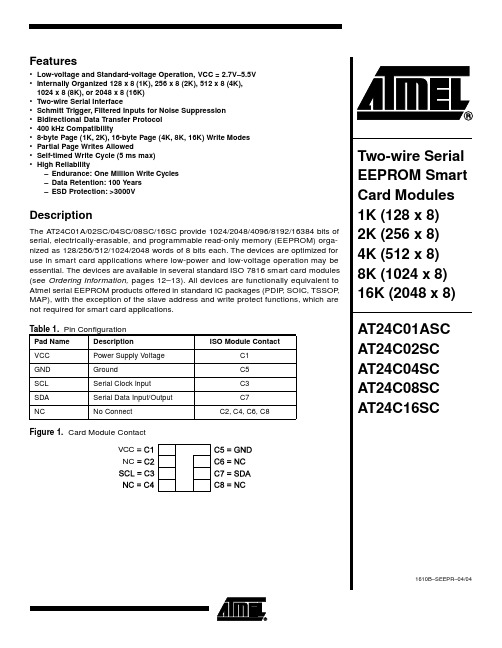

1Features•Low-voltage and Standard-voltage Operation, VCC = 2.7V–5.5V •Internally Organized 128 x 8 (1K), 256 x 8 (2K), 512 x 8 (4K),1024 x 8 (8K), or 2048 x 8 (16K)•Two-wire Serial Interface•Schmitt Trigger, Filtered Inputs for Noise Suppression •Bidirectional Data Transfer Protocol •400 kHz Compatibility•8-byte Page (1K, 2K), 16-byte Page (4K, 8K, 16K) Write Modes •Partial Page Writes Allowed•Self-timed Write Cycle (5 ms max)•High Reliability–Endurance: One Million Write Cycles –Data Retention: 100 Years –ESD Protection: >3000VDescriptionThe AT24C01A/02SC/04SC/08SC/16SC provide 1024/2048/4096/8192/16384 bits of serial, electrically-erasable, and programmable read-only memory (EEPROM) orga-nized as 128/256/512/1024/2048 words of 8 bits each. The devices are optimized for use in smart card applications where low-power and low-voltage operation may be essential. The devices are available in several standard ISO 7816 smart card modules (see Ordering Information, pages 12–13). All devices are functionally equivalent to Atmel serial EEPROM products offered in standard IC packages (PDIP , SOIC, TSSOP ,MAP), with the exception of the slave address and write protect functions, which are not required for smart card applications.Figure 1. Card Module Contact2AT24C01ASC/02SC/04SC/08SC/16SC1610B –SEEPR –04/04Figure 2. Block DiagramPin DescriptionSERIAL CLOCK (SCL): The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.SERIAL DATA (SDA): The SDA pin is bidirectional for serial data transfer. This pin is open-drain driven and may be wire-ORed with any number of other open-drain or open-collector devices.Memory OrganizationAT24C01ASC, 1K SERIAL EEPROM: Internally organized with 16 pages of 8 bytes each, the 1K requires a 7-bit data word address for random word addressing.AT24C02SC, 2K SERIAL EEPROM: Internally organized with 32 pages of 8 bytes each, the 2K requires an 8-bit data word address for random word addressing.Absolute Maximum Ratings*NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings ” may cause permanent dam-age to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.3AT24C01ASC/02SC/04SC/08SC/16SC1610B –SEEPR –04/04AT24C04SC, 4K SERIAL EEPROM: Internally organized with 32 pages of 16 bytes each, the 4K requires a 9-bit data word address for random word addressing.AT24C08SC, 8K SERIAL EEPROM: Internally organized with 64 pages of 16 bytes each, the 8K requires a 10-bit data word address random word addressing.AT24C16SC, 16K SERIAL EEPROM: Internally organized with 128 pages of 16 bytes each, the 16K requires an 11-bit data word address random word addressing.Pin CapacitanceDC CharacteristicsAC CC 2.V IL min and V IH max are reference only and are not tested.AC CharacteristicsTable 2. Pin Capacitance (1)Applicable over recommended operating range from T = 25°C, f = 1.0 MHz, V = +2.7VTable 3. DC Characteristics (1)(1)4AT24C01ASC/02SC/04SC/08SC/16SC1610B –SEEPR –04/04A CC (unless otherwise noted)2.This parameter is characterized and is not 100% tested.Device OperationCLOCK AND DATA TRANSITIONS: The SDA pin is normally pulled high with an exter-nal device. Data on the SDA pin may change only during SCL-low time periods (see Figure 3 on page 5). Data changes during SCL-high periods will indicate a start or stop condition as defined below.START CONDITION: A high-to-low transition of SDA with SCL high is a start condition that must precede any other command (see Figure 4 on page 6).STOP CONDITION: A low-to-high transition of SDA with SCL high is a stop condition.After a read sequence, the Stop command will place the EEPROM in a standby power mode (see Figure 4 on page 6).ACKNOWLEDGE: All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. Each word requires the receiver to acknowledge that it has received a valid command or data byte. During the transmission of commands from the host to the EEPROM, the EEPROM will send a zero to the host to acknowledge that it has received a valid command byte. This occurs on the ninth clock cycle of the com-mand byte. During read operations, the host will send a zero to the EEPROM to acknowledge that it has received a valid data byte and that it requests the next sequen-tial data byte to be transmitted during the subsequent eight clock cycles. This occurs on the ninth clock cycle of the data byte. If the host does not transmit this acknowledge bit,the EEPROM will disable the read operation and return to standby mode.STANDBY MODE: The AT24C01ASC/02SC/04SC/08SC/16SC feature a low-power standby mode that is enabled upon power-up and after the receipt of the stop bit and the completion of any internal operations.MEMORY RESET: After an interruption in protocol, power loss, or system reset, any two-wire part can be reset by following these steps:1.Clock up to 9 cycles.2.Look for SDA high in each cycle while SCL is high.3.Create a start condition as SDA is high.Table 4. AC Characteristics (1) (Continued)5AT24C01ASC/02SC/04SC/08SC/16SC1610B –SEEPR –04/04Timing DiagramsBus TimingFigure 1. Bus TimingNote:SCL: Serial Clock, SDA: Serial Data I/OWrite Cycle TimingFigure 2. Write Cycle TimingNotes:1.The write cycle time t WR is the time from a valid stop condition of a write sequence tothe end of the internal clear/write cycle.2.SCL: Serial Clock, SDA: Serial Data I/OData ValidityFigure 3.Data Validity6AT24C01ASC/02SC/04SC/08SC/16SC1610B –SEEPR –04/04Start and Stop DefinitionFigure 4. Start and Stop DefinitionOutput AcknowledgeFigure 5.Output Acknowledge7AT24C01ASC/02SC/04SC/08SC/16SC1610B –SEEPR –04/04Device AddressingThe 1K, 2K, 4K, 8K, and 16K EEPROM devices all require an 8-bit device address word following a start condition to enable the chip for a read or write operation (see Figure 6on page 7).The device address word consists of a mandatory “1”, “0”, “1”, “0” sequence for the first four most significant bits as shown. This is common to all the serial EEPROM devices.The next three bits of the device address word are the most significant data word address bits for the AT24C16SC (16K), which requires a total of 11 address bits. The AT24C08SC (8K) requires only 10 total word address bits. The most significant two bits are included in the device address word. The unused bit of the device address word should be set to “0”. The AT24C04SC (4K) requires only nine total data word address bits. The most significant bit is included in the device address word. The two unused bits of the device address word should be set to “0”. The AT24C02SC (2K) and AT24C01ASC (1K) do not require any address bits in the device address word. The three unused bits of the device address word should be set to “0”.The eighth bit of the device address is the read/write operation select bit. A read opera-tion is initiated if this bit is high, and a write operation is initiated if this bit is low.Upon a compare of the device address, the EEPROM will output a “0” (ACK). If a suc-cessful compare is not made, the chip will return to a standby state (NO ACK).Figure 6. Device AddressNote:P0, P1, P2 = Data word address bits8AT24C01ASC/02SC/04SC/08SC/16SC1610B –SEEPR –04/04Write OperationsBYTE WRITE: A write operation requires an 8-bit data word address following the device address word and acknowledgment. Upon receipt of this address, the EEPROM will again respond with a “0” (ACK) and then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output a “0” (ACK) and the addressing device, such as a microcontroller, must terminate the write sequence with a stop condi-tion. At this time the EEPROM enters an internally-timed write cycle, t WR , to the nonvolatile memory. All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (refer to Figure 7).Figure 7. Byte WritePAGE WRITE: The 1K/2K EEPROM is capable of an 8-byte page write, and the 4K, 8K,and 16K devices are capable of 16-byte page writes.A page write is initiated the same as a byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to 7(1K/2K) or 15 (4K, 8K, 16K) more data words. The EEPROM will respond with a “0”(ACK) after each data word received. The microcontroller must terminate the page write sequence with a stop condition (refer to Figure 8).Figure 8. Page WriteNote:* = DON ’T CARE bit for 1KThe data word address lower three (1K/2K) or four (4K, 8K, 16K) bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, retaining the memory page row location. When the word address,internally generated, reaches the page boundary, the following byte is placed at the beginning of the same page. If more than eight (1K/2K) or 16 (4K, 8K, 16K) data words are transmitted to the EEPROM, the data word address will “roll over ” and previous data will be overwritten.ACKNOWLEGE POLLING: Once the internally timed write cycle has started and the EEPROM inputs are disabled, acknowledge polling can be initiated. This involves send-ing a start condition followed by the device address word. The read/write bit is representative of the operation desired. Only if the internal write cycle has completed9AT24C01ASC/02SC/04SC/08SC/16SC1610B –SEEPR –04/04will the EEPROM respond with a “0” (ACK), allowing the read or write sequence to continue.Read OperationsRead operations are initiated the same way as write operations, with the exception that the read/write select bit in the device address word is set to “1”. There are three read operations: current address read, random address read, and sequential read.CURRENT ADDRESS READ: The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address “rollover ” during read is from the last byte of the last memory page to the first byte of the first page. The address “rollover ” during write is from the last byte of the cur-rent page to the first byte of the same page.Once the device address with the read/write select bit set to “1” is clocked in and acknowledged by the EEPROM, the current address data word is serially clocked out.The microcontroller does not respond with an input “0” but does generate a following stop condition (refer to Figure 9)Figure 9. Current Address Read.RANDOM READ: A random read requires a “dummy ” byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another start condition. The microcontroller now initiates a current address read by sending a device address with the read/write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a “0” (NO ACK) but does generate a following stop condition (refer to Figure 10).Figure 10. Random ReadNote:* = DON ’T CARE bit for 1K)10AT24C01ASC/02SC/04SC/08SC/16SC1610B –SEEPR –04/04SEQUENTIAL READ: Sequential reads are initiated by either a current address read or a random address read. After the microcontroller receives a data word, it responds with an acknowledge. As long as the EEPROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address limit is reached, the data word address will “rollover ” and the sequen-tial read will continue. The sequential read operation is terminated when the microcontroller does not respond with a “0” (NO ACK) but does generate a following stop condition (refer to Figure 11).Figure 11.Sequential Read11AT24C01ASC/02SC/04SC/08SC/16SC1610B –SEEPR –04/04AT24C01ASC Ordering InformationAT24C02SC Ordering InformationAT24C04SC Ordering InformationAT24C08SC Ordering InformationAT24C16SC Ordering Information12AT24C01ASC/02SC/04SC/08SC/16SC1610B–SEEPR–04/0413AT24C01ASC/02SC/04SC/08SC/16SC1610B –SEEPR –04/04Smart Card ModulesDisclaimer: Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company ’s standard warranty which is detailed in Atmel ’s Terms and Conditions located on the Company ’s web site. The Company assumes no responsibil ity for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time wit h out notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel ’s products are not auth orized for use as critical components in life support devices or systems.Atmel CorporationAtmel Operations2325 Orchard Parkway San Jose, CA 95131Tel: 1(408) 441-0311Fax: 1(408) 487-2600Regional HeadquartersEuropeAtmel SarlRoute des Arsenaux 41Case Postale 80CH-1705 Fribourg SwitzerlandTel: (41) 26-426-5555Fax: (41) 26-426-5500AsiaRoom 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Memory2325 Orchard Parkway San Jose, CA 95131Tel: 1(408) 441-0311Fax: 1(408) 436-4314Microcontrollers2325 Orchard Parkway San Jose, CA 95131Tel: 1(408) 441-0311Fax: 1(408) 436-4314La Chantrerie BP 7060244306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18Fax: (33) 2-40-18-19-60ASIC/ASSP/Smart CardsZone Industrielle13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00Fax: (33) 4-42-53-60-011150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906Tel: 1(719) 576-3300Fax: 1(719) 540-1759Scottish Enterprise Technology Park Maxwell BuildingEast Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000Fax: (44) 1355-242-743RF/AutomotiveTheresienstrasse 2Postfach 353574025 Heilbronn, Germany Tel: (49) 71-31-67-0Fax: (49) 71-31-67-23401150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906Tel: 1(719) 576-3300Fax: 1(719) 540-1759Biometrics/Imaging/Hi-Rel MPU/High Speed Converters/RF DatacomAvenue de Rochepleine BP 12338521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00Fax: (33) 4-76-58-34-80e-mailliterature@Web Site1610B –SEEPR –04/04© Atmel Corporation 2003. All rights reserved. Atmel ® and combinations thereof are registered trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be the trademarks of others.。

I2C总线AT24C02芯片运用1,I2C总线介绍:I2C总线(Inter IC Bus)由飞利浦公司推出,是近年来微电子控制领域广泛采用的一宗新型总线标准,它使同步通信的一种特殊形式,具有接口少、控制简单、器件封装形体小、通信速率较高等优点(可达400Kbps)。

在主从通信中,可以有多个I2C 总线器件同时接到I2C总线上,所有与I2C总线兼容的器件都具有标准的接口,通过地址来识别通信对象,是她可以经由I2C总线相互直接通信。

I2C总线由数据线和时钟线SDA和SCL两条线构成,可发送数据可接收数据。

于CPU 及被控IC间、IC与IC间均可双向传送,各器件均并于总线上,各自有唯一地址。

信息传输中,I2C总线上的各器件既是被控又是控制器件,既是发送器又是接收器。

CPU 发出的控制信号分为地址码和数据码两部分;地址码选址;数据码送数。

故而各IC虽同并于总线上但却各自独立。

I2C总线硬件结构图图中:ACL时钟,SDA数据接上拉电阻,故总线空闲是高电平,任一器件变低均将拉低电平故曰:各器件的时钟线及数据线乃“与”关系。

通信格式为时钟高时下跳开始寻地址发送一字节 8位中低位为数据方向 0为我党要向下面发指令形象的为“O”,俗称为蛋,如川蛋:“川O001”,陕蛋:“陕O001”都是当官的向下发指令,发飙的,当然,单片机哎平方C系统呢有点民主成分,从机可以向主机传信息,既发1,形象的成为“1”:咦你们小麻虾小老百信还要上方发信息呀??!!事实上是的 0为下蛋-----下传数据;1为上访-----上传数据。

记住了吧!时钟为高SCL=1时数据那得稳定俗称维稳期间当然时钟撤了 SCL=0时随便你虾子变化数据。

发送启动信号那得我们主机发了党外人士没这个权利在时钟为高警察在的时候主机发一个下跳沿信号表示开会了开始了既:SCL=1时 SDA 你们老百姓就等着查户口吧!当官的在警察在时下跳了于是衙门发令查户口高七位为你我家庭住址,最低一位为数据方向上面已表在此老子不说了。

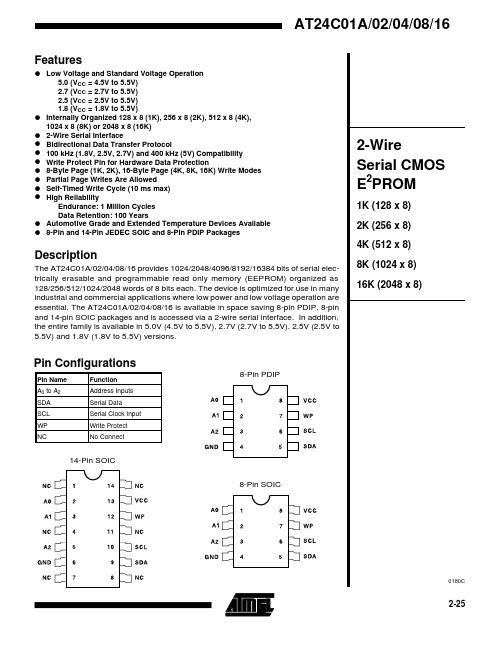

Features•Low Voltage and Standard Voltage Operation5.0 (V CC = 4.5V to 5.5V)2.7 (V CC = 2.7V to 5.5V)2.5 (V CC = 2.5V to 5.5V)1.8 (V CC = 1.8V to 5.5V)•Internally Organized 128 x 8 (1K), 256 x 8 (2K), 512 x 8 (4K),1024 x 8 (8K) or 2048 x 8 (16K)•2-Wire Serial Interface•Bidirectional Data Transfer Protocol•100 kHz (1.8V, 2.5V, 2.7V) and 400 kHz (5V) Compatibility •Write Protect Pin for Hardware Data Protection•8-Byte Page (1K, 2K), 16-Byte Page (4K, 8K, 16K) Write Modes •Partial Page Writes Are Allowed •Self-Timed Write Cycle (10 ms max)•High ReliabilityEndurance: 1 Million Cycles Data Retention: 100 Years•Automotive Grade and Extended Temperature Devices Available •8-Pin and 14-Pin JEDEC SOIC and 8-Pin PDIP PackagesDescriptionThe AT24C01A/02/04/08/16 provides 1024/2048/4096/8192/16384 bits of serial elec-trically erasable and programmable read only memory (EEPROM) organized as 128/256/512/1024/2048 words of 8 bits each. The device is optimized for use in many industrial and commercial applications where low power and low voltage operation are essential. The AT24C01A/02/04/08/16 is available in space saving 8-pin PDIP, 8-pin and 14-pin SOIC packages and is accessed via a 2-wire serial interface. In addition,the entire family is available in 5.0V (4.5V to 5.5V), 2.7V (2.7V to 5.5V), 2.5V (2.5V to5.5V) and 1.8V (1.8V to 5.5V) versions.Pin Configurations8-Pin PDIP8-Pin SOIC14-Pin SOICAT24C01A/02/04/08/16Block Diagram*NOTICE: Stresses beyond those listed under “Absolute Maxi-mum Ratings” may cause permanent damage to the device.This is a stress rating only and functional operation of thedevice at these or any other conditions beyond those indi-cated in the operational sections of this specification is notimplied. Exposure to absolute maximum rating conditionsfor extended periods may affect device reliability. Absolute Maximum Ratings*Pin DescriptionSERIAL CLOCK (SCL): The SCL input is used to positiveedge clock data into each E2PROM device and negativeedge clock data out of each device.SERIAL DATA (SDA): The SDA pin is bidirectional for se-rial data transfer. This pin is open-drain driven and may bewire-ORed with any number of other open-drain or opencollector devices.DEVICE/PAGE ADDRESSES (A2, A1, A0): The A2, A1and A0 pins are device address inputs that are hard wiredfor the AT24C01A and the AT24C02. As many as eight1K/2K devices may be addressed on a single bus system(device addressing is discussed in detail under the DeviceAddressing section).The AT24C04 uses the A2 and A1 inputs for hard wireaddressing and a total of four 4K devices may be ad-dressed on a single bus system. The A0 pin is a no con-nect.The AT24C08 only uses the A2 input for hardwire ad-dressing and a total of two 8K devices may be addressedon a single bus system. The A0 and A1 pins are no con-nects.The AT24C16 does not use the device address pins whichlimits the number of devices on a single bus to one. TheA0, A1 and A2 pins are no connects.(continued)Applicable over recommended operating range from: T AI = -40°C to +85°C, V CC = +1.8V to +5.5V, T AC = 0°C to +70°C,Note:1.V IL min and V IH max are reference only and are not tested.DC CharacteristicsWRITE PROTECT (WP): The AT24C01A/02/04/16 has a Write Protect pin that provides hardware data protection.The Write Protect pin allows normal read/write operations when connected to ground (GND). When the Write Protectpin is connected to V CC , the write protection feature is en-abled and operates as shown in the following table.Pin Description (Continued)Memory OrganizationAT24C01A, 1K SERIAL E 2PROM: Internally organized with 128 pages of 1-byte each, the 1K requires a 7 bit data word address for random word addressing.AT24C02, 2K SERIAL E 2PROM: Internally organized with 256 pages of 1-byte each, the 2K requires an 8 bit data word address for random word addressing.AT24C04, 4K SERIAL E 2PROM: The 4K is internally or-ganized with 256 pages of 2-bytes each. Random word addressing requires a 9 bit data word address.AT24C08, 8K SERIAL E 2PROM:The 8K is internally or-ganized with 4 blocks of 256 pages of 4-bytes each. Ran-dom word addressing requires a 10 bit data word address.AT24C16, 16K SERIAL E 2PROM: The 16K is internally organized with 8 blocks of 256 pages of 8-bytes each.Random word addressing requires an 11 bit data word ad-dress.Pin Capacitance (1)Note:1. This parameter is characterized and is not 100% tested.AT24C01A/02/04/08/16Note:1. This parameter is characterized and is not 100% tested.Applicable over recommended operating range from T A = -40°C to +85°C, V CC = +1.8V to +5.5V, CL = 1 TTL Gate and100 pF (unless otherwise noted).AC CharacteristicsDevice OperationCLOCK and DATA TRANSITIONS: The SDA pin is nor-mally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods (refer to Data Validity timing diagram). Data changes during SCL high periods will indicate a start or stop condition as de-fined below.START CONDITION: A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (refer to Start and Stop Definition timing diagram).STOP CONDITION: A low-to-high transition of SDA with SCL high is a stop condition. After a read sequence, the stop command will place the E 2PROM in a standby power mode (refer to Start and Stop Definition timing diagram).ACKNOWLEDGE: All addresses and data words are se-rially transmitted to and from the E 2PROM in 8 bit words.The E 2PROM sends a zero to acknowledge that it has re-ceived each word. This happens during the ninth clock cy-cle.STANDBY MODE: The AT24C01A/02/04/08/16 features a low power standby mode which is enabled: (a) upon power-up and (b) after the receipt of the STOP bit and thecompletion of any internal operations.Bus Timing SCL: Serial ClockSDA: Serial Data I/OWrite Cycle Timing SCL: Serial Clock SDA: Serial Data I/ONote: 1.The write cycle time t WR is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.AT24C01A/02/04/08/16Data ValidityStart and Stop DefinitionOutput AcknowledgeDevice AddressingThe 1K, 2K, 4K, 8K and 16K E2PROM devices all require an 8 bit device address word following a start condition to enable the chip for a read or write operation (refer to Fig-ure 1).The device address word consists of a mandatory one, zero sequence for the first four most significant bits as shown. This is common to all the E2PROM devices.The next 3 bits are the A2, A1 and A0 device address bits for the 1K/2K E2PROM. These 3 bits must compare to their corresponding hard-wired input pins.The 4K E2PROM only uses the A2 and A1 device address bits with the third bit being a memory page address bit. The two device address bits must compare to their corre-sponding hard-wired input pins. The A0 pin is no connect. The 8K E2PROM only uses the A2 device address bit with the next 2 bits being for memory page addressing. The A2 bit must compare to its corresponding hard-wired input pin. The A1 and A0 pins are no connect.The 16K does not use any device address bits but instead the 3 bits are used for memory page addressing. These page addressing bits on the 4K, 8K, and 16K devices should be considered the most significant bits of the data word address which follows. The A0, A1 and A2 pins are no connect.The eighth bit of the device address is the read/write op-eration select bit. A read operation is initiated if this bit is high and a write operation is initiated if this bit is low. Upon a compare of the device address, the E2PROM will output a zero. If a compare is not made, the chip will return to a standby state.Write OperationsBYTE WRITE: A write operation requires an 8 bit data word address following the device address word and ac-knowledgement. Upon receipt of this address, the E2PROM will again respond with a zero and then clock in the first 8 bit data word. Following receipt of the 8 bit data word, the E2PROM will output a zero and the addressing device, such as a microcontroller, must terminate the write sequence with a stop condition. At this time the E2PROM enters an internally-timed write cycle to the nonvolatile memory. All inputs are disabled during this write cycle and the E2PROM will not respond until the write is complete (refer to Figure 2).PAGE WRITE: The 1K/2K E2PROM is capable of an 8-byte page write, and the 4K, 8K and 16K devices are ca-pable of 16-byte page writes.A page write is initiated the same as a byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the E2PROM acknowledges receipt of the first data word, the microcon-troller can transmit up to seven (1K/2K) or fifteen (4K, 8K, 16K) more data words. The E2PROM will respond with a zero after each data word received. The microcontroller must terminate the page write sequence with a stop con-dition (refer to Figure 3).The data word address lower three (1K/2K) or four (4K, 8K, 16K) bits are internally incremented following the re-ceipt of each data word. The higher data word address bits are not incremented, retaining the memory page row loca-tion. If more than eight (1K/2K) or sixteen (4K, 8K, 16K) data words are transmitted to the E2PROM, the data word address will “roll over” and previous data will be overwrit-ten.ACKNOWLEDGE POLLING: Once the internally-timed write cycle has started and the E2PROM inputs are dis-abled, acknowledge polling can be initiated. This involves sending a start condition followed by the device address word. The read/write bit is representative of the operation desired. Only if the internal write cycle has completed will the E2PROM respond with a zero allowing the read or write sequence to continue.Read OperationsRead operations are initiated the same way as write op-erations with the exception that the read/write select bit in the device address word is set to one. There are three read operations: current address read, random address read and sequential read.CURRENT ADDRESS READ: The internal data word ad-dress counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address “roll over” during read is from the last byte of the last memory page to the first byte of the first page. The address “roll over” during write is from the last byte of the current page to the first byte of the same page.Once the device address with the read/write select bit set to one is clocked in and acknowledged by the E2PROM, the current address data word is serially clocked out. The microcontroller does not respond with an input zero but does generate a following stop condition (refer to Figure 4).RANDOM READ: A random read requires a “dummy”byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the E2PROM, the micro-(continued) AT24C01A/02/04/08/16Figure 1.Device AddressFigure 2.Byte WriteFigure 3. Page Write(* = DON’T CARE bit for 1K)controller must generate another start condition. The mi-crocontroller now initiates a current address read by send-ing a device address with the read/write select bit high.The E 2PROM acknowledges the device address and seri-ally clocks out the data word. The microcontroller does not respond with a zero but does generate a following stop condition (refer to Figure 5).SEQUENTIAL READ: Sequential reads are initiated by either a current address read or a random address read.After the microcontroller receives a data word, it responds with an acknowledge. As long as the E 2PROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words.When the memory address limit is reached, the data word address will “roll over” and the sequential read will con-tinue. The sequential read operation is terminated when the microcontroller does not respond with a zero but does generate a following stop condition (refer to Figure 6).Read Operations(Continued)Figure 5. Random Read(*= DON’T CARE bit for 1K)Figure 4.Current Address ReadFigure 6. Sequential ReadAT24C01A/02/04/08/16Ordering InformationOrdering InformationOrdering Information。

24c02中文资料1. 简介24c02是Microchip公司推出的一种串行电子可擦写可编程读写存储器,属于EEPROM(Electrically Erasable Programmable Read-Only Memory)系列。

它采用2-wire串行总线(I2C)接口,具有体积小、功耗低、可靠性高等特点。

本文档将详细介绍24c02的硬件特性、接口规范、存储容量和使用方法。

2. 硬件特性24c02的主要硬件特性如下:•存储容量:24c02有256个字节,每个字节有8位,总计拥有2Kb的存储空间。

•工作电源:24c02需要使用3.3V到5V的供电电压,支持广泛的电源电压范围。

•通信接口:24c02使用I2C串行总线进行通信,具有两根信号线:串行数据线(SDA)和串行时钟线(SCL)。

•封装类型:24c02有多种封装类型可供选择,如DIP(双列直插式封装)、SOP(小型轻负载封装)等。

3. 接口规范24c02采用I2C串行总线接口,其接口规范如下:•数据传输方式:24c02支持字节读写操作和页写操作。

字节读写操作是指每次读写一个字节的数据;页写操作是指每次可以写入8个连续字节的数据。

•起始信号和停止信号:在I2C总线上进行通信时,需要发送起始信号(Start)和停止信号(Stop)以标识数据传输的开始和结束。

•从器件地址:24c02有多个从器件地址可供选择,通过设置硬件地址引脚,可以实现多个24c02器件的级联。

4. 存储容量24c02的存储容量为2Kb,相当于256个字节。

每个字节有8位,可存储0x00到0xFF的数据。

这些存储空间可以被分为多个页,每页包含8个字节。

5. 使用方法以下是24c02的基本使用方法,供参考:•初始化:将24c02与主控芯片(如单片机)连接,并提供正常的供电电源。

同时,设置24c02的硬件地址引脚,确保能正确寻址。

•写入数据:选择要写入数据的存储地址,发送起始信号和器件地址,然后发送数据字节。

S P E C I F I C A T I O N24C02/24C04/24C08/24C16Version 1.0Two-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8)▉FeaturesThe 24C02/24C04/24C08/24C16 provides 2048/4096/8192/16384 bits of serial electrically erasable and programmable read-only memory (EEPROM) organized as 256/512/1024/2048 words of 8 bits each. The device is optimized for use in many industrial and commercial applications wherelow-power and low-voltage operation are essential. The 24C02/24C04/24C08/24C16 is available in space-saving 8-lead PDIP, 8-lead SOP, and 8-lead TSSOP packages and is accessed via a two-wire serial interface.▉Pin ConfigurationTwo-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8)▉Pin DescriptionsTwo-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8)▉Pin Descriptions24C02, 2K SERIAL EEPROM: Internally organized with 32 pages of 8 bytes each, the 2K requires an 8-bit data word address for random word addressing.24C04, 4K SERIAL EEPROM: Internally organized with 32 pages of 16 bytes each, the 4K requires a 9-bit data word address for random word addressing.24C08, 8K SERIAL EEPROM: Internally organized with 64 pages of 16 bytes each, the 8K requires a 10-bit data word address for random word addressing.24C16, 16K SERIAL EEPROM: Internally organized with 128 pages of 16 bytes each, the 16K requires an 11-bit data word address for random word addressing.▉Device OperationTwo-wire Serial EEPROM 2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8)Two-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8) The 2K, 4K, 8K and 16K EEPROM devices all require an 8-bit device address word following a start condition to enable the chip for a read or write operation (see to Figure 4 on page 7).The device address word consists of a mandatory "1", "0" sequence for the first four most significant bits as shown. This is common to all the Serial EEPROM devices.The next 3 bits are the A2, A1 and A0 device address bits for the 2K EEPROM. These 3 bits must compare to their corresponding hardwired input pins.The 4K EEPROM only uses the A2 and A1 device address bits with the third bit being a memory page address bit. The two device address bits must compare to their corresponding hardwired input pins. The A0 pin is no connect.The 8K EEPROM only uses the A2 device address bit with the next 2 bits being for memory page addressing. The A2 bit must compare to its corresponding hard-wired input pin. The A1 and A0 pins are no connect.The 16K does not use any device address bits but instead the 3 bits are used for memory page addressing. These page addressing bits on the 4K, 8K and 16K devices should be considered the most significant bits of the data word address which follows. The A0, A1 and A2 pins are no connect.The eighth bit of the device address is the read/write operation select bit. A read operation is initiated if this bit is high and a write operation is initiated if this bit is low.Upon a compare of the device address, the EEPROM will output a "0". If a compare is not made, the chip will return to a standby state.▉Write OperationsTwo-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8) Read operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to "1". There are three read operations: current address read,random address read and sequential read.CURRENT ADDRESS READ: The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address "roll over" during read is from the last byte of the last memory page to the first byte of the first page. The address "roll over" during write is from the last byte of the current page to the first byte of the same page.Once the device address with the read/write select bit set to "1" is clocked in and acknowledged by the EEPROM, the current address data word is serially clocked out. The microcontroller does not respond with an input "0" but does generate a following stop condition (see Figure 7 on page 8).RANDOM READ: A random read requires a "dummy" byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another start condition. The microcontroller now initiates a current address read by sending a device address with the read/write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a "0" but does generate a following stop condition (see Figure 8 on page 8). SEQUENTIAL READ: Sequential reads are initiated by either a current address read or a randomTwo-wire Serial EEPROM 2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8)Two-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8)l Absolute Maximum Stress RatingsDC Supply Voltage . . . . . . . . . . . . . . . . .-0.3V to +6.5V Input / Output Voltage . . . . . . . .GND-0.3V to V CC+0.3V Operating Ambient Temperature . . . . . -40℃to +85℃Storage Temperature . . . . . . . . . . . . -65℃to +150℃l CommentsStresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to this device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied or intended. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.Two-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8)▉DC Electrical CharacteristicsApplicable over recommended operating range from TA = 25 ℃, f = 1.0 MHz, VCC = +1.8V Parameter Symbol Min. Typ. Max. Unit ConditionCI/O - - 8 pF VI/O = 0V Input/Output Capacitance(SDA)Input Capacitance (A0, A1,CIN - - 8 pF VIN = 0V A2, SCL)▉AC Electrical CharacteristicsTwo-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8) Figure 10: SCL: Serial Clock, SDA: Serial Data I/OTwo-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8)▉Write Cycle Timing。

AT24C02芯片使用介绍AT24C02简介AT24C02是一个2K 位串行CMOS E2PROM ,内部含有256个8位字节,有一个16字节页写缓冲器。

该器件通过IIC 总线接口进行操作,有专门的写保护功能。

应用于AT24C02制造过程的先进CMOS 技术实质上减少了器件的功耗。

AT24C02特性1、采用I 2C 总线传输数据。

2、工作电压范围:1.8V ~6.0V 。

3、采用低功耗CMOS 技术制造。

4、当WP 为高电平时,AT24C02进入写保护状态。

5、页写缓冲器。

6、自定时擦写周期。

7、1,000,000 编程/擦除周期。

8、寿命长,可保存数据100 年。

9、2种封装:8脚DIP SOIC 或TSSOP 封装。

10、温度范围:商业级、工业级和汽车级。

AT24C02管脚描述1、SCL 串行时钟管脚AT24C02串行时钟输入管脚用于产生该器件所有数据发送或接收的时钟,SCL 串行时钟管脚是一个输入管脚。

2、SDA 串行数据AT24C02的双向串行数据管脚SDA,用于该器件所有数据的发送或接收。

SDA 管脚是一个开漏输出管脚。

3、A0、A1、A2 器件地址输入端这3个输入管脚用于多个器件级联时设置器件地址,当这些管脚悬空时默认值为0。

AT24C02 最大可级联8个器件。

如果只有一个AT24C02被总线寻址,这三个地址输入脚(A0、A1、A2 )可悬空或连接到Vss 或 GND。

4、WP 写保护如果WP管脚连接到Vcc,AT24C02中所有的内容都被写保护只能读。

当WP管脚连接到Vss 或 GND 或悬空时,允许AT24C02器件进行正常的读/写操作。

5、V管脚CC管脚接+1.8V~+6.0V 工作电压的正极。

AT24C02的VCC6、V SS 管脚AT24C02的V SS 管脚接+1.8V ~+6.0V 工作电压的负极(即GND )。

AT24C02的器件寻址AT24C02的芯片地址为1010,其地址控制字格式为1010A2A1A0R/W 。

AT24C02简介AT24C02简介AT24C02是美国Atmel 公司的低功耗CMOS 型E2PROM ,内含256*8位存储空间,具有⼯作电压宽(2.5V~5.5V),擦写次数多(⼤于10000次),写⼊速度快(⼩于10ms),抗⼲扰能⼒强,数据不易丢失,体积⼩等特点。

并且它是采⽤I2C 总线式进⾏数据读写的串⾏操作,只占⽤很少的资源和I/O 线。

A T24C02有⼀个16字节页写缓冲器,该器件通过I2C 总线接⼝进⾏操作,还有⼀个专门的写保护功能。

AT24C02的引脚如图3-9,各引脚功能如下:SCL :串⾏时钟输⼊管脚,⽤于产⽣器件所有数据发送或接收的时钟。

SDA :双向串⾏数据/地址管脚,⽤于器件所有数据的发送或接收。

A0、A1、A2:器件地址输⼊端。

这些输⼊脚⽤于多个器件级联时设置器件地址,当这些脚悬空时默认值为0。

使⽤AT24C02最⼤可级联8个器件,如果只有⼀个24C02被总线寻址,这三个地址输⼊脚A0、A1、A2可悬空或连接到VSS 。

WP :写保护。

如果WP 管脚连接到Vcc ,所有的内容都被写保护,只能读。

当WP 管脚连接到Vss 或悬空,允许器件进⾏正常的读/写操作。

VSS :电源地(GND)。

VCC :电源电压(5V)。

AT24C02⽀持I2C 总线数据传送协议,I2C 总线协议规定:任何将数据传送到总线的器件作为发送器,任何从总线接收数据的器件为接收器。

数据传送是由产⽣串⾏时钟和所有起始停⽌信号的主器件控制的,主器件和从器件都可以作为发送器或接收器,但由主器件控制传送数据发送或接收的模式。

I2C 总线协议定义如下:●只有在总线空闲时才允许启动数据传送。

●在数据传送过程中,当时钟线为⾼电平时,数据线必须保持稳定状态,不允许有跳变,时钟线为⾼电平时,数据线的任何电平变化将被看作总线的起始或停⽌信号。

图3-9 AT24C02引脚图图3-10 AT24C02起始/停⽌时序如图3-10所⽰,时钟线保持⾼电平期间,数据线电平从⾼到低的跳变作为I2C总线的起始信号。