北大数字集成电路课件--6_verilog的数据类型

- 格式:ppt

- 大小:182.50 KB

- 文档页数:23

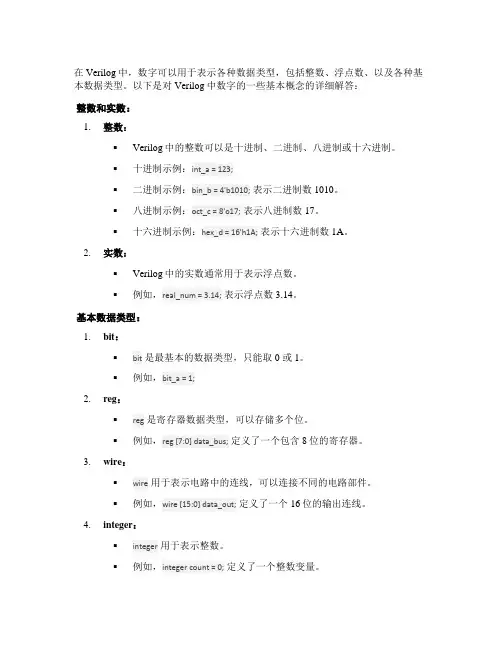

在Verilog中,数字可以用于表示各种数据类型,包括整数、浮点数、以及各种基本数据类型。

以下是对Verilog中数字的一些基本概念的详细解答:整数和实数:1.整数:▪Verilog中的整数可以是十进制、二进制、八进制或十六进制。

▪十进制示例:int_a = 123;▪二进制示例:bin_b = 4'b1010;表示二进制数 1010。

▪八进制示例:oct_c = 8'o17;表示八进制数 17。

▪十六进制示例:hex_d = 16'h1A;表示十六进制数 1A。

2.实数:▪Verilog中的实数通常用于表示浮点数。

▪例如,real_num = 3.14;表示浮点数 3.14。

基本数据类型:1.bit:▪bit是最基本的数据类型,只能取 0 或 1。

▪例如,bit_a = 1;2.reg:▪reg是寄存器数据类型,可以存储多个位。

▪例如,reg [7:0] data_bus;定义了一个包含8位的寄存器。

3.wire:▪wire用于表示电路中的连线,可以连接不同的电路部件。

▪例如,wire [15:0] data_out;定义了一个16位的输出连线。

4.integer:▪integer用于表示整数。

▪例如,integer count = 0;定义了一个整数变量。

5.real:▪real用于表示实数。

▪例如,real voltage = 5.0;定义了一个实数变量。

参数和常量:1.parameter:▪parameter关键字用于定义参数,通常用于指定模块的宽度或大小。

▪例如,parameter WIDTH = 8;定义了一个参数 WIDTH。

2.`define:▪使用define可以定义常量。

▪例如,define MAX_COUNT 100定义了一个最大计数常量。

这些是Verilog中处理数值的基本概念。

根据设计的需求,你可以选择适当的数据类型和表示方式。

请注意,Verilog中的数值表示可以有多种形式,具体的选择取决于设计需求。

6-3Vrilog HDL语言简介硬件描述语言HDL是EDA技术中的重要组成部分,常用的硬件描述语言有Verilog HDL 、VHDL、System Verilog、System C、ABEL HDL和AHDL等,而Verilog HDL和VHDL是当前最流行的并成为IEEE标准的硬件描述语言。

3.1 HDL简介VHDL是超高速集成电路硬件描述语言(Very-High-Speed Integrated Circuit Hardware Description Language)的缩写。

VHDL作为IEEE标准的硬件描述语言和EDA的重要组成部分,经过十几年的发展、应用和完善,以其强大的系统描述能力、规范的程序设计结构、灵活的语言表达风格和多层次的仿真测试手段,在电子设计领域受到了普遍的认同和广泛的接受,成为现代EDA领域的重要的硬件设计语言。

HDL的特点1、HDL具有强大的功能,覆盖面广,描述能力强。

HDL支持门级电路的描述,也支持寄存器传输级电路的描述,还支持以行为算法描述为对象的电路的描述。

2、HDL有良好的可读性。

它可以被计算机接受,也容易被读者理解。

用HDL书写的源文件,既是程序又是文档,既是工程技术人员之间交换信息的文件,又可作为合同签约者之间的文件。

3、HDL具有良好的可移植性。

作为一种已被IEEE承认的工业标准,HDL事实上已成为通用的硬件描述语言,可以在各种不同的设计环境和系统平台中使用。

4、使用HDL可以延长设计的生命周期。

用HDL描述的硬件电路与工艺无关,不会因工艺而过时。

与工艺有关的参数可以通过HDL提供的属性加以描述,工艺改变时,只需要修改相应程序中属性参数即可。

5、HDL支持对大规模设计的分解和已有设计的再利用。

HDL可以描述复杂的电路系统,支持对大规模设计的分解,由多人、多项目组来共同承担和完成。

标准化的规则和风格,为设计的再利用提供了有力的支持。

6、HDL有利于保护知识产权。

verilog 数据类型Verilog数据类型Verilog是一种硬件描述语言,用于描述数字电路和系统。

在Verilog中,数据类型是非常重要的概念,因为它们定义了变量和信号的类型和范围。

本文将介绍Verilog中的数据类型。

1. 整数类型整数类型是Verilog中最基本的数据类型之一。

它们用于表示整数值,可以是有符号或无符号的。

在Verilog中,整数类型有四种:bit、byte、integer和longint。

bit类型是最基本的整数类型,它只有一个位,可以是0或1。

byte类型是8位整数类型,可以表示0到255之间的值。

integer 类型是32位整数类型,可以表示-2147483648到2147483647之间的值。

longint类型是64位整数类型,可以表示-9223372036854775808到9223372036854775807之间的值。

2. 实数类型实数类型用于表示实数值,可以是单精度或双精度的。

在Verilog 中,实数类型有两种:real和realtime。

real类型是单精度实数类型,可以表示大约6到7位有效数字。

realtime类型是双精度实数类型,可以表示大约15到16位有效数字。

3. 向量类型向量类型用于表示多位信号或变量。

在Verilog中,向量类型有两种:wire和reg。

wire类型用于表示多位信号,可以是有符号或无符号的。

它们通常用于连接模块之间的信号。

reg类型用于表示多位变量,可以是有符号或无符号的。

它们通常用于存储状态或计数器值。

4. 枚举类型枚举类型用于表示一组命名的常量。

在Verilog中,枚举类型使用parameter关键字定义。

例如:parameter [RED, GREEN, BLUE] = 3'b001, 3'b010, 3'b100;这将定义一个枚举类型,其中RED、GREEN和BLUE是常量名称,它们分别对应于3位二进制值001、010和100。

Verilog语言是一种硬件描述语言(HDL),被广泛应用于数字集成电路(IC)设计领域。

在Verilog语言中,默认的数值格式对于数字的表示和处理起着重要的作用。

在本文中,我们将就Verilog语言默认的数值格式展开讨论,并探究其在数字电路设计中的应用。

一、二进制表示在Verilog语言中,默认的数值格式是二进制。

二进制是一种基于2的数字系统,其表示方式是通过0和1两个数字进行组合。

在Verilog 语言中,可以通过使用'b'或'B'前缀来表示二进制数值。

'b1010'表示10,其中'b'表示这是一个二进制数值,后面的数字则是该二进制数值对应的十进制数。

这种表示方式在数字逻辑电路设计中非常常见,尤其是在表示寄存器、状态机等时使用频繁。

二、十进制表示除了二进制表示外,在Verilog语言中,默认的数值格式也支持十进制。

十进制是一种基于10的数字系统,其表示方式是通过0-9十个数字进行组合。

在Verilog语言中,可以直接使用数字表示十进制数值。

'10'表示10,这是一个十进制数值。

在一些需要直观表示数量的场景中,使用十进制数值会更为方便。

三、八进制和十六进制表示除了二进制和十进制表示外,在Verilog语言中,默认的数值格式还支持八进制和十六进制表示。

八进制是一种基于8的数字系统,其表示方式是通过0-7这8个数字进行组合。

在Verilog语言中,可以通过使用'o'或'O'前缀来表示八进制数值。

'o17'表示15,其中'o'表示这是一个八进制数值。

十六进制是一种基于16的数字系统,其表示方式是通过0-9以及A-F这16个字符进行组合。

在Verilog语言中,可以通过使用'h'或'H'前缀来表示十六进制数值。

'h1F'表示31,其中'h'表示这是一个十六进制数值。

verilog 数据类型Verilog是一种硬件描述语言,它可以用于设计硬件电路。

在Verilog中,数据类型是非常重要的一个概念,它用于描述硬件电路中的不同类型的数据。

在本文中,我们将探讨Verilog中的不同数据类型。

Verilog数据类型可以分为以下几类:1. 预定义数据类型2. 组合数据类型3. 用户定义数据类型预定义数据类型Verilog中的预定义数据类型通常也被称为基本数据类型,它们包括:1. 整型(integer):整型数据类型是一种带符号的整数类型,它可以表示-2^31到2^31-1之间的整数。

整型数据类型可以用于描述数字数据。

2. 实型(real):实型数据类型是一种带小数点的数值类型,它可以用于表示实数。

在Verilog中,实型数据类型使用IEEE 754格式编码。

实型数据类型通常用于描述模拟信号。

3. 位型(bit):位型数据类型是一种只具有两种值(0或1)的数据类型。

位型数据类型可以用于描述数字数据或逻辑值。

4. 字符型(byte):字符型数据类型是一种ASCII字符集中的字符,它可以表示所有字母、数字、常见标点符号和其他特殊字符。

组合数据类型组合数据类型是由基本数据类型或其他组合数据类型组成的数据类型。

在Verilog中,组合数据类型包括:1. 字符串型(string):字符串数据类型是一个不定长的字符数组,它可以用于描述字符串数据。

2. 数组型(array):数组数据类型是一组相同类型的数据元素的集合,它可以用于描述序列数据,例如存储器存储的数据。

3. 结构体(struct):结构体是由不同类型的数据成员组成的数据类型。

结构体数据类型通常用于描述复杂的硬件电路部件,例如CPU。

4. 无符号型(unsigned):无符号型数据类型是一种不带符号的整数类型。

它可以表示0到2^32-1之间的整数。

无符号型数据类型通常用于描述数字数据。

用户定义数据类型用户定义数据类型是一种自定义的数据类型,可以根据用户的需要定义数据类型。

verilog数据类型Verilog数据类型是用于Verilog硬件描述语言(HDL)的基本数据类型。

它包括内部变量,常量,状态变量,模块参数,端口和信号等。

Verilog HDL有两种不同类型的数据类型:系统类型和用户定义类型。

下面将简要介绍Verilog中的几种常用的数据类型。

1. 整数(integer):整数是最常用的Verilog数据类型,可以表示0到2^32-1之间的整数值,并且可以作为在硬件中使用的变量。

2. 无符号整数(unsigned):无符号整数是一种特殊的整数类型,可以表示0到2^64-1之间的无符号整数。

3. 向量(vector):向量是Verilog中最常用的数据类型,意味着可以定义一个由多个位构成的值。

通常情况下,它用来表示输入或输出信号。

4. 结构体(struct):结构体是Verilog中另一种非常有用的数据类型,它可以用来定义一个由多个不同类型的元素构成的数据结构。

5.枚举(enum):枚举类型是一种特殊的字符串类型,它可以表示一组固定的值,如颜色、星期等。

6. 字符串(string):字符串是Verilog中的一种特殊数据类型,可以表示一串文本字符,如字符串常量或者从文件中读取的字符串。

7. 引用(ref):引用是Verilog中的一种特殊数据类型,它可以用来引用另一个数据类型,如整数、向量等。

8. 句柄(handle):句柄是Verilog中的一种特殊数据类型,它可以用来引用一组变量,模块参数,端口等。

9. 任意精度数字(arbitrary precision number):任意精度数字是Verilog中的一种特殊数据类型,它可以表示任意精度的数字,如浮点数和双精度数字等。

10. 类型定义(typedef):类型定义是Verilog中的一种特殊数据类型,它可以用来定义一组用户定义的类型,如自定义的结构体、枚举等。

Verilog HDL中的数据类型很多,它们的功能和用法也十分多样。

VerilogVerilog HDL 有下列四种基本的值:1) 0:逻辑0 或者“假”状态;2) 1:逻辑1 或者“真”状态;3) x (X):未知状态,对大小写不敏感;4) z (Z):高阻状态,对大小写不敏感。

注意这四种值的解释都内置于语言中。

如一个为z 的值总是意味着高阻抗,一个为0 的值通常是指逻辑0。

在门的输入或者一个表达式中的为“z”的值通常解释成“x”。

此外,x 值和z 值都是不分大小写的,也就是说,值0x1z 与值0X1Z 相同。

Verilog HDL 中的常量是由以上这四类基本值组成的。

3.5.1网络和变量在Verilog HDL 中,根据赋值和对值的保持方式不同,可将数据类型主要分为两大类:网络(net)型和变量(Variable)型。

这两类数据也代表了不同的硬件结构。

3.5.1.1net(网络)型net 表示器件之间的物理连接,需要门和模块的驱动。

网络数据类型是指输出始终根据输入的变化而更新其值的变量,它普通指的是硬件电路中的各种物理连接。

例如:网络型变量L 的值由与门的驱动信号a 和b 所决定,即L=a&b 。

a、b 的值发生变化,L 的值会即将跟着变化。

没有声明的net 的默认类型为1 位 (标量) wire 类型。

Verilog HDL 禁止对已经声明过的网络、变量或者参数再次声明。

下面给出net 声明的语法格式:<net_type> [range] [delay] <net_name>[,net_name];其中:net_type:表示网络型数据数据的类型。

range:用来指定数据为标量或者矢量。

若该项默认,表示数据类型为1 位的标量;反之,由该项指定数据的矢量形式。

delay:指定仿真延迟时间。

net_name:net 名称,一次可定义多个net ,用逗号分开。

【例3.15】网络的声明wand w; // 一个标量wand 类型nettri [15: 0] bus; // 16 位三态总线wire [0: 31] w1, w2; // 两个32 位wire,MSB 为bit0net 类型包括多种不同的种类,表3.2 给出了这些常用的不同类型的功能及其可综合性。