基于FPGA的设计题目

- 格式:doc

- 大小:562.54 KB

- 文档页数:8

![基于FPGA的LCD设计__[文档在线提供]](https://uimg.taocdn.com/d2b4dcc3d5bbfd0a79567377.webp)

本科毕业设计(2009 届)题目基于FPGA的LCD控制器设计学院专业班级学号学生姓名指导教师完成日期年月日基于FPGA的LCD控制器设计基于FPGA的LCD控制器设计【摘要】本课题主要任务是设计基于FPGA的LCD控制器,兼顾好程序的易用性,以方便之后模块的移植和应用。

本课题的设计采用了带ST7920驱动的12864-12液晶模块,并使用Altera公司的cycloneII系列的EP2C5T144C8来作为核心的控制器。

控制器部分采用VHDL语言编写,主体程序采用了状态机作为主要控制方式。

该控制器分为字符显示模块和图片显示模块两个主要部分。

在字符的显示功能上采用显示控制模块与字符调用RAM相结合的方式,使使用者能方便地调用液晶自带的字库来显示字符;而图片显示模块则通过特殊的处理算法解决了图像显示缓冲区X地址不断移位以及上下半屏分开的问题,通过读取图片ROM来显示图片。

最后实现使用FPGA在LCD上的任意位置显示任意的16*16像素的中文字符以及16*8的英文字符,另外要能根据输入数据的变化同步变化LCD上显示的内容。

同时要能将储存模块中的图片数据正常地显示在LCD上。

该课题的研究将有助于采用FPGA的系列产品的开发,特别是需要用到LCD的产品的开发。

同时可以大大缩短FPGA的开发时间。

另外,由于模块的易用性,也将使得更多的采用FPGA的产品之上出现LCD,增加人机之间的交互性,为行业和我们的生活带来新的变化。

【关键词】12864-12,VHDL,LCD,FPGA,状态机- 1 -基于FPGA的LCD控制器设计Design of the LCD Control Module Based on FPGA【Abstract】In this project, the main object is to design a LCD controller based on FPGA, and at the same time emphasize on the convenience for the later application and migration. In this project, I used 12864-12 LCD module with the ST7920 driver. For the controller part, I chose the Cyclone II serial FPGA, the EP2C5T144C8, which developed by the Altera Cooperation. The program of the controller is written by VHDL language, and the main body of the program used state machine as the primary control method. In this LCD controller, there are two major parts, which are the character display module and the picture display module. The character display module put the Character Calling Ram and the display control module together to enable the user to call the embedded character library easily to display the information he/she needed. For the picture display module, the module, through specific algorithm, solved the problems that the x address of the picture display buffer kept stepping forward after every 16 times and the display screen are divided into 2 section by the buffer. And this module, by reading a picture ram, displayed picture which was put earlier.In this project, I finally realized the following function. The first one is to display any 16*16 pixels Chinese character and 16*8 pixels English character on any position of the display screen. The second one is the display information will instantaneously update as the input data changes. The last function is that any given picture data can be displayed properly on the LCD screen.The research of this project will contribute to the developing process of those products which use FPGAs, especially those products also use LCD. And at the same time, it can reduce dramatically on the developing time. In addition, for the convenience of this controller, more and more FPGA based products will come out with LCD screen. This change will enhance the interaction between human and the machine, and bring innovation to the industry and our lives.【Key Words】12864-12,VHDL,LCD,FPGA,State Machine.- 2 -基于FPGA的LCD控制器设计目录第1章绪论 (5)1.1 选题的背景与意义 (5)1.2 LCD的控制,应用和市场的发展现状 (5)1.3 课题的主要研究内容和重点、难点 (7)1.3.1 本课题主要研究内容和重点 (7)1.3.2 本课题的主要难点: (7)1.4 课题研究预期目标 (7)1.4.1 课题研究预期理论目标 (7)1.4.2 课题研究预期技术目标 (8)第2章现代LCD技术 (9)2.1 现代LCD技术简介 (9)2.2 STN-LCD技术的显示原理 (10)2.3 动态STN-LCD驱动方法 (11)第3章现代FPGA技术 (14)3.1 FPGA的发展历程 (14)3.2 FPGA的基本原理 (15)3.2.1 查找表的基本原理 (15)3.2.2 基于乘积项的FPGA的逻辑实现原理 (15)3.3 FPGA的设计方法 (16)3.4 VHDL硬件描述语言 (16)3.5 Quartus II简介 (17)3.6 核心控制芯片选择 (18)3.7 FPGA的设计流程 (19)第4章总体系统设计及资源 (22)4.1 系统设计要求 (22)4.2 系统设计总体框图 (22)4.3 系统开发选用资源 (22)4.3.1 液晶模块选用 (22)4.3.2 FPGA的选择 (28)3基于FPGA的LCD控制器设计4.4 硬件设计 (30)第5章系统各部分模块的设计 (31)5.1 初始化模块设计 (31)5.1.1 LCD模块初始化原理 (31)5.1.2 时钟模块的设计 (32)5.1.3 字符显示前初始化模块的设计 (33)5.1.4 图片显示前初始化模块的设计 (36)5.2 写入数据模块的设计 (37)5.2.1 英文字符部分的数据模块 (37)5.2.2 中文字符部分的数据模块 (40)5.2.3 图片部分的数据模块 (40)5.3 显示控制模块的设计 (40)5.3.1 字符显示控制模块的设计 (40)5.3.2 动态数据的显示控制 (42)5.3.3 图像数据的显示控制 (43)5.4 字符显示及图片显示整体模块 (49)5.5 本章小结 (50)第6章模块测试与使用方法 (51)6.1 模块的使用方法 (51)6.1.1 字符显示模块的使用 (51)6.1.2 图片显示模块的使用 (52)6.2 测试内容 (53)6.2.1 字符显示部分的测试 (53)6.2.2图片显示部分的测试 (54)6.3 测试结果 (57)6.3.1 字符显示 (57)6.3.2 图片显示 (58)6.4小结 (60)结束语 (61)参考文献 (63)致谢 (62)4基于FPGA的LCD控制器设计第1章绪论1.1 选题的背景与意义液晶,是一种在一定温度范围内呈现既不同于固态、液态,又不同于气态的特殊物质态,它既具有各向异性的晶体所特有的双折射性,又具有液体的流动性。

天津工业大学毕业设计(论文)基于FPGA的LCD显示控制系统的设计姓名:马震院(系)别: 信息与通信工程学院专业: 电子信息工程班级:电子061指导教师:周勇职称:讲师2010年 6 月13 日天津工业大学毕业设计(论文)任务书院长教研室主任指导教师毕业设计(论文)开题报告表天津工业大学毕业设计(论文)进度检查记录天津工业大学本科毕业设计(论文)评阅表摘要本课题主要任务是设计基于FPGA的LCD控制器,兼顾好程序的易用性,以方便之后模块的移植和应用。

本课题的设计采用了带ST7920驱动的12864-12的液晶模块,并使用Xilinx公司的spartanII系列的XC2STQ144来作为核心的控制器。

控制器部分采用VHDL语言编写,主体程序采用了状态机作为主要控制方式。

ST7920是一种内置128x64-12汉字图形点阵地液晶显示控制模块,用于显示汉字和模型。

最后实现使用FPGA在LCD上的任意位置显示任意的16*16像素的中文字符以及16*8的英文字符,另外要能根据输入数据的变化同步变化LCD上显示的内容.同时要能将储存模块中的图片数据正常地显示在LCD上。

该课题的研究将有助于采用FPGA的系列产品的开发,特别是需要用到LCD 的产品的开发。

同时可以大大缩短FPGA的开发时间。

另外,由于模块的易用性,也将使得更多的采用FPGA的产品之上出现LCD,增加人机之间的交互性,为行业和我们的生活带来新的变化。

关键词:ST7920;12864—12 ;VHDL;FPGA ;LCDABSTRACTIn this project, the main object is to design a LCD controller based on FPGA,and at the same time emphasize on the convenience for the later application and migration. In this project, This topic is designed with a belt—driven 12864—12 ST7920 LCD module, and use the Xilinx's spartanII series XC2STQ144 as the core of the controller。

课题一定时闹钟设计要求:设计一个具有系统时间设置和带闹钟功能的24小时计时器中的应用。

电子钟要求如下:(1)计时功能:4位LED数字时钟对当前时间的小时和分钟进行显示,显示的最长时间为23小时59分。

(2)设置并显示新的闹钟时间:用户先按“set”键,再用数字键“0”~“9”输入时间,然后按“alarm”键确认。

在正常计时显示状态下,用户直接按下“alarm”键,则已设置的闹钟时间显示在显示屏上。

(3)设置新的计时器时间:用户先按“set”键,再用数字键“0”-“9”输入新的时间,然后按“time”键确认。

在输入过程中;输入的数字在显示屏上从右到左依次显示。

例如,用户要设置新的时间 12:00,则按顺序输入“l”,“2”,“0”,“0”键,与之对应,显示屏上依次显示的信息为:“1”,“12”;“120”,“1200”。

如果用户在输入任意几个数字后较长时间内,例如5秒,没有按任何键,则计时器恢复到正常的计时显示状态。

(4)闹钟功能:如果当前时间与设置的闹钟时间相同,则扬声器发出蜂鸣声;教学提示:根据上述设计的功能,可以进行功能分割成几大功能模块。

例如,系统可能包含按键去抖模块,用于按键编码的编码器,用于时钟计数的计数器,用于保存闹钟时间的寄存器,用于显示的七段数码显示电路等。

但其中最主要部分的是控制各个部分协同工作的电路,即控制器,以按照设计功能产生适当的时序控制。

课题二波形发生器设计要求:(1)设计并实现一个可产生正弦波、三角波波形发生器。

(2)其工作频率为50MHz,可产生1MHz、2MHz、3MHz、4MHz、5MHz的正弦波、三角波。

所产生波形的幅度、相位均可调整,输出数据的字长为12 bit。

若波形的频率为n MHz,则相位的最小调幅为2π*n/60。

(2)要求进行4级幅度调整,即ROM中存储的数据字长为10 bit,ROM输出的数据分别乘以001、100、011、和100。

教学提示:根据题目所给出的要求,可以计算出设计波形发生器时所需的各项参数。

课程设计任务书学生姓名:专业班级:指导教师:工作单位:信息工程学院题目: 电子琴的设计课程设计目的:《FPGA原理与应用》课程设计的目的是为了让学生熟悉基于VHDL语言进行FPGA开发的全流程,并且利用FPGA设计进行专业课程理论知识的再现,让学生体会EDA技术的强大功能,为今后使用FPGA进行电子设计奠定基础。

课程设计内容和要求设计内容:(1)设计一个八音电子琴。

(2)由键盘输入控制音响,同时可自动演奏乐曲。

(3)用户可以将自己编制的乐曲存入电子琴,演奏时可选择键盘输入乐曲或者已存入的乐曲。

要求每个学生单独完成课程设计内容,并写出课程设计说明书、说明书应该包括所涉及到的理论部分和充足的实验结果,给出程序清单,最后通过课程设计答辩。

时间安排:指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (1)Abstract (2)1设计意义和要求 (3)1.1设计意义 (3)1.2功能要求 (3)2方案论证及原理分析 (4)2.1实现方案比较 (4)2.2乐曲实现原理 (4)2.3系统组成及工作原理 (6)3系统模块设计 (8)3.1顶层模块的设计 (8)3.2乐曲自动演奏模块的设计 (8)3.3音阶发生器模块的设计 (9)3.4数控分频器模块的设计 (9)4程序设计 (11)4.1VHDL设计语言和ISE环境简介 (11)4.2顶层模块的程序设计 (12)4.3乐曲自动演奏模块的程序设计 (13)4.4音阶发生器模块的程序设计 (13)4.5数控分频模块的程序设计 (14)5设计的仿真与实现 (15)5.1乐曲自动演奏模块仿真 (15)5.2音调发生模块仿真 (18)5.3数控分频模块仿真 (19)5.4电子琴系统的仿真 (20)5.5设计的实现 (22)5.6查看RTL视图 (23)5.7查看综合报告 (25)6心得体会 (31)7参考文献 (32)8附录 (33)摘要随着基于FPGA的EDA技术的发展和应用领域的扩大与深入,EDA技术在电子信息、通信、自动控制用计算机等领域的重要性日益突出。

基于FPGA的设计题目1.花样彩灯控制器的设计设计要求:假设输入脉冲为3MHz,控制16只LED发光二极管每隔1s或2s 显示一种花样。

要求显示的花样如下:闪烁2次从LED(0)移位点亮到LED(15)一次全部点亮一次从LED(15)开始逐个熄灭至LED(0)1次闪烁2次。

如果按下清零键时,16只LED均熄灭一次,然后再重新按规律显示。

如果没有按下快/慢选择控制键时,16只LED 发光二极管是以每隔1s进行花样显示,否则按下快/慢键选择控制键时,16只LED发光二极管是以每隔2s进行花样显示。

2.利用FPGA实现一个简单的DDS正弦波发生器(DDS:数字显示示波器)可分解为三个部分来设计:时钟产生模块;地址产生模块;ROM 查找表模块。

实现思路:①首先,由外部晶振引入40MHz的时钟到FPGA内部,进入时钟产生模块,对时钟进行处理并3倍频程后,得到一个稳定精确的120MHz的系统时钟;②然后,地址产生模块在系统时钟的激励下,将频率控制字与累加寄存器输出的数据进行累加,然后把累加的结果作为地址输出给ROM查找表地址;③最后,ROM查找表模块在每个系统时钟的上升沿,按照地址来读取ROM 查找表中的相应的波形采样点数据并输出,该数就是最终的DDS信号。

3.多功能信号发生器的设计设计要求:设计一个多功能信号发生器,能够以稳定的频率产生锯齿波、增减锯齿波、三角波、阶梯波、正弦波和方波等六种信号。

系统有3个波形选择开关和一个复位开关,通过波形选择开关可以选择以上各种不同种类的输出波形;按下复位开关时,系统将复位。

设计实现:由于FPGA只能直接输出数字信号,而多功能信号发生器输出的各种波形均为模拟信号,因此设计信号发生器时,需将FPGA输出的信号通过D/A转换电路将数字信号转换成模拟信号。

多功能信号发生器可由信号产生电路、波形选择电路和D/A转换电路构成。

如下图所示:时钟信号波形输出信号产生电波形选择电路D/A转换电路选择信号4.数字跑表的设计设计要求:设计一个数字跑表,该跑表具有复位、暂停、秒表计时等功能。

fpga的课程设计题目一、教学目标本课程的教学目标是使学生掌握FPGA(现场可编程门阵列)的基本原理、设计和应用。

具体包括:1.知识目标:学生能够理解FPGA的基本结构、工作原理和编程方法;了解FPGA在数字电路设计中的应用和优势。

2.技能目标:学生能够使用FPGA开发工具进行简单的数字电路设计,包括逻辑分析、编码、仿真和下载;能够阅读和理解FPGA相关的技术文档。

3.情感态度价值观目标:培养学生对新技术的敏感性和好奇心,提高学生解决实际问题的能力,培养学生的创新精神和团队合作意识。

二、教学内容教学内容主要包括FPGA的基本原理、FPGA的设计方法和应用实例。

具体安排如下:1.FPGA的基本原理:介绍FPGA的结构、工作原理和编程方法;2.FPGA的设计方法:讲解FPGA的设计流程,包括逻辑分析、编码、仿真和下载;3.FPGA的应用实例:分析FPGA在数字电路设计中的应用和优势,举例讲解FPGA的实际应用。

三、教学方法本课程采用讲授法、讨论法、案例分析法和实验法等多种教学方法,以激发学生的学习兴趣和主动性。

1.讲授法:讲解FPGA的基本原理和设计方法;2.讨论法:学生讨论FPGA的应用实例和实际问题;3.案例分析法:分析FPGA的实际应用案例,帮助学生理解FPGA的设计和应用;4.实验法:安排实验课程,让学生动手操作FPGA开发工具,进行实际的数字电路设计。

四、教学资源教学资源包括教材、参考书、多媒体资料和实验设备等。

具体如下:1.教材:选用权威、实用的教材,为学生提供系统的FPGA知识;2.参考书:提供相关的参考书籍,丰富学生的知识体系;3.多媒体资料:制作精美的PPT和教学视频,增强课堂教学的趣味性和生动性;4.实验设备:提供FPGA开发板和实验器材,让学生能够动手实践,提高实际操作能力。

五、教学评估本课程的评估方式包括平时表现、作业和考试等,以全面客观地反映学生的学习成果。

1.平时表现:评估学生在课堂上的参与度、提问和讨论表现,以考察学生的学习态度和理解能力;2.作业:布置适量的作业,评估学生的完成情况和理解程度;3.考试:进行期中和期末考试,评估学生的知识掌握和应用能力。

广西工学院毕业设计(论文)开题报告届)题目名称:A bi-directi on DC-DCC onv erter desi gn based onthe FPGA基于FPGA勺双向DC-D(变换器的设计系别电子信息与控制工程系专业自动化班级学号姓名指导教师_______________________________年月日2)研究重点(1)升压电路、降压电路中开关功率管软开关的实现;(2)基于FPGA的控制电路的设计;(3)控制电路各个模块的编译、仿真。

3)研究难点(1)降压控制模块中移相控制模块的设计,如何通过设计一个变量改变超前桥臂和滞后桥臂之间的移相角;(2)数字PWM控制模块的设计、编译、仿真;(3)如何利用FPGA实现数字PID调节。

4)创新点由于FPGA具有开发周期短、灵活性高、成本低、模块可重复利用率高等特点,本论文采用FPGA进行控制电路的设计,通过设计某种控制策略使得移相PWM-ZVZCS的桥式功率变换电路和新型软开关推挽式Boost功率变换电路组成一个双向DC-DC变换器,满足车载电源系统的设计要求。

5)拟撰写论文的结构摘要第一章绪论第二章主电路拓扑结构及控制方式选择第三章主电路工作原理学位论文,2006,11.[7] 方如举.一种新型双向DC-DC变换器的研究[D].合肥工业大学硕士学位论文,2006,4.[8] 张占松,蔡宣三.开关电源的原理与设计[M] •北京:电子工业出版社,1999.[9] 曲学基,王增幅,曲敬铠.新编高频开关稳压电源[M] •北京:电子工业出版社,2005.[10] 常栋梁.基于FPGA的数字PWM控制器的研制[D].西安科技大学硕士学位论文,2008,4.[11] 潘松,黄继业.EDA技术使用教程[M].北京:科学出版社,2008.[12] 清源计算机工作室.Protel 99 SE原理图与PCB及仿真[M].北京:机械工业出版社,2008.[13] Ehsan Adib *,Hosein Farzanehfard.Softswitching bi-directional DC-DC converter for ultracapacitor-batteries interface[J]. Energy Conversion and Managemen,2009 (50),2879-2884.六、指导教师意见指导教师签名:年月日七、系审核意见负责人签名(系公章):年月日。

基于FPGA的自动打铃器的设计目录第一章绪论 (4)1.1选题目的 (4)1.2 FPGA的发展历程 (4)1.2.1 FPGA的优点 (5)1.3器件及工具介绍 (5)1.3.1 QuartusⅡ设计步骤 (5)第二章系统方案设计 (5)2.1设计方案分析与选择 (5)2.2自动打铃器总体构成 (6)2.3分频模块设计 (7)2.4消抖模块设计 (8)2.5时钟模块设计 (8)2.5.1秒计数模块 (9)2.5.2分计数模块 (9)2.5.3时计数模块 (10)2.5.4调时模块 (11)2.6闹钟模块设计 (12)2.6.1定时模块 (12)2.6.2比较模块 (13)2.7打铃模块设计 (15)2.8报警模块设计 (17)2.8.1报警时长设定模块 (17)2.8.2蜂鸣器发声模块 (17)2.9显示模块设计 (18)2.9.1时间切换模块 (18)2.9.2动态扫描模块 (20)2.10按键电路设计 (22)第三章实验结果分析 (22)3.1测试过程 (22)3.2结果分析 (23)参考文献 (25)附录 (26)摘要自动打铃器为学校上下课时间的准确控制提供了很大的便利,并且在工厂、办公室等场合也起到了提醒人们时间的作用,因此打铃器的设计有一定的实用意义。

本设计的学校打铃器采用基于现场可编程门阵列(FPGA)的方法,底层模块采用硬件描述语言(HDL)设计,不仅能对时、分、秒正常计时和显示,而且还可进行闹铃时间的设定,上下课时间报警,报警时间1-15秒设置。

系统主芯片采用美国Altera 公司的EP3C40F484I7器件,由时钟模块、控制模块、闹钟模块、定时模块、数据译码模块、显示以及报时等模块组成,由按键进行时钟的校时、清零、启停等。

本文在介绍FPGA器件的基础上,着重阐述了如何使用FPGA器件进行系统的开发,以及如何实现学校打铃系统。

通过仿真验证及实际测试,打铃器具有正常计时、定时报警、报警时长设定等功能,可为日常作息提供准确、便捷的提醒。

武汉工业学院毕业设计(论文)设计(论文)题目:基于FPGA的信号发生器设计姓名学号院系电气与电子工程学院专业电子信息科学与技术指导教师目录摘要 ...................................................................................................................................... i ii Abstract (iv)前言 (1)1绪论 (3)1.1 FPGA简介 (3)1.2 modelsim简介 (5)1.3 DDS基本原理介绍 (6)2设计方案 (8)2.1 总体设计方案 (8)2.2方案论证 (8)2.2.1方案一 (8)2.2.2方案二 (9)2.2.3方案三 (9)2.3方案确定 (9)3 硬件电路设计 (11)3.1硬件设计注意事项 (11)3.2 DA电路 (11)3.3滤波电路 (12)3.4硬件电路实现 (13)4软件设计 (14)4.1波形产生模块 (14)4.1.1正弦波 (14)4.1.2方波 (15)4.1.3 三角波 (15)4.2频率控制模块 (16)4.3相位累加模块 (17)4.4选择波形模块 (17)4.5幅度控制模块 (18)4.6软件设计总成 (19)5 调试 (20)5.1设计及仿真调试使用设备 (20)5.2 调试方法 (20)5.2.1 硬件调试 (20)5.2.2 软件调试 (20)5.2.3 综合调试 (20)5.3 调试结果 (21)5.3.1 软件仿真结果及分析 (21)5.3.2 综合调试结果 (24)总结 (25)致谢辞 (26)参考文献 (27)附件1 ROM生成源程序 (28)附件2 40位流水线加法器程序 (30)摘要信号发生器是数字设备运行工作中必不可少的一部分,没有良好的信号源,最终就会导致系统不能够正常工作,更不必谈什么实现其它功能了。

1、彩灯控制器设计内容及要求:设计一个彩灯控制器,具体设计要求如下:(1)要有多种花型变化(至少设计5种),led 至少16路(2)多种花型可以自动变化(3)彩灯变换的快慢节拍可以选择(4)具有清零开关(5)完成全部流程:设计规范文档、模块设计、代码输入、仿真、下载验证等,最后就课程设计本身提交一篇课程设计报告。

2、数字秒表设计内容及要求:设计一用于体育比赛的数字秒表,具体设计要求如下:(1)6位数码管显示,其中两位显示min ,四位显示see ,显示分辨率为0.01 s 。

(2)秒表的最大计时值为59min59.99see 。

(3)设置秒表的复位/启动键,按一下该键启动计时,再按即清0。

依此循环。

(4)设置秒表的暂行/继续键。

启动后按一下暂行,再按继续。

依此循环。

(5)完成全部流程:设计规范文档、模块设计、代码输入、仿真、下载验证等,最后就课程设计本身提交一篇课程设计报告。

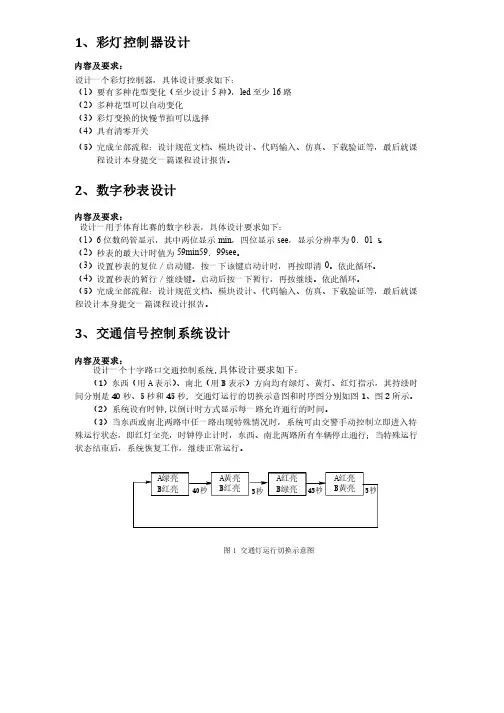

3、交通信号控制系统设计内容及要求:设计一个十字路口交通控制系统设计一个十字路口交通控制系统,,具体设计要求如下:(1)东西(用A 表示)、南北(用B 表示)方向均有绿灯、黄灯、红灯指示,其持续时间分别是40秒、秒、55秒和45秒, , 交通灯运行的切换示意图和时序图分别如图交通灯运行的切换示意图和时序图分别如图1、图2所示。

(2)系统设有时钟统设有时钟,,以倒计时方式显示每一路允许通行的时间。

(3)当东西或南北两路中任一路出现特殊情况时,系统可由交警手动控制立即进入特殊运行状态,即红灯全亮,时钟停止计时,东西、南北两路所有车辆停止通行;当特殊运行状态结束后,系统恢复工作,继续正常运行。

A红亮B黄亮A绿亮B红亮A黄亮B红亮A红亮B绿亮5秒40秒45秒5秒图1 1 交通灯运行切换示意图交通灯运行切换示意图B红CPA绿A黄A红B黄B绿45 S5S 5S 40 S 90 S1S图2 2 交通灯时序图交通灯时序图(4)完成全部流程:设计规范文档、模块设计、代码输入、仿真、下载验证等,最后就课程设计本身提交一篇课程设计报告。

- - -..毕业设计〔论文〕开题报告〔含文献综述、外文翻译〕题目基于FPGA 的步进电机控制器设计姓名学号专业班级所在学院指导教师〔职称〕二○一一年六月十五日-毕业设计〔论文〕开题报告〔包括选题的意义、可行性分析、研究的内容、研究方法、拟解决的关键问题、预期结果、研究进度方案等〕1.选题的背景和意义1.1 选题的背景步进电机已成为出直流电机和交流电机以外的第三类电动机。

传统电动机作为机电能量转换装置,在人类的生活和生产进入电气化过程中起着关键的作用。

可是在人类社会进入电气化时代的今天,传统电动机已不能满足工业自动化和办公自动化等各种运动控制系统的要求。

开展了一系列新的具有控制功能的电动机系统,其中较有自己特点,且应用十分广泛的就是步进电机。

步进电机的开展与计算机工业密切相关。

自从步进电机在计算机外围设备上取代小型直流电动机以后,使其设备的性能提高,很快的促进了步进电机的开展。

另一方面,微型计算机和数字控制技术的开展,又将作为数控系统执行部件的步进电机推广应用到其他领域,如电加工机床、小功率机械加工机床、测量仪器、光学和医疗仪器以及包装机械等。

步进电机是一种使用非常广泛且易于准确控制的执行元件,随着微电子技术的开展,其控制方法多种多样。

基于FPGA 技术对步进电机的转速进展准确控制,满足了现代工业对步进电机的高要求。

1.2 国内外研究现状步进电机最早是在1920年由英国人所开发。

1950年后期晶体管的创造也逐渐应用在步进电机上,这对于数字化的控制变得更为容易。

以后经过不断改进,使得今日步进电机已广泛运用在需要高定位精度、高分解性能、高响应性、信赖性等灵活控制性高的机械系统中。

在生产过程中要求自动化、省人力、效率高的机器中,我们很容易发现步进电机的踪迹,尤其以重视速度、位置控制、需要准确操作各项指令动作的灵活控制性场合步进电机用得最多。

步进电机作为执行元件,是机电一体化的关键产品之一, 广泛应用在各种自动化控制系统中。

FPGA设计实验考试题目(开卷)要求:以下题目除特别说明外,均必须通过硬件测试(即下载至开发板验证),并编写好Test Bench,通过ModelSim仿真,给出其源程序(关键语句必须解释语句含义)、功能仿真图、RTL图(主要图形说明其功能)或状态机图。

其中现场操作50分。

总分100分。

1、设计一个多位数据比较器(测试时以3位为例)2、设计一个投票表决器(测试时以5人为例)3、将开发板上的50MHZ时钟分频为秒脉冲时钟信号module fenp(clk_out,clk_in,reset); output clk_out; input cl k_in; input reset; reg [1:0] cnt; reg clk_out;lways@(posedge clk_in or posedge reset) begin if(reset) begin cnt<=0; clk_out<=0; end else beginif(cnt==24999999) beginclk_out<=!clk_out; cnt<=0; end else cnt<=cnt+1; end end end module系统时钟为50MHz,用Verilog代码怎样将其分频至1/100smodule S20 (clk,rst,clk_out);input clk,rst;output clk_out;reg clk_out;reg [4:0] count1;always@( posedge clk or negedge rst)if ( !rst )begincount1 <= 0;clk_out<= 0;endelsebeginif (count1 < 20)begincount1 <= count1+1;if (count1>=10)clk_out <=1;elseclk_out <=0;endelsecount1 <=0;endendmodule设计一个分频器,要求:占空比为50%的任意奇数次5分频电路。

试题区:(试题区必须与答题区同时交回,含答题纸、试题纸、草稿纸的装订试卷不能分拆)一、单项选择题:(20分)1.在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,不正确的是___C___。

A.PROCESS为一无限循环语句;敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动。

B.敏感信号参数表中,不一定要列出进程中使用的所有输入信号;C.进程由说明部分、结构体部分、和敏感信号三部分组成;(进程由声明语句、顺序语句、敏感信号列表组成)D.当前进程中声明的变量不可用于其他进程。

2.在一个VHDL设计中idata是一个信号,数据类型为integer,数据范围0 to 127,下面哪个赋值语句是正确的___C___。

(信号赋值符号 <= )A.idata := 32;B.idata <= 16#A0#; (十进制数为:10*16= 160,idata范围为0~127)C.idata <= 16#7#E1;(十进制数为:7*16^1= 112)D.idata := B#1010#;3.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是___C___。

A.FPGA是基于乘积项结构的可编程逻辑器件;(FPGA芯片基于查找表的可编程逻辑结构)B.FPGA是全称为复杂可编程逻辑器件;(FPGA 现场可编程逻辑门阵列,CPLD才是复杂可编程逻辑器件)C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。

(MAX7000系列属CPLD结构)4.进程中的变量赋值语句,其变量更新是___A___。

(变量(variable)是立即完成的,信号(signal)有延时)A.立即完成;B.按顺序完成;C.在进程的最后完成;D.都不对。

5.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述___D___。

FPGA设计实验考试抽测题目[1]FPGA设计实验抽测题目1、试用verilog设计一个基本RS锁存器(用行为描述风格),并用test bench程序测试。

要求:用modelsim进行仿真,给出仿真波形图RS锁存器(行为描述方式)Module part2(Q,R,S,CLK);input CLK,R,S;output Q;wire Rg,Sg,Qa,Qb;assign Rg=CLK&R;assign Sg=S&CLK;assign Qa=~(Rg,Qb);assign Qb=~(Sg,Qa);assign Q=Qa;endmoduletest bench程序测试`include”part2.v”module test;reg Rin,Sin,Clock;wire Outa,Outb;intialbeginRin=0;Sin=0;Clock=0;endalways #50 clock=~clock;always@(posedge clock)begin#1 Rin={$random}%2;#3Sin={$random}%2;endpart1 p(.Qa(Outa),.Qb(Outb),.R(Rin),.S(Sin),.CLK(Clock));endmodule2、试用verilog设计一个基本RS锁存器(用结构描述风格),并用test bench程序测试。

RS锁存器(结构描述方式)Module part1(Q,R,S,CLK);input CLK,R,S;output Q;wire Rg,Sg,Qa,Qb;and(Rg,CLK,R);and (Sg ,S,CLK);nor (Qa,Rg,Qb);nor (Qb,Sg,Qa);assign Q=Qa;endmoduletest bench程序测试。

`include”part1.v”module test;reg Rin,Sin,Clock;wire Outa,Outb;intialbeginRin=0;Sin=0;Clock=0;endalways #50 clock=~clock;always@(posedge clock)begin#1 Rin={$random}%2;#3Sin={$random}%2;endpart1 p(.Qa(Outa),.Qb(Outb),.R(Rin),.S(Sin),.CLK(Clock));endmodule3、试用verilog设计一个带低电平清零的D锁存器(用行为描述风格),并用test bench程序测试。

NANCHANG UNIVERSITY学士学位论文THESIS OF BACHELOR(2009—2013年)题目基于FPGA的时间-数字转换器设计学院:信息工程学院系电子系专业班级:电子信息工程093班基于FPGA的时间-数字转换器设计摘要时间是物质存在和运动的基本属性之一,它是科学研究、科学实验和工程技术等领域的必不可少的参量。

时间-数字转换器作为时间测量技术的核心,在诸多领域都有广泛的应用。

实现时间-数字转换电路的方法有许多种,如计数器法、电流积分法、门延迟法以及FPGA法等。

本论文设计的是基于FPGA的时间-数字转换器,设计思想是以计数器为粗时间间隔测量单元,门延迟为细时间间隔测量单元,最终基于FPGA实现TDC系统。

设计借助了Verilog HDL语言对FPGA 进行设计,完成了边缘检测、计数器及串口输出的软件设计,实现了测量范围为30min,分辨率达1ns的大范围、高分辨率TDC系统的设计。

本系统可移植性强,在提高时钟频率和门延迟精度后可应用于微粒子探测、激光测距和定时定位等领域。

关键词:时间-数字转换器FPGA 计数器门延迟分辨率AbstractDesign of Time to Digital Converter based on FPGAAbstractTime is one of the basic attribute of material’s existence and exercise, it’s an essential parameter of scientific researches, scientific experiments, engineering technology and other technology fields. Time-digital converter, as a time measurement technology core, are widely used in many fields.There are many ways to implement the time-digital converter, such as the counter method, the current integration method, the gate delay method and the FPGA method. This thesis designed a FPGA based TDC, the design idea is using the counter as a crude time interval measurement, the gate delay as a precise time interval measurement, and finally, the system is achieved by the FPGA. In the design, with the language of Verilog HDL, we achieved the software design of the edge detection, the counter and the outputting of serial. A measurement range of 30min, 1ns resolution of the large-scale, high-resolution TDC system is designed. This system is portable, if the clock frequency and the accuracy of gate delay are improved, it can be used in particle detection, laser ranging and timing positioning and any other fields.Keywords: Time to Digital Converter; FPGA; Counter; Gate delay; Resolution目录摘要 (I)ABSTRACT (II)前言 (1)1.1选课的背景及意义 (1)1.2国内外研究现状 (1)1.3课题所做的工作及论文章节安排 (2)1.3.1设计思想 (2)1.3.2论文章节安排 (2)时间-数字转换技术研究与分析 (4)2.1时间-数字转换电路的应用领域研究 (4)2.2时间-数字转换电路实现方法分析比较 (4)2.2.1计数器法 (4)2.2.2电流积分法 (5)2.2.3门延迟法 (6)2.2.4 FPGA法 (6)2.3 小结 (6)时间数字转换系统的硬件设计 (7)3.1硬件系统总体设计 (7)3.2开发板介绍 (7)3.3 FPGA芯片介绍 (9)3.3.1 FPGA简介及Cyclone ⅡEP2C5Q208C8N芯片概述 (9)3.3.2Cyclone ⅡEP2C5Q208C8N芯片的特点 (10)3.4 FPGA开发流程 (10)3.4.1功能定义和器件选型 (10)3.4.2设计输入 (11)3.4.3布线布局 (11)3.5 Quartus II仿真平台介绍 (12)3.5.1设计输入 (12)3.5.2项目编译 (13)3.5.3项目仿真 (13)时间-数字转换系统的软件设计 (14)4.1 Verilog语言介绍 (14)4.2基于Verilog语言的FPGA总体设计 (14)4.2.1设计目标及核心原理 (14)4.2.2边缘检测工作原理及设计 (16)4.2.3计数器工作原理及设计 (16)4.2.4门延迟细计数原理及设计 (18)4.2.5数据计算模块原理 (20)4.2.6串口输出模块设计 (20)系统测试 (22)5.1 边缘检测仿真 (22)5.2计数器仿真 (22)5.3串口发送数据仿真 (23)5.4时间-数字转换系统测试 (23)总结 (25)参考文献(Reference) (26)致谢 (27)附录 (28)第一章前言1.1选课的背景及意义时间既是一个抽象的概念,又是物质存在和运动的基本属性之一。

1.花样彩灯控制器的设计设计要求:假设输入脉冲为3MHz,控制16只LED发光二极管每隔1s或2s显示一种花样。

要求显示的花样如下:闪烁2次从LED(0)移位点亮到LED(15)一次全部点亮一次从LED(15)开始逐个熄灭至LED(0)1次闪烁2次。

如果按下清零键时,16只LED均熄灭一次,然后再重新按规律显示。

如果没有按下快/慢选择控制键时,16只LED发光二极管是以每隔1s进行花样显示,否则按下快/慢键选择控制键时,16只LED发光二极管是以每隔2s进行花样显示。

2.利用FPGA实现一个简单的DDS正弦波发生器(DDS:数字显示示波器)可分解为三个部分来设计:时钟产生模块;地址产生模块;ROM查找表模块。

实现思路:①首先,由外部晶振引入40MHz的时钟到FPGA内部,进入时钟产生模块,对时钟进行处理并3倍频程后,得到一个稳定精确的120MHz的系统时钟;②然后,地址产生模块在系统时钟的激励下,将频率控制字与累加寄存器输出的数据进行累加,然后把累加的结果作为地址输出给ROM查找表地址;③最后,ROM查找表模块在每个系统时钟的上升沿,按照地址来读取ROM 查找表中的相应的波形采样点数据并输出,该数就是最终的DDS信号。

3.多功能信号发生器的设计设计要求:设计一个多功能信号发生器,能够以稳定的频率产生锯齿波、增减锯齿波、三角波、阶梯波、正弦波和方波等六种信号。

系统有3个波形选择开关和一个复位开关,通过波形选择开关可以选择以上各种不同种类的输出波形;按下复位开关时,系统将复位。

设计实现:由于FPGA只能直接输出数字信号,而多功能信号发生器输出的各种波形均为模拟信号,因此设计信号发生器时,需将FPGA输出的信号通过D/A转换电路将数字信号转换成模拟信号。

多功能信号发生器可由信号产生电路、波形选择电路和D/A转换电路构成。

如下图所示:时钟信号波形输出选择信号4.数字跑表的设计设计要求:设计一个数字跑表,该跑表具有复位、暂停、秒表计时等功能。

该跑表有三个输入端,分别为时钟输入(CLK)、复位(CLR)和启动/暂停(PAUSE)复位信号高电平有效,可对整个系统异步清0,当启动/暂停(PAUSE)键为低电平时跑表开始计时,为高电平时暂停,变低后在原来的基础上再计数。

为了便于显示,可分秒、秒和分钟信号皆采用BCD码计数方式,并直接输出到6个数码管显示。

5.8位数字频率计的设计设计一个8位频率计,可以测量从1Hz到99 999 999Hz的信号频率,并将被测信号的频率在8个数码管上显示出来。

采用一个标准的基准时钟,在单位时间(如1s)里对被测信号的脉冲数进行计数,即为信号的频率。

整个系统分为三个模块:控制模块,计数测量模块和锁存器模块。

6.基于FPGA的简单运算器的设计①设计要求:该运算器能完成-7到+7的简单的加、减、与、异或四种运算功能,并且可以对溢出的结果进行修正。

硬件实验板由一个八按键电路和一个32位LCD 显示器组成,通过相应的按键输入把运算结果显示在LCD显示器上。

②设计原理:该运算电路由按键输入、控制、修正、显示和运算五大模块组成,来实现加、减、与、异或四种运算功能,首先按键模块用于输入两个数的运算符,通过控制模块传送到运算器模块进行运算,再连接到修正模块,通过修正模块对“溢出”的数值进行修正,最后显示模块功能实现把运算过程反应到LCD 显示器上。

7.基于FPGA的脉冲信号型乐曲播放器的设计设计要求:利用FPGA设计一个控制器,让不同频率的脉冲信号有序的输出并驱动扬声器发声,最终完成一首乐曲的演奏。

设计步骤:①预置乐曲,作预置时,需将乐曲音符转换成相应代码,通过计算逐一将音符换成代码,通过相应软件平台进行乐曲定制;②为提供乐曲发音所需的发音频率,编写数控分频器程序,对单一输入高频,进行预置数分频,生成每个音符的相应频率;③为了给分频提供预置数,需计算分频预置数;④对每部分结构单元逐一进行编译,生成相应的元器件符号,并对独立结构单元功能进行仿真。

8.闹钟系统的设计设计一个带闹钟功能的24小时计时器,包括以下几个组成部分:①显示屏,由四个七段数码管组成;②数字键‘0’到‘9’,输入时间;③TIME(时间)键,用于确定新的时间设置;④ALARM(闹钟)键,用于确定新的闹钟时间设置;⑤扬声器该设计要求完成如下功能:计时功能;闹钟功能;设置新的计时器时间;设置新的闹钟时间;显示所设置的闹钟时间;根据以上的设计要求,整个系统大致包括如下几个组成部分:用于键盘输入的缓冲器;用于时钟计数的计数器;用于保存闹钟时间的寄存器;用于显示七段数码显示电路以及控制以上各部分协同工作的控制器。

9.数字钟的设计①设计要求:假设外部输入脉冲为1Hz,要求使用该频率设计一个时间可调,并通过LED 七段共阴极数码管显示时、分、秒的数字钟。

②设计原理:进行设计数字钟的设计时,首先对1s的时钟进行计数,当计数达到60次时,输出1个分钟(min)脉冲;当1min的时钟计数到达60次时,输出1个小时(h)脉冲;若1h的时钟计数达到23次时,并且1min的计数到59次、1s的计数也达到59次,再来1个1s的脉冲,数字钟就自己复位,重新从零开始计时。

由此,可知数字钟由三个计数模块(二十四进制计数器、十进制计数器和六进制计数器)、7段LED驱动显示模块和顶层模块组成。

10.四组抢答器的设计设计要求:设计一个四组竞争抢答器系统,每组有1个对应的按钮,编号分别为A、B、C、D在主持人的主持下,参赛者通过抢先按下抢答按钮获得答题资格。

当某一组按下按钮并获得答题资格后,LED显示出该组编号,并有抢答成功显示同时锁定其他组的抢答器,使其他组抢答无效。

如果主持人在为按下开始按钮前,已有人按下抢答按钮,属于违规,并显示违规组的编号,同时蜂鸣器发音提示,其他组无效。

获得回答资格后,若该组回答的问题正确,则加1分,否则减1分。

抢答器设有复位开关,由主持人主持。

设计实现:根据设计要求,可以使用多个不同的单元模块,并通过有机的组合来得到抢答器系统。

这些单元模块主要包括抢答判断模块、计分模块和7段LED显示驱动模块。

信号发生器结构图:时钟信号波形输出选择信号11.数字电压表的设计设计要求:使用FPGA控制ADC0809,设计一个量程为5V的数字电压表。

要求采用3位数码管显示电压值,可以显示小数点的后两位。

设计实现;使用FPGA控制ADC0809设计一个量程为5V的数字电压表时,首先通过FPGA 的相关端口控制ADC09809将外部输入转换成8位数字表,再将8为数字表返回到FPGA中进行相关处理,最后将处理好的数据通过LED数码管显示相应的电压值即可。

由于在此系统中只需要对一路模拟电压进行测量,因此可将ADD C 、 ADD B、 ADD A这3根地址选择线进行接地。

12.基于FPGA的可逆加减计数器的实现设计要求:可预置16位可逆加减计数器。

要求计数器有16位计数输出同时有进位和借位输出,预置输入采用同步方式。

用FPGA开发板上的按键作为加减计数控制输入,数码管(或LED)作为计数值输出。

13.采用RAM实现8位计数器设计要求:用一个10×8的双口RAM完成10个8位计数器,计数器的初值分别为1~10,时钟频率为1MHz,计数器技术频率为1Hz.用FPGA开发板上的按键作为计数器计数值的输出选择控制,数码管(或LED)作为选择计数器的计数值输出。

14.十字路口交通灯的设计设计要求:设计一个十字路口交通信号灯的控制电路,要求红、绿灯按一定的规律亮和灭,并在亮灯期间进行倒计时,且将运行时间用数码管显示出来。

绿灯亮时,为该车道允许通行信号,红灯亮时,为该车道禁止通行信号。

要求主干道每次通行时间为Tx秒,支干道每次通行时间为Ty秒。

每次变换运行车道前绿灯闪烁,持续时间为5秒。

即车道要由X转换为Y时,X在通行时间只剩下5秒钟时,绿灯闪烁显示,Y仍为红灯。

15.简单的数字密码锁的设计设计要求:①设计一个密码锁的控制电路,当输入正确密码时,输入开锁信号以推动执行机构的作用,用红灯亮,绿灯熄灭,表示关锁;用红灯灭,绿灯亮,开锁。

②在锁的控制电路中储存一个可以修改的6位密码,其中6位全为实际有效密码,当开锁按钮开关的输入代码等于存储器代码时,实现开锁。

否则一直关锁并持续产生报警信号。

③从第一个按钮触动后的5秒内若未就锁打开,则电路自动处于自锁状态。

使之无法再打开。

并由扬声器发出持续20秒的报警信号。

设计说明:①该题目的主要任务是产生一个开锁信号OPEN,而开锁信号的形成条件是,输入代码和已设密码相同。

实现这种功能的电路构思有多种,本题目运用两片8位锁存器,一片存入密码,另一片输入开锁代码,通过比较的方式,若两者相等,则形成开锁信号。

②在开锁信号产生时,要求输出声,光信号,声音的产生由开锁信号触动扬声器工作,光信号由开锁信号点亮LED指示灯。

③用按钮开关的第一个动作信号触发一个5秒定时器,若5秒内无开锁信号产生,让扬声器发出特殊音响,以示警告,并输出一个信号推动LED不断闪烁。

16.正负脉宽数控调制信号发生器的设计设计要求;此信号发生器可产生占空比可调的方波,高低电平的维持时间由 6 位二进制数控制。

设计思路:此信号发生器是由两个完全相同的可自加载加法计数器和 D 触发器组成的,它的输出信号的高低电平脉宽时间可分别由两组 6 位二进制预置数进行控制。

如果将初始值可预置的加法计数器的溢出信号作为本计数器的初始预置加载信号 LD,则可构成计数初始值自加载方式的加法计数器,从而构成数控分频器。

D 触发器的一个重要功能就是均匀输出信号的占空比。

总体框图:17.简易数据流检测器的设计设计要求:设计一个有限状态机检测5位二进制序列“10010”,要求数据采用串行输入,检测结果用一个高脉冲来指示。

用FPGA开发板上的按键作为数据流输入,led或数码管作为输出指示。

18.空调系统有限状态自动机的设计设计思路:设计一个空调系统的有限状态自动机,它的两个输入端A和B分别与传感器相连,用于检测室内温度。

如果室内温度正常,则A和B均为‘0’。

如果室内温度过高,则A为‘1’,B为‘0’。

如果室内温度过低,则A为‘0’,B为‘1’。

根据A和B的值来判断当前的状态(太热TOO_HOT,太冷TOO_COLD或适中JUST_RIGHT),并决定HEAT和COOL的输出值。

原理图如下:。