杭电计组实验报告10

- 格式:docx

- 大小:61.15 KB

- 文档页数:7

一、实习背景随着我国电子信息产业的飞速发展,电子制造行业在我国经济中扮演着越来越重要的角色。

为了更好地了解电子制造行业的工作环境、生产流程和企业管理,我选择了杭州电子科技大学(以下简称“杭电”)电子制造专业,并参加了杭电电子生产实习。

二、实习单位简介杭电电子是一家集研发、生产、销售于一体的高新技术企业,主要从事电子元器件的研发与生产。

公司拥有先进的生产设备、完善的质量管理体系和优秀的技术团队。

实习期间,我有幸参观了公司的生产车间、实验室和办公区域,对公司的整体情况有了较为全面的了解。

三、实习内容1. 生产车间实习在生产车间实习期间,我主要参与了以下几个方面的学习:(1)熟悉生产流程:我跟随生产一线的工人师傅,了解了公司产品的生产工艺流程,包括原材料采购、生产加工、组装、检验、包装等环节。

(2)学习操作设备:在生产车间,我学习了使用各种生产设备,如焊接机、组装机、检测仪等,掌握了基本操作技能。

(3)了解质量管理:在生产过程中,我了解到公司对产品质量的严格把控,从原材料到成品,每个环节都有严格的质量检查和检验。

2. 实验室实习在实验室实习期间,我主要参与了以下几个方面的工作:(1)学习产品研发:我跟随实验室的技术人员,了解了公司新产品的研发过程,包括需求分析、方案设计、样品制作、测试等。

(2)掌握实验技能:在实验室,我学习了各种实验设备的操作方法和实验技巧,提高了自己的动手能力。

(3)参与项目研发:在导师的指导下,我参与了实验室的一个项目研发,从方案设计到样品制作,都亲身经历了整个研发过程。

3. 办公室实习在办公室实习期间,我主要参与了以下几个方面的工作:(1)了解企业管理:我跟随公司管理人员,了解了公司的组织架构、企业文化、管理制度等。

(2)学习办公软件:在办公室,我学习了使用办公软件,如Word、Excel、PowerPoint等,提高了自己的办公效率。

(3)参与项目策划:我参与了公司一个项目的策划工作,从项目需求分析到项目实施计划,都积极参与其中。

杭电实习报告一、前言随着科技的飞速发展,人工智能技术在各行各业中的应用越来越广泛。

作为计算机专业的学生,为了更好地了解人工智能技术在实际应用中的开发和应用,我选择了杭州电子科技大学计算机科学与技术学院的实习项目。

在这次实习中,我参与了智能车工程制作及调试的工作,通过这次实习,我对人工智能技术有了更深入的了解,也提高了自己的实践能力。

二、实习内容1. 传感器信号采集处理在智能车工程制作中,传感器信号采集处理是关键的一步。

我们使用了工字谐振电感作为传感器来检测信号,通过合理的传感器布局,经过后续电路处理,完成对电磁信号的检测和采集。

这一过程需要对传感器的工作原理和电路处理技术有深入的了解,通过实践,我对这些知识有了更直观的认识。

2. 电机驱动和转向舵机控制智能车的行驶和转向需要电机驱动和转向舵机控制的支持。

在实习过程中,我们自主构思控制方案,设计了电机驱动和转向舵机控制的电路,并进行了软件算法的开发。

这一过程需要掌握电机驱动和舵机控制的技术,同时需要具备一定的编程能力。

通过实践,我掌握了电机驱动和舵机控制的技术,提高了自己的编程能力。

3. 控制算法软件开发控制算法软件是智能车的核心部分,它决定了智能车的行驶和转向性能。

我们使用了PID算法作为车子的主导控制,通过调整参数,实现了对智能车的精确控制。

这一过程需要对控制算法有深入的了解,同时需要具备一定的编程能力。

通过实践,我对控制算法有了更深入的了解,提高了自己的编程能力。

4. 整车布局和调试为了提高智能车在高速与急转等情况下的动力性能和稳定性能,我们需要对整车进行重心与电路等的布局,并对车辆底盘和舵机部分进行改造。

在实习过程中,我们参考学习了前几届队伍的参赛经验,对整车进行了优化布局,并对车辆底盘和舵机部分进行了改造。

这一过程需要具备一定的机械设计和改装能力,通过实践,我提高了自己的机械设计和改装能力。

三、实习收获通过这次实习,我对人工智能技术在实际应用中的开发和应用有了更深入的了解,提高了自己的实践能力。

电子线路实习报告一、实习目的与要求本次电子线路实习旨在让我们更好地理解和掌握电子线路的基本原理和实验技能,培养我们的动手能力和实践能力。

实习要求我们严格遵守实验室纪律,认真完成实验任务,及时记录实验数据和现象,并进行分析总结。

二、实习内容与过程1. 实习前的准备:在实习开始前,我们学习了电子线路的基本原理和实验设备的使用方法。

通过理论学习的铺垫,我们对电子线路实验有了初步的了解。

2. 实习过程:实习过程中,我们按照指导书的要求,完成了以下几个实验项目:(1)电子线路的认识与测量:我们学习了电子元器件的识别和测量方法,掌握了万用表、示波器等仪器的基本使用技巧。

(2)简单的电子线路搭建:我们根据电路图,用面包板搭建了简单的放大电路、滤波电路等,并学会了使用仪器对电路进行分析。

(3)集成运算放大器的应用:我们学习了集成运算放大器的基本原理和应用,掌握了放大、滤波、积分、微分等电路的设计方法。

(4)数字电路的设计与验证:我们学习了数字逻辑电路的基本原理,用集成逻辑门电路设计了一些简单的数字电路,如编码器、译码器等,并使用仪器进行了验证。

3. 实习成果:通过实习,我们掌握了电子线路的基本实验技能,能够独立完成简单的电子线路设计和分析。

同时,我们也培养了实验报告的撰写能力,能够对实验过程和结果进行完整的记录和总结。

三、实习收获与体会1. 实践能力得到提高:通过本次实习,我们在电子线路实验方面的实践能力得到了很大提高。

我们学会了如何使用实验设备,掌握了电子线路的基本实验技能,为以后的学习和工作打下了坚实基础。

2. 团队合作意识增强:在实习过程中,我们与同学们一起探讨、共同进步,不仅提高了个人能力,也培养了团队合作意识。

3. 培养了解决问题的能力:在实习过程中,我们遇到了许多问题,但通过查阅资料、请教老师和同学,我们逐一解决了这些问题。

这使我们学会了如何独立解决问题,提高了我们的综合素质。

4. 认识到了理论联系实际的重要性:通过实习,我们深刻体会到理论联系实际的重要性。

计组实验报告(共10篇)计组实验报告计算机组成原理实验报告一一、算术逻辑运算器1. 实验目的与要求:目的:①掌握算术逻辑运算器单元ALU(74LS181)的工作原理。

②掌握简单运算器的数据传输通道。

③验算由74LS181等组合逻辑电路组成的运输功能发生器运输功能。

④能够按给定数据,完成实验指定的算术/逻辑运算。

要求:完成实验接线和所有练习题操作。

实验前,要求做好实验预习,掌握运算器的数据传送通道和ALU 的特性,并熟悉本实验中所用的模拟开关的作用和使用方法。

实验过程中,要认真进行实验操作,仔细思考实验有关的内容,把自己想得不太明白的问题通过实验去理解清楚,争取得到最好的实验结果,达到预期的实验教学目的。

实验完成后,要求每个学生写出实验报告。

2. 实验方案:1.两片74LS181(每片4位)以并/串联形式构成字长为8为的运算器。

2.8为运算器的输出经过一个输入双向三态门(74LS245)与数据总线相连,运算器的两个数据输入端分别与两个8位寄存器(74LS273)DR1和DR2的输出端相连,DR1和DR2寄存器是用于保存参加运算的数据和运算的结果。

寄存器的输入端于数据总线相连。

3.8位数据D7~D0(在“INPUT DEVICE”中)用来产生参与运算的数据,并经过一个输出三态门(74LS245)与数据总线相连。

数据显示灯(BUS UNIT)已与数据总线相连,用来显示数据总线上所内容。

4.S3、S2、S1、S0是运算选择控制端,由它们决定运算器执行哪一种运算(16种算术运算或16种逻辑运算)。

5.M是算术/逻辑运算选择,M=0时,执行算术运算,M=1时,执行逻辑运算。

6.Cn是算术运算的进位控制端,Cn=0(低电平),表示有进位,运算时相当于在最低位上加进位1,Cn=1(高电平),表示无进位。

逻辑运算与进位无关。

7.ALU-B是输出三态门的控制端,控制运算器的运算结果是否送到数据总线BUS上。

低电平有效。

杭电生产实习报告(精选18篇)杭电生产篇1从x月x日到x月x日,在此期间我们土木工程专业到合肥市三个大型建筑工地上实习,虽然在此之前我们的专业课还没有开设,但通过此次的实习也让我们每个土木人受益非浅,让我们对建筑物有了初步的感行认识,以及为我们今后开设专业课,学习专业知识打下坚实的基础。

非常感谢学校给我们这次实习的机会,让我们有机会到建筑工地现场观看实习,让我们亲眼目睹施工人员如何对建筑物施工。

我们每个人都很高心能够有这样的机会,让我们学习到很多书本上学不到知识。

三天到工地上实习,学校都是用校车专车接送,当我们到达工地集合地点时,我看到同学们头上都戴着安全帽;同时工地的生活区与施工区的门上也写着:不戴安全帽者不得进如施工现场;当然在建筑物结构主体外面的防护网上也写着标语:安全责任,重于泰山;由此可见在建筑施工当中首先要注意的问题就是安全问题。

过去由于生产企业不重视民工安全造成了很多工伤和死亡事故,这些事故给工人和企业带来了很大的损害!同时,为了确保施工能顺利进行和施工的安全,工地是要用砖墙围护起来的,只有建筑施工的各种车辆和内部人员才可以出入,我们实习也要事先和施工方协调商议经过他们的。

进到施工区,我们一眼就看到了建筑物的结构主体,当时结构主体给我的感觉就是不像建筑很不好看。

这个可能是因为它和我所看到过的已经建好并投入使用的楼不同。

主体前面有个很大的场地,这个场地是堆放建筑材料用的,可以看到所堆放的建材主要是钢筋,没有水泥、砂、石之类的建材,这是因为现在已经都采用了成品混凝土来浇筑结构了。

这样可以保证混凝土的质量,减少施工浪费和降低生产成本。

在钢筋堆放区我们可以看到不同型号的钢筋是分开放的,而且还在其前面标明钢筋的型号和进场时间等信息。

在建筑工地上我看到我从未看到过的建筑材料,名字记的不太清楚了,叫加压混凝气团,目前合肥很少有建筑公司在使用这种材料,相对那些传统红砖来说这种材料有很多红砖所不具有的特点:具有隔音保温的作用。

一、实习背景随着科技的不断发展,电子线路在各个领域的应用越来越广泛。

为了使学生们更好地了解电子线路的实际应用,提高实践操作能力,杭州电子科技大学特此组织了电子线路实习活动。

本次实习旨在让学生们深入了解电子线路的基本原理,掌握电子线路的设计与调试方法,培养学生的动手能力和创新意识。

二、实习目的1. 熟悉电子线路的基本原理和常用电子元器件;2. 掌握电子线路的设计与调试方法;3. 培养学生的动手能力和创新意识;4. 提高学生的团队合作能力。

三、实习内容1. 电子线路基础知识学习实习期间,学生们首先学习了电子线路的基本原理,包括电路元件、电路分析方法、电路设计方法等。

通过学习,学生们对电子线路有了初步的认识。

2. 电子线路设计与制作在掌握电子线路基础知识的基础上,学生们开始进行电子线路的设计与制作。

实习过程中,学生们根据所学知识,独立完成以下任务:(1)设计一个简单的电子线路,如稳压电源、滤波电路等;(2)根据设计图纸,选用合适的电子元器件进行焊接;(3)调试电路,确保电路性能达到预期效果。

3. 电子线路测试与优化在完成电子线路设计与制作后,学生们对电路进行测试,并对电路性能进行优化。

具体内容包括:(1)测试电路的稳定性、抗干扰能力等;(2)根据测试结果,对电路进行改进,提高电路性能;(3)撰写实习报告,总结实习经验。

四、实习过程1. 第一阶段:电子线路基础知识学习在这一阶段,学生们通过课堂讲授、自学等方式,掌握了电子线路的基本原理和常用电子元器件。

2. 第二阶段:电子线路设计与制作在这一阶段,学生们根据所学知识,独立完成电子线路的设计与制作。

在制作过程中,学生们遇到了各种问题,通过查阅资料、请教老师等方式,最终成功解决了问题。

3. 第三阶段:电子线路测试与优化在这一阶段,学生们对电路进行测试,并对电路性能进行优化。

通过不断尝试和改进,电路性能得到了明显提升。

五、实习收获1. 掌握了电子线路的基本原理和常用电子元器件;2. 学会了电子线路的设计与调试方法;3. 培养了学生的动手能力和创新意识;4. 提高了学生的团队合作能力。

杭电电子线路实习报告实习单位:杭州电子科技大学实习时间:2024年7月1日-2024年7月31日实习地点:杭州市余杭区杭州电子科技大学一、实习目的和任务本次实习旨在通过参与杭州电子科技大学的电子线路项目,提升实习生对电子线路实践的认识和操作能力。

具体的实习任务包括以下几个方面:1.学习电子线路的基本原理和知识,了解电子线路的搭建和调试过程;2.参与实际的电子线路项目,进行电子线路的设计和实验;3.学习并掌握电子线路相关软件的使用和基本操作;4.参与电子线路实验的分析和总结,撰写实习报告。

二、实习内容和方法1.学习电子线路的基本原理和知识:通过学习相关的教材和资料,了解电子线路的基本原理和知识,包括电子元器件的基本特性、电路的基本组成和工作原理等。

2.参与实际的电子线路项目:在导师的指导下,参与实际的电子线路项目,包括电路的设计、搭建和调试。

通过实际操作,掌握电子线路的搭建和调试过程,提高对电子线路的实践能力。

3.学习并掌握电子线路相关软件的使用和基本操作:学习使用电子线路设计软件,如Protues、Altium Designer等,掌握其基本操作和使用方法。

通过实际的操作和练习,提高对电子线路设计软件的熟练程度。

4.参与电子线路实验的分析和总结,撰写实习报告:在完成实际的电子线路实验后,进行实验结果的分析和总结,撰写相应的实习报告。

通过实习报告的撰写,提升对电子线路实验的整体理解和应用能力。

三、实习感想和收获在本次实习中,我通过参与电子线路项目的设计和实验,深入了解了电子线路的基本原理和知识,提高了对电子线路的实践能力和技术水平。

通过与导师和同学们的合作,我学到了很多实践经验和技巧,对电子线路的搭建和调试过程有了更加深入的认识。

在实践操作中,我学习并掌握了电子线路设计软件的使用方法,能够熟练地进行电路设计和仿真。

通过实际的电子线路实验,我学会了如何进行实验结果的分析和总结,掌握了一些实验技巧和方法。

杭电电子线路实习报告一、实习目的与意义电子线路实习是电子信息工程专业的一门重要实践性课程,通过实习,使我们能够将所学的理论知识与实际操作相结合,提高我们的动手能力和实际问题解决能力。

本次实习,我选择了杭州电子科技大学电子线路实验室进行,实习时间为两周。

二、实习内容与过程在实习期间,我们进行了多个实验项目,包括晶体管放大器、振荡器、滤波器等。

下面我将对其中几个实验项目进行详细介绍。

1. 晶体管放大器实验晶体管放大器实验是电子线路实习中的一个重要实验项目。

通过这个实验,我们了解了晶体管的放大原理,掌握了晶体管放大器的设计与调试方法。

首先,我们根据实验原理,设计了晶体管放大器的电路图,并选择了合适的晶体管。

然后,我们用万用表测量了晶体管的参数,确保其符合设计要求。

接下来,我们将晶体管焊接在电路板上,并连接电源、信号源等设备。

在调试过程中,我们通过改变负载电阻的值,观察晶体管放大器的放大效果。

通过多次调试,我们最终使晶体管放大器达到了预期的放大效果。

2. 振荡器实验振荡器实验是另一个重要的实验项目。

通过这个实验,我们了解了振荡器的工作原理,掌握了振荡器的设计与调试方法。

首先,我们根据实验原理,设计了LC振荡器的电路图,并选择了合适的元件。

然后,我们将元件焊接在电路板上,并连接电源等设备。

在调试过程中,我们通过改变电感线圈和电容器的值,观察振荡器的工作状态。

通过多次调试,我们最终使振荡器产生了稳定的正弦波输出。

3. 滤波器实验滤波器实验是电子线路实习中的另一个实验项目。

通过这个实验,我们了解了滤波器的工作原理,掌握了滤波器的设计与调试方法。

首先,我们根据实验原理,设计了低通滤波器的电路图,并选择了合适的元件。

然后,我们将元件焊接在电路板上,并连接信号源等设备。

在调试过程中,我们通过改变电阻、电容等元件的值,观察滤波器的滤波效果。

通过多次调试,我们最终使滤波器实现了预期的滤波效果。

三、实习收获与体会通过这次电子线路实习,我收获了很多。

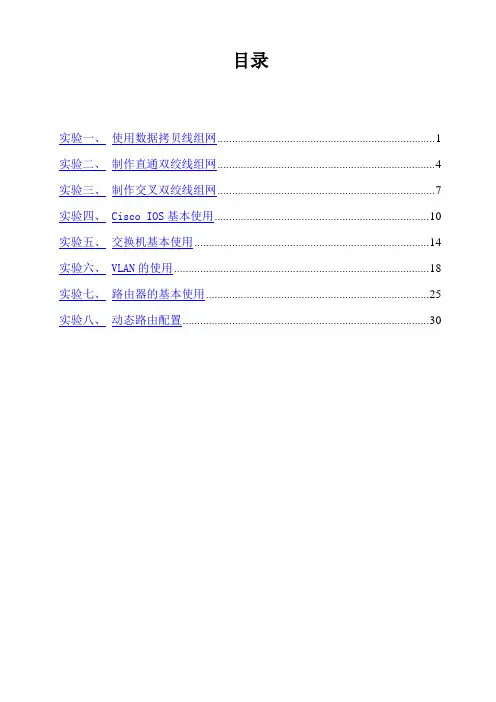

目录实验一、使用数据拷贝线组网 (1)实验二、制作直通双绞线组网 (4)实验三、制作交叉双绞线组网 (7)实验四、Cisco IOS基本使用 (10)实验五、交换机基本使用 (14)实验六、VLAN的使用 (18)实验七、路由器的基本使用 (25)实验八、动态路由配置 (30)实验一、使用数据拷贝线组网实验一使用数据拷贝线组网实验台号:实验时间:实验小组号:成员及本次实验分工:实验目的:学会使用并行电缆(数据拷贝线)实现双机通信和资源共享。

使用直接电缆实现两台PC机之间的通信。

实验环境说明:硬件:2台计算机、2-3根并行电缆软件:Windows XP操作系统实验过程及步骤(可另附页、使用网络拓扑图等辅助说明):(1)、使用并行电缆将两台PC机,进行物理互连;(2)、分别在两台PC机上的网上邻居中创建一个新连接。

按照新建连接向导的指示来做。

首先网络连接类型选为“设置高级连接”;然后其中作为服务器的那台PC机创建为“接受传入的连接”,作为客户机的则创建为“直接连接到其他计算机的连接”,并让此计算机担任“来宾”的角色。

接下去根据向导直至完成创建新连接。

(3)、测试两机的可通用性。

创建好连接之后可以用ping命令测试一下两台机器之间是否已经连通。

(4)、连接创建成功之后,客户机可以找到并登入到服务器,就可以实现对服务器上的资源的共享了。

当然在此之前作为服务器的主机还需要将文件夹属性设置成为可共享的。

测试数据线连接以后Ping对方说明能够Ping通在一台PC上设置共享,然后在另外一台PC上查看共享截图如下:说明通过数据拷贝线成功地连接了两台PC,实现了他们之间的通信。

实验总结(遇到的问题及解决办法、体会):刚开始配置客户机的时候出了点问题。

需要输入对方计算机的名字,我们却输入了服务器上的计算机用户的帐号,所以一直没有连接成功。

后来终于发现了这个问题。

配置也就顺利了。

实验器材、工具领用及归还负责人:验收人:实验执笔人:实验记录人:报告协助人:实验报告完成时间:小组成员签名:指导教师评议成绩评定:指导教师签名:实验二、制作直通双绞线组网实验二制作直通双绞线组网实验台号: 实验时间: 实验小组号:成员及本次 实验分工: 实验目的:1. 了解双绞线的相关知识;2. 学会制作直通双绞线;3. 掌握用双绞线实现集线器和计算机之间的互连。

一、实验模块实验名称:____________________实验课程:____________________实验时间:____________________实验地点:____________________实验人员:____________________二、实验标题____________________三、实验目的1. 了解____________________2. 掌握____________________3. 培养____________________四、实验原理____________________五、实验仪器与设备1. 仪器名称:____________________2. 仪器型号:____________________3. 仪器规格:____________________4. 其他设备:____________________六、实验步骤1. 实验步骤一:(1)____________________(2)____________________(3)____________________2. 实验步骤二:(1)____________________(2)____________________(3)____________________3. 实验步骤三:(1)____________________(2)____________________(3)____________________(注:根据实际实验内容,添加相应步骤)七、实验过程1. 实验过程一:(1)____________________(2)____________________(3)____________________2. 实验过程二:(1)____________________(2)____________________(3)____________________3. 实验过程三:(1)____________________(2)____________________(3)____________________(注:根据实际实验内容,添加相应过程)八、实验数据记录与分析1. 实验数据记录:(注:根据实际实验内容,添加数据记录表格)2. 实验数据分析:(注:根据实际实验内容,对实验数据进行分析)九、实验结论1. 实验结果:(1)____________________(2)____________________(3)____________________2. 实验结论:(1)____________________(2)____________________(3)____________________十、实验讨论1. 实验中遇到的问题及解决方法:(1)____________________(2)____________________(3)____________________2. 实验改进建议:(1)____________________(2)____________________(3)____________________十一、实验总结通过本次实验,我了解了____________________,掌握了____________________,培养了____________________。

一、实习背景随着科技的飞速发展,电子电路技术已成为现代社会不可或缺的一部分。

为了提高学生的实践能力,培养具备实际操作经验的电子电路技术人才,我校组织了电子电路实习活动。

本次实习在杭州电子科技大学电子电路实验室进行,旨在使学生了解电子电路的基本原理,掌握电子电路的设计与制作方法,提高学生的动手操作能力。

二、实习目的1. 熟悉电子电路的基本原理和设计方法;2. 掌握常用电子元器件的性能和选用技巧;3. 提高电子电路的调试和维修能力;4. 培养团队合作精神和创新意识。

三、实习内容1. 电子电路基础知识学习在实习初期,我们学习了电子电路的基本概念、电路元件、电路分析方法等基础知识。

通过学习,我们对电子电路有了初步的认识,为后续的实习工作奠定了基础。

2. 电子电路设计与制作在实习过程中,我们分组进行电子电路设计与制作。

具体内容包括:(1)电路设计:根据任务要求,我们查阅相关资料,确定电路拓扑结构,绘制电路原理图。

(2)元器件选用:根据电路原理图,选择合适的元器件,并计算其参数。

(3)电路制作:按照电路原理图,焊接元器件,组装成完整的电路。

(4)电路调试:对制作好的电路进行调试,确保电路性能达到预期要求。

3. 电路分析与应用在实习过程中,我们还学习了电路分析的基本方法,如基尔霍夫定律、欧姆定律等。

通过分析电路,我们了解了电路的性能和特点,为后续的电路设计与制作提供了理论依据。

4. 电路故障诊断与维修在实习后期,我们学习了电路故障诊断与维修的基本方法。

通过分析电路故障现象,找出故障原因,并采取相应的维修措施,使电路恢复正常工作。

四、实习收获1. 理论与实践相结合:通过本次实习,我们将所学理论知识与实际操作相结合,提高了自己的动手能力。

2. 团队合作:在实习过程中,我们分组进行电子电路设计与制作,培养了团队合作精神。

3. 创新意识:在电路设计与制作过程中,我们不断尝试新的方法,提高了创新意识。

4. 电路故障诊断与维修能力:通过实习,我们掌握了电路故障诊断与维修的基本方法,为今后的学习和工作打下了基础。

杭电电子生产实习报告一、前言作为一名电子信息工程专业的学生,我很荣幸能够在杭州电子科技大学电子生产实习课程中得到实践锻炼的机会。

在这两周的实习过程中,我深刻地认识到理论知识与实际操作的密切结合的重要性,同时也对电子生产流程有了更加全面的了解。

二、实习内容实习期间,我们主要进行了以下几个方面的学习和实践:1. 工厂参观:我们参观了杭州电子科技大学的电子工厂,了解了工厂的基本布局、生产流程以及各种设备的使用方法。

通过参观,我们对电子生产过程有了初步的认识。

2. 电子产品组装:在指导老师的带领下,我们动手组装了一款简单的电子产品。

在这个过程中,我们学习了如何识别元器件、如何阅读电路图、如何进行焊接等实际操作技能。

3. 生产工艺学习:我们学习了电子生产过程中的各种工艺,如SMT贴片工艺、波峰焊工艺、回流焊工艺等,并了解了各种工艺的优缺点及适用场景。

4. 品质控制:我们学习了电子产品质量控制的基本知识,了解了如何进行检验、测试和故障排查,以确保产品质量达到要求。

三、实习收获通过这次实习,我收获颇丰,具体表现在以下几个方面:1. 提高了动手能力:在组装电子产品的过程中,我学会了如何使用各种工具,如螺丝刀、镊子、焊接工具等,提高了自己的动手能力。

2. 加深了对电子生产过程的理解:通过实地操作,我更加深入地了解了电子生产过程中的各个环节,如元器件识别、电路图阅读、焊接工艺等,使我对电子生产有了更加全面的认识。

3. 学会了团队合作:在实习过程中,我们需要分组进行协作,共同完成任务。

在这个过程中,我学会了如何与团队成员沟通、协作,提高了团队协作能力。

4. 培养了质量意识:实习过程中,我们了解了电子产品质量控制的重要性,学会了如何进行质量检验和故障排查,培养了质量意识。

四、实习总结通过这次电子生产实习,我深刻认识到理论知识与实际操作的结合对于电子信息工程专业学生的重要性。

在今后的学习中,我将更加注重理论知识的学习,同时加强实践操作能力的培养,为将来的职业发展打下坚实的基础。

杭电电子线路实习实验报告一、实验目的1. 加深对电子线路理论知识的理解,提高实际操作能力。

2. 掌握基本电子仪器的使用方法,如示波器、信号发生器、万用表等。

3. 学习电子线路的安装与调试方法,培养动手能力和团队协作精神。

二、实验内容本次实验为电子线路安装与调试实验,主要包括以下内容:1. 根据电路图搭建电路;2. 正确使用仪器进行测试;3. 分析测试数据,判断电路是否存在问题;4. 调整电路参数,使电路达到预期性能;5. 撰写实验报告。

三、实验过程1. 根据实验指导书给出的电路图,搭建电路。

在搭建过程中,要注意元器件的极性、引脚顺序等,确保电路的正确性。

2. 使用万用表测量电路中的电压、电流等参数,初步判断电路是否正常。

3. 使用示波器观察电路中的信号波形,分析电路的性能。

如有问题,需调整电路参数,如电阻值、电容值等。

4. 针对电路中可能存在的问题,进行多次调试,直至电路性能达到预期。

5. 撰写实验报告,总结实验过程中遇到的问题及解决方法,反思实验过程中的不足。

四、实验结果与分析1. 实验结果:通过多次调试,最终使电路达到了预期性能,信号波形稳定,电路工作正常。

2. 结果分析:在实验过程中,我们掌握了电子仪器的使用方法,提高了动手能力。

同时,通过分析测试数据,我们学会了判断电路是否存在问题,并能够针对问题进行调整。

此外,实验过程中的团队协作也使我们更好地完成了任务。

五、实验收获1. 掌握了电子线路安装与调试的基本方法;2. 学会了使用电子仪器,如示波器、信号发生器、万用表等;3. 提高了动手能力和团队协作精神;4. 加深了对电子线路理论知识的理解。

六、实验反思1. 在实验过程中,我们要严谨认真,确保电路搭建的正确性;2. 学会分析测试数据,判断电路是否存在问题;3. 调整电路参数时,要耐心细致,切勿急躁;4. 加强团队协作,共同完成实验任务。

总之,本次电子线路实习实验使我们受益匪浅,不仅提高了实际操作能力,还加深了对电子线路理论知识的理解。

一、引言随着科技的不断发展,电子技术已经成为现代工业、日常生活和国防建设的重要组成部分。

为了让学生更好地理解和掌握电子线路的基本原理和设计方法,提高学生的实践能力和创新意识,我校电子工程系组织了电子线路实训课程。

本次实训旨在通过实际操作,使学生深入理解电子线路的基本概念、电路分析方法,并能够设计简单的电子电路。

二、实训目的1. 熟悉电子线路的基本元件和仪器设备。

2. 掌握电子线路的基本分析方法,如电路分析、模拟电路设计等。

3. 提高动手能力和实验技能,培养严谨的科学态度。

4. 培养学生的创新意识和团队合作精神。

三、实训内容本次实训主要包括以下内容:1. 基本元件识别与测试:识别和测试电阻、电容、电感、二极管、三极管等基本电子元件,了解其特性和参数。

2. 基本电路搭建与调试:搭建简单的电路,如放大器、滤波器、振荡器等,并对其进行调试,观察电路性能。

3. 电路分析方法学习:学习电路分析方法,如基尔霍夫定律、节点电压法、回路电流法等,并应用于实际电路分析。

4. 模拟电路设计:设计简单的模拟电路,如运算放大器、稳压电路、信号发生器等,并验证其性能。

5. 数字电路设计:学习数字电路的基本原理,设计简单的数字电路,如逻辑门、计数器、译码器等。

6. 电路仿真软件应用:使用电路仿真软件(如Multisim)进行电路设计和仿真,验证电路性能。

四、实训过程1. 准备阶段:了解实训内容,预习相关理论知识,准备实训所需的元件和仪器。

2. 实践阶段:- 元件识别与测试:通过实物观察和仪器测试,识别各种电子元件,了解其参数和特性。

- 基本电路搭建与调试:按照电路图搭建电路,连接元件,调试电路,观察电路性能。

- 电路分析方法学习:学习电路分析方法,如基尔霍夫定律、节点电压法、回路电流法等,并应用于实际电路分析。

- 模拟电路设计:设计简单的模拟电路,如运算放大器、稳压电路、信号发生器等,并验证其性能。

- 数字电路设计:学习数字电路的基本原理,设计简单的数字电路,如逻辑门、计数器、译码器等。

实验一、常规PID控制算法仿真仿真框图如下实验参数:shiyanpid Ts=0.1s,b为班号1~5,x为学号后2位,1~45实验要求:(1)画Simulinnk框图(2)设计或凑试PID三个参数,进行仿真(3)使稳态误差为0,且动态性能较满意仿真框图:实验分析:b=1,x=15。

比例系数Kp增大时系统动作灵敏,响应速度加快,过大会使振荡次数增加,系统趋向不稳定,这里取120。

积分环节可以消除稳态误差,Ti减小,系统振荡次数增加,这里取Ki为150。

微分环节可以改善系统动态性能,减小超调和调节时间,这里取Kd为10。

系统在2秒内达到稳态。

实验二、积分分离PID控制算法仿真实验参数:shiyanpidjffl Ts=0.1s,b为班号1~5,x为学号后2位,1~45实验要求:(1)画Simulinnk框图(2)使稳态误差为0,且动态性能较满意(3)尝试不同的积分分离的阈值(比如ε=0,0.1,0.2,……,0.9,1),观察阶跃响应,并确定最佳的阈值实验框图:翻译后Switch模块的说明:如果2输入满足规则,则1通道通过,否则3输入通过。

输入被标号。

1输入通过规则是输入2(偏差e)大于或等于阀值。

第一三输入为数据输入,第二输入为控制输入。

原理:|e(k)|<=ε,ki起作用|e(k)|>ε,ki不起作用,由于阶跃输入,(treshhold )ε=0.1,0.2,……,0.9,1。

由于参数原因去kp=50,ki=kd=0时,曲线最好为了体现ε的作用,积分值不取0,改为Ki=10取不同ε后的曲线ε=0.1ε=0.5ε=1分析:ε=0.1时曲线最好,ε过大起不到积分分离的作用,比如ε=1,总会存在积分作用,ε过小可能是控制不能跳出积分分离的区域,从而只存在PD作用,长时间存在静差。

实验三、不完全微分PID控制算法仿真1、不完全微分PID控制器的阶跃响应实验参数:Shiyanpidbwqwfstep Ts=0.1s,仿真时间设为10s,5s,3s P=1 I=1 D=1滤波器参数a=0.1,0.2,……,0.8,1.2,实验框图:框图1:积分输出:微分输出:可见微分只在第一个单位时间有相应,而且较大框图2:a=0.1时a=0.5时:a=1时:分析:引入惯性环节后,对微分环节对阶跃响应有明显的改善作用。

杭电电子线路实习报告 Modified by JEEP on December 26th, 2020.电子线路实习报告姓名:学号:班级:实习时间:实习教室:指导教师:1.报告内容①实习目的1、掌握有源音箱的工作原理以及各元件的作用。

2、掌握焊接有源音箱的方法。

4、了解一般电子电路的设计过程和调试方法。

②电路中各元件作用及原理1、PCB图如下:.2、各元器件作用及原理LR1,LC1,LR2,RR1,RC1,RR2:选频网络,选出中高音。

LR3,LC2,RR3,RC2,R7,C5:调整低频转折率。

LC3,LR5,RC3,RR5,C6,C9:消振网络,防止自激。

LR6,LR7,RR6,RR7:保护电阻。

IC2,IC3,IC4:运算放大器,放大增益。

LR3,LR4,RR3,RR4,R7,R8:反馈电阻。

R1,R2:衰减电阻。

C1:耦合电阻。

IC1:低通滤波,选出低频。

电位器:控制音量。

③计算滤波器的转折频率C2=,C3=,R4=R5=10KΩC2=((2πfp)R),C3=((2πfp)R)fp=110Hz④组装中的故障分析1、焊接过程中,有个别孔径过小,需要将导线剪细后才可插入焊接。

2、调试过程中,低音的声音较小。

通过网络查找发现有可能是放大器增益不够、信号源输出较弱等原因存在。

3、调试过程中,发现低音有杂音存在,有可能是焊接过程中,焊点不够牢固引起线路出现接触不良的情况2.建议与意见通过本次的电子线路实习,让我对有源音箱的工作原理有了深刻的了解,在对音响的组装及后续的调试过程中,增强了自己的操作能力,学会了正确的焊接方法。

对于该课程,我也没有太好的建议,因为指导老师的教学方法还是非常妥当的,课上所讲解的内容都能够较好的掌握,为后面的实践打下良好的基础。

即使在组装过程中出现问题,也能够通过老师或者周围的同学及时的解决问题,因此只要有足够的耐心,能认真的听讲,都能够顺利的完成布置的组装任务。

计组实验十老师:包健一、源代码测试模块代码:module Top(inputinclk,inputmem_clk,inputrst,outputreg[7:0] LED,input [3:0] SW);wireclk;MyButtonmb(.clk_100MHz(mem_clk),.BTN(inclk),.BTN_Out(clk));wire [31:0] ALU_F;wire [31:0] M_R_Data;wire ZF;wire OF;wire [31:0]PC;My_I_CPUmy_i_cpu(.clk(clk),.mem_clk(mem_clk),.rst(rst),.ALU_F(ALU_F),.M_R_Data(M_R_Data),.ZFF(ZF),.OF(OF),.PC_out(PC));always@(*)begincase(SW)4'd0:LED=ALU_F[7:0];4'd1:LED=ALU_F[15:8];4'd2:LED=ALU_F[23:16];4'd3:LED=ALU_F[31:24];4'd4:LED=M_R_Data[7:0];4'd5:LED=M_R_Data[15:8];4'd6:LED=M_R_Data[23:16];4'd7:LED=M_R_Data[31:24];4'd8:LED={ZF,6'd0,OF};4'd12:LED=PC[7:0];4'd13:LED=PC[15:8];4'd14:LED=PC[23:16];4'd15:LED=PC[31:24];default:LED=8'b0000_0000;endcaseendendmodule顶层模块代码:moduleMy_I_CPU(inputclk,inputmem_clk,inputrst,output [31:0] ALU_F,output [31:0] M_R_Data,output ZFF,output OF,output [31:0]PC_out);//wire clk_n = ~clk;wire[31:0] codes;wire [31:0]PC_new;reg [31:0]PC;Inst_Fetch1 inst_fetch(.PC(PC),.rst(rst),.clk(clk),.Inst_codes(codes),.PC_new(PC_new));wire[5:0] OP;wire[5:0] func;wire ZF;assign ZFF=ZF;assignPC_out=PC;wire [1:0]w_r_s;wireimm_s;wirert_imm_s;wire [1:0]wr_data_s;wire[2:0] ALU_OP; wireWrite_Reg;wireMem_Write;wire [1:0]PC_s;wire [15:0] imm;wire [31:0] imm_data ; wire [25:0] address;assign OP = codes[31:26]; assignfunc = codes[5:0]; assignimm = codes[15:0]; assign address=codes[25:0];OP_Decoderop_decoder( .OP(OP),//input.func(func),.ZF(ZF),//input.w_r_s(w_r_s),.imm_s(imm_s),.rt_imm_s(rt_imm_s),.wr_data_s(wr_data_s),.ALU_OP(ALU_OP),.Write_Reg(Write_Reg),.Mem_Write(Mem_Write), .PC_s(PC_s));wire[4:0] rs;wire[4:0] rt;wire[4:0] rd;assignrs = codes[25:21]; assignrt = codes[20:16]; assignrd = codes[15:11];wire[4:0] W_Addr;wire [31:0]W_Data;wire [31:0]ALU_B;assign W_Addr=(w_r_s[1])?5'b11111:((w_r_s[0])?rt:rd);assign W_Data=(wr_data_s[1])?PC_new:((wr_data_s[0])?M_R_Data:ALU_F); assign imm_data = (imm_s)?{{16{imm[15]}},imm}:{{16{1'b0}},imm}; assign ALU_B =(rt_imm_s)?imm_data:R_Data_B;always@(*)begincase(PC_s)2'b00:PC=PC_new;2'b01:PC=R_Data_A;2'b10:PC=PC_new+(imm_data<<2);2'b11:PC={PC_new[31:28],address,2'b00};default:PC=PC_new;endcaseendwire [31:0]R_Data_A;wire [31:0]R_Data_B;RegisterHeapregister(.R_Addr_A(rs),.R_Addr_B(rt),.W_Addr(W_Addr),.Write_Reg(Write_Reg),.Reset(rst),.Clk(clk),.W_Data(W_Data),.R_Data_A(R_Data_A),.R_Data_B(R_Data_B));wire [31:0]ALU_A;assign ALU_A = R_Data_A;ALU alu(.ALU_OP(ALU_OP),.A(ALU_A),.B(ALU_B),.F(ALU_F),.ZF(ZF),.OF(OF));Data_Memdata_mem (.clka(mem_clk), // input clka.wea(Mem_Write), // input [0 : 0] wea.addra(ALU_F[5:0]), // input [5 : 0] addra.dina(R_Data_B), // input [31 : 0] dina.douta(M_R_Data) // output [31 : 0] douta);Endmodule二、仿真波形三、电路图四、引脚配置:NET "LED[7]" LOC = "T11";NET "LED[6]" LOC = "R11";NET "LED[5]" LOC = "N11";NET "LED[4]" LOC = "M11";NET "LED[3]" LOC = "V15";NET "LED[2]" LOC = "U15";NET "LED[1]" LOC = "V16";NET "LED[0]" LOC = "U16";//LEDNET "inclk" LOC = "C9";NET "mem_clk" LOC = "V10";//100mHZNET "SW[3]" LOC = "M8";// 右边4个开关NET "SW[2]" LOC = "V9";NET "SW[1]" LOC = "T9";NET "SW[0]" LOC = "T10";NET "rst" LOC = "D9";五、思考与探索1,经过汇编器汇编即可产生程序的机器码。

以执行beq $t2,$zero,Loop2这条指令为例,offect字段值为0001H,此时PC为0000_0020,PC加上offect*4得0000_0024H,正好为Loop2的地址,所以计算的目标地址和转移目标地址一致。

2,这条指令与jal的区别在于增加了一个判断条件,可以将地址为rs值的正负进行判断,即根据指令的OP字段由译码及控制电路产生控制信号,该控制信号用于控制对R_Data_A正负的判断,若R_Data_A为负,则bltzal这条指令的后续执行与jal 相同。

由此便实现了该条指令。

3,其实编写实验八的过程也就是将前面所有的实验进行一次应用和巩固的过程。

当然了,在这个实验中同样涉及到了IP核的应用。