SPI接口的全称是"Serial Peripheral Interface",意为串行外围接口,是Motorola首先在其MC68HCXX系列处理器上定义的。SPI接口主要应用在EEPROM, FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

SPI接口是在CPU和外围低速器件之间进行同步串行数据传输,在主器件的移位脉冲下,数据按位传输,高位在前,地位在后,为全双工通信,数据传输速度总体来说比I2C总线要快,速度可达到几Mbps。

SPI接口是以主从方式工作的,这种模式通常有一个主器件和一个或多个从器件,其接口包括以下四种信号:

(1)MOSI –主器件数据输出,从器件数据输入

(2)MISO –主器件数据输入,从器件数据输出

(3)SCLK –时钟信号,由主器件产生

(4)/SS –从器件使能信号,由主器件控制

在点对点的通信中,SPI接口不需要进行寻址操作,且为全双工通信,显得简单高效。

在多个从器件的系统中,每个从器件需要独立的使能信号,硬件上比I2C

系统要稍微复杂一些。

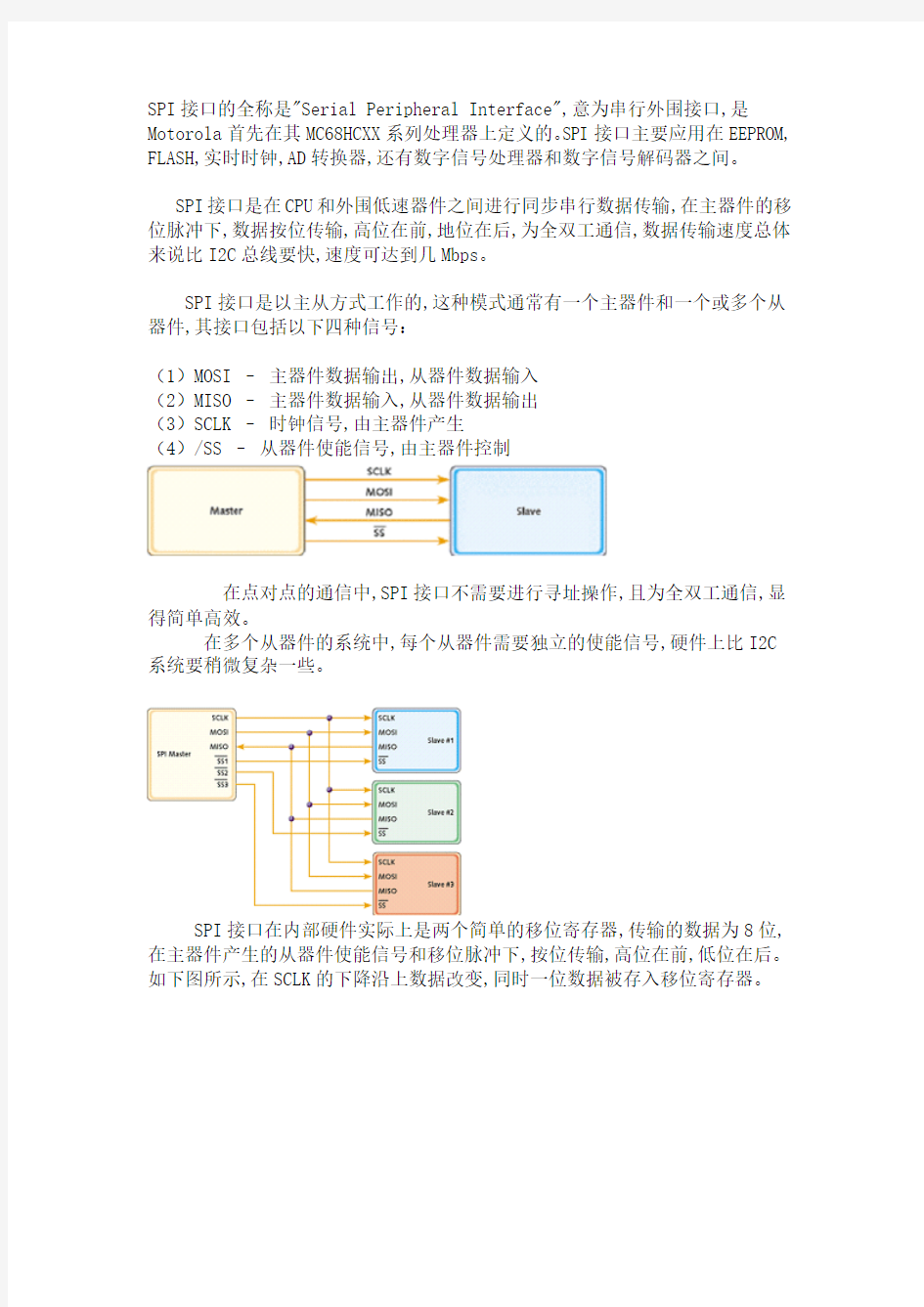

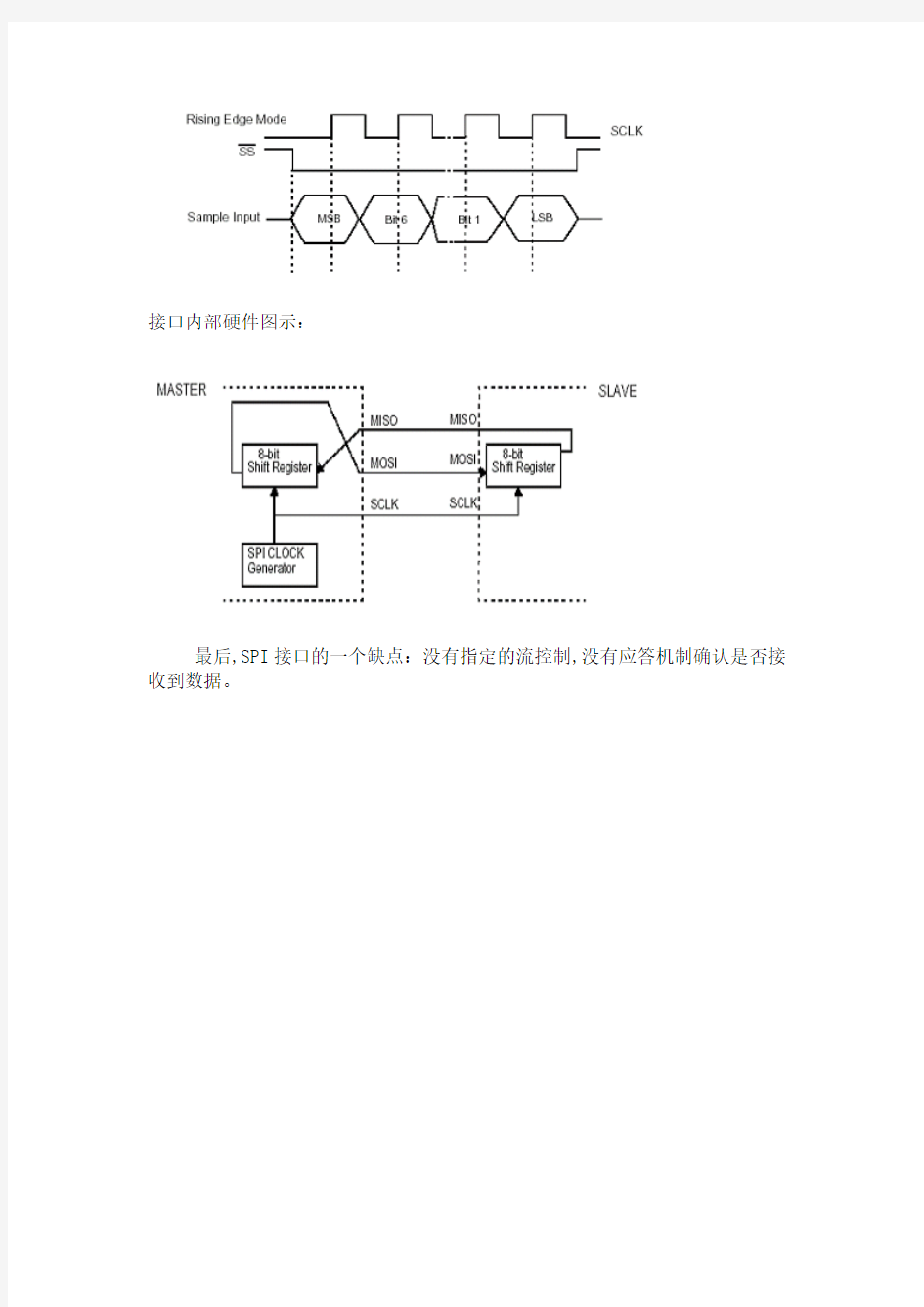

SPI接口在内部硬件实际上是两个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。如下图所示,在SCLK的下降沿上数据改变,同时一位数据被存入移位寄存器。

接口内部硬件图示:

最后,SPI接口的一个缺点:没有指定的流控制,没有应答机制确认是否接收到数据。

SPI接口设计与实现 SPI(SerialPeripheralInterface)总线是一种同步串行外设接口,它 可以使MCU与各种外围设备以串行方式进行通信以交换信息。SPI总线应用广泛,已经成为很多器件的标准配置,可以直接和各个厂家生产的 多种标准外围器件直接接口。其它常用的串行接口还有I2C、UART这 两种接口,这三种接口互有优缺点。与I2C接口相比,SPI接口速度更快、协议更简单、并且是全双工的,但连线也相对多一些。与UART接口相比,SPI更灵活,因为其使用主设备的时钟进行同步,所以两个比特之间 的时间间隔可以是任意的。在点对点的通信中,SPI接口不需要进行寻 址操作,且为全双工通信,显得简单高效。 1SPI总线工作原理 SPI总线一般以主/从模式工作,通常有一个主设备和一个或多个从设备,数据传输由主机控制,典型SPI结构框图如图1所示。SPI总线包含四条信号线,分别是sclk、miso、mosi和cs,其中,sclk为数据传输时钟,由主机产生;miso是从机输出,主机输入数据线;mosi是主机输出, 从机输入数据线;cs是从设备片选信号,由主机控制,当连接多个从设备时,通过该信号选择不同的从设备。SPI总线是按字节发送数据的,主机和从机内部都包含一个8位串行移位寄存器,在时钟信号控制下,寄存 器内的数据由高到低输出至各自的数据线,8个时钟后,两个寄存器内的数据就被交换了。如果只进行写操作,主机只需忽略接收到的字节;反之,若主机要读取从机的一个字节,就必须发送一个空字节来引发从机 的传输。当主机发送一个连续的数据流时,可以进行多字节传输,在这 种传输方式下,从机的片选端必须在整个传输过程中保持低电平。 根据串行同步时钟极性和相位不同,SPI有四种工作方式。时钟极性(CPOL)为0时,同步时钟的空闲状态为低电平,为1时,同步时钟的空闲 状态为高电平。时钟相位(CPHA)为0时,在同步时钟的第一个跳变沿采 样数据,为1时,在同步时钟的第二个跳变沿采样数据。因为主设备时

详解SPI总线规范 SPI是英文Serial Peripheral Interface的缩写,中文意思是串行外围设备接口,SPI是Motorola公司推出的一种同步串行通讯方式,是一种三线同步总线,因其硬件功能很强,与SPI有关的软件就相当简单,使CPU有更多的时间处理其他事务。 SPI概述 SPI:高速同步串行口。3~4线接口,收发独立、可同步进行. SPI,是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。是Motorola首先在其MC68HCX X系列处理器上定义的。SPI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议,比如AT91RM9200. SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。外围设置FLASH RAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT或INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。 SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)。 (1)SDO –主设备数据输出,从设备数据输入 (2)SDI –主设备数据输入,从设备数据输出 (3)SCLK –时钟信号,由主设备产生 (4)CS –从设备使能信号,由主设备控制 其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。这就允许在同一总线上连接多个SPI设备成为可能。 接下来就负责通讯的3根线了。通讯是通过数据交换完成的,这里先要知道SPI是串行通讯协议,也就是说数据是一位一位的传输的。这就是SCK时钟线存在的原因,由SCK提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。数据输出通过SDO线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。完成一位数据传输,输入也使用同样原理。这样,在至少8次时钟信号的改变(上沿和下沿为一次),就可以完成8位数据的传输。 要注意的是,SCK信号线只由主设备控制,从设备不能控制信号线。同样,在一个基于SPI的设备中,至少有一个主控设备。这样传输的特点:这样的传输方式有一个优点,与普通的串行通讯不同,普通的串行通讯一次连续传送至少8位数据,而SPI允许数据一位一位的传送,甚至允许暂停,因为SCK时钟线由主控设备控制,当没有时钟跳变时,从设备不采集或传送数据。也就是说,主设备通过对SCK时钟线的控制可以完成对通讯的控制。SPI还是一个数据交换协议:因为SPI的数据输入和输出线独立,所以允许同时完成数据的输入和输出。不同的SPI设备的实现方式不尽相同,主要是数据改变和采集的时间不同,在时钟信号上沿或下沿采集有不同定义,具体请参考相关器件的文档。

SPI:高速同步串行口。3~4线接口,收发独立、可同步进行 SPI的通信原理: 主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)。 (1)SDO –主设备数据输出,从设备数据输入 (2)SDI –主设备数据输入,从设备数据输出 (3)SCLK –时钟信号,由主设备产生 (4)CS –从设备使能信号,由主设备控制 其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。这就允许在同一总线上连接多个SPI设备成为可能。 接下来就负责通讯的3根线了。通讯是通过数据交换完成的,这里先要知道SPI是串行通讯协议,也就是说数据是一位一位的传输的。这就是SCK时钟线存在的原因,由SCK提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。数据输出通过SDO线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。完成一位数据传输,输入也使用同样原理。这样,在至少8次时钟信号的改变(上沿和下沿为一次),就可以完成8位数据的传输。 要注意的是,SCK信号线只由主设备控制,从设备不能控制信号线。同样,在一个基于SPI的设备中,至少有一个主控设备。这样传输的特点:这样的传输方式有一个优点,与普通的串行通讯不同,普通的串行通讯一次连续传送至少8位数据,而SPI允许数据一位一位的传送,甚至允许暂停,因为SCK时钟线由主控设备控制,当没有时钟跳变时,从设备不采集或传送数据。也就是说,主设备通过对SCK时钟线的控制可以完成对通讯的控制。SPI还是一个数据交换协议:因为SPI的数据输入和输出线独立,所以允许同时完成数据的输入和输出。不同的SPI设备的实现方式不尽相同,主要是数据改变和采集的时间不同,在时钟信号上沿或下沿采集有不同定义,具体请参考相关器件的文档。 在点对点的通信中,SPI接口不需要进行寻址操作,且为全双工通信,显得简单高效。在多个从设备的系统中,每个从设备需要独立的使能信号,硬件上比I2C系统要稍微复杂一些。 最后,SPI接口的一个缺点:没有指定的流控制,没有应答机制确认是否接收到数据。 SPI协议举例 SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。 假设下面的8位寄存器装的是待发送的数据10101010,上升沿发送、下降沿接收、高位先发送。 那么第一个上升沿来的时候数据将会是sdo=1;寄存器中的10101010左移一位,后面补入送来的一位未知数x,成了0101010x。下降沿到来的时候,sdi上的电平将锁存到寄存器中去,那么这时寄存器=0101010sdi,这样在8个时钟脉冲以后,两个寄存器的内容互相交换一次。这样就完成里一个spi时序。

基于CPLD 的SP I 接口设计 D esign i ng SP I I n terface ba sed on CPLD 何永泰 (楚雄师范学院 楚雄 675000) 【摘 要】 根据SP I 同步串行接口的通信协议,介绍了在X ilinx Coo lR unnct XPLA 3CPLD 中利用V HDL 语言实现SP I 接口的设计原理和编程思想,通过用此接口,使得那些没有SP I 接口功能的微处理器和微控制器,也能通过SP I 接口与外围设备进行数据交换。 【关键词】 SP I 接口,CPLD ,接口扩展,接口设计,串行接口 ABSTRACT A cco rding to comm un icati on p ro toco l of SP I synch ronou s serial in terface ,th is paper p resen ts the design theo ry and p rogramm ing idea of i m p lem en ting SP I in terface w ith V HDL language in X ilinx Coo lR unner XPLA 3CPLD .T h is in terface can be u sed to data exchange w ith peri pheral apparatu s fo r m icrop rocesso r and m icrocon tro ller w h ich have no t SP I in terface functi on .KEYWOR D S SP I in terface ,CPLD ,in terface expan si on ,in terface design ,serial in terface 1 SP I 总线接口协议 SP I (Seri on Perp heral In terface )总线接口是一个 全双工,同步串行数据接口。许多微处理器,微控制器和外部设备具有这个接口。它能够实现在微控制器之间或微控制器与外部设备之间通信。SP I 总线通常有4条线组成,即:串行时钟线(SCK )、主机输出从机输入 线(M O S I )、 主机输入从机输出线(M ISO )和从机选择线SS N 。SCK 靠主机和数据流来驱动。M O S I 数据线从主机输出数据作为从机的输入数据。M ISO 数据线传送从机输出的数据作为主机的输入数据。在大多数情况下,使用一个SP I 作为主机,它控制数据向1个或几个从机传送。主机驱动数据从它的SCK 和M O S I 端到各从机的SCK 和M O S I 端,被选择的从机驱动数据从它的M ISO 端到主机的M ISO 端。SS N 控制线用于从机选择控制。 SCK 的相位和极性能改变SP I 的数据格式,时钟极性CPOL =‘0’,串行数据的移位操作由时钟正脉冲触发,时钟极性CPOL =‘1’,串行数据的移位操作由负脉冲触发;时钟相位CPHA =‘0’, 串行数据的移位 图1 CPHA =‘0’时SP I 的数据转换时序图 操作由时钟脉冲前沿触发,时钟相位CPHA =‘1’,串行数据的移位操作由时钟脉冲后沿触发。时钟相位CPHA =‘0’时SP I 的数据转换时序图如图1所示。 在图1中SCK 信号在第一个SCK 周期中的前半周期无效,在这种模式中,SS 的下降沿示意数据传送的开始,因此,SS 在连续串行字节之间必须被取反和重新申明。时钟相位CPHA =‘1’时SP I 的数据转换时序图如图2所示。 在图2中SCK 信号从无效电平到有效电平的第一边沿意味着在这种模式下数据传送的开始,SS 信号能保持有效的低电平在连续串行字节之间,这种模式用于只有一个主机和一个从机的系统中。 在SP I 传送数据时,8位数据从一个SP I 接口移出时,另一个SP I 接口也开始移出8位数据,这样主机的8位移位寄存器和从机的8位移位寄存器可以被看作是16移位寄存器,16位移位寄存器移动8个位置就实现了在主机和从机之间交换数据。基于CPLD 的SP I 接口设计中,从SP I 总线上接收的数据被保存在一个接收寄存器中,发送的数据被写到一个发送寄存器中 。 图2 CPHA =‘1’时SP I 的数据转换时序图 3 20040414收到,20040724改回 33 何永泰,男,1970年生,讲师,在读硕士,研究方向:电子工程设计。 ? 72?第17卷 第10期 电脑开发与应用 (总497)

SPI 串行外设接口总线,最早由Motorola提出,出现在其M68系列单片机中,由于其简单实用,又不牵涉到专利问题,因此许多厂家的设备都支持该接口,广泛应用于外设控制领域。 SPI接口是一种事实标准,并没有标准协议,大部分厂家都是参照Motorola的SPI接口定义来设计的。但正因为没有确切的版本协议,不同家产品的SPI接口在技术上存在一定的差别,容易引起歧义,有的甚至无法直接互连(需要软件进行必要的修改)。 虽然SPI接口的内容非常简单,但本文仍将就其中的一些容易忽视的问题进行讨论。 SPI ( Serial Peripheral Interface ) SPI接口是Motorola 首先提出的全双工三线同步串行外围接口,采用主从模式(Master Slave)架构;支持多slave模式应用,一般仅支持单Master。 时钟由Master控制,在时钟移位脉冲下,数据按位传输,高位在前,低位在后(MSB first);SPI 接口有2根单向数据线,为全双工通信,目前应用中的数据速率可达几Mbps的水平。 SPI接口信号线 SPI接口共有4根信号线,分别是:设备选择线、时钟线、串行输出数据线、串行输入数据线。 设备选择线SS-(Slave select,或CS-)

SS-线用于选择激活某Slave设备,低有效,由Master驱动输出。只有当SS-信号线为低电平时,对应Slave设备的SPI接口才处于工作状态。 SCLK:同步时钟信号线, SCLK用来同步主从设备的数据传输,由Master驱动输出,Slave设备按SCK的步调接收或发送数据。 串行数据线: SPI接口数据线是单向的,共有两根数据线,分别承担Master到Slave、Slave到Master的数据传输;但是不同厂家的数据线命名有差别。 Motorola的经典命名是MOSI和MISO,这是站在信号线的角度来命名的。 MOSI:When master, out line; when slave, in line MISO:When master, in line; when slave, out line 比如MOSI,该线上数据一定是Master流向Slave的。因此在电路板上,Master的MOSI引脚应与Slave的MOSI引脚连接在一起。双方的MISO也应该连在一起,而不是一方的MOSI连接另一方的MISO。 不过,也有一些产家(比如Microchip)是按照类似SDI,SDO的方式来命名,这是站在器件的角度根据数据流向来定义的。 SDI:串行数据输入 SDO:串行数据输出 这种情况下,当Master与Slave连接时,就应该用一方的SDO连接另一个方的SDI。 由于SPI接口数据线是单向的,故电路设计时,数据线连接一定要正确,必然是一方的输出连接另一方的输入。 其实这个问题本来很简单的,但由于不同厂家产品的命名习惯可能不同,因此还需小心,以免低级出错。 数据传输的时序模式

SPI通信协议(SPI总线)学习 各位读友大家好!你有你的木棉,我有我的文章,为了你的木棉,应读我的文章!若为比翼双飞鸟,定是人间有情人!若读此篇优秀文,必成天上比翼鸟! SPI通信协议(SPI总线)学习1、什么是SPI?SPI是串行外设接口(Serial Peripheral Interface)的缩写。是Motorola 公司推出的一种同步串行接口技术,是一种高速的,全双工,同步的通信总线。2、SPI优点支持全双工通信通信简单数据传输速率块3、缺点没有指定的流控制,没有应答机制确认是否接收到数据,所以跟IIC总线协议比较在数据可靠性上有一定的缺陷。4、特点1):高速、同步、全双工、非差分、总线式2):主从机通信模式5、协议通信时序详解1):SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。也是所有基于SPI的设备共有的,它们是SDI(数据输入)、SDO(数据输出)、SCLK(时钟)、CS(片选)。(1)SDO/MOSI –主设备数据输出,从设备数据输入;(2)SDI/MISO –主设备数据输入,从设备数据输出;(3)SCLK –时钟信号,由主设备产生;(4)CS/SS –从设备使能信号,由主设备控制。当有多个从设备的时候,因为每个从设备上都有一个片选引脚接入到主设备机中,当我们的主设备和某个从设备通信时将需要将从设备对应的片选引脚电平拉低或者是拉高。2):需要说明的是,我们SPI通信有4种不同的模式,不

同的从设备可能在出厂是就是配置为某种模式,这是不能改变的;但我们的通信双方必须是工作在同一模式下,所以我们可以对我们的主设备的SPI模式进行配置,通过CPOL(时钟极性)和CPHA(时钟相位)来控制我们主设备的通信模式,具体如下:Mode0:CPOL=0,CPHA=0Mode1:CPOL=0,CPHA=1Mode2:CPOL=1,CPHA=0Mode3:CPOL=1,CPHA=1时钟极性CPOL 是用来配置SCLK的电平出于哪种状态时是空闲态或者有效态,时钟相位CPHA是用来配置数据采样是在第几个边沿:CPOL=0,表示当SCLK=0时处于空闲态,所以有效状态就是SCLK处于高电平时CPOL=1,表示当SCLK=1时处于空闲态,所以有效状态就是SCLK处于低电平时CPHA=0,表示数据采样是在第1个边沿,数据发送在第2个边沿CPHA=1,表示数据采样是在第2个边沿,数据发送在第1个边沿例如:CPOL=0,CPHA=0:此时空闲态时,SCLK处于低电平,数据采样是在第1个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在上升沿,数据发送是在下降沿。CPOL=0,CPHA=1:此时空闲态时,SCLK 处于低电平,数据发送是在第1个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿。CPOL=1,CPHA=0:此时空闲态时,SCLK处于高电平,数据采集是在第1个边沿,也就是SCLK由高电平到低电平的跳变,所以数据采集是在下降沿,数据发送是在上升沿。CPOL=1,CPHA=1:此时空闲态时,SCLK处于高电平,数据发送是在第

SPI 接口的设计 第二章介绍了模数转换器的可编程控制架构,其中可编程控制功能的实现需要分成两部分:一部分为SPI 接口电路,以及其根据部寄存器存储的数据产生的控制信号;另一部分是具体的电路受控模块。本章将介绍接口与数字逻辑电路的设计,包括应用于本模数转换器的SPI 接口与数字逻辑电路的设计、综合以及仿真验证。 3.1 数据通信接口 3.1.1 串行通信 基本的通信方式有两种:并行通信和串行通信。并行通信是指数据以成组的方式,在多条并行信道上同时进行传输。 串行通信指要传送的数据或信息按一定的格式编码,然后在单根线上,按位的先后顺序进行传送。接收数据时,每次从单根线上按位接收信息,再把它们拼成一个字符,送给CPU (Central Processing Unit )做进一步的处理。收发双方必须保持字符同步,以使接收方能从接收的数据比特流中正确区分出与发送方相同的一个一个字符。串行通信只需要一条传输信道,易于实现,是目前主要采用的一种通信方式,它具有通信线少以及传送距离远等优点。 串行通信时,按数据的传送的方向可以分为单工、半双工和全双工等三种方式。 (1)单工(Simplex ):数据线仅能向一个方向传输数据,两个设备进行通信时,一边只能发送数据,另一边只能接收数据。 (2)半双工(Half Duplex ):数据可在两个设备间向任一个方向传输,但因为只有一根传输线,故同一时间只能向一个方向传输数据,不能同时收发。 (3)全双工(Full Duplex ):对数据的两个传输方向采用不同的通路,可以同时发送和接收数据, 串行通信有两种基本工作方式:异步方式和同步方式。采用异步方式(Asynchronous )时,数据发送的格式如图3-1所示。不发送数据时,数据信号线呈现高电平,处于空闲状态。当有数据要发送时,数据信号线变成低电平,并持续一位的时间,用于表示字符的开始,称为起始位。起始位之后,在信号线上依次出现待发送的每一位字符数据,最低有效位0D 最先出现。采用不同的编码方案,待发送的每个字符的位数就不同。当字符用ASCII 码表示时,数据位占7位(60~D D )。在数据位的后面有一个奇偶校验位,其后有停止位,用于指示字符的结束。停止位可以是一位也可以是一位半或两位。可见,用异步方式发送一个7位的ASCII 码字符时,实际需发送10位、10.5位或11位信息。如

二、通信的SPI 概念 2.1、SPI:高速同步串行口 SPI:高速同步串行口。是一种标准的四线同步双向串行总线。 SPI,是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。是Motorola首先在其MC68HCXX系列处理器上定义的。SPI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议,比如AT91RM9200. SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。 SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(用于单向传输时,也就是半双工方式)。也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)。 (1)SDO –主设备数据输出,从设备数据输入 (2)SDI –主设备数据输入,从设备数据输出 (3)SCLK –时钟信号,由主设备产生 (4)CS –从设备使能信号,由主设备控制 其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。这就允许在同一总线上连接多个SPI设备成为可能。 接下来就负责通讯的3根线了。通讯是通过数据交换完成的,这里先要知道SPI是串行通讯协议,也就是说数据是一位一位的传输的。这就是SCK时钟线存在的原因,由SCK 提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。数据输出通过SDO线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。完成一位数据传输,输入也使用同样原理。这样,在至少8次时钟信号的改变(上沿和下沿为一次),就可以完成8位数据的传输。 要注意的是,SCK信号线只由主设备控制,从设备不能控制信号线。同样,在一个基于SPI的设备中,至少有一个主控设备。这样传输的特点:这样的传输方式有一个优点,与普通的串行通讯不同,普通的串行通讯一次连续传送至少8位数据,而SPI允许数据一位一位的传送,甚至允许暂停,因为SCK时钟线由主控设备控制,当没有时钟跳变时,从

竭诚为您提供优质文档/双击可除 spi协议实例 篇一:spi协议 一spi协议概括 spi,是英语serialperipheralinterface的缩写,顾名思义就是串行外围设备接口。是motorola首先在其 mc68hcxx系列处理器上定义的。spi接口主要应用在eepRom,Flash,实时时钟,ad转换器,还有数字信号处理器和数字信号解码器之间。spi,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为pcb的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议,比如at91Rm9200. spi的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。也是所有基于spi的设备共有的,它们是sdi(数据输入),sdo(数据输出),sck (时钟),cs(片选)。 (1)sdo–主设备数据输出,从设备数据输入

(2)sdi–主设备数据输入,从设备数据输出 (3)sclk–时钟信号,由主设备产生 (4)cs–从设备使能信号,由主设备控制 其中cs是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。这就允许在同一总线上连接多个spi设备成为可能。 接下来就负责通讯的3根线了。通讯是通过数据交换完成的,这里先要知道spi是串行通讯协议,也就是说数据是一位一位的传输的。这就是sck时钟线存在的原因,由sck 提供时钟脉冲,sdi,sdo则基于此脉冲完成数据传输。数据输出通过sdo线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。完成一位数据传输,输入也使用同样原理。这样,在至少8次时钟信号的改变(上沿和下沿为一次),就可以完成8位数据的传输。 要注意的是,sck信号线只由主设备控制,从设备不能控制信号线。同样,在一个基于spi的设备中,至少有一个主控设备。这样传输的特点:这样的传输方式有一个优点,与普通的串行通讯不同,普通的串行通讯一次连续传送至少8位数据,而spi允许数据一位一位的传送,甚至允许暂停,因为sck时钟线由主控设备控制,当没有时钟跳变时,从设备不采集或传送数据。也就是说,主设备通过对sck时钟线

SPI 串行通信接口是一种常用的标准接口,由于其使用 简单方便且节省系统资源,很多芯片都支持该接口,应用相当广泛[1]。但是现有文献和设计多数仅实现了SPI 接口的基本发送和接收功能,对SPI 接口的时序控制没有进行深入的研究。全功能SPI 接口应具有四种不同的时钟模式,以适应具有不同时序要求的从控制器。文中主要研究SPI 接口的时钟时序,并用具体电路实现具有4种不同极性和相位的时钟,最后通过仿真验证和FPGA 验证[2]。 1SPI 控制器典型结构 SPI 模块中的典型结构是用于通信的主从2个控制器之 间的连接,如图1所示。由串行时钟线(SPICLK )、主机输入从机输出线(SPISOMI )、主机输出从机输入线(SPISIMO )、SPI 选通线(SPISTE )4条线组成[3]。当CPU 通过译码向主控制器写入要传输的数据时,主控制器通过串行时钟线来启动数据传输,将会在串行时钟线的一个边沿将数据移出移位寄存器,而在串行时钟的另一个边沿将数据锁存在移位寄存器中。 SPI 选通线是SPI 控制器的使能端,可以选择多个从机,实现 一主多从的结构,只要SPI 选通信号将要选的从机处的选通信号变为低电平就能够连接成功。 2 全功能SPI 控制器设计 2.1 SPI 控制器内部结构 SPI 控制器的原理框图如图2所示,其中主要包括:1)SPI 控制器的内部寄存器 SPI 操作控制寄存器(SPICTL ),SPI 状态寄存器(SPISTS ), SPI 波特率设计寄存器(SPIBRR ),SPI 接收缓冲寄存器 图1 SPI 主从连接Fig.1 Master -slave link 全功能SPI 接口的设计与实现 辛晓宁,孙文强 (沈阳工业大学研究生学院,辽宁沈阳110870) 摘要:SPI (Serial Peripheral Interface ,串行外围接口)是Motorola 公司提出的外围接口协议,它采用一个串行、同步、全双工的通信方式,解决了微处理器和外设之间的串行通信问题,并且可以和多个外设直接通信,具有配置灵活,结构简单等优点。根据全功能SPI 总线的特点,设计的SPI 接口可以最大发送和接收16位数据;在主模式和从模式下SPI 模块的时钟频率最大可以达到系统时钟的1/4,并且在主模式下可以提供具有四种不同相位和极性的时钟供从模块选择;可以同时进行发送和接收操作,拥有中断标志位和溢出中断标志位。关键词:全功能SPI ;时钟极性和相位;串行通信;微处理器;中断控制中图分类号:TP332.3 文献标识码:A 文章编号:1674-6236(2012)23-0153-04 Design and implementation of full featured SPI master interface XIN Xiao -ning ,SUN Wen -qiang (Graduate School ,Shenyang University of Technology ,Shenyang 110870,China ) Abstract:The SPI put forward by Motorola Company is a full-duplex ,synchronous serial date link that is standard across many microprocessors ,microcontrollers ,and peripherals It enables communication between microprocessors and peripherals and inter -processor communication ,The SPI system is flexible enough to interface directly with numerous commercially available peripherals ,and it also has some excellences such as it can be configured flexibly and it has a simply structure ,and so on.This SPI has 16-bit transmit and receive capability.The maximum transmission rate in both slave mode and master mode is now CLKOUT/4.The SPI can provide four different clocking schemes on the SPICLK pin.It can be sending and receiving at same time.It has SPI interrupt flag and TXBUF full flag. Key words:full function of SPI ;polarity and phase of CLK ;serial communication microprocessor ;interrupt control 收稿日期:2012-08-11 稿件编号:201208039 作者简介:辛晓宁(1965—),男,辽宁沈阳人,博士,教授。研究方向:SOC 集成电路设计。 电子设计工程 Electronic Design Engineering 第20卷Vol.20第23期No.23 2012年12月Dec.2012 -153-

SPI通信协议(SPI总线)学习 1、什么是SPI? SPI是串行外设接口(Serial Peripheral Interface)的缩写。是Motorola 公司推出的一 种同步串行接口技术,是一种高速的,全双工,同步的通信总线。 2、SPI优点 支持全双工通信 通信简单 数据传输速率块 3、缺点 没有指定的流控制,没有应答机制确认是否接收到数据,所以跟IIC总线协议比较在数据可靠性上有一定的缺陷。 4、特点 1):高速、同步、全双工、非差分、总线式 2):主从机通信模式 5、协议通信时序详解 1):SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。也是所有基于SPI的设备共有的,它们是SDI(数据输入)、SDO(数据输出)、SCLK(时钟)、CS(片选)。 (1)SDO/MOSI – 主设备数据输出,从设备数据输入; (2)SDI/MISO – 主设备数据输入,从设备数据输出; (3)SCLK – 时钟信号,由主设备产生; (4)CS/SS – 从设备使能信号,由主设备控制。当有多个从设备的时候,因为每个从设 备上都有一个片选引脚接入到主设备机中,当我们的主设备和某个从设备通信时将需 要将从设备对应的片选引脚电平拉低或者是拉高。 2):需要说明的是,我们SPI通信有4种不同的模式,不同的从设备可能在出厂是就是配置为某种模式,这是不能改变的;但我们的通信双方必须是工作在同一模式下,所以我们可以对我们的主设备的SPI模式进行配置,通过CPOL(时钟极性)和CPHA(时钟相位)来控制我们主设备的通信模式,具体如下: Mode0:CPOL=0,CPHA=0 Mode1:CPOL=0,CPHA=1 Mode2:CPOL=1,CPHA=0 Mode3:CPOL=1,CPHA=1 时钟极性CPOL是用来配置SCLK的电平出于哪种状态时是空闲态或者有效态,时钟相位CPHA 是用来配置数据采样是在第几个边沿: CPOL=0,表示当SCLK=0时处于空闲态,所以有效状态就是SCLK处于高电平时 CPOL=1,表示当SCLK=1时处于空闲态,所以有效状态就是SCLK处于低电平时 CPHA=0,表示数据采样是在第1个边沿,数据发送在第2个边沿 CPHA=1,表示数据采样是在第2个边沿,数据发送在第1个边沿 例如: CPOL=0,CPHA=0:此时空闲态时,SCLK处于低电平,数据采样是在第1个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在上升沿,数据发送是在下降沿。

SPI串口通信协议 1.1 SPI串口通信介绍 SPI是英文Serial Peripheral Interface的缩写,中文意思是串行外围设备接口,SPI是Motorola公司推出的一种同步串行通讯方式,是一种三线同步总线,因其硬件功能很强,与SPI有关的软件就相当简单,使CPU有更多的时间处理其他事务。 SPI:高速同步串行口。3~4线接口,收发独立、可同步进行. SPI,是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。是Motorola首先在其MC68HCXX系列处理器上定义的。SPI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议,比如AT91RM9200. SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT或INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。 SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)。 (1)SDO –主设备数据输出,从设备数据输入 (2)SDI –主设备数据输入,从设备数据输出

SPI接口的优缺点及通信原理 SPI是串行外设接口(Serial Peripheral Interface)的缩写。是一种同步串行接口技术,是高速的,全双工,同步的通信总线。下面就有iBeacon、蓝牙模块厂家-云里物里科技来帮大家讲解下SPI接口的优缺点。 1、SPI接口的优点 支持全双工操作; 操作简单; 数据传输速率较高。 同时,它也具有如下缺点: 需要占用主机较多的口线(每个从机都需要一根片选线); 只支持单个主机; 没有指定的流控制,没有应答机制确认是否接收到数据。 2、SPI通信原理 SPI的通信原理是以主从方式工作,这种模式通常有一个主设备和一个或多个从设备。SPI接口经常被称为4线串行总线,分别是SDI(数据输入)、SDO(数据输出)、SCLK(时钟)、CS(片选)。 (a)SDO/MOSI–主设备数据输出,从设备数据输入; (b)SDI/MISO–主设备数据输入,从设备数据输出; (c)SCLK–时钟信号,由主设备产生; (d)CS/SS–从设备使能信号,由主设备控制。 在SPI总线上,某一时刻可以出现多个从设备,但只能存在一个主设备,主设备通过片选线来确定要通信的从设备。这就要求从设备的MISO口具有三态特性,使得该口线在设备未被选通时表现为高阻抗。

3、数据传输 在一个SPI时钟周期内,会完成如下操作: 1)主设备通过MOSI线发送1位数据,从设备通过该线读取这1位数据; 2)从设备通过MISO线发送1位数据,主设备通过该线读取这1位数据。 这是通过移位寄存器来实现的。如图所示,主设备和从设备各有一个移位寄存器,且二者连接成环。随着时钟脉冲,数据按照从高位到低位的方式依次移出主设备寄存器和从机寄存器,并且依次移入从设备寄存器和主设备寄存器。当寄存器中的内容全部移出时,相当于完成了两个寄存器内容的交换。 4、内部工作机制 SSPSR是SPI设备内部的移位寄存器(Shift Register).它的主要作用是根据SPI时钟信号状态,往SSPBUF里移入或者移出数据,每次移动的数据大小 由Bus-Width以及Channel-Width所决定。

基于FPGA的SPI接口设计 SPI是一种在FPGA和其他芯片之间传输数据的简单有效的接口方式。 SPI项目 第一部分:什么是SPI 第二部分:SPI的简单实现 第三部分:应用 第一部分:什么是SPI SPI是允许一个器件同其他一个或多个器件进行通讯的简单接口。 SPI是什么样的? 首先让我们来看看两个芯片之间的SPI接口是如何连接的。 在两个芯片时间通讯时,SPI需要4条连线。 正如你所看到的,他们是SCK、MISO、MOSI以及SSEL。其中一个芯片叫做主控芯片,另一个叫从芯片。 SPI基础 基本特点: 1.同步 2.串行 3.全双工 4.非即插即用 5.一主多从 更多细节: 1.同步时钟有主控芯片产生,每个时钟传输一位数据 2.数据在传输前,首先许要进行并转串,才能用一条线传输 3.两条数据线,一条输入、一条输出 4.主从双方有关于SPI传输的先验知识,如比特顺序、数据长度等 5.数据传输有主控芯片发起,每次只与一个从芯片通讯 SPI是一种同步全双工的通讯接口,每个时钟在两条数据线上各传输一比特数据。 简单的传输 假设在主从芯片之间进行的是8位长度的,高位数据在前的SPI传输,则单个字节的传输在波形上看起来是这样的。 MOSI是主输出线,而MISO则是从输出线。由于SPI是全双工的,所以在时钟沿上两条线同时传输数据。MOSI将数据从主控芯片传输至从芯片,MISO则将从芯片的数据传输到主控芯片。 详细的说是这样的: 1,首先主控芯片使能相应的SSEL信号,通知相应的从芯片数据传输要开始了; 2,主控芯片产生8个SPI时钟周期,并将数据在每个时钟沿发送出去,同时从芯片在也每个时钟沿将数据发送到MISO线上。 3,主控芯片撤销SSEL信号,一次SPI传输结束 多个从芯片的情况

三、SPI是英文Serial Peripheral Interface的缩写,中文意思是串行外围设备接口,SPI是Motorola公司推出的一种同步串行通讯方式,是一种三线同步总线,因其硬件功能很强,与SPI有关的软件就相当简单,使CPU有更多的时间处理其他事务。 SPI概述 SPI:高速同步串行口。3~4线接口,收发独立、可同步进行. SPI,是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。是Motorola首先在其MC68HCXX系列处理器上定义的。SPI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB 的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议,比如AT91RM9200. SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI 和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT或INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。 SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)。 (1)SDO –主设备数据输出,从设备数据输入 (2)SDI –主设备数据输入,从设备数据输出 (3)SCLK –时钟信号,由主设备产生 (4)CS –从设备使能信号,由主设备控制 其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。这就允许在同一总线上连接多个SPI设备成为可能。 接下来就负责通讯的3根线了。通讯是通过数据交换完成的,这里先要知道SPI是串行通讯协议,也就是说数据是一位一位的传输的。这就是SCK时钟线存在的原因,由SCK提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。数据输出通过SDO 线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。完成一位数据传输,输入也使用同样原理。这样,在至少8次时钟信号的改变(上沿和下沿为一次),就可以完成8位数据的传输。 要注意的是,SCK信号线只由主设备控制,从设备不能控制信号线。同样,在一个基于SPI的设备中,至少有一个主控设备。这样传输的特点:这样的传输方式有一个优点,与普通的串行通讯不同,普通的串行通讯一次连续传送至少8位数据,而SPI允许数据一位一位的传送,甚至允许暂停,因为SCK时钟线由主控设备控制,当没有时钟跳变时,从设备不采集或传送数据。也就是说,主设备通过对SCK时钟线的控制可以完成对通讯的控制。SPI还是一个数据交换协议:因为SPI的数据输入和输出线独立,所以允许同时完成数据的输入和输出。不同的SPI设备的实现方式不尽相同,主要是数据改变和采集的时间不同,在时钟信号上沿或下沿采集有不同定义,具体请参考相关器件的文档。 在点对点的通信中,SPI接口不需要进行寻址操作,且为全双工通信,显得简单高效。在多个从设备的系统中,每个从设备需要独立的使能信号,硬件上比I2C系统要稍微复杂一些。 最后,SPI接口的一个缺点:没有指定的流控制,没有应答机制确认是否接收到数据。 AT91RM9200的SPI接口主要由4个引脚构成:SPICLK、MOSI、MISO及/SS,其中SPICLK是整个SPI总线的公用时钟,MOSI、MISO作为主机,从机的输入输出的标志,MOSI是主机的输出,从机的输入,MISO 是主机的输入,从机的输出。/SS是从机的标志管脚,在互相通信的两个SPI总线的器件,/SS管脚的电平低的是从机,相反/SS管脚的电平高的是主机。在一个SPI通信系统中,必须有主机。SPI总线可以配置成单主单从,单主多从,互为主从。 SPI的片选可以扩充选择16个外设,这时PCS输出=NPCS,说NPCS0~3接4-16译码器,这个译码器是需要外接4-16译码器,译码器的输入为NPCS0~3,输出用于16个外设的选择。 [编辑本段] SPI协议举例