过零比较和锁相环相位比较器电路原理图如图

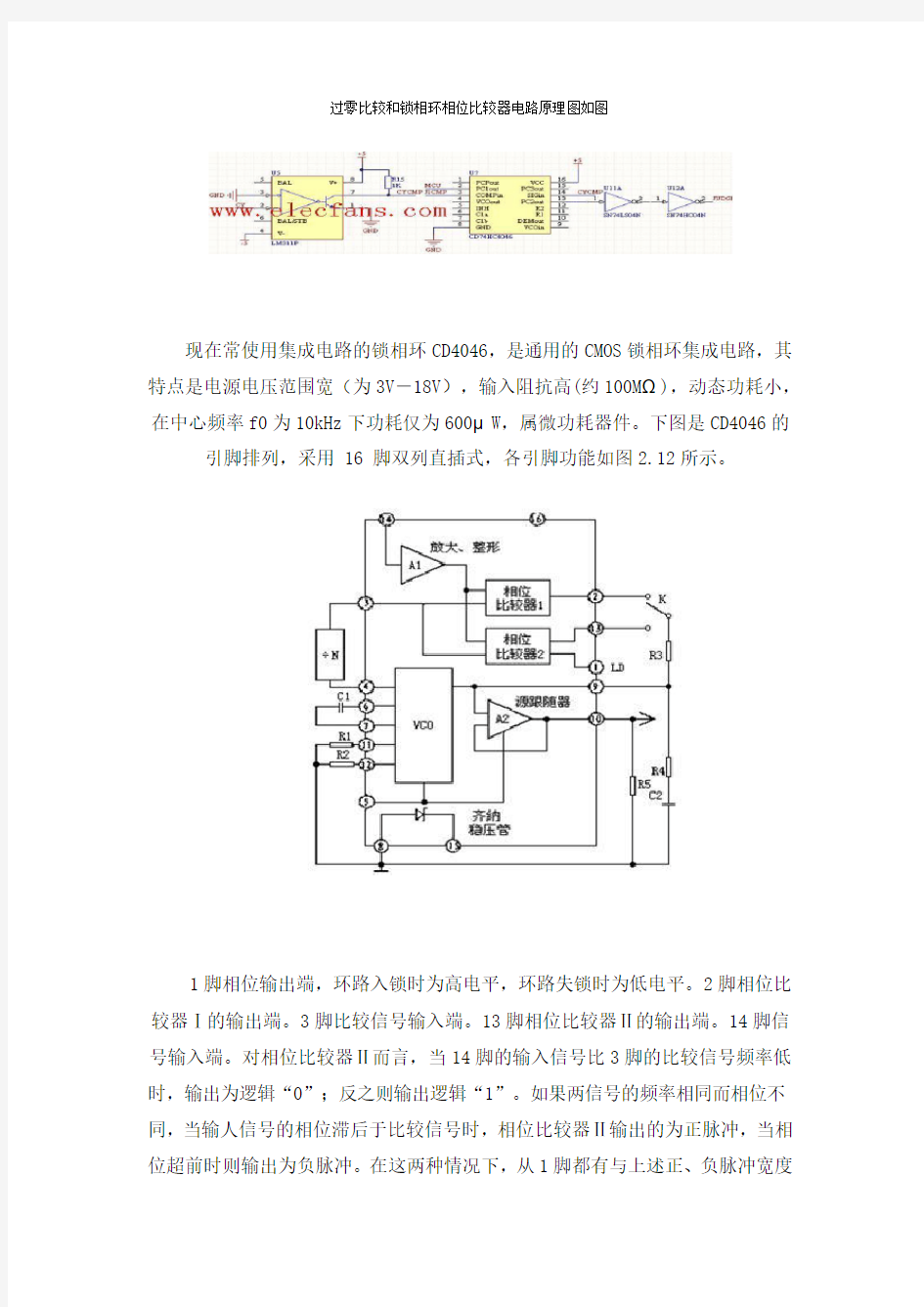

现在常使用集成电路的锁相环CD4046,是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。下图是CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如图2.12所示。

1脚相位输出端,环路入锁时为高电平,环路失锁时为低电平。2脚相位比较器Ⅰ的输出端。3脚比较信号输入端。13脚相位比较器Ⅱ的输出端。14脚信号输入端。对相位比较器Ⅱ而言,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑“0”;反之则输出逻辑“1”。如果两信号的频率相同而相位不同,当输人信号的相位滞后于比较信号时,相位比较器Ⅱ输出的为正脉冲,当相位超前时则输出为负脉冲。在这两种情况下,从1脚都有与上述正、负脉冲宽度

相同的负脉冲产生。从相位比较器Ⅱ输出的正、负脉冲的宽度均等于两个输入脉冲上升沿之间的相位差。而当两个输入脉冲的频率和相位均相同时,相位比较器Ⅱ的输出为高阻态,则1脚输出高电平。上述波形如图2.13所示。由此可见,从1脚输出信号是负脉冲还是固定高电平就可以判断两个输入信号的情况了。

图2.13 比较器输出波形图

电压比较器可以看作是放大倍数接近“无穷大”的运算放大器。

电压比较器的功能:比较两个电压的大小(用输出电压的高或低电平,表示两个输入电压的大小关系):当”+”输入端电压高于”-”输入端时,电压比较器输出为高电平;

当”+”输入端电压低于”-”输入端时,电压比较器输出为低电平;

电压比较器的作用:它可用作模拟电路和数字电路的接口,还可以用作波形产生和变换电路等。利用简单电压比较器可将正弦波变为同频率的方波或矩形波。

简单的电压比较器结构简单,灵敏度高,但是抗干扰能力差,因此我们就要对它进行改进。改进后的电压比较器有:滞回比较器和窗口比较器。

运放,是通过反馈回路和输入回路的确定“运算参数”,比如放大倍数,反馈量可以是输出的电流或电压的部分或全部。而比较器则不需要反馈,直接比较两个输入端的量,如果同相输入大于反相,则输出高电平,否则输出低电平。电压比较器输入是线性量,而输出是开关(高低电平)量。一般应用中,有时也可以用线性运算放大器,在不加负反馈的情况下,构成电压比较器来使用。

可用作电压比较器的芯片:所有的运算放大器。常见的有LM324 LM358 uA741 TL081\2\3\4 OP07 OP27,这些都可以做成电压比较器(不加负反馈)。LM339、LM393是专业的电压比较器,切换速度快,延迟时间小,可用在专门的电压比较场合,其实它们也是一种运算放大器。

关于比较器滞回的讨论需要从“滞回”的定义开始, 与许多其它技术术语一样, “滞回”源于希腊语, 含义是“延迟”或“滞后”, 或阻碍前一状态的变化。工程中, 常用滞回描述非对称操作, 比如, 从A到B和从B 到A是互不相同。在磁现象、非可塑性形变以及比较器电路中都存在滞回。

绝大多数比较器中都设计带有滞回电路, 通常滞回电压为5mV到10mV。内部滞回电路可以避免由于输入端的寄生反馈所造成的比较器输出振荡。但是内部滞回电路虽然可以使比较器免于自激振荡, 却很容易被外部振幅较大的噪声淹没。这种情况下需要增加外部滞回, 以提高系统的抗干扰性能。

首先, 看一下比较器的传输特性。图1所示是内部没有滞回电路的理想比较器的传输特性, 图2所示为实际比较器的传输特性。从图2可以看出, 实际电压比较器的输出是在输入电压(VIN)增大到2mV时才开始改变。

图1. 理想比较器的传输特性

图2. 实际比较器的传输特性

运算放大器在开环状态下可以用作比较器, 但是一旦输入信号中有少量的噪声或干扰, 都将会在两个不同的输出状态之间产生不期望的频繁跳变(图3)。用带有内部滞回电路的比较器代替开环运算放大器能够抑制输出的频繁跳变和振荡。或在比较器的正反馈电路中增加外部滞回电路, 正反馈的作用是确保输出在一个状态到另一个状态之间快速变化, 使比较器的输出的模糊状态时间达到可以忽略的水平, 如果在正反馈中加入滞回电路可减缓这种频繁跳变。

图3. 无滞回电路时比较器输出的模糊状态和频繁跳变

举个例子, 考虑图4所示简单电路, 其传输特性如图5所示。比较器的反相输入电压从0开始线性变化, 由分压电阻R1、R2构成正反馈。当输入电压从1点开始增加(图6), 在输入电压超过同相阈值VTH+ = VCCR2/(R1 + R2)之前, 输出将一直保持为VCC。在阈值点, 输出电压迅速从VCC跳变为VSS, 因为, 此时反相端输入电压大于同相端的输入电压。输出保持为低电平, 直到输入经过新的阈值点5 , VTH- = VSSR2/(R1 + R2)。在5点, 输出电压迅速跳变回VCC, 因为这时同相输入电压高于反相输入电压。

图4. 具有滞回的简单电路

图5. 图4电路的传输特性

图6. 图4电路的输入/输出电压波形

图4所示电路中的输出电压VOUT与输入电压VIN的对应关系表明, 输入电压至少变化2VTH时, 输出电压才会变化。因此, 它不同于图3的响应情况(放大器无滞回), 即对任何小于2VTH的噪声或干扰都不会导致输出的迅速变化。在实际应用中, 正、负电压的阈值可以通过选择适合的反馈网络设置。

其它设置可以通过增加不同阈值电压的滞回电路获得。图7电路使用了两个MOSFET和一个电阻网络调节正负极性的阈值。与图4所示比较器不同, 电阻反馈网络没有加载到负载环路, 图8给出了输入信号变化时的输出响应。

图7. 通过外部MOSFET和电阻构成滞回电路

图8. 图7电路的输入/输出电压波形

比较器内部的输出配置不同, 所要求的外部滞回电路也不同。例如, 具有内部上拉电阻的比较器, 可以在输出端和同相输入端直接加入正反馈电阻。输入分压网络作用在比较器的同相输入端, 反相输入电压为一固定的参考电平(如图9)。

图9. 在带有上拉电阻的比较器中加滞回电路

如上所述, 具有内部滞回的比较器提供两个门限:一个用于检测输入上升电压(VTHR),一个用于检测输入下降电压(VTHF), 对应于图8的VTH1和VTH2。两个门限的差值为滞回带(VHB)。当比较器的输入电压相等时, 滞回电路会使一个输入迅速跨越另一输入, 从而使比较器避开产生振荡的区域。图10所示为比较器反相输入端电压固定, 同相输入端电压变化时的工作过程, 交换两个输入可以得到相似波形, 但是输出电压极性相反。

图10. 图9电路的输入/输出电压波形

根据输出电压的两个极限值(两个电源摆幅), 可以很容易地计算反馈分压网络的电阻值。

内部有4mV滞回和输出端配有上拉电阻的比较器-- 如Maxim公司的MAX9015、MAX9017和MAX9019等。这些比较器设计用于电压摆幅为VCC和0V的单电源系统。可以按照以下步骤, 根据给定的电源电压、电压滞回(VHB)和基准电压(VREF), 选择并计算需要的元件:

第1步

选择R3, 在触发点流经R3的电流为(VREF - VOUT)/R3。考虑到输出的两种可能状态, R3由如下两式求得:

R3 = VREF/IR3和R3 = (VCC - VREF)/IR3.

取计算结果中的较小阻值, 例如, VCC = 5V, IR3 = 0.2μA, 使用MAX9117比较器(VREF = 1.24V), 则计算结果为6.2M和19M, 选则R3为6.2M。

第2步选择滞回电压(VHB)。在本例中, 选择滞回电压为50mV。

第3步R1可按下式计算。

对于这个例子, R1的值为:

第4步

输入VIN上升门限(VTHR)的选择, 例如:

在该门限点, 当输入电压VIN超过阈值时, 比较器输出由低电平变到高电平。本例中, 选择VTHR = 3V。

第5步

计算R2, R2可按下式计算:

本例中, R2的标准值为44.2k。

第6步

按如下步骤验证电压和滞回电压:VIN上升门限= 2.992V, 等于VREF乘以R1, 除以R1、R2和R3并联后的阻值。

VIN下降门限= 2.942V。

因此, 滞回电压= VTHR - VTHF = 50mV.

最后, 开漏结构的比较器内部滞回电压为4mV (MAX9016、MAX9018、MAX9020), 需要外接上拉电阻, 如图11所示。外加滞回可以通过正反馈产生, 但是计算公式与上拉输出的情况稍有不同。

图11. 在输出为开漏结构的比较器中加滞回电路

按如下步骤计算电阻值:

第1步

选择R3, 在IN_+端的漏电流小于2nA, 所以通过R3的电流至少为0.2μA, 以减小漏电流引起的误差。R3可由R3 = VREF/IR3或R3 = [(VCC - VREF)/IR3] - R4两式求得, 取其较小值。例如, 使用MAX9118 (VREF=1.24V), VCC = 5V, IR3 = 0.2μA, R4 = 1M, 计算结果为6.2M和18M, 则R3选6.2M。

第2步

选择需要的滞回电压(VHB)。

第3步

选择R1, R1可按下式计算:

在此例中, R1为:

第4步

选择VIN上升门限(VTHR), 如下式:

在该门限点, 当输入电压VIN超过阈值时, 比较器输出由低电平变到高电平。本例中, 选择VTHR = 3V。

第5步

计算R2, 如下式:

本例中, R2的标准值为49.9k。

第6步

按如下步骤验证触发电压和滞回电压:

单限比较器电路

图1b为其传输特性。

图3为某仪器中过热检测保护电路。它用单电源供电,1/4LM339的

反相输入端加一个固定的参考电压,它的值取决于R1于R2。U R=R2/(R1+R2)*U CC。同相端的电压就等于热敏元件Rt的电压降。当机内温度为设定值以下时,“+”端电压大于“-”端电压,Uo为高电位。当温度上升为设定值以上时,“-”端电压大于“+”端,比较器反转,Uo输出为零电位,使保护电路动作,调节R1的值可以改变门限电压,既设定温度值的大小。

图3

迟滞比较器

图1

不难看出,当输出状态一旦转换后,只要在跳变电压值附近的干扰不超过ΔU之值,输出电压的值就将是稳定的。但随之而来的是分辨率降低。因为对迟滞比较器来说,它不能分辨差别小于ΔU的两个输入电压值。

迟滞比较器加有正反馈可以加快比较器的响应速度,这是它的一个优点。除此之外,由于迟滞比较器加的正反馈很强,远比电路中的寄生耦合强得多,故迟滞比较器还可免除由于电路寄生耦合而产生的自激振荡。

图2

图3为某电磁炉电路中电网过电压检测电路部分。电网电压正常时,1/4LM339的U4<2.8V,U5=2.8V,输出开路,过电压保护电路不工作,作为正反馈的射极跟随器BG1是导通的。当电网电压大于242V 时,U4>2.8V,比较器翻转,输出为0V,BG1截止,U5的电压就完全决定于R1与R2的分压值,为2.7V,促使U4更大于U5,这就使翻转后的状态极为稳定,避免了过压点附近由于电网电压很小的波动而引起的不稳定的现象。由于制造了一定的回差(迟滞),在过电压保护后,电网电压要降到242-5=237V时,U4 图3 双限比较器(窗口比较器) R1 用LM339组成振荡器 锁相环路相位噪声分析 张文军 电信0802 【摘要】本文对锁相电路的相位噪声进行了论述,并对其中各组成部件的相位噪声也做了较为详细的分析。文中最后提出了改进锁相环相位噪声的办法。 【关键词】锁相环;相位噪声;分析 引言 相位噪声是一项非常重要的性能指标,它对电子设备和电子系统的影响很大,从频域看它分布的载波信号两旁按幂律谱分布。用这种信号无论做发射激励信号,还是接收机本振信号以及各种频率基准,这些信号在解调过程中都会和信号一样出现在解调终端,引起基带信噪比下降。在通信系统中使环路信噪比下将,误码率增加;在雷达系统中影响目标的分辨能力,即改善因子。接收机本振的相位噪声遇到强干扰信号时,会产生“倒混频”,使接收机有效噪声系数增加。随着电子技术的发展,对频率源的信号噪声要求越来越严格,因此低相位噪声在物理、天文、无线电通信、雷达、航空、航天以及精密计量、仪器仪表等各种领域里都受到重视。 1 相位噪声概述 相位噪声 ,就是指在系统内各种噪声作用下所表现的相位随机起伏,相位的随机 起伏起必然引起频率随机起伏,这种起伏速度较快,所以又称之为短期频率稳定度。 理想情况下,合成器的输出信号在频域中为根单一的谱线,而实际上任何信号的频谱都不可能绝对纯净,总会受到噪声的调制产生调制边带。由于相位噪声的存在,使波形发生畸变。在频域中其输出信号的谱线就不再是一条单根的谱线,而是以调制边带的形式连续地分布在载波的两边,在主谱两边出现了一些附加的频谱,从而导致频谱的扩展,相位噪声的边带是双边 的,是以0f 为中心对称的,但为了研究方便,一般只取一个边带。其定义为偏离载频1Hz 带宽内单边带相位噪声的功率与载频信号功率之比,它是偏离 载频的复氏频率m f 的函 数 ,记为 () m f ζ,单位为d B c / Hz ,即 ()010lg[/](1) m SSB f P P ζ= 式中SSB P 为偏离载频m f 处,1Hz 带宽内单边带噪声功率;0P 为载波信号功率。 第一部分 模拟电子课程设计 目录 1 课程设计的目的与作用 (1) 1.1设计目的、主要任务及设计思想 (1) 1.2设计作用 (1) 1.2.1滞回比较器 (1) 1.2.2双限比较器 (1) 2 设计任务及所用multisim软件环境介绍 (1) 2.1设计任务 (1) 2.2 Multisim软件环境介绍: (2) 3 电路模型的建立 (2) 3 .1滞回比较器 (2) 3 .2双限比较器 (2) 4 理论分析及计算 (3) 4 .1滞回比较器理论分析及计算 (3) 4 .2双限比较器 (4) 5 仿真结果分析 (5) 5 .1滞回比较器 (5) 5 .2双限比较器 (5) 6 设计总结和体会 (6) 7 参考文献 (6) 1 课程设计的目的与作用 1.1设计目的、主要任务及设计思想 根据设计要求完成对滞回比较器和双限比较器的设计,进一步加强对模拟电子技术的理解。了解比较器的工作原理,掌握外围电路设计与主要性能参数的测试方法。 1.2设计作用 1.2.1.滞回比较器:又称施密特触发器,其抗干扰能力强,如果输入电压受到干扰或噪声的影响,在门限电平上下波动,而输出电压不会在高、低两个电平间反复的跳动。 1.2.2.双限比较器:在实际工作中,有时需要检测输入模拟信号的电平是否处在两个给定的电平之间,此时要求比较器有两个门限电平,这种比较器称为双限比较器。 2设计任务及所用multisim软件环境介绍 2.1设计任务 初步了解和掌握滞回比较器和双限比较器的设计、调试过程,能进一步巩固课堂上学到的理论知识,了解滞回比较器和双限比较器的工作原理 2.2 Multisim软件环境介绍 Multisim是美国国家仪器(NI)有限公司推出的以Windows为基础的仿真工具,适用于板级的模拟/数字电路板的设计工作。它包含了电路原理图的图形输入、电路硬件描述语言输入方式,具有丰富的仿真分析能力。 3 电路模型的建立 3.1.滞回比较器 图3.1 3.2.双限比较器 1.锁相环的基本原理和模型 在并网逆变器系统中,控制器的信号需要与电网电压的信号同步,锁相环通过检测电网电压相位与输出信号相位之差,并形成反馈控制系统来消除误差,达到跟踪电网电压相位和频率的目的。一个基本的锁相环结构如图1-1所示,主要包括鉴相器,环路滤波器,压控振荡器三个部分。 图1-1 基本锁相环结构 鉴相器的主要功能是实现锁相环输出与输入的相位差检测;环路滤波器的主要作用应该是建立输入与输出的动态响应特性,滤波作用是其次;压控振荡器所产生的所需要频率和相位信息。 PLL 的每个部分都是非线性的,但是这样不便于分析设计。因此可以用近似的线性特性来表示PLL 的控制模型。 鉴相器传递函数为:)(Xo Xi Kd Vd -= 压控振荡器可以等效为一个积分环节,因此其传递函数为:S Ko 由于可以采用各种类型不同的滤波器(下文将会讲述),这里仅用)(s F 来表示滤波器的传递函数。 综合以上各个传递函数,我们可以得到,PLL 的开环传递函数,闭环传递函数和误差传递函数分别如下: S s F K K s G d o op )()(=,)()()(s F K K S s F K K s G d o d o cl +=,) ()(s F K K S S s H d o += 上述基本的传递函数就是PLL 设计和分析的基础。 2.鉴相器的实现方法 鉴相器的目的是要尽可能的得到准确的相位误差信息。可以使用线电压的过零检测实现,但是由于在电压畸变的情况下,相位信息可能受到严重影响,因此需要进行额外的信号处理,同时要检测出相位信息,至少需要一个周波的时间,动态响应性能可能受到影响。 一般也可以使用乘法鉴相器。通过将压控振荡器的输出与输入相乘,并经过一定的处理得到相位误差信息。 在实际的并网逆变器应用中还可以在在同步旋转坐标系下进行设计,其基本的目的也是要得的相差的数值。同步旋转坐标系下的控制框图和上图类似,在实际使用中,由于pq 理论在电网电压不平衡或者发生畸变使得性能较差,因而较多的使用dq 变换,将采样得到的三相交流电压信号进行变化后与给定的直流参考电压进行比较。上述两种方法都使用了近似,利用在小角度时正弦函数值约等于其角度,因而会带来误差,这个误差是人为近似导致的误差,与我们要得到的相位误差不是一个概念,最终的我们得到相位误差是要形成压控振荡器的输入信号,在次激励下获得我们所需要的频率和相位信息。 2.1乘法鉴相器 基于AVR 的单片嵌入式系统原理与实践应用 模拟比较器和ADC接口 模拟比较器和模数转换ADC 是单片机内部最常见的两种支持模拟信号输入的功能接口。大部分AVR 都具备这两种类型的接口。本章将以ATmage16 芯片为例,介绍这两种模 拟接口的原理和应用设计方法。 软件设计 下面是实现简易电压的系统程序代码。 /***************************************************** File name : demo_10_3.c Chip type : ATmega16L 华东师范大学电子系马潮10-13 第10 章模拟比较器和ADC 接口 Program type : Application Clock frequency : 4.000000 MHz Memory model : Small External SRAM size : 0 Data Stack size : 256 *****************************************************/ #include 锁相环相位噪声与环路带宽的关系分析 2009-09-09 15:13:17 作者:李仲秋曾全胜来源:现代电子技术 关键字:电荷泵锁相环相位噪声功率谱密度环路带宽 0 引言 电荷泵锁相环是闭环系统,系统各个部分都是一个噪声源,各部分噪声的大小不仅与电路本身有关,而且还与环路带宽等因素有关。因此,设计时必须分析其各频率范围内噪声源影响力的大小,权衡确定环路带宽与各噪声源的相互制约关系。以下利用锁相环的等效噪声模型,重点分析电荷泵锁相环系统的相位噪声特性,得出系统噪声特性的分布特点以及与环路带宽的关系。 1 电荷泵锁相环的基本原理 图1为电荷泵锁相环的示意图,主要由鉴相鉴频器(PFD)、电荷泵、滤波器、压控振荡器(VCO)、分频器等5部分组成,鉴相鉴频器主要用来检测输入信号x(t)与反馈信号xf(t)的频率、相位误差,并产生UP,DOWN信号控制电荷泵的开关。电荷泵由两个对称的电流源和开关组成。电荷泵的开关会对滤波器上的电容充放电,电流经过滤波器滤波后滤掉高频信号,在滤波器上产生能调整压控振荡器频率和相位的电压v(t)。当v(t)上的电压被调整为一个合适的电压值时,xi(t)的频率和相位与x(t)的一致,系统最终处于平衡状态,从而实现对输入信号的跟踪。 2 电荷泵锁相环的噪声模型与相位噪声特性分析 电荷泵锁相环的环路等效噪声模型可以用锁相环各子模块附加噪声源表示。图2给出了带有无源滤波器锁相环噪声源模的型。设fm为距离调制频率的偏移量,该图中主分频器、参考时钟分频器的均方噪声功率谱密度分别被表示为ψd(fm)和ψrcf(fm);鉴相鉴频器的相位噪声被表示为ψpd(fm);晶体振荡器的相位噪声被表示为ψx(fm);相位噪声源的单位是电荷泵的噪声被等价为电流源inp(fm)(单位: ); 滤波器的噪声被等价为电压源Vnf(fm)(单位: 的自由振荡噪声被表示为 环路输出信号的均方噪声功率谱密度被表示为它是闭环情况下所有噪声源影响的总和。输出相位噪声功率谱密度可以表示为: 式中:ψo lp2(fm)为具有低通传输函数的噪声源功率谱密度;ψohp2(fm)为具有高通传输函数的噪声源功率谱密度。 在图2所示的噪声源等效模型中,ψd(fm),ψref(fm),ψpd(fm),ψx(fm)和inp(fm)具有低通传输特性,其传输函数可以表示为: 式中:G(s)和H(s)分别为环路的开环增益函数和闭环增益函数。归一化的电荷泵相位噪声inp(fm)/Kpd和晶体振荡器噪声ψx(fm)/R对ψo lp(fm)的影响也可以用式(2)来表示。当用j2πfm代替s时,ψo2(fm)中具有低通传输函数噪声源功率谱密度的噪声分量ψo lp2 (fm)可以表示为: 滞回电压比较器原理及特性 滞回电压比较器 滞回比较器又称施密特触发器,迟滞比较器。这种比较器的特点是当输入信号ui逐渐增大或逐渐减小时,它有两个阈值,且不相等,其传输特性具有“滞回”曲线的形状。 滞回比较器也有反相输入和同相输入两种方式。 UR是某一固定电压,改变UR值能改变阈值及回差大小。 以图4(a)所示的反相滞回比较器为例,计算阈值并画出传输特性 图4 滞回比较器及其传输特性 (a)反相输入;(b)同相输入 1,正向过程 正向过程的阈值为 形成电压传输特性的abcd段 2,负向过程 负向过程的阈值为 形成电压传输特性上defa段。由于它与磁滞回线形状相似,故称之为滞回电压比较器。 利用求阈值的临界条件和叠加原理方法,不难计算出图4(b)所示的同相滞回比较器的两个阈值 两个阈值的差值ΔUTH=UTH1–UTH2称为回差。 由上分析可知,改变R2值可改变回差大小,调整UR可改变UTH1和UTH2,但不影响回差大小。即滞回比较器的传输特性将平行右移或左移,滞回曲线宽度不变。 图5 比较器的波形变换 (a)输入波形;(b)输出波形 例如,滞回比较器的传输特性和输入电压的波形如图6(a)、(b)所示。根据传输特性和两个阈值(UTH1=2 V, UTH2=–2V),可画出输出电压uo的波形,如图6(c)所示。从图(c)可见,ui在UTH1与UTH2之间变化,不会引起uo的跳变。但回差也导致了输出电压的滞后现象,使电平鉴别产生误差。 图6 说明滞回比较器抗干扰能力强的图 (a)已知传输特性;(b)已知ui 波形; (c)根据传输特性和ui波形画出的uo波形 一种自适应迟滞性比较器的设计 关键词:迟滞电路,比较器 摘要:设计了一种由滤波器和迟滞比较器构成的传输频率信号电路。设计使用滤波器将输入信号改变适当的相位作为迟滞比较器标准端的信号,而原信号输入比较器的另一端。那么由于迟滞比较器的电压同时随输入信号改变。 迟滞电路(hysteresis circuit)又称施密特触发电路(schmitt trigger circuit)。因他能滤除干扰噪声而获得很广泛的运用。在一些应用场合中,特别在某些模/数转换电路中[1],迟滞比较器作为抗干扰的比较器应用较多。为了获得更好的转换效果,需要较好地选择迟滞比较器正端输入的基准电压。而信号的未知为确定基准电压带来麻烦。本文设计的一种加入滤波器的迟滞比较器解决了这个问题。 1 迟滞比较器的设计 迟滞性是比较器的一种特性,他使比较器的输入阈值随输入(出)电平而改变。比较器实现的方法很多。他们都有不同形式的正反馈。最常见的即是由放大器接成正反馈组成。这类迟滞比较器由于方便的设计和放大器的标准生产成为主流。设计选用了最常见的由放大器正反馈的设计,如图1所示。 由米尔曼公式可得输入电压升高和降低时的基准电压如下式: 而电路能滤掉的噪声即迟滞性为: 由上式可知,迟滞性由电源电压和R4,R5阻值决定。本设计中V r的大小是变成的,因此正负基准电压也随V r变化,为了达到自适应的目的希望基准电压对输入有好的跟随性同时减小输出端的影响。因此将R4取值得比R5要小一个数量级。 2 滤波器的设计 设计滤波器往往要考虑下列因素: (1)工作频率范围。 (2)参数变化的灵敏度及稳定度。 (3)实际元件的重量和大小。 (4)运算放大器的电压源。 2.1 滤波器的选择[2] 本设计是工作在低频的比较器。此时当信号频率是低频时可以考虑的方式有低通、带通或全通,同时还可选择一阶或多阶。在考虑此设计后,一阶滤波器在此设计中是较好的,且低通 数值比较器电路的仿真分析及应用 程勇 陈素 陈淑平 (机电信息工程系 实训中心 450008) 摘要:数值比较器是数字电路中经常用到的典型电路,传统的教学模式中,对数值比较器的学习及应用设计,离不开在实验室中的电路调试,学习方式较为枯燥抽象,又耗时费力,学习效果也不尽理想。现代电子设计中,由于仿真软件的出现,变抽象的知识为直观的展示,既可以通过仿真学习数值比较器的工作原理,又可以通过仿真进行数值比较器的应用设计,学习及应用效果事半功倍。 关键词:数值比较器、仿真分析、应用 在各种数字系统尤其是在数字电子计算机中,经常需要对两个二进制数进行大小判别,然后根据判别结果转向执行某种操作。用来完成两个二进制数的大小比较的逻辑电路称为数值比较器,简称比较器。在数字电路中,数值比较器的输入是要进行比较的两个二进制数,输出是比较的结果。 一.电路设计分析 首先讨论1位数值比较器。1位数值比较器是多位比较器的基础。当A 和B 都是1位二进制数时,它们的取值和比较结果可由1位数值比较器的真值表表示,如表1所示。 表1 1位数值比较器的真值表 由真值表可得如下逻辑表达式 A B A B A B F AB F AB F AB AB A B ><====+=⊕ 由逻辑表达式可以画出如图1所示的逻辑图。 图1 1位数值比较器逻辑图 二.比较器电路的仿真分析 (一)元件选取及电路组成 打开仿真软件Multisim 10,根据图1所示的1位数值比较器逻辑图,可以在仿真软件Multisim 10中构建仿真电路,如 图3所示。 1.元件选取 (1)指示灯的选取 1位数值比较器逻辑运算完后,输出结果处 接一指示灯作为指示,灯亮表示运算结果成立, 灯灭表示运算结果不成立。单击元件栏的Place Indicator→PROBE,选取PROBE_RED指示灯。 为了观察清晰明白,将指示灯PROBE连击打开其图2 指示灯的Label设置 设置对话框,在其Label中的标号由默认的X1改为“A等于B”、“A大于B”、“A 小于B”等。如图2所示。 (2)其他元器件可参照以下说明取用。 电源VCC:Place Source→POWER_SOURCES→VCC 接地:Place Source→POWER_SOURCES→GROUND,选取电路中的接地。 或非门U1A的选取:Place TTL→74LS→74LS02D 与门U3A、U5A的选取:Place TTL→74LS→74LS08D 非门U2 A、U4A的选取:Place TTL→74LS→74LS04N 2.电路组成 参照图3放置元件并进行连接,构成1位数值比较器的仿真测试电路。 (二)仿真分析 神奇的滞回电压比较器 初学者感觉滞回电压比较器比较奇妙,是因为它有两个转折的门限电压,为了容易理解,不妨从一个更通俗的例子说起。比如我们常用饮水机中的温控开关.就是比较简单也是比较典型的具有滞回特性的器件。假如我们设定开关工作的温度是T1,如果开关没有滞回的特点,当达到这个温度时,电热器断开,温度下降,当低于这个温度时,电加热器接通。这样就会出现一种情况,电热器在这个温度附近会频繁接通和断开,温度达到T1一加热器件断开一温度下降一导致电热器接通一温度上升-加热器件又断开,如此反复,在临界区附近产生振荡。这是我们不希望的结果,所以,温控开关一般是具有滞回的特点,动作(断开)温度TH和复位(接通)温度TL有一定的温度差一回复误差。比如:设定开关断开的温度是大于95℃,复位接通的温度是小于90℃,回复误差根据需要可以调整,这样就解决了温控开关频繁接通和断开的问题。接通到断开,断开到接通沿着不同的路径,不走回头路,故此称为滞回控制开关。 滞回电压比较器和上述的温控开关是一样的道理,可以类比理解。大家知道运算放大器在开环状态下可以用作比较器,其理想和实际的电压传输特性如附图所示,实际特性是只有当它的差模输入电压足够大时,输出电压Uo才为正负最大值。Uo在从+Uce变为-Uss或从-Uss变为+Uce的过程中,随着Ui的变化,将经过线性区,并需要一定的时间。可以知道,在单限比较器中,输入电压在阀值电压附近的微小变化,都将引起两个不同的输出状态之间产生不期望的频繁穿越跳变,不管这种微小变化是来源于输入信号还是外部干扰。因此,虽然单限比较器很灵敏,但是抗干扰能力差。而滞回比较器具有滞回特性,即具有惯性,因此也就具有一定的抗干扰能力。用带有内部滞回电路的比较器代替开环运算放大器能够抑制输出的频繁跳变和振荡。 滞回电压比较器电路有两个阀值电压,类似本文开始提到的温控开关,有两个门限值UH、UL。输入电压Ui从小变大过程中使输出电压Uo产生跃变的阔值电压UH,不等于Ui从大变小过程中使输出电压Uo产生跃变的阀值电压UL.电路具有滞回特性。举个例子,如附图所示为从反向输入端输入的滞回比较器电路.由分压电阻Rl:R2构成正反馈。假设Rl=lOkn,R2=lOOn,电源供电电压为:U CC=13V,Uss=-13V,反馈系数F=R2/(R 1+R2)。比较器的反相输入电压从0开始线性变化,当Ui=0时,加到同相的输入瑞电压为Uref=RI/(R1+R2)Eref,Uo=Uce,同相端总电压UH=1 V,同相端电压大于反相端电压,这是一个稳定的状态。 输入电压由零向正方向增长,只要它还小于UH,即Ui<1V,输出电压Uo都保持最大正的电征Ucc不变,即Uo=13V。当Ui一旦超过UH一点点,平衡即被破坏,由于反向输入电压大于正向输入电压,输出电压Uo就会从最大正向电压Ucc(+13V)向负向最大电压Uss(-13V)转换。而且由于R1、R2引入的正向反馈作用将加速这种转换,形成跳变,获得理想的传输电压特性,Uo从+13V跳变到-13V。 跳变完成后,加到同相端的总电压为:UL=0.86V,显然只要输入电压保持大干UL即U>0.86V,输出电压将保持负的最大值Uss(-13V)不变。但是当输入电压U从大到小下降到小于UL(0.86V)时,一个相反的连锁反馈又将使输出电压Uo从负的最大值Vss(-13V)跳变到正的最大值Ucc(+13 V)。通过改变Eref的大小可方便改变滞回区间。 斯密特滞回触发器只有-个触发端子,比较方便灵活,在实际中具有广泛的应用,如一开始提到的温控开关就可以用滞回触发器实现。再比如开关电源中的欠压保护就是滞回比较器的典型应用,当市电电压低于一定值时.通过滞回比较器使开关电源停止工作,保护电网和机器的安全。 我们以常用的UC3842为例简单说明其原理,UC3842⑦脚为电压输入端,内接施密特滞回触发器,利用其回滞特性实现锁存,其启动电压范围为16V-34V。 在电源启动,Vcc<16V时,输入电压施密器比较器输出为0,此时无基准电压产生,电路不工作;当Vcc>16V时输入电压施密特比较器送出高电平到5v稳压器,产生5v基准电压,此电压一方面供内部电路工作,另一方面通过⑧脚向外部提供参考电压。一旦施密特比较器翻转为高电平(芯片开始工作以后),Vcc可以在10V-34V范围内变化而不影响电路的工作状态。当Vcc低于10V时.施密特比较器又翻转为低电平,电路停止工作。当出现机器启动困难的故障时,就要考虑该脚外围元件是否正常,该部分电路比较简单,维修应该不复杂,关键是判断故障,要抓住其故障特点。由于保护电路的滞回特点,-般是启动困难,一旦启动成功,能长时间稳定工作。 The Research of Noise in The PLL LU Shiqiang , YANG Guoyu ( School of the Microwave engineering ,UESTC ChengDu 610054 China ) Absract This articles introducs the basic concepts and the phase noise in phase-locked loops (PLLs). It focus on a detailed examination of two critical specifications associated with PLLs : phase noise and reference spurs. What causes them and how can they be minimized? Also it inculdes an example . Key words :PLL ; Phase Noise ; Oscillator 1 . The Basic Theory of the PLL A phase-locked loop is a feedback system combining a voltage controlled oscillator and a phase comparator so connected that the oscillator maintains a constant phase angle relative to a reference signal. Phase-locked loops can be used, for example, to generate stable output frequency signals from a fixed low-frequency signal . The phase locked loop can be analyzed in general as a negative feedback system with a forward gain term and a feedback term. .A simple block diagram of a voltage-based negative-feedback system is shown in Figure 1. Figure 1. Standard negative-feedback control system model In a phase-locked loop, the error signal from the phase comparator is proportional to the relative phase of the input and feedback signals. The average output of the phase detector will be constant when the input and feedback signals are the same frequency. The usual equations for a negative-feedback system apply. Forward Gain = G(s), [s = jw = j2pif] Loop Gain = G(s) H(s) Closed Loop Gain = G(s)/[1+G(s)H(s)] Because of the integration in the loop, at low frequencies the steady state gain, G(s) is very high and VO/VI, Closed-Loop Gain =1/ H and Fo=NF REF. . The components of a PLL that contribute to the loop gain include : 1. The phase detector (PD) and charge pump (CP). 2. The loop filter, with a transfer function of Z(s) 3. The voltage-controlled oscillator (VCO), with a sensitivity of KV /s 4. The feedback divider, 1/N 滞回比较器文件管理序列号:[K8UY-K9IO69-O6M243-OL889- 实验十电压比较器的安装与测试 一.实验目的 1.了解电压比较器的工作原理。 2.安装和测试四种典型的比较器电路:过零比较器、电平检测器、滞回比较器和窗口比较器。 二.预习要求 1.预习过零比较器、电平检测器、滞回比较器和窗口比较器的工作原理。 2.预习使用示波器测量信号波形和电压传输特性的方法。 三.实验原理 电压比较器的基本功能是能对两个输入电压的大小进行比较,判断出其中那一个比较大。比较的结果用输出电压的高和低来表示。电压比较器可以采用专用的集成比较器,也可以采用运算放大器组成。由集成运算放大器组成的比较器,其输出电平在最大输出电压的正极限值和负极限值之间摆动,当要和数字电路相连接时,必须增添附加电路,对它的输出电压采取箝位措施,使它的高低输出电平,满足数字电路逻辑电平的要求。 下面讨论几种常见的比较器电路。 基本过零比较器(零电平比较器) 过零比较器主要用来将输入信号与零电位进行比较, +15V 以决定输出电压的极性。电路如图1所示: u i 2 7 放大器接成开环形式,信号u i 从反向端输入,同 μA741 6 u o 相端接地。当输入信号u i < 0时,输出电压u o 为正极限 3 4 值U OM ;由于理想运放的电压增益A u →∞,故当输 ?15V 入信号由小到大,达到 u i = 0 时,即 u ?= u + 的时刻, 输出电压 u o 由正极限值 U OM 翻转到负极限值 ?U OM 。 图 1 反向输入过零比较器 当u i > 0时输出u o 为负极限值 ?U OM 。因此,输出翻转的临界条件是u + = u ? = 0。 即: +U OM u i < 0 u o = (1) ?U OM u i > 0 其传输特性如图2(a )所示。所以通过该电路输出的电压值,就可以鉴别输入信号电压u i 是大于零还是小于零,即可用做信号电压过零的检测器。 锁相环的组成和工作原理 时间:2011-11-23 来源:作者: 关键字:锁相环工作原理 1.锁相环的基本组成 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。 锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。 因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。 锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。 2.锁相环的工作原理 锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。 鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为: 式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。则模拟乘法器的输出电压uD为: 用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压uC(t)。即uC(t)为: 式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为: 上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,uc(t)为恒定值。当上式不等于零时,说明锁相环的相位还未锁定,输入信号和输出信号的频率不等,uc(t)随时间而变。 因压控振荡器的压控特性如图8-4-3所示,该特性说明压控振荡器的振荡频率ωu以ω0为中心,随输入信号电压uc(t)的变化而变化。该特性的表达式 上式说明当uc(t)随时间而变时,压控振荡器的振荡频率ωu也随时间而变,锁相环进入“频率牵引”,自动跟踪捕捉输入信号的频率,使锁相环进入锁定的状态,并保持ω0=ωi的状态不变。 8.4.2锁相环的应用 1.锁相环在调制和解调中的应用 (1)调制和解调的概念 为了实现信息的远距离传输,在发信端通常采用调制的方法对信号进行调制,收信端接收到信号后必须进行解调才能恢复原信号。 所谓的调制就是用携带信息的输入信号ui来控制载波信号uC的参数,使载波信号的某一个参数随输入信号的变化而变化。载波信号的参数有幅度、频率和位相,所以,调制有调幅(AM)、调频(FM)和调相(PM)三种。 调幅波的特点是频率与载波信号的频率相等,幅度随输入信号幅度的变化而变化;调频波的特点是幅度与载波信号的幅度相等,频率随输入信号幅度的变化而变化;调相波的特点是幅度与载波信号的幅度相等,相位随输入信号幅度的变化而变化。调幅波和调频波的示意图如图8-4-4所示。 ADI官网下载了个资料,对于PLL学习和设计来说都非常实用的好资料,转发过来,希望对大家有帮助(原文链接 https://www.doczj.com/doc/ee2503282.html,/zh/content/cast_faq_PLL/fca.html#faq_pll_01) ?参考晶振有哪些要求?我该如何选择参考源? ?请详细解释一下控制时序,电平及要求? ?控制多片PLL芯片时,串行控制线是否可以复用? ?请简要介绍一下环路滤波器参数的设置? ?环路滤波器采用有源滤波器还是无源滤波器? ?PLL对于VCO有什么要求?以及如何设计VCO输出功率分配器? ?如何设置电荷泵的极性? ?锁定指示电路如何设计? ?PLL对射频输入信号有什么要求? ?PLL芯片对电源的要求有哪些? ?内部集成了VCO的ADF4360-x,其VCO中心频率如何设定? ?锁相环输出的谐波? ?锁相环系统的相位噪声来源有哪些?减小相位噪声的措施有哪些? ?为何我测出的相位噪声性能低于ADISimPLL仿真预期值? ?锁相环锁定时间取决于哪些因素?如何加速锁定? ?为何我的锁相环在做高低温试验的时候,出现频率失锁? ?非跳频(单频)应用中,最高的鉴相频率有什么限制? ?频繁地开关锁相环芯片的电源会对锁相环有何影响? ?您能控制PLL芯片了么?,R分频和N分频配置好了么? ?您的晶振输出功率有多大?VCO的输出功率有多大? ?您的PFD鉴相极性是正还是负? ?您的VCO输出频率是在哪一点?最低频率?最高频率?还是中间的某一点?VCO 的控制电压有多大? ?您的PLL环路带宽和相位裕度有多大? ?评价PLL频率合成器噪声性能的依据是什么? ?小数分频的锁相环杂散的分布规律是什么? ?到底用小数分频好还是整数分频好? ?ADI提供的锁相环仿真工具ADISimPLL支持哪些芯片,有什么优点? ?分频–获得高精度时钟参考源? ?PLL,VCO闭环调制,短程无线发射芯片? ?PLL,VCO开环调制? ?时钟净化----时钟抖动(jitter)更小? ?时钟恢复(Clock Recovery)? 问题:参考晶振有哪些要求?我该如何选择参考源? 答案:波形:可以使正弦波,也可以为方波。 功率:满足参考输入灵敏度的要求。 运放与比较器的用法 NE5532是双极型双运放,剩下的一个不用,可以将它们的输入端全部悬空即可,跟该运放相似的还有LM358、LM324,它们不用的输入端都可以悬空。而对于CMOS运放,由于输入阻抗极高,若将输入端悬空,很容易受干扰,故对于像ICL7642、MC14573这类CMOS 运放,内部用不完的运放,输入端一般要接高电平或地。 1、运放可以连接成为比较输出,比较器就是比较。 2、比较器输出一般是OC,便于电平转换;比较器没有频补,Slew Rate比同级运放大, 但接成放大器易自激。 比较器的开环增益比一般放大器高很多,因此比较器正负端小的差异就引起输出端变化. 3、频响是一方面,另外运放当比较器时输出不稳定,不一定能满足后级逻辑电路的要求。 4、比较器为集电极开路输出,容易输出TTL电平,而运放有饱和压降,使用不便。 关于运算放大器与专用比较器的区别可分为以下几点: 1.比较器的翻转速度快,大约在ns数量级,而运放翻转速度一般为us数量级(特殊高速运放 除外); 2.运放输入可以接成负反馈电路,而比较器不能使用负反馈,虽然比较器也有同相和反相两 个输入端,但因为其内部没有相位补偿电路,如果输入负反馈,电路不能稳定工作,内部无相位补偿电路.这也是比较器比运放速度快的原因. 3.运放的初级一般采用推挽电路,双极性输出,而多数比较器输出极为集电级开路结构,所 以需要上拉电阻,单极性输出,容易和数字电路连接. 加法器和减法器就是用运算放大器搭的运算电路. 电压比较器 电压比较器可以看作是放大倍数接近―无穷大‖的运算放大器。 电压比较器的功能:比较两个电压的大小(用输出电压的高或低电平,表示两个输入电压的大小关系): 当‖+‖输入端电压高于‖-‖输入端时,电压比较器输出为高电平; 当‖+‖输入端电压低于‖-‖输入端时,电压比较器输出为低电平; 电压比较器的作用:它可用作模拟电路和数字电路的接口,还可以用作波形产生和变换电路等。利用简单电压比较器可将正弦波变为同频率的方波或矩形波。 简单的电压比较器结构简单,灵敏度高,但是抗干扰能力差,因此我们就要对它进行改进。改进后的电压比较器有:滞回比较器和窗口比较器。 运放,是通过反馈回路和输入回路的确定―运算参数‖,比如放大倍数,反馈量可以是输出的电流或电压的部分或全部。而比较器则不需要反馈,直接比较两个输入端的量,如果同相输入大于反相,则输出高电平,否则输出低电平。电压比较器输入是线性量,而输出是开关(高低电平)量。一般应用中,有时也可以用线性运算放大器,在不加负反馈的情况下,构成电压比较器来使用。 实验十电压比较器的安装与测试 一.实验目的 1.了解电压比较器的工作原理。 2.安装和测试四种典型的比较器电路:过零比较器、电平检测器、滞回比较器和窗口比较器。 二.预习要求 1.预习过零比较器、电平检测器、滞回比较器和窗口比较器的工作原理。 2.预习使用示波器测量信号波形和电压传输特性的方法。 三.实验原理 电压比较器的基本功能是能对两个输入电压的大小进行比较,判断出其中那一个比较大。比较的结果用输出电压的高和低来表示。电压比较器可以采用专用的集成比较器,也可以采用运算放大器组成。由集成运算放大器组成的比较器,其输出电平在最大输出电压的正极限值和负极限值之间摆动,当要和数字电路相连接时,必须增添附加电路,对它的输出电压采取箝位措施,使它的高低输出电平,满足数字电路逻辑电平的要求。 下面讨论几种常见的比较器电路。 基本过零比较器(零电平比较器) 过零比较器主要用来将输入信号与零电位进行比较,+15V 以决定输出电压的极性。电路如图1所示:u i 2 7 放大器接成开环形式,信号u i从反向端输入,同μA7416u o 相端接地。当输入信号u i< 0时,输出电压u o为正极限34 值U OM;由于理想运放的电压增益A u→∞,故当输-15V 入信号由小到大,达到u i = 0 时,即u -= u + 的时刻, 输出电压u o 由正极限值U OM 翻转到负极限值-U OM。图 1 反向输入过零比较器 当u i >0时输出u o为负极限值-U OM。因此,输出翻转的临界条件是u + = u - = 0。 即:+U OM u i< 0 u o = (1) -U OM u i >0 其传输特性如图2(a)所示。所以通过该电路输出的电压值,就可以鉴别输入信号电压u i是大于零还是小于零,即可用做信号电压过零的检测器。 相位噪声基础及测试原理和方法 相位噪声指标对于当前的射频微波系统、移动通信系统、雷达系统等电子系统影响非常明显,将直接影响系统指标的优劣。该项指标对于系统的研发、设计均具有指导意义。相位噪声指标的测试手段很多,如何能够精准的测量该指标是射频微波领域的一项重要任务。随着当前接收机相位噪声指标越来越高,相应的测试技术和测试手段也有了很大的进步。同时,与相位噪声测试相关的其他测试需求也越来越多,如何准确的进行这些指标的测试也愈发重要。 1、引言 随着电子技术的发展,器件的噪声系数越来越低,放大器的动态范围也越来越大,增益也大有提高,使得电路系统的灵敏度和选择性以及线性度等主要技术指标都得到较好的解决。同时,随着技术的不断提高,对电路系统又提出了更高的要求,这就要求电路系统必须具有较低的相位噪声,在现代技术中,相位噪声已成为限制电路系统的主要因素。低相位噪声对于提高电路系统性能起到重要作用。 相位噪声好坏对通讯系统有很大影响,尤其现代通讯系统中状态很多,频道又很密集,并且不断的变换,所以对相位噪声的要求也愈来愈高。如果本振信号的相位噪声较差,会增加通信中的误码率,影响载频跟踪精度。相位噪声不好,不仅增加误码率、影响载频跟踪精度,还影响通信接收机信道内、外性能测量,相位噪声对邻近频道选择性有影响。如果要求接收机选择性越高,则相位噪声就必须更好,要求接收机灵敏度越高,相位噪声也必须更好。 总之,对于现代通信的各种接收机,相位噪声指标尤为重要,对于该指标的精准测试要求也越来越高,相应的技术手段要求也越来越高。 2、相位噪声基础 2.1、什么是相位噪声 相位噪声是振荡器在短时间内频率稳定度的度量参数。它来源于振荡器输出信号由噪声引起的相位、频率的变化。频率稳定度分为两个方面:长期稳定度和短期稳定度,其中,短期稳定度在时域内用艾伦方差来表示,在频域内用相位噪声来表示。 2.2、相位噪声的定义 锁相环输出信号相位噪声噪声及杂散特性分析应用实践 【摘要】本文详细地介绍了锁相环的鉴频鉴相器、分频器和输入参考信号的相位噪声对锁相环合成输出信号的近端相位噪声的具体贡献值。并以CDMA 1X基站系统中800MHz的FS 单板的锁相环输出信号相位噪声指标进行理论计算。为广大锁相环设计者提供理论计算方法的参考和实践设计的参考依据。 【关键词】锁相环设计,相位噪声 一、术语和缩略语 表格 1 术语和缩略语 二、问题的提出 锁相环工作原理图,由三部分组成:鉴相器(PFD)、环路滤波器(LPF)和压控晶体振荡器(VCXO),如图0-1所示。 图0-1锁相环原理框图 锁相环输出信号指标主要有相位噪声、谐波抑制、杂散、输出功率、跳频时间。在本文中以CDMA1X基站系统中800MHz的FS单板应用为背景,在CDMA基站中不需要跳频,所以调频时间基本不做要求。输出功率比较好控制,只要调整衰减网络就能保证。锁相环输出信号的相位噪声、谐波抑制和杂散成为影响系统指标的主要因素,成为锁相环技术的关键指标项。在锁相环设计中,相位噪声和杂散成为系统设计主要难点。 三、解决思路 相位噪声分析 相位噪声主要由VCO、鉴频鉴相器、分频器和输入参考信号的相位噪声这四部分引入。环路滤波器对于由鉴频鉴相器、分频器和输入参考信号的相位噪声这三部分引入的相位噪声 具有低通特性,对于VCO产生的相位噪声具有高通特性。一般来说环路带宽内的相位噪声主要决定于由鉴频鉴相器、分频器和输入参考信号,环路带宽以外的相位噪声主要决定于VCO,在环路带宽周围,这四部分的噪声影响相当。所以为了尽量降低输出信号的相位噪声环路滤波器的环路带宽的最佳点是由鉴频鉴相器、分频器和输入参考信号的相位噪声这三部分引入的相位噪声总和与VCO引入的相位噪声相同时的频率。在实际运用中还礼滤波器的设计是非常重要的。对于远端相位噪声如100KHz和1MHz处的一般远远高于环路带宽,其相位噪声主要决定于VCO,要保证其指标主要是选择良好的VCO。而近端相位噪声如100Hz主要由鉴频鉴相器、分频器和输入参考信号的相位噪声决定,但如果还礼带宽取得很小的话如200Hz则VCO的影响也将非常之大。而如果环路带宽远远大于1KHz如为6KHz 以上时1KHz处的相位噪声也将主要由鉴频鉴相器、分频器和输入参考信号的相位噪声决定。下面就分别分析这三部分相位噪声。 由鉴相器引入的相位噪声 由于鉴相器引入的相位噪声为: PD Phase Noise = ( 1 Hz Normalized Phase Noise Floor from Table ) + 10log( Comparison Frequency ) + 20log( N ) 现在FS板的中频环路采用的PLL芯片为NS的LMX2306,其相位噪声基底为-210dBc/Hz。 在CDMA 1X 基站系统800MHz的FS单板中采用的鉴相频率为30KHz,两个中频分别为69.99MHz和114.99MHz,由鉴相器产生的相位噪声为: 69.99MHz: PD Phase Noise= -210+10log(30000)+20log(69990000/30000)= -97.9dBc/Hz 114.99MHz: PD Phase Noise= -210+10log(30000)+20log(114990000/30000)=-93.5dBc/Hz 射频本振范围为754~779MHz。步进为30KHz,鉴相频率为240KHz。对于779MHz 的本振由鉴相器引入的相位噪声为: PD Phase Noise= -210+10log(240000)+20log(779000000/240000)=-85.9dBc/Hz 由分频器引入的相位噪声 由分频器引入的相位噪声的计算公式入下: DIV Phase Noise = (Device Phase Noise Floor )+ 20log( N ) PLL芯片中分频器的相位噪声在器件手册中并没有给出。一般高频分频器的相位噪声基底约为-165dBc/Hz左右。因此就假设分频器的相位噪声基底为-165dBc/Hz,于是得到分频器引起的相位噪声如下: 69.99MHz的中频频率为: DIV Phase Noise= -165+20log(69990000/30000)= -97.6dBc/Hz 114.99MHz的中频频率为: DIV Phase Noise= -165+20log(114990000/30000)= -93.3dBc/Hz 779MHz的射频频率为: DIV Phase Noise= -165+20log(779000000/240000)= -94.7dBc/Hz 由参考信号引入的相位噪声 参考信号引起的相位噪声的计算公式如下 REF Phase Noise = (REF’S Phase Noise )-20log(R)+ 20log( N ) 系统的参考信号都是由GPSTM模块提供的,GPSTM输出的参考信号的相位噪声为-130dBc/Hz@100Hz和-145dBc/Hz@1KHz。最后参考信号通过FDM板到FS板,FDM板输【重要】锁相环的相位噪声分析

滞回比较器

锁相环的基本原理和模型

AVR模拟比较器使用方法

锁相环相位噪声与环路带宽的关系分析

滞回电压比较器原理及特性

迟滞性比较器的设计方法

数值比较器的应用

神奇的滞回电压比较器

锁相环中的相位噪声研究

滞回比较器

锁相环的组成和工作原理

锁相环常见问题解答要点

运放与比较器的用法

电压比较器原理及使用

相位噪声基础及测试原理和方法

锁相环输出信号相位噪声噪声及杂散特性分析应用实践