实验五 4位十进制频率计设计

- 格式:doc

- 大小:107.00 KB

- 文档页数:6

频率计的设计内容介绍:数字频率计是用来测量信号频率的装置。

它可以测量正弦波、方波、三角波和尖脉冲信号的频率。

在进行模拟、数字电路的设计、安装、调试的过程中,经常要用到频率计。

由于其用十进制数显示,测量速度快、精度高、显示直观,因此频率计得到广泛的应用。

一、设计内容及技术指标设计内容:设计用四只数码管显示结果的数字频率计。

技术指标:1、测量信号:正弦波、方波、三角波2、被测量信号频率范围:1HZ—9999HZ3、显示方式:4位十进制数显示4、时基电路由555定时器组成多谐振荡器产生的时基信号,其脉冲宽度分别为:正脉冲 1S,负脉冲0.25S二、电路原理及框图数字频率计测频率的基本原理:所谓频率,就是周期性信号在单位时间(1s)内变化的次数。

若在一定时间间隔T 内测得这个周期性信号的重复变化次数为N,则其频率可表示为:f=N/T (1)图1(a)是数字频率计的组成框图。

被测信号vx经放大整形电路变成计数器所要求的脉冲信号I,其频率与被测信号的频率fx相同。

时基电路提供标准时间基准信号II,其高电平持续时间t1=1s,当l秒信号来到时,闸门开通,被测脉冲信号通过闸门,计数器开始计数,直到l秒信号结束时闸门关闭,停止计数。

若在闸门时间1s内计数器计得的脉冲个数为N,则被测信号频率fx=NHz。

逻辑控制电路的作用有两个:一是产生锁存脉冲IV,使显示器上的数字稳定;二是产生清“0”脉冲V,使计数器每次测量从零开始计数。

各信号之间的时序关系如图1(b)所示。

I所谓频率,就是周期性信号的在单位时间(1s )内变化的次数,若在一定时间间隔T 内测得这个周期性信号的重复变化次数为N ,则其频率可表示为:T N f = (2.2.1)上图是数字频率计的结构框图。

被测信号X V 经放大整形电路变成计数器所要求的脉冲信号I ,其频率与被测信号的频率x f 相同。

时基电路提供标准时间基准信号II ,其高电平持续的时间s t 11=,当s 1信号来到时,闸门开通,被测脉冲信号通过闸门,计数器开始计数,直到s 1信号结束时闸门关闭,停止计数。

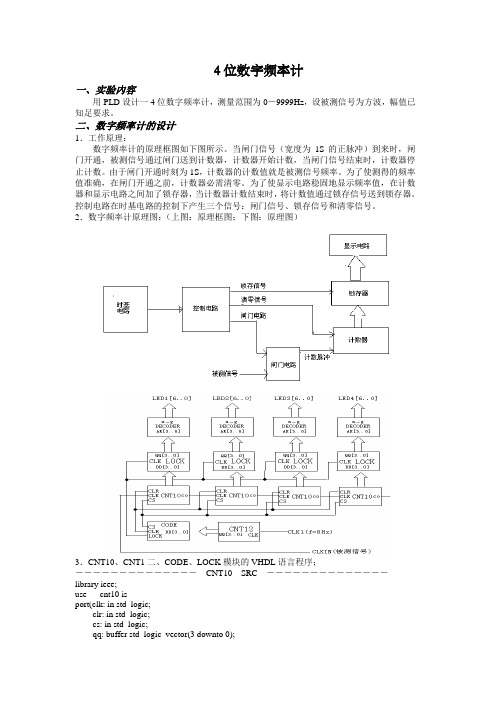

4位数字频率计一、实验內容用PLD设计一4位数字频率计,测量范围为0-9999Hz,设被测信号为方波,幅值已知足要求。

二、数字频率计的设计1.工作原理:数字频率计的原理框图如下图所示。

当闸门信号(宽度为1S的正脉冲)到来时,闸门开通,被测信号通过闸门送到计数器,计数器开始计数,当闸门信号结束时,计数器停止计数。

由于闸门开通时刻为1S,计数器的计数值就是被测信号频率。

为了使测得的频率值准确,在闸门开通之前,计数器必需清零。

为了使显示电路稳固地显示频率值,在计数器和显示电路之间加了锁存器,当计数器计数结束时,将计数值通过锁存信号送到锁存器。

控制电路在时基电路的控制下产生三个信号:闸门信号、锁存信号和清零信号。

2.数字频率计原理图:(上图:原理框图;下图:原理图)3.CNT10、CNT1二、CODE、LOCK模块的VHDL语言程序;――――――――――――――CNT10SRC――――――――――――――library ieee;use cnt10 isport(clk: in std_logic;clr: in std_logic;cs: in std_logic;qq: buffer std_logic_vector(3 downto 0);co: out std_logic);end cnt10;architecture one of cnt10 isbeginprocess(clk, clr, cs)beginif (clr = '1') then qq <= "0000";elsif (clk'event and clk = '1') thenif (cs = '1') thenif (qq = 9) then qq <= "0000";else qq <= qq + 1;end if;end if;end if;end process;process(qq)beginif (qq = 9) then co <= '0';else co <= '1';end if;end process;end one;――――――――――――――CNT12SRC――――――――――――――library ieee;use cnt12 isport(clk: in std_logic;qq: buffer std_logic_vector(3 downto 0));end cnt12;architecture one of cnt12 isbeginprocess(clk)beginif (clk'event and clk='1') thenif (qq = 11) then qq <= "0000";else qq <= qq + 1;end if;end if;end process;end one;――――――――――――――CODE SRC――――――――――――――library ieee;use code isport(dd: in std_logic_vector(3 downto 0);cs: out std_logic;clr: out std_logic;lock: out std_logic);end code;architecture one of code isbeginprocess(dd)beginif (dd = 0) then clr <= '1';else clr <= '0';end if;if (dd = 11) then lock <= '1';else lock <= '0';end if;if ((dd > 0) and (dd < 9)) then cs <= '1';else cs <= '0';end if;end process;end one;――――――――――――――LOCK SRC ――――――――――――――library ieee;use lock isport(clk: in std_logic;dd: in std_logic_vector(3 downto 0);qq: out std_logic_vector(3 downto 0));end lock;architecture one of lock isbeginprocess(clk, dd)beginif (clk'event and clk = '1') then qq <= dd;end if;end process;end one;4.CNT10、CNT1二、CODE、LOCK模块的仿真结果;(附原始记录)―――――――――――――――CNT10仿真结果―――――――――――――――――――――――――――――CNT12仿真结果―――――――――――――――――――――――――――――CODE仿真结果――――――――――――――――――――――――――――――LOCK仿真结果―――――――――――――――5.项目下载步骤;(1)器件选定选择器件为MAX7000S系列的EPM7128SLC84(2)管脚锁定(说明为何要进行管脚锁定)所谓管脚锁定,就是将加法器adder+gdf的输入,输出信号安排在器件的指定管脚上.在实际应用中,PLD器件常常与其他电路连在一路,因此PLD器件的管脚锁定应按如实际电信号名管脚号信号名管脚号信号名管脚号信号名管脚号LED10 64 LED10 73 LED10 4 LED10 12 LED11 65 LED11 75 LED11 6 LED11 15 LED12 67 LED12 76 LED12 5 LED12 16 LED13 68 LED13 77 LED13 8 LED13 17 LED14 69 LED14 79 LED14 9 LED14 18 LED15 70 LED15 80 LED15 10 LED15 20 LED16 74 LED16 81 LED16 11 LED16 21 CLKIN 33 CLKI 35利用ByteBlaster下载电缆把数字频率计项目以JATG方式下载到EDA实验板的EPM7128SLC84器件中.在编程进程中,若器件或电缆或电源有问题,则会产生错误警告信息.(4)频率测量在CLKO输入端加上不同的时钟信号,按照数字频率计上的显示植,观察测得的频率是不是准确三、选做部份:4位乘法器的设计1.乘法控制器的的设计(1)控制器的ASM图:(2)控制器的VHDL语言程序:END mulcon;ARCHITECTURE one OF mulcon ISSIGNAL current_state,next_state:BIT_VECTOR(1 DOWNTO 0);CONSTANT s0:BIT_VECTOR(1 DOWNTO 0):="00";CONSTANT s1:BIT_VECTOR(1 DOWNTO 0):="01";CONSTANT s2:BIT_VECTOR(1 DOWNTO 0):="10";CONSTANT s3:BIT_VECTOR(1 DOWNTO 0):="11";BEGINcom1:PROCESS(current_sTA TE,start,i4)BEGINCASE current_state ISWHEN s0=>IF(start='1')THEN next_state<=S1;ELSE next_state<=s0;END IF;WHEN s1=>next_state<=s2;WHEN s2=>next_state<=s3;WHEN s3=>IF(i4='1')THEN next_state<=s0;ELSE next_state<=s2;END IF;END CASE;END PROCESS com1;com2:PROCESS(current_state,bi)BEGINCASE current_state ISWHEN s0=>endd<='1';clr<='1';ca<='0';cb1<='0';cb0<='0';cm1<='0';cm0<='0';cc<='0';WHEN s1=>endd<='0';clr<='0';ca<='1';cb1<='1';cb0<='1';cm1<='0';cm0<='0';cc<='0';WHEN s2=>IF(bi='1')THEN endd<='0'; clr<='1';ca<='0';cb1<='0';cb0<='0';cm1<='1';cm0<='1';cc<='1';ELSE endd<='0'; clr<='1';ca<='0';cb1<='0';cb0<='0';cm1<='0';cm0<='0';cc<='1';END IF;WHEN s3=>endd<='0';clr<='1';ca<='0';cb1<='0';cb0<='1';cm1<='0';cm0<='1';cc<='0';END CASE;END PROCESS com2;reg:PROCESS(clk)BEGINIF clk='1' AND clk'EVENT THENcurrent_state<=next_state;END IF;END PROCESS reg;END;(3)控制器的仿真时序图(附原始记录)2.顶层原理图3.顶层原理图仿真结果(附原始记录)四、实验体会;(实验中碰到什么问题?如何解决?)。

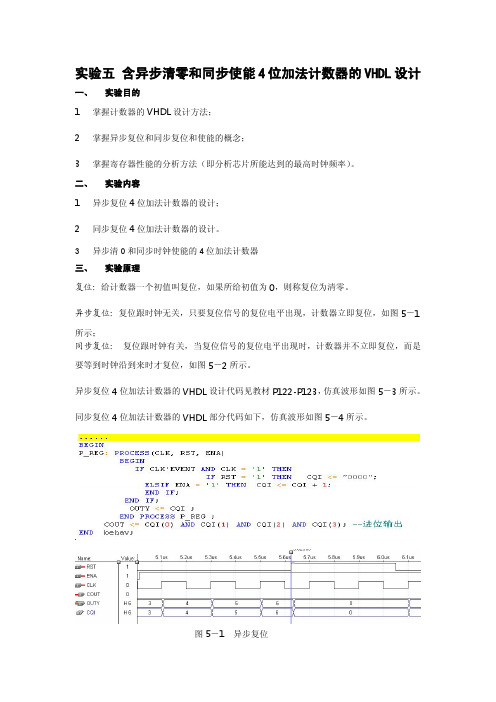

实验五含异步清零和同步使能4位加法计数器的VHDL设计一、实验目的1掌握计数器的VHDL设计方法;2掌握异步复位和同步复位和使能的概念;3掌握寄存器性能的分析方法(即分析芯片所能达到的最高时钟频率)。

二、实验内容1异步复位4位加法计数器的设计;2同步复位4位加法计数器的设计。

3异步清0和同步时钟使能的4位加法计数器三、实验原理复位:给计数器一个初值叫复位,如果所给初值为0,则称复位为清零。

异步复位:复位跟时钟无关,只要复位信号的复位电平出现,计数器立即复位,如图5-1所示;同步复位:复位跟时钟有关,当复位信号的复位电平出现时,计数器并不立即复位,而是要等到时钟沿到来时才复位,如图5-2所示。

异步复位4位加法计数器的VHDL设计代码见教材P122-P123,仿真波形如图5-3所示。

同步复位4位加法计数器的VHDL部分代码如下,仿真波形如图5-4所示。

.图5-1异步复位图5-2同步复位图5-3异步复位计数器仿真波形图5-4同步复位计数器仿真波形四、实验步骤(一)异步复位4位加法计数器的设计1建立一个设计工程,工程名为CNT4B;2打开文本编辑器,建立一个VHDL设计文件,其VHDL代码见教材P164中的例6-20,文件名存为CNT4B.VHD。

注意文件的扩展名要选为.vhd,而且要求工程名、文件名和设计实体名必须相同。

3选器件:ACEX1K,EP1K30TC144-3(旧)或Cyclone,EP3C40Q240C8目标芯片。

4编译;5建立波形文件,然后保存,其文件名必须与工程名一致;【波形设置:①设置仿真时间为10us:②设置输入信号的波形:时钟周期设置为200ns,其他输入信号的波形设置参看图6-3。

】6仿真,观察输出波形是否正确;7时序分析:分析芯片所能达到的最高时钟频率。

【打开时序分析器,然后执行菜单命令:analysis/register performance/start,可以看到最高时钟频率为100.00MHZ】(二)同步复位4位加法计数器的设计8建立一个设计工程,工程名为CNT4B_SYS;9打开文本编辑器,建立一个VHDL设计文件,其VHDL代码参看异步计数器代码和实验原理中的参考代码,文件名存为CNT4B_SYS.VHD。

数字逻辑电路大型实验报告姓名指导教师专业班级学院信息工程学院提交日期一、实验目的学习用FPGA实现数字系统的方法二、实验内容1.FPGA, Quartus II 和VHDL使用练习2.四位数字频率计的设计三、四位数字频率计的设计1.工作原理当系统正常工作时,8Hz信号测频控制信号发生器进行信号的变换,产生计数信号,被测信号通过信号整形电路产生同频率的矩形波,送入计数模块,计数模块对输入的矩形波进行计数,将计数结果送入锁存器中,保证系统可以稳定显示数据,显示译码驱动电路将二进制表示的计数结果转换成相应的能够在七段数码显示管上可以显示的十进制结果。

在数码显示管上可以看到计数结果。

工作原理图如下:2.设计方案1) 整形电路:整形电路是将待测信号整形变成计数器所要求的脉冲信号2)控制信号产生器(分频电路):用8Hz时钟信号产生1Hz时钟信号、锁存器信号和cs信号3)计时器:采用级联的方式表示4位数4)锁存器:计数结束后的结果在锁存信号控制下锁存5)译码器:将锁存的计数结果转换为七段显示码3.顶层原理图(总图)注:①CLK1:8Hz时钟信号输入; CLKIN:待测信号输入;②显像时自左而右分别是个位、十位、百位、千位;③顶层原理图中:(1)consignal模块:为频率计的控制器,产生满足时序要求的三个控制信号;(2)cnt10模块:有四个,组成四位十进制(0000-1001)计数器,使计数器可以从0计数到9999;(3)lock模块:有四个,锁存计数结果;(4)decoder模块:有四个,将8421BCD码的锁存结果转换为七段显示码。

4.底层4个模块(控制信号产生模块,十进制计数器模块,锁存器模块,译码模块)的仿真结果。

cnt10模块(十进制计数器模块):输入:CLK:待测量的频率信号(时钟信号模拟);CLR:清零信号,当clr=1时计数器清零,输出始终为0000,只有当clr=0时,计数器才正常计数CS:闸门信号,当cs=1时接收clk计数,当cs=0时,不接收clk,输出为0;输出:co:进位信号,图中,在1001(9)的上方产生一个进位信号0,其余为1。

目录一、设计任务与要求 (2)二、总体框图 (2)三、选择器件 (3)四、功能模块 (3)五、总体设计电路 (12)四位十进制频率计一、设计任务与要求1、用大规模可编程器件设计一个数字频率计,主要技术指标如下:1)频率测量范围:1Hz~10kHz。

2)数字显示位数:4位数字显示。

3)测量时间:t<=1.5s。

2、利用设计软件对EP1C12Q240C8器件进行设计输入设计仿真及器件编程,使其具备要求的逻辑功能。

3、计算参数,安装、调试电路。

4、画出完整电路图,写出设计总结报告。

5、选作内容:用数字频率计测量信号周期。

二、总体框图模块功能1)计数器:实现十进制计数功能。

2)锁存器:锁存信号。

3)频率信号控制发生器:输入端clk收到1Hz信号后,其输出端testen控制各个计数器的使能,clr_cnt控制各个计数器的清零,load控制锁存器内数据的输出。

4)译码驱动电路:将锁存器输出的BCD码译码,译码后输送到译码显示器件。

5)数码管显示:显示待测信号的频率值。

设计思路频率测量的基本原理是计算每秒钟内待测信号的脉冲个数。

这就要求testpl的计数使能信号tsten能产生一个1秒脉宽的周期信号,并对频率计的每一计数器cnt10的使能端ena进行同步控制。

当tsten为高电平"1"时,允许计数;为低电平"0"时停止计数,并保持其计数结果。

在停止计数期间,首先需要一个锁存信号load的上跳沿将计数器在前1 秒种的计数值锁存进16位锁存器reg16b中。

锁存信号之后,必须有一个清零信号clr_cnt对计数器进行清零,为下1 秒的计数操作做准备,然后由数码管显示出来。

三、选择器件电路中的所有器件都是VHDL语言设计生成的,所以无通用常规器件。

四、功能模块分频器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity div isport(clk_in:IN std_logic;div_outb,div_outc:out std_logic);end div;ARCHITECTURE a of div issignal fre_nb:integer range 0 to 25000000;signal fre_nc:integer range 0 to 100000;signal clk_tmpb:std_logic;signal clk_tmpc:std_logic;begindiv_outb<=clk_tmpb;div_outc<=clk_tmpc;process(clk_in) beginif falling_edge(clk_in) then if fre_nb>24999999 then fre_nb<=0;clk_tmpb<=not clk_tmpb; elsefre_nb<=fre_nb+1; end if;if fre_nc>99999 then fre_nc<=0;clk_tmpc<=not clk_tmpc; elsefre_nc<=fre_nc+1; end if; end if;end process;end a;逻辑功能:将50MH 分频为单位脉冲1Hz 和扫描频率。

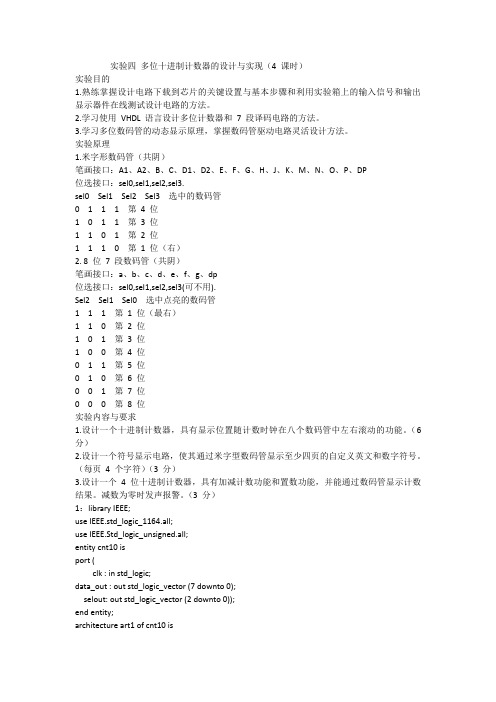

实验四多位十进制计数器的设计与实现(4 课时)实验目的1.熟练掌握设计电路下载到芯片的关键设置与基本步骤和利用实验箱上的输入信号和输出显示器件在线测试设计电路的方法。

2.学习使用VHDL 语言设计多位计数器和7 段译码电路的方法。

3.学习多位数码管的动态显示原理,掌握数码管驱动电路灵活设计方法。

实验原理1.米字形数码管(共阴)笔画接口:A1、A2、B、C、D1、D2、E、F、G、H、J、K、M、N、O、P、DP位选接口:sel0,sel1,sel2,sel3.sel0 Sel1 Sel2 Sel3 选中的数码管0 1 1 1 第4 位1 0 1 1 第3 位1 1 0 1 第2 位1 1 1 0 第1 位(右)2. 8 位7 段数码管(共阴)笔画接口:a、b、c、d、e、f、g、dp位选接口:sel0,sel1,sel2,sel3(可不用).Sel2 Sel1 Sel0 选中点亮的数码管1 1 1 第1 位(最右)1 1 0 第2 位1 0 1 第3 位1 0 0 第4 位0 1 1 第5 位0 1 0 第6 位0 0 1 第7 位0 0 0 第8 位实验内容与要求1.设计一个十进制计数器,具有显示位置随计数时钟在八个数码管中左右滚动的功能。

(6 分)2.设计一个符号显示电路,使其通过米字型数码管显示至少四页的自定义英文和数字符号。

(每页4 个字符)(3 分)3.设计一个4 位十进制计数器,具有加减计数功能和置数功能,并能通过数码管显示计数结果。

减数为零时发声报警。

(3 分)1:library IEEE;use IEEE.std_logic_1164.all;use IEEE.Std_logic_unsigned.all;entity cnt10 isport (clk : in std_logic;data_out : out std_logic_vector (7 downto 0);selout: out std_logic_vector (2 downto 0));end entity;architecture art1 of cnt10 isbeginprocess(clk)variable cnt1:integer range 0 to 9; beginif clk'event and clk='1' thencnt1:=cnt1+1;if cnt1>9 thencnt1:=0;end if;end if;case cnt1 iswhen 0 => data_out <= "11111100"; -- 0 when 1 => data_out <= "01100000"; -- 1 when 2 => data_out <= "11011010"; -- 2 when 3 => data_out <= "11110010"; -- 3 when 4 => data_out <= "01100110"; -- 4 when 5 => data_out <= "10110110"; -- 5 when 6 => data_out <= "10111110"; -- 6 when 7 => data_out <= "11100000"; -- 7 when 8 => data_out <= "11111100"; -- 8 when 9 => data_out <= "11101110"; -- 9 when others => NULL;end case;end process;process(clk)variable cntsel:integer range 0 to 13; beginif clk'event and clk='1' then cntsel:=cntsel+1;if cntsel>13 thencntsel:=0;end if;end if;case cntsel iswhen 0 => selout <= "111";when 1 => selout <= "110";when 2 => selout <= "101";when 3 => selout <= "100";when 4 => selout <= "011";when 5 => selout <= "010";when 6 => selout <= "001";when 7 => selout <= "000";when 8 => selout <= "001";when 9 => selout <= "010";when others => NULL;end case;end process;end art1;2:Library IEEE;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Entity miguan isport( clk : in std_logic;WX : out std_logic_vector (3 downto 0);DX : out std_logic_vector (15 downto 0)); End entity miguan;Architecture bhv of miguan isType state is(st0,st1,st2,st3);Signal current_state:state :=st0;Signal next_state:state;Signal shu1 : integer range 0 to 3;Signal shu2 : std_logic_vector(13 downto 0); Signal A,B,C,D:std_logic_vector(15 DOWNTO 0); Beginprocess (clk) isBeginIf (clk'event and clk='1') thenshu2<=shu2+"00000000000001";If shu2="11111111111111"thencurrent_state<=NEXT_STATE;elsecurrent_state<=current_state;End if;End if;End process;Process (current_state)BeginCase current_state iswhenst0=>A<="0110101000000000";--xB<="0000000011110000";--lC<="1000010000011110";--dD<="0001000110111011";--sNEXT_STATE<=ST1;whenst1=>A<="0000000011111100";--UB<="1000010000000011";--TC<="0001000111110011";--ED<="0011000111000111";--RNEXT_STATE<=ST2;whenst2=>A<="0000000011111111";--0B<="0001000111111011";--6C<="0000000000001100";--1D<="0001000111111111";--8NEXT_STATE<=st3;whenst3=>A<="0001000111111011";--6B<="1001010110000000";--4C<="0001000110111011";--5D<="0000000000001100";--1NEXT_STATE<=ST0;End case;End process;Process (clk) isBeginif rising_edge(clk) thenif shu1>3 thenshu1<=0;elseshu1<=shu1+1;end if;case shu1 isWHEN 0 =>WX<="1110";DX<=A;WHEN 1 =>WX<="1101";DX<=B;WHEN 2 =>WX<="1011";DX<=C;WHEN 3 =>WX<="0111";DX<=D;End case;End if;End process;End architecture bhv;3:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity wybcount4 isport(count_clk,saopin_clk,en,load,reset,add_sub:in std_logic;data_in3:in std_logic_vector(3 downto 0);--Left1data_in2:in std_logic_vector(3 downto 0);data_in1:in std_logic_vector(3 downto 0);data_in0:in std_logic_vector(3 downto 0);--Right1duanxuan:out std_logic_vector(7 downto 0);--duan xuansel:out std_logic_vector(1 downto 0);--wei xuanbell:out std_logic);end entity wybcount4;architecture beh of wybcount4 isconstant num0:std_logic_vector:="01111110";constant num1:std_logic_vector:="00001100";constant num2:std_logic_vector:="10110110";constant num3:std_logic_vector:="10011110";constant num4:std_logic_vector:="11001100";constant num5:std_logic_vector:="11011010";constant num6:std_logic_vector:="11111010";constant num7:std_logic_vector:="00001110";constant num8:std_logic_vector:="11111110";constant num9:std_logic_vector:="11011110";function number(x:std_logic_vector) return std_logic_vector is begincase x iswhen "0000" => return num0;when "0001" => return num1;when "0010" => return num2;when "0011" => return num3;when "0100" => return num4;when "0101" => return num5;when "0110" => return num6;when "0111" => return num7;when "1000" => return num8;when "1001" => return num9;when others =>return "00000000";end case;end number;signal Q3:std_logic_vector(3 downto 0);--zhong jian zhisignal Q2:std_logic_vector(3 downto 0);signal Q1:std_logic_vector(3 downto 0);signal Q0:std_logic_vector(3 downto 0);beginprocess(count_clk,reset,en,load,add_sub) isbegin--counter10IF reset = '0' THENQ0<=(OTHERS => '0');Q1<=(OTHERS => '0');Q2<=(OTHERS => '0');Q3<=(OTHERS => '0');ELSIF rising_edge(count_clk) THENif en='0' thenif load='0' thenQ0<=data_in0;Q1<=data_in1;Q2<=data_in2;Q3<=data_in3;elsif add_sub='0' then--addQ0<=Q0+1;if Q0>=9 thenQ0<="0000";Q1<=Q1+1;if Q1>=9 thenQ1<="0000";Q2<=Q2+1;if Q2>=9 thenQ2<="0000";Q3<=Q3+1;if Q3>=9 thenQ3<="0000";end if;end if;end if;end if;else--subQ0<=Q0-1;if Q0<=0 thenQ0<="1001";Q1<=Q1-1;if Q1<=0 thenQ1<="1001";Q2<=Q2-1;if Q2<=0 thenQ2<="1001";Q3<=Q3-1;if Q3<=0 thenQ3<="1001";end if;end if;end if;end if;end if;end if;END IF;if (Q0="0000" and Q1="0000" and Q2="0000" and Q3="0000") then bell<='1';elsebell<='0';end if;end process;process(saopin_clk) is--sao pin xian shivariable qq:std_logic_vector(0 to 1);beginif (saopin_clk'event and saopin_clk='1') thenif qq<=3 then qq:=qq+1;else qq:="00";end if;end if;case qq iswhen "00" => sel<="00";duanxuan<=number(Q0);when "01" => sel<="01";duanxuan<=number(Q1);when "10" => sel<="10";duanxuan<=number(Q2);when "11" => sel<="11";duanxuan<=number(Q3);end case;end process;end architecture beh;。

电子设计自动化实验实验名称综合性实验二、硬件描述语言的层次化设计实验设备(1) EDA实验箱 ( 型号 ), ( 2)计算机 , ( 3) EDA软件( QuartusII )实验目的1、熟悉 EDA软件( QuartusII)的硬件描述语言输入设计方法;2、掌握 VHDL语言的层次化设计方法和仿真分析方法;3、了解功能仿真、时序仿真和时序参数分析的意义。

实验内容1、用 VHDL语言完成 4 位十进制计数器、 4 位锁存器、测频控制器的设计,包括编译、综合、仿真;**2、采用层次化设计的方法,用VHDL语言的元件例化语句写出 4 位十进制频率计的顶层文件,并分别给出其测频功能和时序仿真分析波形图,并加以分析;**3、用 EDA实验箱进行硬件验证,并分析测量结果; 建议硬件测试实验电路采用电路结构,待测信号F_IN 接 clock0 ;测频控制时钟CLK接 clock2 ; **4、在 2 基础上将其扩展为8 位十进制频率计,或带译码输出的 4 位十进制频率计。

实验报告要求根据以上实验内容写出实验报告:1、简述 4 位频率计模块的工作原理及其设计、编译、仿真分析过程;2、给出模块设计文件、仿真测试文件、仿真结果波形图及其分析报告;3、简述硬件验证过程和验证结果。

1、简述 4 位频率计模块的工作原理根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为 1 秒的对输入信号脉冲计数允许的信号; 1 秒计数结束后,计数值锁入锁存器的锁存信号和为下一测频计数周期作准备的计数器清0 信号。

这 3 个信号可以由一个测频控制信号发生器产生,即TESTCTL,它的设计要求是,TESTCTL的计数使能信号CNT_EN能产生一个1 秒脉宽的周期信号,并对频率计的每一计数器 CNT10的 ENA使能端进行同步控制。

当CNT_EN高电平时,允许计数;低电平时停止计数,并保持其所计的脉冲数。

在停止计数期间,首先需要产生一个锁存信号LOAD,在该信号上升沿时,将计数器在前1 秒钟的计数值锁存进各锁存器REG4B中,并由外部的7 段译码器译出,显示计数值。

设计报告课程名称在系统编程技术任课教师设计题目四位十进制频率计设计班级姓名学号日期一、题目分析㈠主要指标和要求1.设计4位十进制频率计,学习较复杂的数字系统设计方法;2.深入学习数字系统设计的方法与步骤;3.用元件例化语句写出频率计的顶层文件;4.用VHDL硬件描述语言进行模块电路的设计;5.设计硬件要求:PC机,操作系统为Windows2000/XP,本课程所用系统均为Quartus II设计平台,GW48系列SOPC/EDA实验开发系统。

㈡原理工作说明:1、测频原理若某一信号在T秒时间里重复变化了N 次,则根据频率的定义可知该信号的频率fs 为:fs=N/T 通常测量时间T取1秒或它的十进制时间。

频率总体计方框图如下:图(1)频率总体计方框图(1)、时基T 产生电路:提供准确的计数时间T。

晶振产生一个振荡频率稳定的脉冲,通过分频整形、门控双稳后,产生所需宽度的基准时间T的脉冲,又称闸门时间脉冲。

注意:分频器一般采用计数器完成,计数器的模即为分频比。

(2)、计数脉冲形成电路:将被测信号变换为可计数的窄脉冲,其输出受闸门脉冲的控制。

(3)、计数显示电路:对被测信号进行计数,显示被测信号的频率。

计数器一般采用多位10 进制计数器;控制逻辑电路控制计数的工作程序:准备——计数——显示——复位——准备下一次测量。

2、具体实现根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1秒的对输入信号脉冲计数允许的信号;1秒计数结束后,计数值锁入锁存器的锁存信号和为下一测频计数周期作准备的计数器清0信号。

这3个信号可以由一个测频控制信号发生器产生,即图(a)中的TESTCTL,它的设计要求是,TESTCTL的计数使能信号CNT_EN 能产生一个1秒脉宽的周期信号,并对频率计的每一计数器CNT10的ENA使能端进行同步控制。

当CNT_EN高电平时,允许计数;低电平时停止计数,并保持其所计的脉冲数。

在停止计数期间,首先需要产生一个锁存信号LOAD,在该信号上升沿时,将计数器在前1秒钟的计数值锁存进各锁存器REG4B中,并由外部的7段译码器译出,显示计数值。

EDA实验报告实验三、4位十进制的频率计设计班级115学号姓名日期2010.11.2一、实验目的1、设计4位十进制频率计,学习较复杂的数字系统设计方法,熟悉对Quartus II 软件的使用。

2、用4位十进制计数器对用户输入时钟UCLK进行记数二、实验原理:根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1秒的对输入信号脉冲计数允许的信号;1秒计数结束后,计数值被锁入锁存器,计数器清零,为下一测频计数周期作准备。

这3个信号可以由一个测频控制信号发生器产生下图中的TESTCTL,它的设计要求是:TESTCTL的计数使能信号CNT_EN能产生一个1秒脉宽的周期信号,并对频率计的每一计数器CNT10的ENA使能端进行同步控制。

当CNT_EN高电平时,允许计数;低电平时停止计数,并保持其所计的脉冲数。

在停止计数期间,首先需要一个锁存信号LOAD的上跳沿将计数器在前1秒钟的计数值锁存进各锁存器REG4B中,并由外部的7段译码器译出,显示计数值。

设置锁存器的好处是:显示的数据稳定,不会由于周期性的清零信号而不断闪烁。

锁存信号之后,必须有一清零信号RST_CNT对计数器进行清零,为下1秒钟的计数操作作准备。

4位十进制频率计设计的原理框图四、实验步骤及结果五、1破解软件2、新建工程3、程序输入及编译新建文件并输入程序并进行编译。

实验VHDL程序代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY EX10 ISPORT (clk1Hz : IN STD_LOGIC; -- 1 Hz clockuclk : IN STD_LOGIC; -- user clock inputled0 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); led1 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); led2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); led3 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);p_cnt_en : OUT STD_LOGIC; -- IO01p_rst_cnt: OUT STD_LOGIC; -- IO00p_load : OUT STD_LOGIC -- IO02);END EX10;ARCHITECTURE behv OF EX10 ISCOMPONENT cnt10PORT (clk : IN STD_LOGIC;rst : IN STD_LOGIC;ena : IN STD_LOGIC;outy: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);cout: OUT STD_LOGIC);END COMPONENT;COMPONENT reg4bPORT (load: IN STD_LOGIC;din : IN STD_LOGIC_VECTOR(3 DOWNTO 0);dout: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;COMPONENT testctlPORT (clkk : IN STD_LOGIC;cnt_en : OUT STD_LOGIC;rst_cnt: OUT STD_LOGIC;load : OUT STD_LOGIC);END COMPONENT;SIGNAL cnt_en : STD_LOGIC;SIGNAL rst_cnt : STD_LOGIC;SIGNAL load : STD_LOGIC;SIGNAL dout0, dout1, dout2, dout3: STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL cout0, cout1, cout2, cout3: STD_LOGIC;BEGINp_cnt_en <= cnt_en ;p_rst_cnt <= rst_cnt;p_load <= load ;u_testctl:testctl PORT MAP (clkk => clk1Hz ,cnt_en => cnt_en ,rst_cnt => rst_cnt,load => load); u_cnt10_0:cnt10 PORT MAP (clk => uclk ,rst => rst_cnt,ena => cnt_en ,outy => dout0 ,cout => cout0 );u_cnt10_1:cnt10 PORT MAP (clk => cout0 ,rst => rst_cnt,ena => cnt_en ,outy => dout1 ,cout => cout1 );u_cnt10_2:cnt10 PORT MAP (clk => cout1 ,rst => rst_cnt,ena => cnt_en ,outy => dout2 ,cout => cout2 );u_cnt10_3:cnt10 PORT MAP (clk => cout2 ,rst => rst_cnt,ena => cnt_en ,outy => dout3 ,cout => cout3 );u_reg4b_0:reg4b PORT MAP (load => load ,din => dout0, dout => led0);u_reg4b_1:reg4b PORT MAP (load => load ,din => dout1,dout => led1);u_reg4b_2:reg4b PORT MAP (load => load ,din => dout2,dout => led2);u_reg4b_3:reg4b PORT MAP (load => load ,din => dout3,dout => led3);END behv;TESTCTL.VHD 程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY testctl ISPORT (clkk : IN STD_LOGIC;cnt_en : OUT STD_LOGIC;rst_cnt: OUT STD_LOGIC;load : OUT STD_LOGIC);END testctl;ARCHITECTURE behv OF testctl IS SIGNAL div2clk: STD_LOGIC;BEGINPROCESS(clkk)BEGINIF clkk'EVENT AND clkk = '1' THENdiv2clk <= NOT div2clk;END IF;END PROCESS;PROCESS(clkk, div2clk) BEGINIF clkk = '0' AND div2clk = '0' THENrst_cnt <= '1';ELSErst_cnt <= '0';END IF;load <= NOT div2clk;cnt_en <= div2clk;END PROCESS;END behv;LIBRARY IEEE;USEIEEE.STD_LOGIC_1164.ALL; USEIEEE.STD_LOGIC_UNSIGNED. ALL;ENTITY cnt10 ISPORT (clk : IN STD_LOGIC;rst : IN STD_LOGIC;ena : IN STD_LOGIC; outy: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);cout: OUT STD_LOGIC);END cnt10;ARCHITECTURE behv OF cnt10 ISSIGNAL cqi: STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(clk, rst, ena) BEGINIF rst = '1' THENcqi <= "0000";cout <= '0';ELSIF clk'EVENT AND clk = '1' THENIF ena = '1' THENIF cqi = "1001" THENcqi <= "0000";cout <= '1';ELSEcqi <= cqi + 1;cout <= '0';END IF;END IF;END IF;outy <= cqi;END PROCESS;END behv;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY reg4b ISPORT (load: IN STD_LOGIC;din : IN STD_LOGIC_VECTOR(3 DOWNTO 0); dout: OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END reg4b;ARCHITECTURE behv OF reg4b ISBEGINPROCESS(load)BEGINIF load'EVENT AND load = '1' THENdout <= din;END IF;END PROCESS;END behv;打开RTL图形时序仿真:打开“assignments”中的“assignments editor”打开EDA,装入模式10.根据EDA 管脚进行指定保存,并下载“sof”文件到EDA启动EDA软件。

四川理工学院小组成员:梁天德、傅青云、杨文科指导老师:徐金龙设计一个4位十进制数字显示的数字式频率计,用来测量输入信号的频率。

基本要求如下:(1)4位十进制数字显示的数字式频率计,其频率测量范围为1Hz~9999kHz;(2)有1~9999Hz和10~9999kHz两个量程,并用LED指示;(2)频率计能根据测试信号的频率进行量程能够自动转换。

(3)采用记忆显示方式,即在计数过程中不显示测试数据,待计数过程结束后显示测试结果,并将此结果保持到下一次计数结束,显示时间不小于1S;当输入的信号大于9999kHz 时,输出显示全H。

方案:频率的定义:信号在1秒内的变化次数。

对信号进行放大、整形,以方波的形式作为CPLD计数的输入。

需要产生1秒的阀门计数信号,控制CPLD的计数时间,可由8MHz时钟信号分频得到。

使用量程1(1~9999Hz)时,直接对方波信号进行计数,1秒内计数的到的值就是信号的频率,并在四位数码管上显示。

使用量程2(10~9999kHz)时,需要对信号进行1k分频,在1秒内对分频后的信号进行计数,计数的值就是当前信号的频率除以1k,并用四位数码管显示,注意当前量程单位是kHz,用LED指示。

量程自动切换:系统启动默认为量程1,在以后运行中,可以通过当前的计数值、量程、溢出标识来判断下一次应选择的计数的分频比、量程状态指示、绝对溢出显示,可通过组合逻辑来实现。

硬件电路信号放大整形8MHz系统时钟产生EPM7128SLC84-15 管脚配置量程指示4位数码管显示ISP下载系统电源软件部分(max+plus2环境)整体框架:信号输入,时钟输入,计数、量程控制核心,量程输出,4位数码管动态输出核心。

下面解剖计数、量程控制核心时钟信号。

被测信号输入:根据量程选择是否进行1K分频频率计计数核心:由4个BCD计数器74160和4个锁存器构成,注意虽然计数器清零信号和锁存器锁存信号都是1Hz,但是清零信号要比锁存信号晚一个时钟周期(1/8MHz)。

实验五 4位十进制频率计设计 一、实验目的:设计4位十进制频率计,学习较复杂的数字系统设计方法。 二、原理说明: 根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1秒的对输入信号脉冲计数允许的信号;1秒计数结束后,计数值锁入锁存器的锁存信号和为下一测频计数周期作准备的计数器清0信号。这清0个信号可以由一个测频控制信号发生器产生,即图5-1中的TESTCTL,它的设计要求是,TESTCTL的计数使能信号CNT_EN能产生一个1秒脉宽的周期信号,并对频率计的每一计数器CNT10的EN使能端进行同步控制。当CNT_EN高电平时,允许计数;低电平时停止计数,并保持其所计的脉冲数。在停止计数期间,首先需要一个锁存信号LOAD的上跳沿将计数器在前1秒钟的计数值锁存进各锁存器REG4B中,并由外部的7段译码器译出,显示计数值。设置锁存器的好处是,显示的数据稳定,不会由于周期性的清零信号而不断闪烁。锁存信号之后,必须有一清零信号RST_CNT对计数器进行清零,为下1秒钟的计数操作作准备。 【例5-1】10进制计数器,用于计算分频结果,并连接数码管显示。 module cnt10d(clk,rst,en,cq,cout); input clk; input rst; input en; output[3:0] cq; output cout; reg[3:0] cq; reg cout; always@(posedge clk or posedge rst) begin if(rst) cq<=4'b0000; else if(en) begin if(cq<9) begin cq<=cq+1'b1;cout<=1'b0; end else begin cq<=4'b0000; cout<=1'b1; end end end endmodule 【例5-2】--测频控制器,使得频率计能自动测频 module testctl(clkk,cnt_en,rst_cnt,load); input clkk; // 1HZ output cnt_en; output rst_cnt; output load;

reg div2clk; wire cnt_en; reg rst_cnt; wire load; always@(posedge clkk) div2clk<=~div2clk; always @(clkk or div2clk) begin if(!clkk & !div2clk) rst_cnt<=1'b1; else rst_cnt<=1'b0; end assign load = ~div2clk; assign cnt_en = div2clk; endmodule 【例5-3】锁存器,将频率计的每位数锁存后输出

module reg4(clk,cq,led ); input clk; input[3:0] cq; output[3:0] led; reg[3:0] led; always@(posedge clk) led<=cq; endmodule

[例5-4] 用原理图方式将各模块连接起来 也可以用.v文件实现系统组合。 三、 实验内容: 1、根据例5-1、例5-2、例5-3以及4位十进制频率计的工作原理写出频率计的顶层文件(或者原理图),并给出其测频时序波形,及其分析。在测试时候添加以下两个模块: (1)DE2上有两个时钟源,分别是(50MHZ ,PIN_N2),(27MHz,PIN_D13),编写一个分频模块,分别产生测频器的clk(8Hz)和 f_in(频率任意定)时钟,用于连接在DE2上进行测试。 module div27(clk2,Q2); input clk2; output Q2; reg Q2; reg [25:0] count; always@(posedge clk2) begin if(count==26999999) count<=0; else count<=count+1'b1; end always@(count) begin if(count==26999999) Q2<=1; else Q2<=0; end endmodule 上述为27MHZ分频为1HZ的代码 module div_50(Clk1,Q1); input Clk1; output Q1; reg Q1; reg [25:0] count; always @(posedge Clk1) begin if(count==49999) count<=0; else count<=count+1; end always@(count ) begin if(count==49999) Q1<=1; else Q1<=0; nd endmodule 上述为50MHZ分频为1000HZ 的代码 (2)编写数码显示模块led7s,用于显示频率计数的结果显示。 module decl7s(a,led7s); input[3:0]a; output[6:0]led7s; reg[6:0]led7s; always @ (a ) begin led7s={7{1'b0}}; begin case(a) 4'b0000:led7s[6:0]= 7'b1000000; 4'b0001:led7s[6:0]= 7'b1111001; 4'b0010:led7s[6:0]= 7'b0100100; 4'b0011:led7s[6:0]= 7'b0110000; 4'b0100:led7s[6:0]= 7'b0011001; 4'b0101:led7s[6:0]= 7'b0010010; 4'b0110:led7s[6:0]= 7'b0000010; 4'b0111:led7s[6:0]= 7'b1111000; 4'b1000:led7s[6:0]= 7'b0000000; 4'b1001:led7s[6:0]= 7'b0011000; default:led7s[6:0]= {7{1'b0}}; endcase end end endmodule 2、频率计设计硬件验证。编译、综合和适配频率计顶层设计文件,并编程下载进入目标器件中。 3、引脚锁定说明 信号 DE2器件 引脚名称 Clk,f_in( 自己定义锁定时钟) 27M时钟源 PIN_D13 50M时钟源 PIN_N2 Led7s1 数码显示管HEX0(显示个位) HEX0[0] PIN_AF10 HEX0[1] PI N_AB12 HEX0[2] PIN_AC12 HEX0[3] PIN_AD11 HEX0[4] PIN _AE11 HEX0[5] PIN_V14 HEX0[6] PIN_V13 Led7s2 数码显示管HEX1(显示十位) HEX1[0] PIN_V20 HEX1[1] PI N_V21 HEX1[2] PIN_W21 HEX1[3] PIN_Y22 HEX1[4] PIN _AA24 HEX1[5] PIN_AA23 HEX1[6] PIN_AB24 Led7s3 数码显示管HEX2(显示百位) HEX2[0] PIN_AB23 HEX2[1] PI N_V22 HEX2[2] PIN_AC25 HEX2[3] PIN_AC26 HEX2[4] PIN _AB26 HEX2[5] PIN_AB25 HEX2[6] PIN_Y24 Led7s4 数码显示管HEX3(显示千位) HEX3[0] PIN_Y23 HEX3[1] PI N_AA25 HEX3[2] PIN_AA26 HEX3[3] PIN_Y26 HEX3[4] PIN _Y25 HEX3[5] PIN_U22 HEX3[6] PIN_W24 Carry_out 溢出指示灯亮,可以作为扩大测量范围的接口,可接在发光二极管。 任意一个,如 LEDR17对应引脚PIN_AD12)

四、实验步骤 1、构建一个工程名为Cnt10d的工程。 (1)由File->New Project Wizard,弹出对话框,设置文件夹目录,Project名称。 暂无文件添加,按next,继续 根据DE2实验平台,选择FPGA目标器件为:Cyclone II 系列:EP2C35F672C6 仍然使用软件自带的综合仿真工具,所以按NEXT,继续 Project建立总结,按Finish完成 (2).输入Cnt10d的Verilog文本。由File->New,得如下对话框,选择Verilog HDL File,点击ok。将设计的Verilog程序输入,并存盘名为Cnt10d.v (3).由File->new,弹出对话框,选择other files->Vector Waveform File,将波形文件存盘 为Cnt10d.vwf。 (4).设定Cnt10d.v是目前的顶层文件。 (5).由Processing->start->start annlysis & elaboration对程序进行初步的分析 (6).双击波形文件下的空白区,得到如下对话框,点击Noder Finder,弹出一个对话框,单击List,选中Clk、en、rst几个端口,单击>_后,点击OK。由edit->end time ,设定仿真终止时间为1us, 选中Clk点击,设置周期是10ns。 (7).由assigments->settings,对仿真工具设定为功能仿真,并将激励文件调入。由Processing->generate functional simulation netlist,提取功能仿真的网表。由processing -> start simulation 进行功能仿真,并对结果进行分析。 (8).由assignments->settings,更改仿真器的设置为时序仿真:timing。由processing->start compile对设计进行全编译。再由processing -> start simulation 进行时序仿真,分析结果。 (9)仿照工程Cnt10d的设计方法,设计testctl、 reg4、 decl7s并仿真,得到仿真波形。设计div27、div_50,不用仿真。

2.用原理图方式将各模块连接起来,也可以用.v文件实现系统组合。 3.引脚锁定 4.检查无误后,下载到DE2板上 五、实验结果:1.相关波形见附件 2.下载到DE2板后,DE2板上显示的是1000,达到了目的要求。 六、思考题 将频率计扩展为8位十进制频率计,并在测频速度上给予优化,使其能测出更高的频率。 答:将Cnt10d和 reg4和decl7s三个模块分别都增加为八个,再按照对应的接口功能引脚对应锁定。要将输入的测试频率提高,改变分频器即可。