第6章S08输入输出接口

S08AW系列微控制器的I/O接口采用模块化设计方式,即输入/输出系统端口由许多标准模块组成。以S08AW60为例,其64-Pin封装的芯片端口包括PTA、PTB、PTC、PTD、PTE、PTF和PTG这7个I/O口,共54个通用I/O引脚。这些引脚大都与片上多种外围设备复用,如定时器模块、通信模块和键盘中断模块等。这些特殊外围设备模块的优先级比通用I/O接口的优先级高,因此当使能某个外围设备时,则与该复用管脚相关的输入/输出功能将被禁止。

本章主要介绍S08AW系列微控制器通用I/O端口的功能、设置和使用方法,以及按键和LED显示接口、输入/输出接口的设计例程等。

6.1S08 I/O端口原理

通用I/O端口又称并行数字I/O端口,用来实现微控制器与外部设备的信息交换,并完成控制和数据采集,是微控制器一个必不可少的基本组成部分。当一个MCU引脚作为通用I/O 端口时,应对该引脚的两个寄存器进行设置:一个是该引脚的方向寄存器,用来设定该引脚是用于输入还是输出;另一个是该引脚的数据寄存器,当用作输出时,应先将要输出的数据写入该数据寄存器,然后才能送到引脚上;当用作输入口时,引脚上的数据将先存入该数据寄存器,然后CPU再读该寄存器中已存入的数据。

设定MCU的某个引脚是输入还是输出的方向寄存器是PTxDD,PTxDD是方向寄存器的英文缩写名称,x代表A、B、C、D、E、F、G这八个端口之一。

6.1.1I/O端口引脚分布

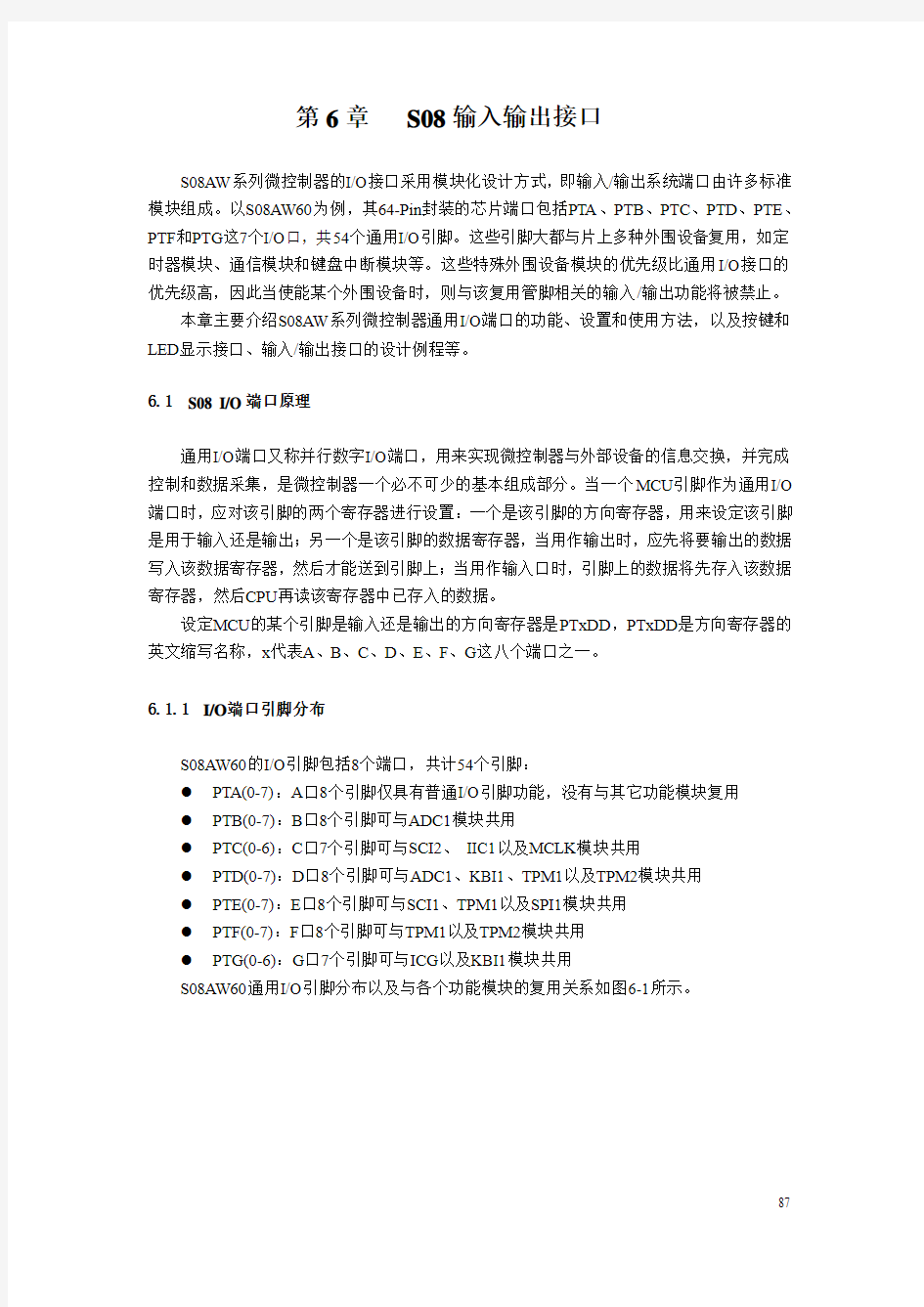

S08AW60的I/O引脚包括8个端口,共计54个引脚:

●PTA(0-7):A口8个引脚仅具有普通I/O引脚功能,没有与其它功能模块复用

●PTB(0-7):B口8个引脚可与ADC1模块共用

●PTC(0-6):C口7个引脚可与SCI2、IIC1以及MCLK模块共用

●PTD(0-7):D口8个引脚可与ADC1、KBI1、TPM1以及TPM2模块共用

●PTE(0-7):E口8个引脚可与SCI1、TPM1以及SPI1模块共用

●PTF(0-7):F口8个引脚可与TPM1以及TPM2模块共用

●PTG(0-6):G口7个引脚可与ICG以及KBI1模块共用

S08AW60通用I/O引脚分布以及与各个功能模块的复用关系如图6-1所示。

PTE4/SS1

图6-1通用I/O引脚与各个功能模块的复用关系

6.1.2I/O端口工作原理

S08AW60的通用I/O一般可通过设置相应的寄存器使其具有输入、输出、内部上拉选择、斜率控制及驱动强度控制等功能。

选择I/O端口工作方式的控制寄存器有PTxDD、PTxD、PTxPE、PTxSE、PTxDS等。其中PTxDD代表端口方向寄存器,PTxD代表端口数据寄存器,PTxPE代表内部上拉控制寄存器,PTxSE代表斜率控制寄存器,PTxDS代表驱动强度选择寄存器。关于上拉控制、斜率控制以及驱动强度选择寄存器将在后面介绍。

S08AW60MCU微控制器的双向可编程通用I/O(GPIO)中单个引脚的简化功能逻辑示意图参见图6-2。每个引脚有两个寄存器控制:数据寄存器PTxDn和数据传输方向寄存器PTxDDn,其中x代表端口名,如A、B、C、D、E、F、G,n代表该端口的第几位引脚,n=0,

1,2…7。例如PTAD1表示PTA端口引脚1的数据寄存器。

图6-2 双向GPIO原理示意图

1.数据方向寄存器PTxDDn

数据方向寄存器PTxDDn决定x端口各引脚是输入还是输出,各个端口的每一个引脚都对应数据方向寄存器中的一位。若PTxDDn=0,相应的x端口的n引脚作为输入引脚,读取PTxD 将返回该引脚值。当PTxDDn=1,相应x端口的n引脚作为输出引脚,读取PTxD 将返回最后一次写入PTxD的值。

每个端口由5~8个引脚组成。例如,对于A口的某个引脚PTA0,当设置PTADD0=0时,PTA0引脚作为普通输入引脚,可以将外部的高/低电平通过该引脚写入MCU内部;当PTADD0=1时,PTA0引脚作为普通输出引脚,MCU内部可以通过该引脚输出高电平或低电平。

另外,对于模拟功能和数字功能复用的引脚,模拟功能具有较高的优先级。当引脚复用为模拟功能,则该引脚数字功能被关闭,此时读该端口数据寄存器将返回0。当同时使能端口模拟功能和数字功能时,则模拟功能控制该引脚。例如,对于端口B的引脚,若同时使能ADC功能及通用I/O时,则ADC功能控制该端口引脚。

在应用程序设计时,欲将某端口的某个引脚设为输出,通常应先设置该端口的方向寄存器(即写入1),然后再向相应端口的数据寄存器PTxDn写入输出数据(0或1)。

例如:为了将A端口的Bit2位设为输出,可以使用汇编指令BSET:

BSET 2,PTADD ;通过向A口方向寄存器的Bit2位赋值1来使该位为输

;出功能。例如,原来PTADD=00000000B,执行此汇编语句

;后PTADD=00000100B

2.端口上拉电阻寄存器

在上拉寄存器PTxPE中,可设定该端口的某管脚是否使能内部上拉器件。如果并行输入/ 输出控制逻辑或任何外围设备功能将管脚配置为输出,上拉器件就会被禁止,这与对应的上拉寄存器位的状态无关。如果管脚由模拟功能控制,上拉器件同样会被禁止。

3. 斜率控制寄存器

在斜率控制寄存器PTxSE中,可设定该端口的某管脚是否使能斜率控制。该功能启动时,转换控制限制输出的转换速度。它起到的作用就是减少输出的波形在跳变沿时的过冲,使电压波形的上升或下降的斜率减少,变得平滑些。斜率控制寄存器对配置为输入的管脚没有任何影响。

4.驱动强度选择寄存器

在驱动强度选择寄存器PTxDS中,通过设置对应的位可以选择该管脚是高驱动强度或低驱动强度,高驱动时能够送出或吸收更大的电流。不过要注意的是:不能超出MCU送出或吸收电流的限制范围。通常引脚正常工作时的拉/灌电流在高驱动时为±10mA,低驱动强度为±2mA,极限值最大不超过25mA。

复位后所有与I/O共用的外围设备功能被禁止,各管脚被默认配置为输入(PTxDDn = 0),斜率控制使能(PTxSEn = 1)、选定低驱动强度(PTxDSn = 0)、内部上拉被禁止(PTxPEn = 0)。

6.2S08AWI/O端口设置

S08AW60MCU的每个端口除了可作为通用I/O外,还分别具有专用I/O功能,可以根据需要选择。有的端口启动专用功能后,通用I/O功能将自动关闭;有的端口专用功能只占用部分引脚,其余引脚的I/O功能仍可以正常工作。例如PTB端口就可以设置为A/D输入功能。此外,有的引脚仅具有单向输入或输出功能。具体情况取决于专用功能的特殊要求以及对I/O的设置,可参见其它章节。这里分别介绍各个I/O接口的并行通用数字I/O功能和设置方法。

6.2.1 A口相关寄存器

1.端口A数据寄存器和数据方向寄存器

A口数据寄存器PTAD及数据方向寄存器PTADD如表6-1和表6-2所示。PTAD的英文全称是Port A Data Register,PTADD的英文全称是Port A Data Direction Register。

表6-1 A口数据寄存器

复位默认值:00000000B

当A口被设为输入端口时,读取PTAD寄存器将返回引脚的逻辑电平值;A设为输出端口时,读取PTAD寄存器将返回上一次写入该寄存器的值,写入的数据将被锁存在PTAD 中。

表6-2 A口数据方向寄存器

复位默认值:00000000B

方向寄存器的这些位控制着A 端口管脚的数据传输。复位后,默认PTADD寄存器各位为0,此时为高阻输入状态,上拉功能被禁止。

2.端口A控制寄存器(PTAPE,PTASE,PTADS)

一个端口的控制寄存器通常包括该端口的输入功能时的上拉电阻使能、输出功能时的压摆率使能(又称斜率使能)和输出功能时的强弱驱动选择这三种选择。

A端口上拉使能寄存器PTAPE(Port A Pin Internal Pullup Enable Control Registers)如表6-3所示。当端口A作为输入引脚时,PTAPE中的各位控制着相应引脚内部上拉是否使能;当端口A作为输出引脚时,无论该寄存器各位处于何种状态,内部上拉均关闭。

表6-3 A口上拉使能控制寄存器

复位默认值:00000000B

PTAPE[7:0]—上拉使能端口A

1:内部上拉使能。

0:内部上拉关闭。

A端口斜率控制寄存器PTASE(Port A Pin Output Slew Rate Control Enable Registers)如表6-4所示。当端口A作为输出引脚时,PTASE中的各位控制各相关PTA管脚是否使能输出斜率;当端口A作为输入引脚时,无论该寄存器各位处于何种状态均不会产生任何影响。

表6-4 A口斜率使能控制寄存器

复位默认值:00000000B

PTASE[7:0]—斜率使能端口A

1:输出斜率控制被使能。

0:输出斜率控制被禁止。

A端口驱动强度选择寄存器PTADS(Port A Pin Output Drive Strength Selection Control Registers)如表6-5所示。当端口A作为输出引脚时,PTADS中的各位可设定各相关PTA管脚是选择低输出驱动还是高输出驱动;当端口被配置为输入引脚时,该寄存器不会产生任何影响。

表6-5 A口驱动强度选择寄存器

复位默认值:00000000B

PTADS[7:0]—端口A驱动强度端口选择

1:选择高输出驱动强度。

0:选择低输出驱动强度。

6.2.2B口相关寄存器

1.端口B数据及方向寄存器

B口既可作为普通输入或输出口使用,也可作为ADC模块来使用。任何一个引脚的ADC 输入使能均会使该管脚的通用I/O功能被禁止。B口的数据寄存器PTBD及方向寄存器PTBDD分别如表6-6和表6-7所示:

表6-6 B口数据寄存器

复位默认值:00000000B

表6-7 B口方向寄存器

复位默认值:00000000B

当B作为输入端口时,读取PTBD寄存器将返回引脚的逻辑电平值;B为输出端口时,读取PTBD寄存器将返回上一次写入该寄存器的值,写入的数据将被锁存。方向寄存器PTBDD的这些位控制着B 端口管脚的数据传输方向以及被PTBD读取的数据内容。复位后,默认PTBDD寄存器各位为0,此时为高阻输入状态,上拉被禁止。

2.端口B控制寄存器(PTBPE,PTBSE,PTBDS)

B端口上拉使能寄存器如表6-8所示。当端口B作为输入引脚时,PTBPE中的各位控制着相应引脚的内部上拉是否使能;当端口B作为输出引脚时,无论PTBPE寄存器各位何种状态,内部上拉均被关闭。

表6-8 B口上拉使能控制寄存器

复位默认值:00000000B

PTBPE[7:0]—端口B上拉使能

1:内部上拉使能。

0:内部上拉关闭。

B端口斜率使能寄存器如表6-9所示。当端口B作为输出引脚时,PTBSE中的各位可设定相关的PTB管脚是否使能输出斜率控制;当端口B作为输入引脚时,无论PTBSE寄存器各位处于何种状态,均不产生任何影响。

表6-9 B口斜率使能控制寄存器

复位默认值:00000000B

PTBSE[7:0]—斜率使能端口B

1:输出斜率控制被使能。

0:输出斜率控制被禁止。

B端口驱动强度选择寄存器如表6-10所示。当端口B作为输出引脚时,PTBDS中的各位可设定相关的PTB管脚是否选择低输出驱动或高输出驱动;当端口B作为输入引脚时,

这些位不会产生任何影响。

表6-10 B口驱动强度选择寄存器

复位默认值:00000000B

PTBDS[7:0]—端口B驱动强度端口选择

1:选择的高输出驱动强度。

0:选择的低输出驱动强度。

6.2.3 C口相关寄存器

1.端口C数据及方向寄存器

C口既可作为普通输入或输出口使用,也可以与SCI2、IIC及MCLK模块共享引脚。这些功能模块中的任一个使能,都将会使通用I/O口的数据方向寄存器失去作用。其数据寄存器PTCD及方向寄存器PTCDD分别如表6-11和表6-12所示:

表6-11 C口数据寄存器

复位默认值:00000000B

表6-12 C口方向寄存器

复位默认值:00000000B

当C作为输入端口时,读取PTCD寄存器将返回引脚的逻辑电平值;当C作为输出端口时,读取PTCD寄存器将返回上一次写入该寄存器的值,写入的数据将被锁存。方向寄存器的这些位控制着C 端口管脚的数据传输方向以及从PTCD读取的数据内容。复位后,默认PTCDD寄存器各位为0,且为高阻输入状态,上拉被禁止。

2.端口C控制寄存器(PTCPE,PTCSE,PTCDS)

C端口上拉使能控制寄存器如表6-13所示。当端口C作为输入引脚时,PTCPE中的各位控制着相应引脚的内部上拉是否使能;当端口C作为输出引脚时,无论PTCPE寄存器各位何种状态,内部上拉均被关闭。

表6-13 C口上拉使能控制寄存器

复位默认值:00000000B

PTCPE[6:0]—上拉使能端口B

1:内部上拉使能。

0:内部上拉关闭。

C端口斜率使能寄存器如表6-14所示。当端口C作为输出引脚时,PTCSE中的各位可设定相关的PTC管脚是否使能输出斜率控制;当端口C作为输入引脚时,无论PTCSE寄存器各位处于何种状态,均不产生任何影响。

表6-14 C口斜率使能控制寄存器

复位默认值:00000000B

PTCSE[6:0]—斜率使能端口C

1:输出斜率控制被使能。

0:输出斜率控制被禁止。

C端口驱动强度选择寄存器如表6-15所示。当端口C作为输出引脚时,PTCDS中的各位可设定相关的PTC 管脚是否选择低输出驱动或高输出驱动;当端口C作为输入引脚时,这些位不会产生任何影响。

表6-15 C口驱动强度选择寄存器

复位默认值:00000000B

PTCDS[7:0]—端口C驱动强度端口选择

1:选择高输出驱动强度。

0:选择低输出驱动强度。

6.2.4 D口相关寄存器

1.端口D数据及方向寄存器

D口既可作为普通输入或输出口使用,也可以与ADC, KBI以及TPM1和TPM2内部时钟输入模块共享引脚。这些功能模块中的任一个使能,都将会使通用I/O口的数据方向寄存器失去作用。这里需要注意的是当一个引脚既作为ADC模块又作为数字外设功能时,ADC 具有较高的优先级。其数据寄存器PTDD及方向寄存器PTDDD分别如表6-16和表6-17所示:

表6-16 D口数据寄存器

复位默认值:00000000B

表6-17 D口方向寄存器

复位默认值:00000000B

当D作为输入端口时,读取PTDD寄存器将返回引脚的逻辑电平值;D为输出端口时,读取PTDD寄存器将返回上一次写入该寄存器的值,写入的数据将被锁存。方向寄存器PTDDD的这些位控制着D 端口管脚的数据传输方向以及从PTDD读取的数据内容。复位后,默认PTDDD寄存器各位为0,且为高阻输入状态,上拉被禁止。

2.端口D控制寄存器(PTDPE,PTDSE,PTDDS)

D端口上拉使能寄存器如表6-18所示。当端口D作为输入引脚时,PTDPE中的各位控制着相应引脚的内部上拉是否使能;当端口D作为输出引脚时,无论PTDPE寄存器各位何种状态,内部上拉均被关闭。

表6-18 D口上拉使能控制寄存器

复位默认值:00000000B

PTDPE[7:0]—端口D上拉使能

1:内部上拉使能。

0:内部上拉关闭。

D端口斜率使能寄存器如表6-19所示。当端口D作为输出引脚时,PTDSE中的各位可设定相关的PTD管脚是否使能输出斜率控制;当端口D作为输入引脚时,无论PTDSE寄存器各位处于何种状态,均不产生任何影响。

表6-19 D口斜率使能控制寄存器

复位默认值:00000000B

PTDSE[7:0]—端口D斜率使能

1:输出斜率控制被使能。

0:输出斜率控制被禁止。

D端口驱动强度选择寄存器如表6-20所示。当端口D作为输出引脚时,PTDDS中的各位可设定相关的PTD 管脚是否选择低输出驱动或高输出驱动;当端口D作为输入引脚时,这些位不会产生任何影响。

表6-20 D口驱动强度选择寄存器

复位默认值:00000000B

PTDDS[7:0]—端口D驱动强度端口选择

1:选择高输出驱动强度。

0:选择低输出驱动强度。

6.2.5 E 口相关寄存器

1.端口E 数据及方向寄存器

E 口既可作为普通输入或输出口使用,也可以与SCI1、SPI 以及TPM1定时通道模块共享引脚。当这些功能模块中的任一个使能,都将会使通用I/O 口的数据方向寄存器失去作用。其数据寄存器PTED 及方向寄存器PTEDD 如表6-21和表6-22所示:

表6-21 E 口数据寄存器

复位默认值:00000000B

表6-22 E 口方向寄存器

复位默认值:00000000B

当E 作为输入端口时,读取PTED 寄存器将返回引脚的逻辑电平值;当E 作为输出端口时,读取PTED 寄存器将返回上一次写入该寄存器的值,写入的数据将被锁存。

方向寄存器的这些位控制着E 端口管脚的数据传输方向以及为PTED 读取的数据内容。复位后,默认PTEDD 寄存器各位为0,且为高阻输入状态,上拉被禁止。

2. 端口E 控制寄存器(PTEPE,PTESE,PTEDS)

E 端口上拉使能寄存器如表6-23所示。当端口E 作为输入引脚时,PTEPE 中的各位控制着相应引脚的内部上拉是否使能;当端口E 作为输出引脚时,无论PTEPE 寄存器各位何种状态,内部上拉均被关闭。

表6-23 E 口上拉使能控制寄存器

复位默认值:00000000B

PTEPE[7:0]—端口E 上拉使能

1:内部上拉使能。 0:内部上拉关闭。

E 端口斜率使能寄存器如表6-24所示。当端口E 作为输出引脚时,PTESE 中的各位可

设定相关的PTE管脚是否使能输出斜率控制;当端口E作为输入引脚时,无论PTESE寄存器各位处于何种状态,均不产生任何影响。

表6-24 E口斜率使能控制寄存器

复位默认值:00000000B

PTESE[6:0]—端口E斜率使能

1:输出斜率控制被使能。

0:输出斜率控制被禁止。

E端口驱动强度选择寄存器如表6-25所示。当端口E作为输出引脚时,PTEDS中的各位可设定相关的PTE管脚是否选择低输出驱动或高输出驱动;当端口E作为输入引脚时,这些位不会产生任何影响。

表6-25 E口驱动强度选择寄存器

复位默认值:00000000B

PTEDS[7:0]—端口E驱动强度端口选择

1:选择高输出驱动强度。

0:选择低输出驱动强度。

6.2.6 F口相关寄存器

1. 端口F数据及方向寄存器

F口既可作为普通输入或输出口使用,也可以与TPM1和TPM2定时通道模块共享引脚。当这些功能模块中的任一个使能,都将会使通用I/O口的数据方向寄存器失去作用。其数据寄存器PTFD及方向寄存器PTFDD分别如表6-26和表6-27所示:

表6-26 F口数据寄存器

复位默认值:00000000B

表6-27 F口方向寄存器

复位默认值:00000000B

当F作为输入端口时,读取PTFD寄存器将返回引脚的逻辑电平值;F为输出端口时,读取PTFD寄存器将返回上一次写入该寄存器的值,写入的数据将被锁存。方向寄存器PTFDD的这些位控制着F 端口管脚的数据传输方向以及为PTFD读取的数据内容。复位后,默认PTFDD寄存器各位为0,且为高阻输入状态,上拉被禁止。

2. 端口F控制寄存器(PTFPE,PTFSE,PTFDS)

F端口上拉使能寄存器如表6-28所示。当端口F作为输入引脚时,PTFPE中的各位控制着相应引脚的内部上拉是否使能;当端口F作为输出引脚时,无论PTFPE寄存器各位何种状态,内部上拉均被关闭。

表6-28 F口上拉使能控制寄存器

复位默认值:00000000B

PTFPE[7:0]—端口F上拉使能

1:内部上拉使能。

0:内部上拉关闭。

F端口斜率使能寄存器如表6-29所示。当端口F作为输出引脚时,PTFSE中的各位可设定相关的PTF管脚是否使能输出斜率控制;当端口F作为输入引脚时,无论PTFSE寄存器各位处于何种状态,均不产生任何影响。

表6-29 F口斜率使能控制寄存器

复位默认值:00000000B

PTFSE[6:0]—端口F斜率使能

1:输出斜率控制被使能。

0:输出斜率控制被禁止。

F端口驱动强度选择寄存器如表6-30所示。当端口F作为输出引脚时,PTFDS中的各位可设定相关的PTF 管脚是否选择低输出驱动或高输出驱动;当端口F作为输入引脚时,

这些位不会产生任何影响。

表6-30 F口驱动强度选择寄存器

复位默认值:00000000B

PTFDS[7:0]—端口F驱动强度端口选择

1:选择高输出驱动强度。

0:选择低输出驱动强度。

6.2.7 G口相关寄存器

1.端口G数据及方向寄存器

G口既可作为普通输入或输出口使用,也可以与KBI,ICG模块共享引脚。当作为KBI 输入模块的任一位使能时,都将会使该位作为通用I/O口的数据方向寄存器失去作用。同时需要注意的是当外部振荡器使能时,PTG5和PTG6作为振荡器管脚来使用,此时相应引脚的I/O控制寄存器不起作用。

其数据寄存器PTGD及方向寄存器PTGDD分别如表6-31和表6-32所示:

表6-31 G口数据寄存器

复位默认值:00000000B

表6-32 G口方向寄存器

复位默认值:00000000B

当G作为输入端口时,读取PTGD寄存器将返回引脚的逻辑电平值;当G作为输出端口时,读取PTGD寄存器将返回上一次写入该寄存器的值,写入的数据将被锁存。方向寄存器PTGDD的这些位控制着G 端口管脚的数据传输方向以及从PTGD读取的数据内容。复位后,默认PTGDD寄存器各位为0,且为高阻输入状态,上拉被禁止。

2.AW60端口G控制寄存器(PTGPE,PTGSE,PTGDS)

G端口上拉使能寄存器如表6-33所示。当端口G作为输入引脚时,PTGPE中的各位控制着相应引脚的内部上拉是否使能;当端口G作为输出引脚时,无论PTGPE寄存器各位何种状态,内部上拉均被关闭。

表6-33 G口上拉使能控制寄存器

复位默认值:00000000B

PTGPE[6:0]—端口G上拉使能

1:内部上拉使能。

0:内部上拉关闭。

G端口斜率使能寄存器如表6-34所示。当端口G作为输出引脚时,PTGSE中的各位可设定相关的PTG管脚是否使能输出斜率控制;当端口G作为输入引脚时,无论PTGSE寄存器各位处于何种状态,均不产生任何影响。

表6-34 G口斜率使能控制寄存器

复位默认值:00000000B

PTGSE[6:0]—端口G斜率使能

1:输出斜率控制被使能。

0:输出斜率控制被禁止。

G端口驱动强度选择寄存器如表6-35所示。当端口G作为输出引脚时,PTGDS中的各位可设定相关的PTG 管脚是否选择低输出驱动或高输出驱动;当端口G作为输入引脚时,这些位不会产生任何影响。

表6-35 G口驱动强度选择寄存器

复位默认值:00000000B

PTGDS[7:0]—端口G驱动强度端口选择

1:选择高输出驱动强度。

0:选择低输出驱动强度。

6.3S08键盘与显示应用设计

微控制器应用系统中,通常都需要键盘和显示功能,也就是常说的人机界面。它包括用户对应用系统的状态干预和数据输入,以及应用系统向用户报告运行状态和运行结果。这里以按键和LED为例介绍在S08AW微控制器实验系统中常用的独立式和矩阵式键盘接口。

6.3.1独立式按键接口

在微控制器系统中,用到的按键较少时一般采用独立式结构。所谓独立式按键就是各个按键独立的占用一个MCU的输入引脚,键的工作不会影响其它的I/O口。图6-3是S08AW60与四个按键的接口电路图。使用了PTA0~PTA3共4个引脚。

图6-3 独立式按键电路结构

独立式按键电路配置灵活,软件设计简单,但每个按键必须占用一根I/O口线,因此,当按键较多时,I/O口线浪费较大。这里按键输入均采用低电平有效的方式,此外,外接的上拉电阻保证了按键断开时,I/O口线上有确定的高电平。由于S08AW60的PTA口引脚内部可以设置上拉电阻,如果内部上拉使能则外接电路就不需再接上拉电阻了。

【例6-1】基于S08AW60微控制器的独立式按键程序设计。

分析:独立式按键的程序设计通常采用查询式结构:先逐位查询MCU的每根I/O口线的输入状态,如发现某一根I/O口线的输入为低电平,则可确认该I/O口线所对应的按键已按下,然后,再转向该键的功能处理程序。

按键的程序设计流程如图6-4所示。

图6-4 独立式键盘扫描程序流程图

独立式按键的C语言源程序:

/****************************************************************************\ * * 河南工业大学Freescale MCU&DSP联合实验室

* * 文件名:key_test1.c

* * MCU:S08AW60

* * 编译环境:CodeWarrior 6.1

* * 程序员:易宇航

* * 版本:V1.0

* * 描述:4位独立式按键程序设计

* * 日期:2008.7

\*****************************************************************************/ #include

#include "derivative.h" /* include peripheral declarations资源定义*/

#define NON_KEY 0x0f /*定义无键返回值*/

/****************************************************************************\ * * 函数名称:key_delay()

* * 函数功能:延时消抖动

* * 入口参数:de----延时参数

* * 出口参数:无

\****************************************************************************/ void key_delay(unsigned int de)

{

while(de--)

{

__RESET_W ATCHDOG();

}

}

/****************************************************************************\ * * 函数名称:KeyScan()

* * 函数功能:键盘扫描

* * 入口参数:无

* * 出口参数:无

\****************************************************************************/ unsigned char KeyScan()

{

unsigned char key;/*key:存放键值*/

/*扫描第0个按键*/

if(PTAD&0xfe==0)

{

key_delay(100);/*延时,消抖*/

while(PTAD &0x0fe==0);

key=0x00;

return key;

}

/*扫描第1个按键*/

if(PTAD &0xfd==0)

{

key_delay(100);/*延时,消抖*/

while(PTAD &0x0fd==0);

key=0x01;

return key;

}

/*扫描第2个按键*/

if(PTAD &0xfb==0)

{

key_delay(100);/*延时,消抖*/

while(PTAD &0xfb==0);

key=0x02;

return key;

}

/*扫描第3个按键*/

if(PTAD &0xf7==0)

{

key_delay(100);/*延时,消抖*/

while(PTAD &0xf7==0);

key=0x03;

return key;

}

return NON_KEY;/*无键盘按下时返回NON_KEY(0x0f)*/

}

6.3.2矩阵式键盘接口

矩阵式键盘的结构与工作原理比独立式键盘接口稍复杂些。当MCU系统中所需键盘按键数量较多时,为了减少MCU的I/O口占用,通常将按键排列成矩阵形式,如图6-5所示。

1.矩阵式键盘的结构与工作原理

矩阵式键盘由行线和列线组成,按键位于行、列线的交叉点上。每条水平线和垂直线在交叉处不直接连通,而是通过一个按键进行连接。这样,一个4×4的行、列结构可以构成一个具有16个按键的键盘,显然,在按键数量较多时,矩阵式键盘较之独立式按键键盘要节省很多I/O口。

第六章输入输出及接口 〔习题6.2〕 I/O端口与存储器地址常有__????___?和__????___?两种编排方式,8088/8086处理器支持后者,设计有专门的I/O指令。其中指令IN是将数据从__????___?传输到__????___?,执行该指令时8088/8086处理器引脚产生__????___?总线周期。指令“OUT DX, AL”的目的操作数是__????___?寻址方式,源操作数是__????___?寻址方式。 〔解答〕 (I/O端口与存储器地址)统一编址 (I/O端口与存储器地址)独立编址 外设 处理器 I/O读 (I/O端口的DX)寄存器间接 寄存器 〔习题6.4〕 基于教程P142图6-7接口电路,编程使发光二极管循环发光。具体要求是:单独按下开关K0,发光二极管以L0、L1、L2、……L7顺序依次点亮,每个维持200ms,并不断重复,直到有其他按键操作;单独按下开关K1,发光二极管以L7、L6、L5、……L0顺序依次点亮,每个也维持200ms,并不断重复,直到有其他按键操作;其他开关组合均不发光,单独按下开关K7,则退出控制程序。延时200ms可以直接调用子程序DELAY实现。 〔解答〕 again: mov dx,6000h mov al,0ffh out dx,al ;全不亮 again1: in al,dx cmp al,7fh ;D7~D0=0111111B ? jz done ;单独按下K7,退出 cmp al,0feh ;D7~D0=11111110B ? jz next1 ;单独按下K0,转移到next1 cmp al,0fdh ;D7~D0=11111101B ? jz next2 ;单独按下K1,转移到next2 jmp again ;其它情况不点亮 next1: mov cx,8 mov al,1 ;从K0开始 next11: out dx,al ;某个LED电亮 call delay ;延时200ms shl al,1 ;rol al,1 loop next11 jmp again1 next2: mov cx,8

第6章S08输入输出接口 S08AW系列微控制器的I/O接口采用模块化设计方式,即输入/输出系统端口由许多标准模块组成。以S08AW60为例,其64-Pin封装的芯片端口包括PTA、PTB、PTC、PTD、PTE、PTF和PTG这7个I/O口,共54个通用I/O引脚。这些引脚大都与片上多种外围设备复用,如定时器模块、通信模块和键盘中断模块等。这些特殊外围设备模块的优先级比通用I/O接口的优先级高,因此当使能某个外围设备时,则与该复用管脚相关的输入/输出功能将被禁止。 本章主要介绍S08AW系列微控制器通用I/O端口的功能、设置和使用方法,以及按键和LED显示接口、输入/输出接口的设计例程等。 6.1S08 I/O端口原理 通用I/O端口又称并行数字I/O端口,用来实现微控制器与外部设备的信息交换,并完成控制和数据采集,是微控制器一个必不可少的基本组成部分。当一个MCU引脚作为通用I/O 端口时,应对该引脚的两个寄存器进行设置:一个是该引脚的方向寄存器,用来设定该引脚是用于输入还是输出;另一个是该引脚的数据寄存器,当用作输出时,应先将要输出的数据写入该数据寄存器,然后才能送到引脚上;当用作输入口时,引脚上的数据将先存入该数据寄存器,然后CPU再读该寄存器中已存入的数据。 设定MCU的某个引脚是输入还是输出的方向寄存器是PTxDD,PTxDD是方向寄存器的英文缩写名称,x代表A、B、C、D、E、F、G这八个端口之一。 6.1.1I/O端口引脚分布 S08AW60的I/O引脚包括8个端口,共计54个引脚: ●PTA(0-7):A口8个引脚仅具有普通I/O引脚功能,没有与其它功能模块复用 ●PTB(0-7):B口8个引脚可与ADC1模块共用 ●PTC(0-6):C口7个引脚可与SCI2、IIC1以及MCLK模块共用 ●PTD(0-7):D口8个引脚可与ADC1、KBI1、TPM1以及TPM2模块共用 ●PTE(0-7):E口8个引脚可与SCI1、TPM1以及SPI1模块共用 ●PTF(0-7):F口8个引脚可与TPM1以及TPM2模块共用 ●PTG(0-6):G口7个引脚可与ICG以及KBI1模块共用 S08AW60通用I/O引脚分布以及与各个功能模块的复用关系如图6-1所示。