在分析运算放大器信号运算电路时,必须掌握运算放大器工作于线性区的特点,运算放大器的开环放大倍数是很高的,一般运放的开环差模增益都大于80dB(即放大倍数以上),所以要使运放工作于线性区必须引入深反馈,以减小两个输入端的净输入电压,也就是说运放工作于线性区时同相输入端于反相输入端的电压接近于零,即,运放工作于线性区的这一特点简称“虚短”,即不是真正短路+ U ≈ ? U。又因运放的输入电阻很高104MΩ ,场效应管作出的运放大于106 MΩ,所以运放两个输入端的电流可视为零,即-I =0,+I=0,这是运放工作于线性区的第二个特点,称为“虚断”。掌握了运放的这两个特点,分析运算放大器信号运算电路就十分简便。

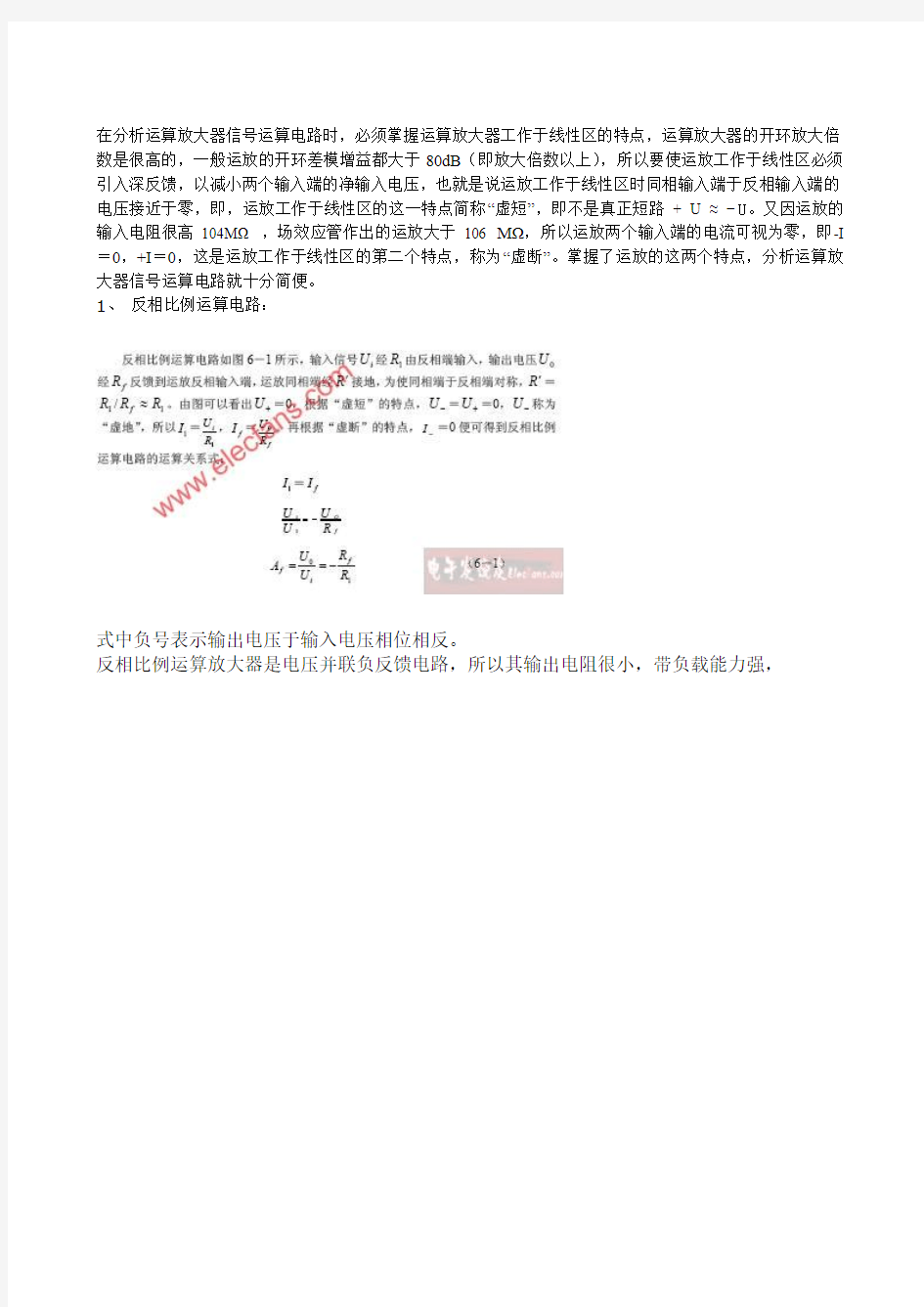

1、反相比例运算电路:

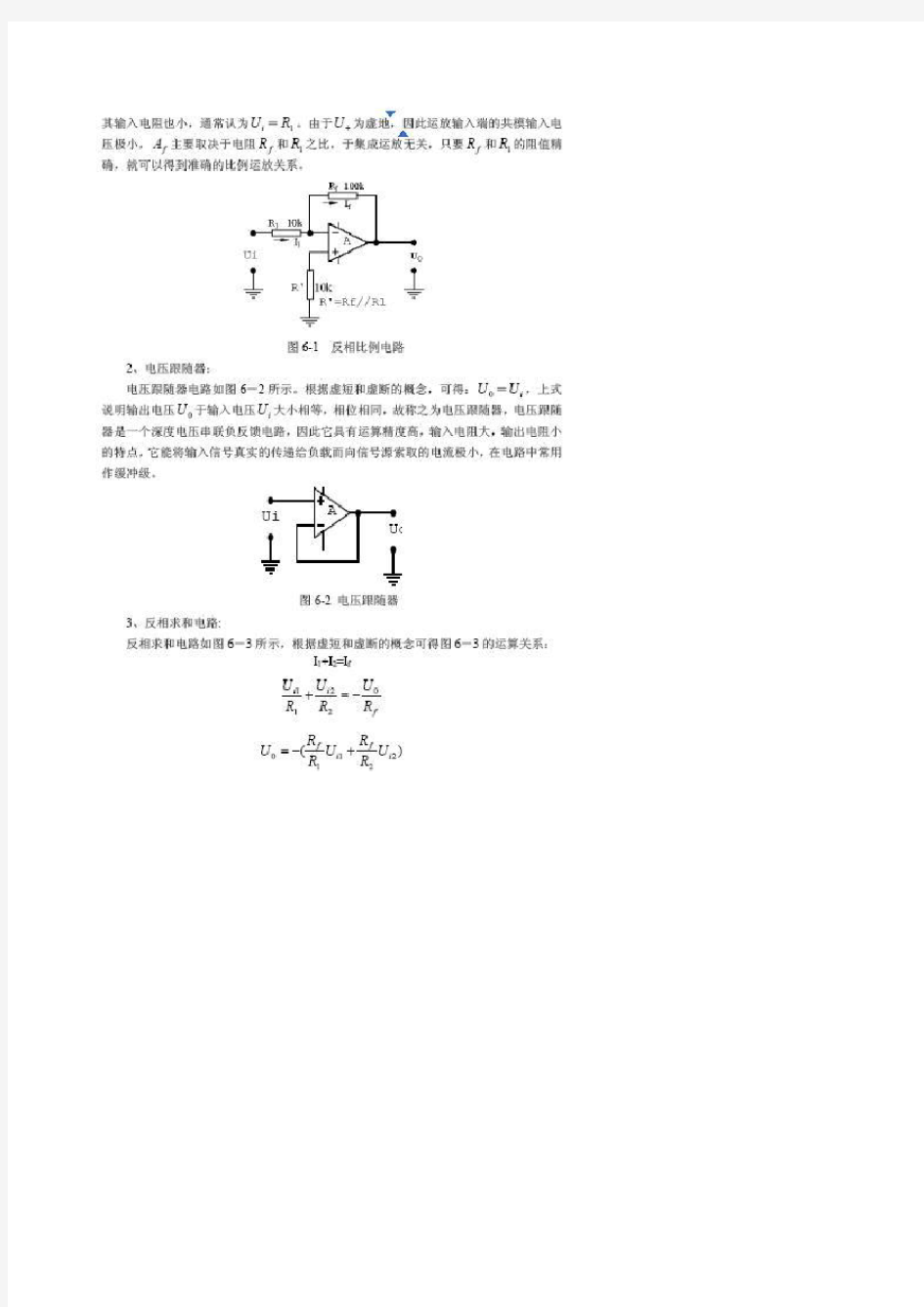

式中负号表示输出电压于输入电压相位相反。

反相比例运算放大器是电压并联负反馈电路,所以其输出电阻很小,带负载能力强,

《电路与电子学基础》实验报告 实验名称集成运算放大器应用 班级2013211XXX 学号2013211XXX 姓名XXX

实验7.1 反相比例放大器 一、实验目的 1.测量反相比例运算放大器的电压增益,并比较测量值与计算值。 2.测定反响比例放大器输出与输入电压波形之间的相位差。 3.根据运放的输入失调电压计算直流输出失调电压,并比较测量值与计算值。 4.测定不同电平的输入信号对直流输出失调电压的影响。 二、实验器材 LM 741 运算放大器 1个 信号发生器 1台 示波器 1台 电阻:1kΩ 2个,10kΩ 1个,100kΩ 2个 三、实验步骤 1.在EWB平台上建立如图7-1所示的实验电路,仪器按图设置。 单击仿真开关运行动态分析,记录输入峰值电压 V和输出峰值电压 ip V,并记录直流输出失调电压of V及输出与输入正弦电压波形之间的op 相位差。

Vip=4.9791mV Vop=498.9686mV Vof=99.37mV 相位差π 2.根据步骤1的电压测量值,计算放大器的闭环电压增益Av。 Av=-100.2 3.根据电路元件值,计算反相比例运算放大器的闭环电压增益。 Av=-100 4.根据运放的输入失调电压 V和电压增益Av,计算反相比例运放 if 的直流输出失调电压 V。 of Vof=100mV 四、思考与分析 1.步骤3中电压增益的计算值与步骤1,2中的测量值比较,情况如何? 计算值为-100,测量值为-100.2,基本相等,略有误差

2.输出与输入正弦电压波形之间的相位差怎样? 相位差为π 3.步骤1中直流输出失调电压的测量值与步骤4中的计算值比较,情况如何? 测量值为99.37mV,计算值为100mV,基本相等,略有误差 4.步骤1中峰值输出电压占直流输出失调电压的百分之几? 500% 5.反馈电阻 R的变化对放大器的闭环电压增益有何影响? f 在R1一定的条件下,Rf越大,闭环电压增益越大 实验7.2 加法电路 一、实验目的 1.学习运放加法电路的工作原理。 2.分析直流输入加法器。 3.分析交直流输入加法器。 4.分析交流输入加法器。 二、实验器材 LM741 运算放大器 1个直流电源 2个 0~2mA毫安表 4个万用表 1个 信号发生器 1台

运算放大器组成的电路五花八门,令人眼花瞭乱,是模拟电路中学习的重点。在分析它的工作原理时倘没有抓住核心,往往令人头大。为此本人特搜罗天下运放电路之应用,来个“庖丁解牛”,希望各位从事电路板维修的同行,看完后有所斩获。 遍观所有模拟电子技朮的书籍和课程,在介绍运算放大器电路的时候,无非是先给电路来个定性,比如这是一个同向放大器,然后去推导它的输出与输入的关系,然后得出Vo=(1+Rf)Vi,那是一个反向放大器,然后得出Vo=-Rf*Vi……最后学生往往得出这样一个印象:记住公式就可以了!如果我们将电路稍稍变换一下,他们就找不着北了!偶曾经面试过至少100个以上的大专以上学历的电子专业应聘者,结果能将我给出的运算放大器电路分析得一点不错的没有超过10个人!其它专业毕业的更是可想而知了。 今天,芯片级维修教各位战无不胜的两招,这两招在所有运放电路的教材里都写得明白,就是“虚短”和“虚断”,不过要把它运用得出神入化,就要有较深厚的功底了。 虚短和虚断的概念 由于运放的电压放大倍数很大,一般通用型运算放大器的开环电压放大倍数都在80 dB以上。而运放的输出电压是有限的,一般在 10 V~14 V。因此运放的差模输入电压不足1 mV,两输入端近似等电位,相当于“短路”。开环电压放大倍数越大,两输入端的电位越接近相等。 “虚短”是指在分析运算放大器处于线性状态时,可把两输入端视为等电位,这一特性称为虚假短路,简称虚短。显然不能将两输入端真正短路。 由于运放的差模输入电阻很大,一般通用型运算放大器的输入电阻都在1MΩ以上。因此流入运放输入端的电流往往不足1uA,远小于输入端外电路的电流。故通常可把运放的两输入端视为开路,且输入电阻越大,两输入端越接近开路。“虚断”是指在分析运放处于线性状态时,可以把两输入端视为等效开路,这一特性称为虚假开路,简称虚断。显然不能将两输入端真正断路。 在分析运放电路工作原理时,首先请各位暂时忘掉什么同向放大、反向放大,什么加法器、减法器,什么差动输入……暂时忘掉那些输入输出关系的公式……这些东东只会干扰你,让你更糊涂﹔也请各位暂时不要理会输入偏置电流、共模抑制比、失调电压等电路参数,这是设计者要考虑的事情。我们理解的就是理想放大器(其实在维修中和大多数设计过程中,把实际放大器当做理想放大器来分析也不会有问题)。 好了,让我们抓过两把“板斧”------“虚短”和“虚断”,开始“庖丁解牛”了。 (原文件名:1.jpg)

第九章集成运算放大器及其应用(易映萍) 9.1 差分放大电路 9.2互补功率放大电路 9.3 集成运算放大电路 9.4 理想集成运放的线性运用电路 9.5 理想集成运放的非线性运用电路 习题 第九章集成运算放大器及其应用 9.1 差分放大电路 9.1.1 直接耦合多级放大电路的零点漂移现象 工业控制中的很多物理量均为模拟量,如温度、流量、压力、液面和长度等,它们通过不同的传感器转化成的电量也均为变化缓慢的非周期性连续信号,这些信号具有以下两个特点: 1.信号比较微弱,只有通过多级放大才能驱动负载; 2.信号变化缓慢,一般采用直接耦合多级放大电路将其放大。 u=0)时,人们在试验中发现,在直接耦合的多级放大电路中,即使将输入端短路(即 i u≠0),这种现象称为零点漂移(简称为零漂),如图输出端还会产生缓慢变化的电压(即 o 9.1所示。 (a)测试电路(b)输出电压u o的漂移 图9.1 零点漂移现象 9.1.2 零漂产生的主要原因 在放大电路中,任何参数的变化,如电源电压的波动、元件的老化以及半导体元器件参数随温度变化而产生的变化,都将产生输出电压的漂移,在阻容耦合放大电路中,耦合电容对这种缓慢变化的漂移电压相当于开路,所以漂移电压将不会传递到下一级电路进一步放

大。但是,在直接耦合的多级放大电路中,前一级产生的漂移电压会和有用的信号(即要求放大的输入信号)一起被送到下一级进一步放大,当漂移电压的大小可以和有用信号相当时,在负载上就无法分辨是有效信号电压还是漂移电压,严重时漂移电压甚至把有效信号电压淹没了,使放大电路无法正常工作。 采用高质量的稳压电源和使用经过老化实验的元件就可以大大减小由此而产生的漂移,所以由温度变化所引起的半导体器件参数的变化是产生零点漂移现象的主要原因,因而也称零点漂移为温度漂移,简称温漂,从某种意义上讲零点漂移就是静态工作点Q点随温度的漂移。 9.1.3抑制温漂的方法 对于直接耦合多级放大电路,如果不采取措施来抑制温度漂移,其它方面的性能再优良,也不能成为实用电路。抑制温漂的方法主要由以下几种: (1)采用稳定静态工作的分压式偏置放大电路中Re的负反馈作用; (2)采用温度补偿的方法,利用热敏元件来抵消放大管的变化; (3)采用特性完全相同的三极管构成“差分放大电路”; 9.1.4 差分放大电路 差分放大电路是构成多级直接耦合放大电路的基本单元电路。直接耦合的多级放大电路的组成框图如图9.2所示。 图9.2 多级放大的组成框图 A倍后传送到负载上,对电路造从上图可知输入级一旦产生了温漂,会经中间级放大 u2 A≈1,对电路造成的成严重的影响,而中间级产生的温漂,由于直接到达功放级而功放的 u 影响跟输入级相比少得多,所以,我们主要应设法抑制输入级产生的温漂,故在直接耦合的多级放大电路中只有输入级常采用差分放大电路的形式来抑制温漂。 9.1.4.1 差分放大电路的组成及结构特点 一.电路组成 差分放大电路如图9.3所示。

习题答案 5.1 在题图5.1所示的电路中,已知晶体管V 1、V 2的特性相同,V U on BE 7.0,20)(==β。求 1CQ I 、1CEQ U 、2CQ I 和2CEQ U 。 解:由图5.1可知: BQ CQ BQ )on (BE CC I I R R I U U 213 1 1+=--即 11CQ11.01.4 2.7k 20I -7V .0-V 10CQ CQ I I k +=Ω Ω ? 由上式可解得1CQ I mA 2≈ 2CQ I mA I CQ 21== 而 1CEQ U =0.98V 4.1V 0.2)(2-V 1031=?+=+-R )I I (U BQ CQ CC 2CEQ U =5V 2.5V 2-V 1042=?=-R I U CQ CC 5.2 电路如题图5.2所示,试求各支路电流值。设各晶体管701.U ,)on (BE =>>βV 。 U CC (10V) V 1 R 3 题图5.1

解:图5.2是具有基极补偿的多电流源电路。先求参考电流R I , ()815 17 0266..I R =+?---=(mA ) 则 8.15==R I I (mA ) 9.0105 3== R I I (mA ) 5.425 4==R I I (mA ) 5.3 差放电路如题图5.3所示。设各管特性一致,V U on BE 7.0)(=。试问当R 为何值时,可满足图中所要求的电流关系? 解: 53010 7 0643..I I C C =-==(mA ) 则 I 56V 题图 5.2 R U o 题图5.3

2702 1 476521.I I I I I I C C C C C C == ==== mA 即 2707 065.R .I C =-= (mA ) 所以 61927 07 06...R =-= (k Ω) 5.4 对称差动放大电路如题图5.1所示。已知晶体管1T 和2T 的50=β,并设 U BE (on )=0.7V,r bb ’=0,r ce =。 (1)求V 1和V 2的静态集电极电流I CQ 、U CQ 和晶体管的输入电阻r b’e 。 (2)求双端输出时的差模电压增益A ud ,差模输入电阻R id 和差模输出电阻R od 。 (3)若R L 接V 2集电极的一端改接地时,求差模电压增益A ud (单),共模电压增益A uc 和共模抑制比K CMR ,任一输入端输入的共模输入电阻R ic ,任一输出端呈现的共模输出电阻R oc 。 (4) 确定电路最大输入共模电压围。 解:(1)因为电路对称,所以 mA ...R R .U I I I B E EE EE Q C Q C 52050 21527 062270221=+?-=+?-== = + V 1 V 2 + U CC u i1 u i2R C 5.1k ΩR L U o 5.1kΩ R C 5.1k Ω R E 5.1k Ω -6V R B 2k Ω 题图5.1 R B 2k Ω + - R L /2 + 2U od /2 + U id /2 R C R B V 1 (b) + U ic R C R B V 1 (c) 2R EE + U

实验名称 集成运算放大器的基本应用 一.实验目的 1.掌握集成运算放大器的正确使用方法。 2.掌握用集成运算放大器构成各种基本运算电路的方法。 3.学习正确使用示波器交流输入方式和直流输入方式观察波形的方法,重点掌握积分输入,输出波形的测量和描绘方法。 二.实验元器件 集成运算放大器 LM324 1片 电位器 1k Ω 1只 电阻 100k Ω 2只;10k Ω 3只;5.1k Ω 1只;9k Ω 1只 电容 0.01μf 1只 三、预习要求 1.复习由运算放大器组成的反相比例、反相加法、减法、比例积分运算电路的工作原理。 2.写出上述四种运算电路的vi 、vo 关系表达式。 3.实验前计算好实验内容中得有关理论值,以便与实验测量结果作比较。 4.自拟实验数据表格。 四.实验原理及参考电路 本实验采用LM324集成运算放大器和外接电阻、电容等构成基本运算电路。 1. 反向比例运算 反向比例运算电路如图1所示,设组件LM324为理想器件,则 11 0υυR R f -=

R f 100k R 1 10k A 10k R L v o v 1 R 9k 图1 其输入电阻1R R if ≈,图中1//R R R f ='。 由上式可知,改变电阻f R 和1R 的比值,就改变了运算放大器的闭环增益vf A 。 在选择电路参数是应考虑: ○ 1根据增益,确定f R 与1R 的比值,因为 1 R R A f vf - = 所以,在具体确定f R 和1R 的比值时应考虑;若f R 太大,则1R 亦大,这样容易引起较大的失调温漂;若f R 太小,则1R 亦小,输入电阻if R 也小,可能满足不了高输入阻抗的要求,故一般取f R 为几十千欧至几百千欧。 若对放大器输入电阻有要求,则可根据1R R i =先确定1R ,再求f R 。 ○ 2运算放大器同相输入端外接电阻R '是直流补偿电阻,可减小运算放大器偏执电流产生的不良影响,一般取1//R R R f =',由于反向比例运算电路属于电压并联负反馈,其输入、输出阻抗均较低。 本次试验中所选用电阻在电路图中已给出。 2. 反向比例加法运算 反向比例加法运算电路如图2所示,当运算放大器开环增益足够大时,其输入端为“虚地”,11v 和12v 均可通过1R 、2R 转换成电流,实现代数相加,其输出电压 ??? ??+-=122111 v R R v R R v f f o 当R R R ==21时 ()1211v v R R v f o +- = 为保证运算精度,除尽量选用精度高的集成运算放大器外,还应精心挑选精度高、稳定性好的电阻。f R 与R 的取值范围可参照反比例运算电路的选取范围。 同理,图中的21////R R R R f ='。

计算机组成原理实验报告 一、实验目的及要求 本次实验要求掌握加法器、减法器的设计与实现。 可以利用原理图设计并实现 1 位、8 位和32 位加法器,以及32 位加减器。设计1 位加法器,将加法器中加入减法功能,可以利用SUB(减)的控制信号; 二、实验设备(环境)及要求 1. Windows 2000 或Windows XP 2. QuartusII9.1 sp2、DE2-115 计算机组成原理教学实验系统一台。 三、实验内容与步骤 (1)两个二进制数字A,B 和一个进位输入C0相加,产生一个和输出S,以及一个进位输出C1,这种运算电路成为全加器(1 位加法器)。1 位全加器有两个输出S 和C1,其中S 为加法器的和,C1 为进位位输出。下表中列出一位全加器进行加法运算的输入输出真值表: 表2-1 加法器的真值表 根据以上真值表,可以得到 1 位加法器的输入与输出逻辑关系。 根据上面的逻辑关系式可以建立如下图的 1 位加法器的原理图

接着进行功能仿真: 开始功能仿真,在【Processing】菜单下,选择【Start Simulation】启动仿真工具。实验结果: 在5-10ns 时,A=1,B=0,C0=0,则C1=0,S=1; 在15-20ns 时,A=1,B=1,C0=0,则C1=1,S=0; 在30-35ns 时,A=0,B=1,C0=1,则C1=1,S=0; 在35-40ns 时,A=1,B=1,C0=1,则C1=1,S=1; (2)8 位加法器的原理图设计 实验原理8 位加法器用于对两个8 位二进制数进行加法运算,并产生进位。8 位加法器真值表如下所示:

实验六:加法器的使用 1.实验目的 1) 熟悉加法器的工作原理与逻辑功能; 2) 掌握加法器的使用。 2.理论准备 1)二进制并行加法器是一种能并行产生两个二进制数算术和的逻辑部件,按其进位方式的不同可分为串行进位和超前进位二进制并行加法器; 2)串行进位二进制并行加法器是由全加器级联而成的。其特点是:被加数和加数的各位能同时并行到达各位的输入端,而各位全加器的进位输入则是按照由低位向高位逐级串行传递的,各进位形成一个进位链。由于每一位相加的和都与本位进位输入有关,所以,最高位必须等到各低位全部相加完成并送来进位信号之后才能产生运算结果。显然,这种加法器运算速度较慢,而且位数越多,速度就越低; 3)为了提高加法器的运算速度,必须设法减小或去除由于进位信号逐级传送所花的时间,使各位的进位直接由加数和被加数来决定,而不需依赖低位进位。根据这一思想设计的加法器称为超前进位(又称先行进位)二进制并行加法器。超前进位4位二进制并行加法器有74283。 3.实验内容 用4位并行加法器(74283)设计一个可以做加法和减法的电路。当控制信号M=0时,将两个无符号的4位二进制数相加,当M=1时它将两个无符号数相减。 4.设计过程 1)输入:a[4..1]为被加数(或被减数,b[4..1]为加数(或减数),a[4..1]和b[4..1]为4位二进制数,控制信号M,当M=0时,电路实现加法运算,即执行a[4..1]+b[4..1],当M=1时,电路实现减法运算,即执行a[4..1]-b[4..1]。减法采用补码运算。 2)用一个4位二进制并行加法器(74283)和4个异或门实现上述逻辑功能。将4位二进制a[4..1]直接加到并行加法器的A4、A3、A2和A1输入端,4位二进制b[4..1]通过异或门加到并行加法器的B4、B3、B2和B1输入端,并将功能变量M作为异或门的另一个输入且同时加到并行加法器的CIN进位输入端。 3)当M=0时,CIN=0,b[4..1]⊕M= b[4..1]⊕0= b[4..1],加法器实现a[4..1]+b[4..1];当M=1时,CIN=1,b[4..1]⊕M= b[4..1]⊕1 = b[4..1]’,加法器实现a[4..1]+b[4..1]’+1,即a[4..1]-b[4..1]。 4)根据真值表和逻辑函数画逻辑图。根据上式可以画出如图一所示的逻辑图。

实训九 集成运放的线性应用 内容一 集成运放的反相、同相比例运算电路 一、实训目的 1.掌握集成运算放大器的使用方法。 2.了解集成运放构成反相比例、同相比例运算电路的工作原理。 3.掌握集成运放反相比例、同相比例运算电路的测试方法。 二、实训测试原理 1. 反相放大电路 电路如图(1)所示。输入信号U i 通过电阻R 1加到集成运放的反相输入端,输出信号通过反馈电阻R f 反送到运放的反相输入端,构成电压并联负反馈。 根据“虚断”概念,即i N =i p ,由于R 2接地, 所以同相端电位U p =0。又根据“虚短”概念可知,U N =U p ,则U N =U p =0,反相端电位也为零。但反相端又不是接地点,所以N 点又称“虚地”。则有 f 1i i =,1i = 1i R U ,f i =-f 0R U 则0U =-1 f R R i U 。 运放的同相输入端经电阻R 2接地,R 2叫平衡电阻,其大小为R 2=R 1∥R f 。 图(1) 反相放大电路 图(2) 同相放大电路 图(3) 电压跟随器 2. 同相放大电路 电路如图(2)所示。输入信号U i 通过平衡电阻R 2加到集成运放的同相输入端,输出信号通过反馈电阻R f 反送到运放的反相输入端,构成电压串联负反馈。根据“虚断”与“虚短”的概念,有N P i U U U ==,i N =i P =0;则得i 1f 0)1(U R U +=若1R =∞,0f =R ,则i 0U U =即为电压跟随器,如图(3)。

三、实训仪器设备 1.直流稳压电源 2.万用表 3.示波器 四、实训器材 1. 集成块μA741(HA17741) 2. 电阻10KΩ×2 100KΩ×2 2 KΩ×2 3. 电位器1KΩ×1 五、实训电路 图(3)反相比例运算实训电路 图(4)同相比例运算实训电路 六、测试步骤及内容 1. 反相比例运算实训

电子设计自动化 大作业 题目加法器与减法器 学院泉城学院 班级电气09Q2班 姓名李文建 学号 20093005034 二O一一年十一月六日

加法器和减法器 一、设计要求: (1)构造一个四位二进制加法器和一个四位二进制减法器,完成各自的功能仿真。(2)利用四个按键输入四位加数(或减数)和被加数(或被减数)。 (3)用七段数码管显示四位和(或差),用一只发光二极管指示进位(或借位)信号。(4)利用个开关控制,确定是四位二进制加法器还是一个四位二进制减法器。 二、总体设计: 1、总体结构图

2、各模块功能 (1)第一个4-16译码器实现输入四位加数(或减数)和被加数(或被减数)。 (2)开关模块:控制B0、B1、B2、B3,当M=0时,执行A+B,当M=1时,执行A-B。 (3)加法(减法)器模块: 加法器:采用全加器的串行进位,本四位二进制加法器由四个一位二进制加法器组成,输入A i、B i、C i,输出S i、C i+1。 减法器:与加法器的区别仅仅在于最后的和数为两数相减。 (4)LED灯: 加法器:灯亮表示有进位,灯灭表示无进位。 减法器:灯亮表示有借位,灯灭表示无进位。 (5)第二个4-16译码器:输入为四为加法器的和S0、S1、S2、S3,输出为Y0—Y6分别控制七段数码管的a1、b1、c1、d1、e1、f1、g1,输出Y9—Y15分别控制第二个七段数码管的a2、b2、c2、d2、e2、f2、g2。 (6)数码管:显示输出结果。 三、单元模块设计 1、第一个4—16译码器 (1)模块功能 通过四个按键输入四位二进制数,由译码器得到四位加数(或减数)和被加数(或被减数)的所有组合,从而实现加法器(或减法器)的输入。 (2)端口定义

<熟悉QuartusII和Verilog HDL数字逻辑电路设计基础环境> 实验报告 学生姓名:李旭文超周 班级学号:11自动化1138033 1138019 指导老师:潘秀琴

<实验报告内容> 一、实验名称:学习QurtusII基本功能和使用方法,完成一位减法器、一位 加法器的原理图输入和文本输入、编译校验及功能仿真。 二、实验学时:4学时 三、实验目的:熟悉Quartus II基本功能和使用方法,掌握原理图输入、文本输入的步骤。 四、实验内容:完成一位加法器、一位减法器的设计输入并进行仿真输出。 五、实验原理:数字逻辑电路中各种门电路的功能和使用方法 六、实验步骤: 1.了解quartusII的基本功能使用; 2.设计输入:首先设计出逻辑电路,然后将所设计的数字逻辑电路以某种方式输入到计算机中,QuartusII有原理图输入和文本(代码)输入两种输入模式。3.设计编译校验:编译连接好的输入图形。 七、实验结果: 1.加法器:A.半加器 原理图: 文本:

波形图: B.一位全加器全加器: 原理图: 文本输入:

波形图: 2.减法器:原理图: 文本输入:

波形图: 八、心得体会:这是使用这个软件的第二次实验对于软件的使用已经比较熟练能够很快连接好电路进行试验 九、附录:<程序代码> 1.加法器: A.半加器 module adder(a,b,s,co); input a,b; output s,co; and X1(a,b); xor Y1(a,b); endmodule B.一位全加器 module onebit_fulladd(a,b,ci,sum,cout); input a,b,ci; output sum,cout; wire sum_temp,c_1,c_2,c_3; xor xor1(sum_temp,a,b);

集成运算放大器电路分析及应用(完整电子教案) 3.1 集成运算放大器认识与基本应用 在太阳能充放电保护电路中要利用集成运算放大器LM317实现电路电压检测,并通过三极管开关电路实现电路的控制。首先来看下集成运算放大器的工作原理。 【项目任务】 测试如下图所示,分别测量该电路的输出情况,并分析电压放大倍数。 R1 15kΩ R3 15kΩ R4 10kΩ V2 4 V XFG1 1 VCC 5V U1A LM358AD 3 2 4 8 1 VCC 3 5 2 4 R1 15kΩR2 15kΩ R3 15kΩ R4 10kΩ V2 4 V XFG1 1 VCC 5V U1A LM358AD 3 2 4 8 1 VCC 3 5 2 4 函数信号发生器函数信号发生器 (a)无反馈电阻(b)有反馈电阻 图3.1集成运算符放大器LM358测试电路(multisim) 【信息单】 集成运放的实物如图3.2 所示。 图3.2 集成运算放大 1.集成运放的组成及其符号 各种集成运算放大器的基本结构相似,主要都是由输入级、中间级和输出级以及偏置电路组成,如图3.3所示。输入级一般由可以抑制零点漂移的差动放大电路组成;中间级的作用是获得较大的电压放大倍数,可以由共射极电路承担;输出级要求有较强的带负载能力,一般采用射极跟随器;偏置电路的作用是为各级电路供给合理的偏置电流。

图3.3集成运算放大电路的结构组成 集成运放的图形和文字符号如图 3.4 所示。 图3.4 集成运放的图形和文字符号 其中“-”称为反相输入端,即当信号在该端进入时, 输出相位与输入相位相反; 而“+”称为同相输入端,输出相位与输入信号相位相同。 2.集成运放的基本技术指标 集成运放的基本技术指标如下。 ⑴输入失调电压 U OS 实际的集成运放难以做到差动输入级完全对称,当输入电压为零时,输出电压并不为零。规定在室温(25℃)及标准电源电压下,为了使输出电压为零,需在集成运放的两输入端额外附加补偿电压,称之为输入失调电压U OS ,U OS 越小越好,一般约为 0.5~5mV 。 ⑵开环差模电压放大倍数 A od 集成运放在开环时(无外加反馈时),输出电压与输入差模信号的电压之比称为开环差模电压放大倍数A od 。它是决定运放运算精度的重要因素,常用分贝(dB)表示,目前最高值可达 140dB(即开环电压放大倍数达 107 )。 ⑶共模抑制比 K CMRR K CMRR 是差模电压放大倍数与共模电压放大倍数之比,即od CMRR oc A K =A ,其含义与差动放大器中所定义的 K CMRR 相同,高质量的运放 K CMRR 可达160d B 。 ⑷差模输入电阻 r id r id 是集成运放在开环时输入电压变化量与由它引起的输入电流的变化量之比,即从输入端看进去的动态电阻,一般为M Ω数量级,以场效应晶体管为输入级的r id 可达104M Ω。分析集成运放应用电路时,把集成运放看成理想运算放大器可以使分析简化。实际集成运 放绝大部分接近理想运放。对于理想运放,A od 、K CMRR 、r id 均趋于无穷大。 ⑸开环输出电阻 r o r o 是集成运放开环时从输出端向里看进去的等效电阻。其值越小,说明运放的带负载能力越强。理想集成运放r o 趋于零。 其他参数包括输入失调电流I OS 、输入偏置电流 I B 、输入失调电压温漂 d UOS /d T 和输入失调电流温漂 d IOS /d T 、最大共模输入电压 U Icmax 、最大差模输入电压 U Idmax 等,可通过器件

加法器 3.2.1 加法器的原理 在将两个多位二进制数相加时,除了最低位以外,每一位都应该考虑来自低位的进位,即将两个对应位的加数和来自低位的进位3个数相加。这种运算称为全加,所用的电路称为全加器。 多位加法器的构成有两种方式:并行进位和串行进位。并行进位加法器设有进位产生逻辑,预算速度较快;串行进位方式是将全加器级联构成多位加法器。并行进位加法器通常比串行级联加法器占用更多的资源。随着为数的增加,相同位数的并行加法器与串行加法器的资源占用差距也越来越大,因此,在工程中使用加法器时,要在速度和容量之间寻找平衡点。 本次设计采用的是并行加法器方式。 3.2.2 加法器要求实现的功能 实现两个二进制数字的相加运算。当到达时钟上升沿时,将两数输入,运算,输出结果。 3.2.3 加法器的VHDL语言实现 (以下以12位数加16位数生成16位数的加法器为例) LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_arith.ALL; ENTITY add121616 is PORT(clk : in STD_LOGIC; Din1 :in signed (11 downto 0); Din2 :in signed (15 downto 0); Dout:out signed (15 downto 0)); END add121616; ARCHITECTURE a of add121616 is SIGNAL s1: signed(15 downto 0); BEGIN s1<=(Din1(11)&Din1(11)&Din1(11)&Din1(11)&Din1); PROCESS(Din1,Din2,clk) BEGIN if clk'event and clk='1' then Dout<=s1+Din2; end if; end process; end a; 3.2.4 加法器的模块图

常用运算放大器电路(全集) 下面是[常用运算放大器电路(全集)]的电路图 常用OP电路类型如下: 1. Inverter Amp. 反相位放大电路: 放大倍数为Av = R2 / R1但是需考虑规格之Gain-Bandwidth数值。R3 = R4 提供1 / 2 电源偏压 C3 为电源去耦合滤波 C1, C2 输入及输出端隔直流 此时输出端信号相位与输入端相反 2. Non-inverter Amp. 同相位放大电路: 放大倍数为Av=R2 / R1 R3 = R4提供1 / 2电源偏压 C1, C2, C3 为隔直流

此时输出端信号相位与输入端相同 3. Voltage follower 缓冲放大电路: O/P输出端电位与I/P输入端电位相同 单双电源皆可工作 4. Comparator比较器电路: I/P 电压高于Ref时O/P输出端为Logic低电位 I/P 电压低于Ref时O/P输出端为Logic高电位 R2 = 100 * R1 用以消除Hysteresis状态, 即为强化O/P输出端, Logic高低电位差距,以提高比较器的灵敏度. (R1=10 K, R2=1 M) 单双电源皆可工作 5. Square-wave oscillator 方块波震荡电路: R2 = R3 = R4 = 100 K R1 = 100 K, C1 = 0.01 uF

Freq = 1 /(2π* R1 * C1) 6. Pulse generator脉波产生器电路: R2 = R3 = R4 = 100 K R1 = 30 K, C1 = 0.01 uF, R5 = 150 K O/P输出端On Cycle = 1 /(2π* R5 * C1) O/P输出端Off Cycle =1 /(2π* R1 * C1) 7. Active low-pass filter 主动低通滤波器电路: R1 = R2 = 16 K R3 = R4 = 100 K C1 = C2 = 0.01 uF 放大倍数Av = R4 / (R3+R4) Freq = 1 KHz 8. Active band-pass filter 主动带通滤波器电路:

实验集成运算放大器的基本应用(Ⅱ)——有源滤波器 一、实验目的 1、熟悉用运放、电阻和电容组成有源低通滤波、高通滤波和带通、带阻滤波器。 2、学会测量有源滤波器的幅频特性。 二、实验原理 (a)低通(b)高通 (c) 带通(d)带阻 图9-1 四种滤波电路的幅频特性示意图 由RC元件与运算放大器组成的滤波器称为RC有源滤波器,其功能是让一定频率范围内的信号通过,抑制或急剧衰减此频率范围以外的信号。可用在信息处理、数据传输、抑制干扰等方面,但因受运算放大器频带限制,这类滤波器主要用于低频范围。根据对频率范围的选择不同,可分为低通(LPF)、高通(HPF)、带通(BPF)与带阻(BEF)等四种滤波器,它们的幅频特性如图9-1所示。 具有理想幅频特性的滤波器是很难实现的,只能用实际的幅频特性去逼近理想的。一般来说,滤波器的幅频特性越好,其相频特性越差,反之亦然。滤波器的阶数越高,幅频特性衰减的速率越快,但RC网络的节数越多,元件参数计算越繁琐,电路调试越困难。任何高阶滤波器均可以用较低的二阶RC有滤波器级联实现。 1、低通滤波器(LPF) 低通滤波器是用来通过低频信号衰减或抑制高频信号。 如图9-2(a)所示,为典型的二阶有源低通滤波器。它由两级RC滤波环节与同相比例运算电路组成,其中第一级电容C接至输出端,引入适量的正反馈,以改善幅频特性。 图9-2(b)为二阶低通滤波器幅频特性曲线。

(a)电路图 (b)频率特性 图9-2 二阶低通滤波器 电路性能参数 1 f uP R R 1A + = 二阶低通滤波器的通带增益 RC 2π1 f O = 截止频率,它是二阶低通滤波器通带与阻带的界限频率。 uP A 31 Q -= 品质因数,它的大小影响低通滤波器在截止频率处幅频特性的形状。 2、高通滤波器(HPF ) 与低通滤波器相反,高通滤波器用来通过高频信号,衰减或抑制低频信号。 只要将图9-2低通滤波电路中起滤波作用的电阻、电容互换,即可变成二阶有源高通滤波器,如图9-3(a)所示。高通滤波器性能与低通滤波器相反,其频率响应和低通滤波器是“镜象”关系,仿照LPH 分析方法,不难求得HPF 的幅频特性。 (a) 电路图 (b) 幅频特性 图9-3 二阶高通滤波器 电路性能参数A uP 、f O 、Q 各量的函义同二阶低通滤波器。 图9-3(b )为二阶高通滤波器的幅频特性曲线,可见,它与二阶低通滤波器的幅频特性曲线有“镜像”关系。 3、 带通滤波器(BPF )

实验--集成运算放大器的基本应用

实验集成运算放大器的基本应用(Ⅱ)——有源滤波器一、实验目的 1、熟悉用运放、电阻和电容组成有源低通滤波、高通滤波和带通、带阻滤波器。 2、学会测量有源滤波器的幅频特性。 二、实验原理 (a)低通(b)高通 (c) 带通(d)带阻 图9-1 四种滤波电路的幅频特性示意图 由RC元件与运算放大器组成的滤波器称为RC有源滤波器,其功能是让一定频率范围内的信号通过,抑制或急剧衰减此频率范围以外的信号。可用在信息处理、数据传输、抑制干扰等方面,但因受运算放大器频带限制,这类滤波器主要用于低频范围。根据对频率范围的选择不同,可分为低通(LPF)、高通(HPF)、带通(BPF)与带阻(BEF)等四种滤波器,它们的幅频特性如图9-1所示。

具有理想幅频特性的滤波器是很难实现的,只能用实际的幅频特性去逼近理想的。一般来说,滤波器的幅频特性越好,其相频特性越差,反之亦然。滤波器的阶数越高,幅频特性衰减的速率越快,但RC 网络的节数越多,元件参数计算越繁琐,电路调试越困难。任何高阶滤波器均可以用较低的二阶RC 有滤波器级联实现。 1、 低通滤波器(LPF ) 低通滤波器是用来通过低频信号衰减或抑制高频信号。 如图9-2(a )所示,为典型的二阶有源低通滤波器。它由两级RC 滤波环节与同相比例运算电路组成,其中第一级电容C 接至输出端,引入适量的正反馈,以改善幅频特性。 图9-2(b )为二阶低通滤波器幅频特性曲线。 (a)电路图 (b)频率特性 图9-2 二阶低通滤波器 电路性能参数 1 f uP R R 1A += 二阶低通滤波器的通带增益 RC 2π1f O = 截止频率,它是二阶低通滤波 器通带与阻带的界限频率。 uP A 31Q -= 品质因数,它的大小影响低 通滤波器在截止频率处幅频特性的形状。

运算放大器应用电路的设计与制作 (一) 运算放大器 1.原理 运算放大器是目前应用最广泛的一种器件,当外部接入不同的线性或非线性元器件组成输入和负反馈电路时,可以灵活地实现各种特定的函数关系。在线性应用方面,可组成比例、加法、减法、积分、微分、对数等模拟运算电路。 运算放大器一般由4个部分组成,偏置电路,输入级,中间级,输出级。 图1运算放大器的特性曲线 图2运算放大器输入输出端图示 图1是运算放大器的特性曲线,一般用到的只是曲线中的线性部分。如图2所示。U -对应的端子为“-”,当输入U -单独加于该端子时,输出电压与输入电压U -反相,故称它为反相输入端。U +对应的端子为“+”,当输入U +单独由该端加入时,输出电压与U +同相,故称它为同相输入端。 输出:U 0= A(U +-U -) ; A 称为运算放大器的开环增益(开环电压放大倍数)。 在实际运用经常将运放理想化,这是由于一般说来,运放的输入电阻很大,开环增益也很大,输出电阻很小,可以将之视为理想化的,这样就能得到:开环电压增益A ud =∞;输入阻抗r i =∞;输出阻抗r o =0;带宽f BW =∞;失调与漂移均为零等理想化参数。 2.理想运放在线性应用时的两个重要特性 输出电压U O 与输入电压之间满足关系式:U O =A ud (U +-U -),由于A ud =∞,而U O 为有限值,因此,U +-U -≈0。即U +≈U -,称为“虚短”。

由于r i =∞,故流进运放两个输入端的电流可视为零,即I IB =0,称为“虚断”,这说明运放对其前级吸取电流极小。 上述两个特性是分析理想运放应用电路的基本原则,可简化运放电路的计算。 3. 运算放大器的应用 (1)比例电路 所谓的比例电路就是将输入信号按比例放大的电路,比例电路又分为反向比例电路、同相比例电路、差动比例电路。 (a) 反向比例电路 反向比例电路如图3所示,输入信号加入反相输入端: 图3反向比例电路电路图 对于理想运放,该电路的输出电压与输入电压之间的关系为: 为了减小输入级偏置电流引起的运算误差,在同相输入端应接入平衡电阻 R ’=R 1 // R F 。 输出电压U 0与输入电压U i 称比例关系,方向相反,改变比例系数,即改变两个电阻的阻值就可以改变输出电压的值。反向比例电路对于输入信号的负载能力有一定的要求。 (b) 同向比例电路 同向比例电路如图4所示,跟反向比例电路本质上差不多,除了同向接地的一段是反向输入端: i 1 f O U R R U - =

综合电子系统实习报告 设计题目:8位加法器和减法器的设计

一、实习目的:综合电子系统实习是电子信息类专业学生了解电子系统设计实现过程,培养实践动手能力的实践性教学环节,是电子信息工程等理工科专业学生一门必修的实践性课程。通过学习和实践,可以让学生进一步接触电子元器件,电子材料及电子产品的生产实际,了解电子工艺的一般知识和掌握基本电路板的制作,元件的焊接,产品的组装等技能,了解电子工艺生产线的流程和基本管理知识,使学生通过设计一个课题,巩固和加深在“模拟电子技术基础”和“数字电子技术基础”等课程中所学到的理论知识和实验技能,掌握常用电子电路中的一般分析和设计方法,熟悉protel和其他开发软件的使用方法,提高电子电路的分析、设计和实验能力,为以后从事生产和科研工作打下一定的基础,为今后专业实验,毕业设计准备必要的工艺知识和操作技能。同时培养学生严谨的工作作风,养成良好的工作习惯,它是基本技能和工艺知识的入门向导,又是创新实践和创新精神的启蒙。综合电子系统实习对训练我们基本操作技能,提高我们实际动手能力是难得的一次好机会。 二、实习基本内容和要求: (1)掌握常用电子元器件的种类,性能,选用原则及质量辨别; (2)掌握电子产品装配及材料; (3)学会印制电路板的制作,掌握锡焊原理及手工焊接工艺技术; (4)学会器件的装配,焊接,调试; (5)学会使用常用电子测试仪器设备,初步具有借助说明书或资料掌握常用工具,仪器的使用能力; (6)掌握常用电子电路的设计方法,学会系统实物制作和调试。 三、实习工具: (1)电烙铁:由于焊接的元件多,所以使用的是外热式电烙铁,功率为30w,烙铁头是铜制。 (2)螺丝刀、钻孔机、斜口钳、尖嘴钳等必备工具。 (3)焊锡,由于锡它的熔点低,焊接时,焊锡能迅速散步在金属表面焊接牢固,焊点光亮美观。 (4)数字万用表,5V直流稳压电源。 要求:1、利用逻辑门电路设计8位加法器和减法器,实现两个8位二进制数的加法运算和减法运算; 2、具有进位信号输入和输出能力; 3、通过功能选择控制信号F选择运算功能,F=0,加法运算,F=1, 进行减法运算; 4、用发光二极管显示两个输入数据和运算结构。 1、设计原理:

单电源供电集成运算放大器的电路及其应用 文章包括以下四个部分 一、单电源运放应用:基础知识 二、单电源运放应用:基本电路 三、单电源运算放大器电路应用:滤波 四、单电源运算放大器的偏置与去耦电路设计 大多数集成运算放大器电略部采用正、负对称的双电源供电,在只有一组电源的情况下,集成运算放大器也能正常工作。图1所示为两种采用单电源供电的供电电路。 采用单电源对集成这算放大器供电的常用方法是,把集成运算放大器两输入端电位抬高(且通常抬高至电源电压的一半,即E+/2),抬高后的这个电位就相当于双电源供电时的“地”电位,因此在静态工作时,输出端的电位也将等于两输入端的静态电位,即E+/2。 图中,集成运算放大器两输入端抬高的电压由R4、R5对电源分压后产生,约等于E+ /2;C2为滤波电容;C1和C3分别为输入、输出隔直电容。为了减小输入失调电流的影响,图1(a)中R1应等于R2与R4的并联值,图1(b)中R1应等于R2与R3的并联值。 图1(a)为反相输入方式,电路的交流放大倍数为R4/R3=100倍;图1(b)为同相输入方式,电路的交流放大倍数为R3/R2=10倍。

单电源运放应用图集(一):基础知识 我们经常看到很多非常经典的运算放大器应用图集,但是这些应用都建立在双电源的基础上,很多时候,电路的设计者必须用单电源供电,但是他们不知道该如何将双电源的电路转换成单电源电路。 在设计单电源电路时需要比双电源电路更加小心,设计者必须要完全理解这篇文章中所述的内容。 1.1 电源供电和单电源供电 所有的运算放大器都有两个电源引脚,一般在资料中,它们的标识是VCC+和VCC -,但是有些时候它们的标识是VCC+和GND。这是因为有些数据手册的作者企图将这种标识的差异作为单电源运放和双电源运放的区别。但是,这并不是说他们就一定要那样使用――他们可能可以工作在其他的电压下。在运放不是按默认电压供电的时候,需要参考运放的数据手册,特别是绝对最大供电电压和电压摆动说明。 绝大多数的模拟电路设计者都知道怎么在双电源电压的条件下使用运算放大器,比如图一左边的那个电路,一个双电源是由一个正电源和一个相等电压的负电源组成。一般是正负15V,正负12V和正负5V也是经常使用的。输入电压和输出电压都是参考地给出的,还包括正负电压的摆动幅度极限Vom以及最大输出摆幅。 单电源供电的电路(图一中右)运放的电源脚连接到正电源和地。正电源引脚接到VCC +,地或者VCC-引脚连接到GND。将正电压分成一半后的电压作为虚地接到运放的输入引脚上,这时运放的输出电压也是该虚地电压,运放的输出电压以虚地为中心,摆幅在Vom 之内。有一些新的运放有两个不同的最高输出电压和最低输出电压。这种运放的数据手册中会特别分别指明Voh 和Vol 。需要特别注意的是有不少的设计者会很随意的用虚地来参考输入电压和输出电压,但在大部分应用中,输入和输出是参考电源地的,所以设计者必须在输入和输出的地方加入隔直电容,用来隔离虚地和地之间的直流电压。(参见1.3节) 图一 通常单电源供电的电压一般是5V,这时运放的输出电压摆幅会更低。另外现在运放的供电电压也可以是3V 也或者会更低。出于这个原因在单电源供电的电路中使用的运放