FPGA和可靠性有关的几个概念

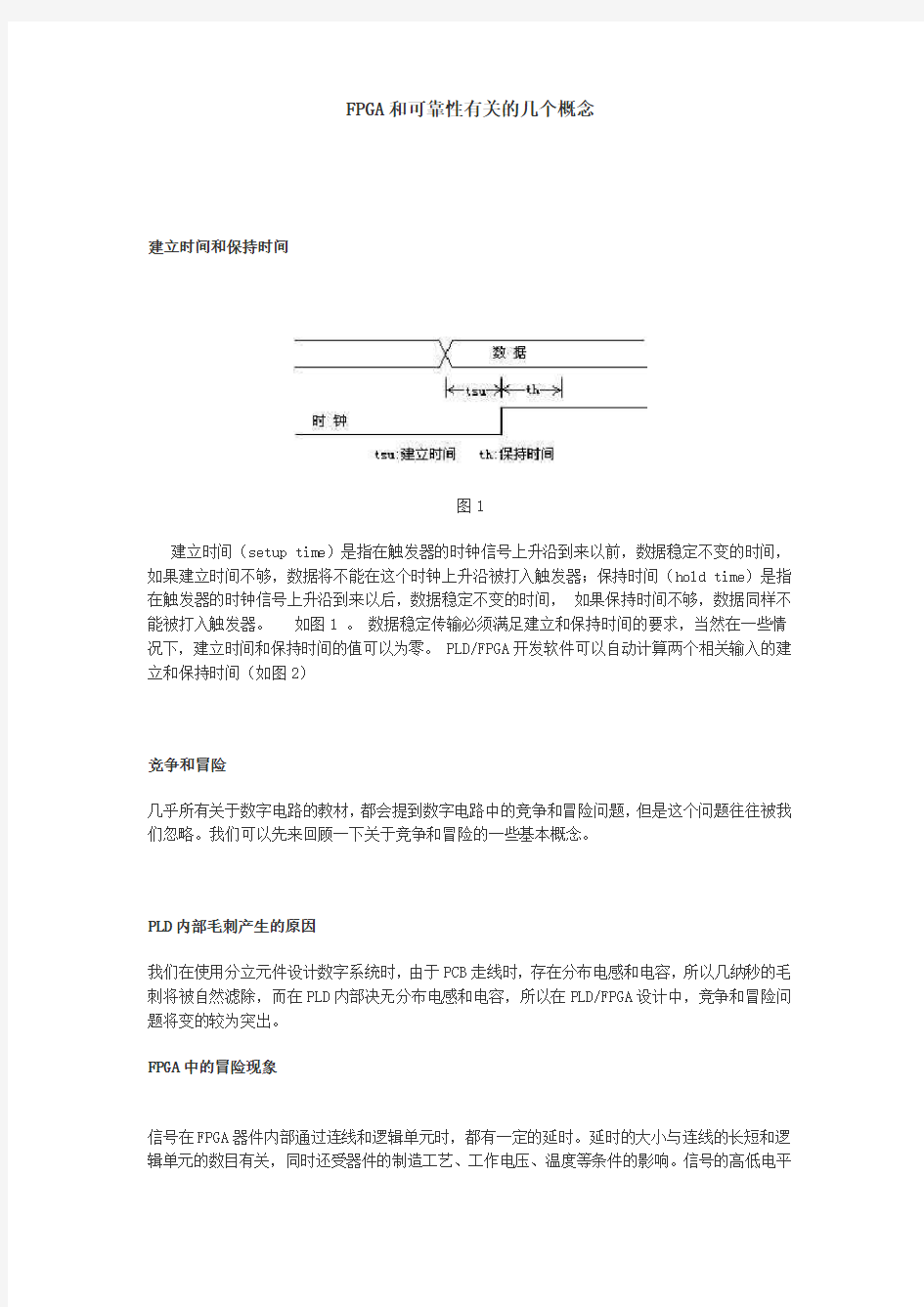

建立时间和保持时间

图1

建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。如图1 。数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。 PLD/FPGA开发软件可以自动计算两个相关输入的建立和保持时间(如图2)

竞争和冒险

几乎所有关于数字电路的教材,都会提到数字电路中的竞争和冒险问题,但是这个问题往往被我们忽略。我们可以先来回顾一下关于竞争和冒险的一些基本概念。

PLD内部毛刺产生的原因

我们在使用分立元件设计数字系统时,由于PCB走线时,存在分布电感和电容,所以几纳秒的毛刺将被自然滤除,而在PLD内部决无分布电感和电容,所以在PLD/FPGA设计中,竞争和冒险问题将变的较为突出。

FPGA中的冒险现象

信号在FPGA器件内部通过连线和逻辑单元时,都有一定的延时。延时的大小与连线的长短和逻辑单元的数目有关,同时还受器件的制造工艺、工作电压、温度等条件的影响。信号的高低电平

转换也需要一定的过渡时间。由于存在这两方面因素,多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,往往会出现一些不正确的尖峰信号,这些尖峰信号称为"毛刺"。如果一个组合逻辑电路中有"毛刺"出现,就说明该电路存在"冒险"。(与分立元件不同,由于PLD内部不存在寄生电容电感,这些毛刺将被完整的保留并向下一级传递,因此毛刺现象在PLD、FPGA设计中尤为突出)

图6.21给出了一个逻辑冒险的例子,从图6.22的仿真波形可以看出,"A、B、C、D"四个输入信号经过布线延时以后,高低电平变换不是同时发生的,这导致输出信号"OUT"出现了毛刺。(我们无法保证所有连线的长度一致,所以即使四个输入信号在输入端同时变化,但经过PLD内部的走线,到达或门的时间也是不一样的,毛刺必然产生)。可以概括的讲,只要输入信号同时变化,(经过内部走线)组合逻辑必将产生毛刺。将它们的输出直接连接到时钟输入端、清零或置位端口的设计方法是错误的,这可能会导致严重的后果。所以我们必须检查设计中所有时钟、清零和置位等对毛刺敏感的输入端口,确保输入不会含有任何毛刺

图6.21 存在逻辑冒险的电路示例

图6.22 图6.21所示电路的仿真波形

冒险往往会影响到逻辑电路的稳定性。时钟端口、清零和置位端口对毛刺信号十分敏感,任何一点毛刺都可能会使系统出错,因此判断逻辑电路中是否存在冒险以及如何避免冒险是设计人员必须要考虑的问题。

判断一个逻辑电路在某些输入信号发生变化时是否会产生冒险,首先要判断信号是否会同时变化,

然后判断在信号同时变化的时候,是否会产生冒险,这可以通过逻辑函数的卡诺图或逻辑函数表达式来进行判断。对此问题感兴趣的读者可以参考有关脉冲与数字电路方面的书籍和文章。

如何处理毛刺

我们可以通过改变设计,破坏毛刺产生的条件,来减少毛刺的发生。例如,在数字电路设计中,常常采用格雷码计数器取代普通的二进制计数器,这是因为格雷码计数器的输出每次只有一位跳变,消除了竞争冒险的发生条件,避免了毛刺的产生。

毛刺并不是对所有的输入都有危害,例如D触发器的D输入端,只要毛刺不出现在时钟的上升沿并且满足数据的建立和保持时间,就不会对系统造成危害,我们可以说D触发器的D输入端对毛刺不敏感。根据这个特性,我们应当在系统中尽可能采用同步电路,这是因为同步电路信号的变化都发生在时钟沿,只要毛刺不出现在时钟的沿口并且不满足数据的建立和保持时间,就不会对系统造成危害。(由于毛刺很短,多为几纳秒,基本上都不可能满足数据的建立和保持时间)

以上方法可以大大减少毛刺,但它并不能完全消除毛刺,有时,我们必须手工修改电路来去除毛刺。我们通常使用"采样"的方法。一般说来,冒险出现在信号发生电平转换的时刻,也就是说在输出信号的建立时间内会发生冒险,而在输出信号的保持时间内是不会有毛刺信号出现的。如果在输出信号的保持时间内对其进行"采样",就可以消除毛刺信号的影响。

有两种基本的采样方法:一种方法是在输出信号的保持时间内,用一定宽度的高电平脉冲与输出信号做逻辑"与"运算,由此获取输出信号的电平值。图6.23说明了这种方法,采样脉冲信号从输入引脚"SAMPLE"引入。从图6.24的仿真波形上可以看出,毛刺信号出现在"TEST"引脚上,而"OUT"引脚上的毛刺已被消除了.

图6.23 消除毛刺信号的方法之一

图6.24 图6.23所示电路的仿真波形

上述方法的一个缺点是必须人为的保证sample信号必须在合适的时间中产生,另一种更常见的方法是利用D触发器的D输入端对毛刺信号不敏感的特点,在输出信号的保持时间内,用触发器读取组合逻辑的输出信号,这种方法类似于将异步电路转化为同步电路。图6.25给出了这种方法的示范电路,图6.26是仿真波形。

图6.25 消除毛刺信号方法之二

图6.26 图6.25所示电路的仿真波形

在仿真时,我们也可能会发现在FPGA器件对外输出引脚上有输出毛刺,但由于毛刺很短,加上PCB本身的寄生参数,大多数情况下,毛刺通过PCB走线,基本可以自然被虑除,不用再外加阻容滤波。

如前所述,优秀的设计方案,如采用格雷码计数器,同步电路等,可以大大减少毛刺,但它并不能完全消除毛刺。毛刺并不是对所有输入都有危害,例如D触发器的D输入端,只要毛刺不出现在时钟的上升沿并且满足数据的建立和保持时间,就不会对系统造成危害。因此我们可以说D触发器的D输入端对毛刺不敏感。但对于D触发器的时钟端,置位端,清零端,则都是对毛刺敏感的输入端,任何一点毛刺就会使系统出错,但只要认真处理,我们可以把危害降到最低直至消除。下面我们就对几种具体的信号进行探讨。

时钟信号

最关键的信号之一,有专门的论述,请参阅有关门控时钟的讨论

清除和置位信号

清除和置位信号要求象对待时钟那样小心地考虑它们,因为这些信号对毛刺也是非常敏感的。正如使用时钟那样,最好的清除和置位是从器件的引脚单直接地驱动。有一个主复位Reset引脚是常用的最好方法,主复位引脚给设计项目中每个触发器馈送清除或置位信号。几乎所有PLD

器件都有专门的全局清零脚和全局置位。如果必须从器件内产生清除或置位信号,则要按照“门控时钟”的设计原则去建立这些信号,确保输入无毛刺。

若采用门控清除或者门控置位,则单个引脚或者触发器作为清除或置位的源,而有其它信号作为地址或控制线。在清除或复位的有效期间,地址或控制线必须保持稳定图4.2.13示出4个容许的清除和复位配置的实例。决不能用多级逻辑或包含竞争状态单级逻辑产生清除或置位信号。更详细的考虑见4.2.5节“竞争状态”。

组合逻辑输出

当PLD输出引脚给出系统内其它部分的边沿敏感信号或电平敏感信号时,这些出信号必须象内部时钟、清除和置位信号一样小心地对待。只要可能就应在PLD输出端寄存那些对险象敏感的组合输出。如果你不能寄存险象敏感的输出,则应符合“门控时钟”中讨论的门控时钟的条件。决不能用多级逻辑驱动毛刺敏感的输出。

异步输入信号

按照定义,异步输入不是总能满足(它们所馈送的触发器的)建立和保持时间的要求。因此,异步输入常常会把错误的数据锁存到触发器,或者使触发器进入亚稳定的状态,在该状态下,触发器的输出不能识别为l或0。如果没有正确地处理,亚稳性会导致严重的系统可靠性问题。

图4.2.14示出具有异步信号控制使能输入的二进制计数器。当使能输入违反计数;的建立时间或保持时间的约束条件时,计数器的每一位会有错误的动作。一位在加法:数器而另一位在保持状态,造成计数器进入无效状态。此外,各位中的任何一位都可1变成亚稳定的,使电路的其它部分出现各种问题。

采用附加触发器同步使能信号的方法可保证不违反计数器的建立时间,从而解决可靠性的问题。图4.2.15示出一种同步化的方法。虽然同步触发器仍会感受到亚稳性,但它在下一个时钟边沿之前是稳定的。通常,为在EPLD中避免亚稳性问题,决不能把一个异步信号输出到器件内两个或更多的触发器中。同步异步输入的另一种方法示于图4.2.16。输入驱动一个触发器的时钟,该触发器的数据输入接到Vcc。这个电路对于检测短于一个时钟周期的异步事件是有用的。

寄存异步输入信号

亚稳定状态。图4.4.10示出了一个具有异步输入的状态机。图乙4.10 带有异步输入的状态机图4.4。1l表明了如何通过增加输入寄存器,以确保满足状态机所要求的建立时间和保持时间。虽然增加的寄存器仍然要面对可能出现的c违反建立和保持时间的现象,但是已防止状态寄存器进入亚稳态,状态机也不会进入未定义的状态。

组合逻辑电路中的竞争与冒险 前面分析组合逻辑电路时,都没有考虑门电路的延迟时间对电路产生的影响。实际上, 从信号输入到稳定输出需要一定的时间。由于从输入到输出的过程中, 不同通路上门的级数不同, 或者门电路平均延迟时间的差异, 使信号从输入经不同通路传输到输出级的时间不同。由于这个原因, 可能会使逻辑电路产生错误输出,通常把这种现象称为竞争冒险。 竞争:在组合逻辑电路中, 某个输入变量通过两条或两条以上途径传到输出门的输入端, 由于每条途径的延迟时间不同帮到达输出门的时间就有先有后, 这种现象称为竞争。 冒险:是指数字电路中, 某个瞬间出现了非预期信号的现象, 即某一瞬间数字电路出现了违背真值表所规定的逻辑电平。这样就出现了不该出现的尖脉冲, 一、 竞争冒险的概念及其产生的原因 以图示电路为例可看出, 大多数组合电路都存在竞争, 但所有竞争不一定都产生错误的干扰脉冲。竞争是产生冒险的必然条件, 而冒险并非竞争的必然结果。由以上分析可知, 只要两个互补的信号送入同一门电路, 就可能出现竞争冒险。因此把冒险现象分为两种: 1. “ 0”型冒险

A A +冒险在理想情况下输出电平为“ 1” , 由于竞争输出产生低电平窄脉冲。 A A ?冒险在理想情况下输出电平为“ 0” ,由于竞争输出产生高电平窄脉冲。 二、竞争冒险的判断方法 判断竞争冒险是否存在的方法很多,最常见的方法有: 1.代数法 在逻辑函数表达式中, 是否存在某变量的原变量和反变量。若去掉其他变量得到 A A Y +=,电路有可能产生“ 0”冒险;若得到 A A Y ?=,则可能产生“ 1” 冒险。 2.卡诺图法 画出逻辑函数的卡诺图, 当卡诺图中两个合并最小项圈相切, 即两个合并最小项圈相邻—有相邻项, 各合并最小项圈各自独立—不相交时, 这个逻辑函数有可能出现冒险现象。 三、消除竞争冒险的方法 1.修改逻辑设计 (1代数法 ①逻辑变换消去互补量 ((C A B A Y ++=当 B =C=0时, A A Y ?=, 存在竞争冒险。若将逻辑函数表达式进行逻辑变换,则 BC B A AC Y ++=,这时消去了 A A ?互补量,从而不会产生竞争冒险。②增加乘积项 C A AB Y +=当 B=C=1时, A A Y +=,存在竞争冒险。若增加乘积项 BC , 则 BC C A AB Y ++=,消除了竞争冒险。 (2卡诺图法 将卡诺图中相切的圈用一个多余的圈连接起来,即可消除冒险现象。

31仿真与测试竞争冒 险现象

项目三组合逻辑电路 任务一仿真与测试竞争冒险现象 【学习目标】 1.掌握组合逻辑电路的分析方法; 2.掌握组合逻辑电路的简单设计方法; 3.掌握组合逻辑电路的竞争冒险及消除方法。 【任务引入】 按照逻辑功能不同,数字电路常分两大类:一类组合逻辑电路(简称组合电路);另一类时序逻辑电路(简称时序电路)。如果一个逻辑电路在任何时刻的输出状态只取决于该时刻的输入状态,与电路原来状态无关,这样的电路称为组合逻辑电路。本节课内容我们学习组合逻辑电路的分析与设计方法,了解并掌握组合逻辑电路中的竞争冒险现象及其消除方法。 【基本理论】 一、组合逻辑电路概述 1.组合逻辑电路在电路结构上的特点: (1)构成电路基本元件是门电路,不含记忆单元(存储元件); (2)只有从输入到输出通路,没有从输出反馈到输入回路。 2.组合电路逻辑功能的描述 描述组合电路逻辑功能的方法有逻辑函数式、真值表、逻辑图、工作波形图、卡诺图等几种。 3-1-1 组合逻辑电路的框图 组合逻辑电路n个输入端,用x1,x2,…,xn表输入变量; 有m个输出端,用y1,y2,…,ym表示输出变量,输出变量与输入变量间逻辑关系: y1 =f1(x1,x2,…,xn) y2 =f2(x1,x2,…,xn) … ym =fm(x1,x2,…,xn) 二、组合逻辑电路的分析与设计 1.组合逻辑电路的分析 步骤如下: (1)用逐级递推法写出输出逻辑函数与输入逻辑变量之间的关系; (2)用公式法或者卡诺图法化简,写出最简逻辑表达式;

(3)根据最简逻辑函数式列出功能真值表; (4)根据真值表写出逻辑功能说明,以便理解电路的作用。 例3-1-1:分析下图3-1-2三变量组合逻辑电路的功能。 图3-1-2 三变量组合逻辑电路 解: 第一步:写出输出逻辑函数与输入逻辑变量之间的关系,如下: 第二步:化简写出最简逻辑表达式,得:F=AB+BC+CA 第三步:列出功能真值表 第四步:写出逻辑功能说明 当输入A 、B 、C 中有2个或3个为1时,输出Y 为1,否则输出Y 为 0。所以这个电路实际上是一种3人表决用的组合电路:只要有2票或3 票同意,表决就通过。 2.组合逻辑电路的设计 组合逻辑电路的设计是根据给定的实际逻辑功能,找出实现该功能的逻辑电路。步骤如下: (1)根据给出的条件,找出什么是逻辑变量,什么是逻辑函数,用字母设 出,另外用0和1各表示一种状态,找出逻辑函数和逻辑变量之间的 关系; (2)根据逻辑函数和逻辑变量之间的关系列出真值表,并根据真值表写出逻辑表达式; C AB F =1BC F =2CA F =3AC BC AB F F F F 321==

芯片功能的增加和数据吞吐量的要求,促使芯片行业从较低数据率的并行连接,转向较高速度的串行连接。SERDES(Serializer-Dese rializer,)是经高速差分对,而不是经较低速度的并行总线传输串行化的数据。一个实例是用单个PCI-Express通道,替代传统的32位、64MHz PCI总线(可达到2.112Gb/s),仅用4条线(运行在2.5GHz),可达到4Gb/s 总数据率。简言之,SERDES协议允许用较少的引脚数传输较高的数据率。 典型的SERDES的FPGA实现 图1给出在复杂的FPGA实现中各种可能的SERDES接口,包括数据通路(芯片到芯片,SPI 4.2,PCI-Express,SGM11)、背板(GbE/GSM11,PCI Express/AS,专用)接口、存储器接口(DDR1/ⅡSDRAM,QDRⅡSRAM)。可由FPGA实现的芯片包括存储器控制器、帧调节器/MAC、DSP协处理器、控制板接口和背板驱动器。 SERDES接口有两类:源同步(SS)接口和时钟数据恢复(CDR)接口。这两类接口的基本差别是如何实现同步。源同步接口有一个伴随传输数据的分离时钟信号。CDR没有分离的时钟信号,代之以嵌入在数据开关转换中的时钟。这就是说,CDR接收机将锁相数据信号本身来得到时钟。表1给出这两类接口的基本差别。CDR接口通常运行在较高的速度和较长的距离,因而会带来较大的设计问题。基于此原因,本文主要集中在CDR方面。 图1 典型的SERDES应用 时钟数据恢复 时钟数据恢复(CDR)接收机必须恢复来自数据的嵌入式时钟。更确切地说,时钟起源于数据信令的开关转换。CDR发送到串行化数据开始,然后,变换数据为8b/10b(或类似的编码方法)。编码取8位数据,并变换此数据为10位符号。8b/10b编码在

一.ISE实现的步骤 在综合之后,我们开始启动FPGA在ISE中的实现过程,整个过程包括以下几个步骤: 1.Translate - 将输入的网表文件和约束文件整合后输出到一个Xilinx私有的通用数据库文件 (Native Generic Database,NGD)中。 2.MAP-将设计映射到目标器件的资源上,可以选择在此阶段完成资源的布局。 3.Place and Route-按照时序约束的要求,完成设计的布局布线。 4.Generate Programming File- 生成一个可下载到FPGA器件的bit流文件。 本文将会详细的介绍如何完成一个设计的实现过程以及实现过程的这四个步骤。 二.启动实现过程的方法 1.在design窗口的第一行,找到view选项,选中Implementation模式,表示design窗口中显示的是Implementation过程的界

面。新建工程中默认选择Implementation 模式。 2.在design窗口上半部分的hierarchy子窗口中,点击顶层文件。 3.在design窗口下半部分的processes子窗口中,可以双击Implement Design启动完整实现过程,也可以右键选中run启动 完整实现过程。同时,可以展开Implement Design,单独执行Translate、MAP、Place and Route等过程。Implement 结束以后,可以双击Generate Programming File生成bit流文件。Generate Programming File过程也可以通过邮件选中 run来启动。 三.Translate Translate过程将输入的所有网表文件和约束文件进行整合,输出到一个NGD(Native Generic Database)文件中。NGD文件是Xilinx自定义的一种通用数据库文件,在文件中设计被映射成各种NGD 定义的基元,例如与门、或门、LUTs、flip-flops和RAM等。NGD文件中同时包含着原始网表文件中描

实验题目:组合电路中的竞争和冒险 姓名:班级:学号: 实验时间: 一.实验目的: 1、观察组合电路中的竞争与冒险现象,了解竞争冒险的实验原理 2、了解消除竞争与冒险的方法 二.实验仪器及器件: 1、实验箱、万用表、示波器 2、74LS00,74LS20 三.实验原理: 1、竞争冒险的原理 (1)竞争: 在组合逻辑电路中,某个输入变量通过两条或两条以上的途径传到输出端,由于每条途径延迟时间不同,到达输出门的时间就有先有后,这种现象称为竞争。 (2)冒险:信号在器件内部通过连线和逻辑单元时,都有一定的延时。延时的大小与连线的长短和逻辑单元的数目有关,同时还受器件的制造工艺、工作电压、温度等条件的影响。信号的高低电平转换也需要一定的过渡时间。由于存在这两方面因素,多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,往往会出现一些不正确的尖峰信号,这些尖峰信号称为"毛刺"。如果一个组合逻辑电路中有"毛刺"出现,就说明该电路存在冒险。 (3)竞争冒险产生原因:由于延迟时间的存在,当一个输入信号经过多条路径传送后又重新会合到某个门上,由于不同路径上门的级数不同,或者门电路延迟时间的差异,导致到达会合点的时间有先有后,从而产生瞬间的错误输出。 (4)竞争与冒险的关系:有竞争不一定会产生冒险,但有冒险就一定有竞争。 2、冒险现象的判别 Y=A?A’可能出现1型冒险 Y=A+A’可能出现0型冒险 3、消除竞争冒险的方法 (1)利用冗余项法: 利用冗余项消除毛刺有2 种方法:代数法和卡诺图法法: a、代数法,在产生冒险现象的逻辑表达式上,加上冗余项或乘上冗余因子; b、卡诺图法,将卡诺图中相切的圈用一个多余的圈连接起来。 (2)选通法: 在电路中加入选通信号,在输出信号稳定后,选通允许输出,从而产生正确输出。 滤出法: 由于冒险脉冲是一个非常窄的脉冲,可以在输出端接一个几百微法的电容将其滤出掉。 (3)常用消除方法: 1、接入滤波电容Cf; 2、引入选通脉冲; 3、修改逻辑设计; 4、.利用可靠性编码; 5、引入封锁脉冲。

1. 什么是竞争冒险? 信号在通过连线和逻辑单元时,都有一定的延时。延时的大小与连线的长短和逻辑单元的数目有关,同时还受器件的制造工艺、工作电压、温度等条件的影响。信号的高低电平转换也需要一定的过渡时间。由于存在这两方面因素,多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,成为“竞争”;往往导致出现一些不正确的尖峰信号,这些尖峰信号称为"毛刺"。 如果一个组合逻辑电路中有"毛刺"出现,就说明该电路存在“冒险”。冒险是由变量的竞争引起的。冒险又分为逻辑冒险和功能冒险。 简言之:在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争,竞争产生冒险。 2. 竞争冒险产生的原因?(1)根本原因:延迟(2)详细分析: 竞争冒险的产生受到四个要素的制约,即:时间延迟、过渡时间、逻辑关系和延迟信号相位。 [1]时间延迟,即信号在传输中受路径、器件等因素影响,输入端信号间出现的时间差异 [2]过渡时间,即脉冲信号状态不会发生突变,必须经历一段极短的过渡时间 [3]逻辑关系,即逻辑函数式 [4]延迟信号相位,即延迟信号状态间的相位关系,涵盖延迟信号同相位和延迟信号反相位两个方面。延迟信号状态变化相同的则是延迟信号同相位,反之则是反相位。 时间延迟和过渡时间要素是竞争冒险的产生原因,逻辑关系和延迟信号相位要素是竞争冒险的产生机制。由原因和机制,构成竞争冒险的产生条件。当电路满足产生条件时,则一定产生毛刺。 3. 如何判断有竞争冒险? 3.1 逻辑冒险的判断方法有两种: 1). 代数法: 在逻辑函数表达式中,若某个变量同时以原变量和反变量两种形式出现,例如:逻辑函数在一定条件下可简化为Y=A+A反或Y=A*A反就具备了竞争条件。去掉其余变量(也就是将其余变量取固定值0或1),留下有竞争能力的变量,如果表达式为F=A+A~(用A~表示A的反变量,以下同),就会产生0型冒险(F应该为1而实际却为0);如果表达式为F=AA~,就会产生1型冒险。例:表达式 F=AB+CB~,当A=C=1时,F=B+B~,在B发生跳变时,可能出现0型冒险。 2). 卡诺图法:将函数填入卡诺图,按照函数表达式的形式圈好卡诺圈。 A\BC| 00 01 11 10 ----------------------- 0 | 0 0 0 1 1 | 0 1 1 1 F=AC+BC~的卡诺图(将101和111的1圈一起,010和110的1圈一起)通过观察发现,这两个卡诺圈相切。则函数在相切处两值间跳变时发生逻辑冒险。(前提是这两个卡诺圈没有被其他卡诺圈包围) 3.2 功能冒险的判断: 功能冒险是当多个输入信号同时变化的瞬间,由于变化快慢不同而引起的冒险。 卡诺图法:依然用上面的卡诺图,按同样函数圈好。举例F=AC+BC~中,ABC从111变为

FPGA设计与应用 串口通信实验报告 班级:1105103 姓名:苏林效 学号:1110510321 日期:2014年10月29日

实验性质:验证性实验类型:必做 开课单位:电信院学时:2学时 一、实验目的 1、了解串口通信的基本原理; 2、掌握锁相环的基本原理和使用方法; 3、掌握起始位和停止位的含义及实现方法; 4、掌握VHDL状态机的基本使用方法; 5、掌握基本的接口设计和调试技巧; 二、实验准备 2.1 串口通信原理(1分) 串口通信是以字节为单位,按位传输数据和接收数据的。 先看一下发送数据:串行线缆的两端事先约定好串行传输的参数(传输速度、传输格式等),之后进行传输,①当没有数据传输的时候,发送端向数据线上发送“1”;②当要传输数据时,发送端先发送一个“0”来表示要传输数据了,这样当接收端检测到“0”便可以知道有数据到来了;③开始传输后,数据以约定的速度和格式传输;④每次传输完成一个字节之后,都在其后发送一个停止位“1”。这样,发送数据就结束了。 再来看接收数据,初始状态是等待状态,接收的一直是“1”,当检测到0时进入检验状态,在检验状态下如果再检测到0(一般采用过采样)则进入接收数据状态,当接收完8位比特数后判断是否有停止位,如果有则此字节接收结束,重新进入等待状态准备接受下一字节。 2.2 锁相环的基本原理(1分) 锁相环是以锁定输入载波信号的相位为目标的一种载波环实现形式。它由三部分组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)。如上图。 锁相环的工作原理:压控振荡器的输出经过采集并分频,后与基准信号同时

输入鉴相器。鉴相器通过比较上述两个信号的相位差,输出结果通过环路滤波器,滤除噪声和高频分量,然后输出一个直流脉冲电压,用它来控制VCO ,使它的频率改变,使()lim 0c p t θ=。经过较短时间后,VCO 的输出稳定于某一值。环路一旦进入锁定状态后,压控振荡器的输出信号与环路的输入信号(参考信号)相位时刻保持一致。 三、代码及测试 3.1程序及分析(2分) 顶层原理图如上所示,主要包括三个模块,锁相环(输出57.69MHz )、分频(输出接受时的10倍采样速率和数码管显示速率)、接受(按57.6kbps 接受从串口发来的数据)。 分频模块代码: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY DIV IS PORT(CLK : IN STD_LOGIC; --锁相环输出时钟57.69M COUT1 : OUT STD_LOGIC; --分频器输出采样时钟576k COUT2 : OUT STD_LOGIC);

一、简答题 1、什么是触发器的空翻现象?简述造成空翻现象的原因。 答:如果在一个时钟脉冲的高电平作用下,触发器的状态发生了两次或两次以上的翻转,这叫做“空翻”。 由于是电平触发,在CP=1期间,数据输入端如果连续发生变化,触发器也连续随着变化,直到CP由1变0才停止,造成空翻现象的原因是触发器电平触发。 2.简述时序逻辑电路分析的步骤。 答:(1)观察电路,确定电路类型;是同步时序电路还是异步时序电路;是Mealy 型时序电路还是Moore型时序电路。 (2)根据电路写出各触发器驱动方程及时钟方程(即各触发器的CP信号表达式,如果是同步时序电路,则可不写时钟方程(因为每个触发器均接同一个脉冲源,来一个时钟脉冲,每个触发器同时变化)。 (3)将各触发器的驱动方程带入触发器的特性方程,写出各个触发器次态 1 n Q的逻辑 表达式(即状态方程)。 (4)根据电路写出输出逻辑表达式(输出方程)。 (5)推出时序逻辑电路的状态转换真值表、状态转换图及时序图(又称波形图)。 (6)总结和概括这个时序电路的逻辑功能。 3.最小项的性质。 答:(1)任何一组变量取值下,只有一个最小项的对应值为1; (2)任何两个不同的最小项的乘积为0; (3)任何一组变量取值下,全体最小项之和为1。 4.组合电路产生竞争冒险的原因及常用的消除竞争冒险的方法。 答:在组合电路中,当逻辑门有两个互补输入信号同时向相反状态变化时,输出端可能产生过渡干扰脉冲的现象。常用的消除竞争冒险的方法有:输入端加滤波电容、加封锁或选通脉冲、修改逻辑设计等。 5.简述时序逻辑电路与组合逻辑电路的异同。 答:时序逻辑电路是一种任意时刻的输出不仅取决于该时刻电路的输入,而且还与电路过去的输入有关的逻辑电路。因此,时序逻辑电路必须具备输入信号的存储电路,以便此信号在下一时刻其作用。组合逻辑电路在某一时刻的输出只取决于该时刻逻辑电路的输出,与过去的历史情况无关。因此,不需用存储电路记忆过去的输入,只有门电路就可构成。6.简述触发器的基本性质。 答:每个触发器有两个互非的输出端Q和Q,且有以下两个基本性质: (1)触发器有两个稳定的工作状态 一个是“1”态,即输出端Q=1,Q=0;另一个是“0”态,即输出端Q=0,Q=1。在没有外界信号作用时,触发器维持原有的稳定状态不变。 (2)两个稳定的工作状态相互转变 在外界信号作用下,触发器可以从一个稳定状态翻转为另一个稳定状态。所谓“稳定”的状态,是指没有外界信号作用时,触发器电路中电流和电压均维持恒定数值。 7.逻辑函数的表示方法有哪几种?

摘要 同步是通信系统中很重要的一个过程,它可以使通信系统更稳定、更可靠、更准确,它是数字通信系统有顺序进行的技术支撑。同步分为位同步、帧同步和载波同步,我们对数字通信信号的同步除了载波同步和帧同步之外,还要进行位同步。位同步也就是保证接收端准确有效抽样判决数字基带信号序列的基础,一般位同步信号从解调后的基带信号中提取出来,同时也可以从已调频带信号当中直接提取位同步信号,一般可以进行一元中央位置采样的决定,最好是在接收元素结束时间采样的决定。位同步有插入导频法(一种外同步法)和直接法(一种自同步法),本文运用了数字锁相法提取位同步电路的方案,以大规模可编程逻辑器件FPGA为主控制器,以VHDL硬件描述语言为主要语言对其进行在线编程,在QuartusⅡ软件工具中进行仿真和调试,以达到功耗低、成本低、效率高的技术要求。 关键词:位同步;数字锁相电路;FPGA;VHDL;QuartusⅡ

ABSTRACT Synchronization is a very important process in communication system, it can make the system more stable, more reliable, more accurate, it is the digital communication system has the technical support of the order. Synchronization is divided into bit synchronization, frame synchronization and carrier synchronization, we on the digital communication signal in addition to frame and carrier synchronization and bit synchronization. Bit synchronization is the basis to ensure the correct and effective decision receiver sampling digital baseband signal sequence,general synchronization signal is extracted from the baseband demodulated signals, but also can directly extract bit synchronization signal from the frequency band signal has, in general can be a central position sampling decisions, preferably in the receiving elements in the end time sampling decision. Bit synchronization is the pilot insertion method (a kind of external synchronization method) and direct method (a self synchronizing method), this paper uses digital PLL method of bit synchronization circuit extraction, with the large-scale programmable logic device FPGA as the main controller, using the VHDL hardware description language is the main language of the online programming, simulation and debugging in QuartusⅡsoftware tools, to meet the requirements of low power consumption, low cost, high efficiency technology Keywords: Bit synchronization (symbol extraction process); digital phase locked loop circuit (bit synchronization circuit); FPGA; VHDL; QuartusⅡ

实验十七竞争冒险 一、实验目的 通过实验观察组合电路中存在的竟争冒险现象,学会用实验手段消除责争冒险对电路 的影响. 二、实验内容 1.八位串行奇仍校验电路竞争冒险现象的观察及消除。 图17.1所示电路为八位串行奇偶校验电路。 图17.1八位串行奇、偶校验电路 按图接线。 测试电路的逻辑功能。a.b…g,h分别接逻辑开关K1;~K9,z接发光二级管显示。改变K1~K8的状态.观察并记录Z的变化。

(注:时间关系,仅列举几个有代表性的结果。其中以开关闭合表示“1”,开关断开表示“0”.) K1K2K3K4K5K6K7K8Z 000000001 000000010 000000111 000001110 000011111 000111110 001111111 011111110 111111111 表 由表可以看出每一次开关的断开和闭合都影响发光二极管的状态。

a接脉冲.b.c··h接高电平.用示波器观察并记录a和y湍的波形测出信号经七级异或门的延迟时间。

由上图可以看出,延迟时间为20ms a和h端接同一脉冲.b.c··g为高电平.观察并记录a和y端的波形。说明y端的

波形有何异常现象 如上图所示输出端y出现了原设计中没有的窄脉冲, 若采用加电容的办法来消除此异常现象.则电容C应接在何处 如图所示,滤波电容C应该与输出端并联. ,若设门的输出电阻R0≈100Ω,估算电容C值的大小测出门电路的阈值电压V T

用实验法测出消除上述异常现象所需的电容值.说明产生误差的原因有哪些 2.组合电路竞争冒险现象的观察及消除 组合电路如图17.2所示。 测试电路功能.结果列成真值表形式。 泪实验法测定.在信号变化过程中.竟争冒险在何处,什么时刻可能出现 用校正项的办法来消除竟争冒险.则电路应怎洋修改画出修改后的电路.并用实验验证之。若改用加滤波电容的办法来消除竞争冒险.则电容C应加在何处其值约为多大试通过实验验证之。

项目三 组合逻辑电路 任务一 仿真与测试竞争冒险现象 【学习目标】 1.掌握组合逻辑电路的分析方法; 2.掌握组合逻辑电路的简单设计方法; 3.掌握组合逻辑电路的竞争冒险及消除方法。 【任务引入】 按照逻辑功能不同,数字电路常分两大类:一类组合逻辑电路(简称组合电路);另一类时序逻辑电路(简称时序电路)。如果一个逻辑电路在任何时刻的输出状态只取决于该时刻的输入状态,与电路原来状态无关,这样的电路称为组合逻辑电路。本节课内容我们学习组合逻辑电路的分析与设计方法,了解并掌握组合逻辑电路中的竞争冒险现象及其消除方法。 【基本理论】 一、组合逻辑电路概述 1.组合逻辑电路在电路结构上的特点: (1)构成电路基本元件是门电路,不含记忆单元(存储元件); (2)只有从输入到输出通路,没有从输出反馈到输入回路。 2.组合电路逻辑功能的描述 描述组合电路逻辑功能的方法有逻辑函数式、真值表、逻辑图、工作波形图、卡诺图等几种。 3-1-1 组合逻辑电路的框图 组合逻辑电路n 个输入端,用x1,x2,…,xn 表输入变量; 有m 个输出端,用y1,y2,…,ym 表示输出变量,输出变量与输入变量间逻辑关系: y1 =f1(x1,x2,…,xn) y2 =f2(x1,x2,…,xn) … ym =fm(x1,x2,…,xn) 二、组合逻辑电路的分析与设计 1.组合逻辑电路的分析 步骤如下: (1)用逐级递推法写出输出逻辑函数与输入逻辑变量之间的关系; (2)用公式法或者卡诺图法化简,写出最简逻辑表达式; (3)根据最简逻辑函数式列出功能真值表; (4)根据真值表写出逻辑功能说明,以便理解电路的作用。 例3-1-1:分析下图3-1-2三变量组合逻辑电路的功能。 图3-1-2三变量组合逻辑电路 解: 第一步:写出输出逻辑函数与输入逻辑变量之间的关系,如下: A B C F & & & & AB F =1BC F =2CA F =3

FPGA实现步进电机控制源代码.txt我爸说过的最让我感动的一句话:“孩子,好好学习吧,爸以前玩麻将都玩儿10块的,现在为了供你念书,改玩儿1块的了。”module fenpin(clk_48m,reset,out_door,addr,data,data_rd,rd,rw,Grating_a,Grating_b); input clk_48m,data_rd,reset,rd,rw,Grating_a,Grating_b; input [8:0]addr; output out_door; inout [7:0]data; reg flag; reg [23:0]step; reg [23:0]pul_counter; reg [5:0]clk_div1m; reg [23:0]den; reg [23:0]counter; reg [23:0]counter_now; reg [19:0]Grating_counter; reg [7:0]com; reg [7:0]databuff; reg out=0; reg data_link; reg direct; assign data=data_link?databuff:8'bzzzzzzzz; assign out_door=out&flag; always@(posedge clk_48m) if(clk_div1m<6'h2e) clk_div1m <=clk_div1m+1; else clk_div1m<=0; assign clk_1m=(clk_div1m==6'h2e); always @(posedge clk_1m) begin if(!reset) begin

项目三组合逻辑电路 任务一仿真与测试竞争冒险现象 【学习目标】 1.掌握组合逻辑电路的分析方法; 2.掌握组合逻辑电路的简单设计方法; 3.掌握组合逻辑电路的竞争冒险及消除方法。 【任务引入】 按照逻辑功能不同,数字电路常分两大类:一类组合逻辑电路(简称组合电路);另一类时序逻辑电路(简称时序电路)。如果一个逻辑电路在任何时刻的输出状态只取决于该时刻的输入状态,与电路原来状态无关,这样的电路称为组合逻辑电路。本节课内容我们学习组合逻辑电路的分析与设计方法,了解并掌握组合逻辑电路中的竞争冒险现象及其消除方法。 【基本理论】 一、组合逻辑电路概述 1.组合逻辑电路在电路结构上的特点: (1)构成电路基本元件是门电路,不含记忆单元(存储元件); (2)只有从输入到输出通路,没有从输出反馈到输入回路。 2.组合电路逻辑功能的描述 描述组合电路逻辑功能的方法有逻辑函数式、真值表、逻辑图、工作波形图、卡诺图等几种。 3-1-1 组合逻辑电路的框图 组合逻辑电路n个输入端,用x1,x2,…,xn表输入变量; 有m个输出端,用y1,y2,…,ym表示输出变量,输出变量与输入变量间逻辑关系: y1 =f1(x1,x2,…,xn) y2 =f2(x1,x2,…,xn) … ym =fm(x1,x2,…,xn) 二、组合逻辑电路的分析与设计 1.组合逻辑电路的分析 步骤如下: (1)用逐级递推法写出输出逻辑函数与输入逻辑变量之间的关系; (2)用公式法或者卡诺图法化简,写出最简逻辑表达式; (3)根据最简逻辑函数式列出功能真值表;

(4)根据真值表写出逻辑功能说明,以便理解电路的作用。 例3-1-1:分析下图3-1-2三变量组合逻辑电路的功能。 图3-1-2 三变量组合逻辑电路 解: 第一步:写出输出逻辑函数与输入逻辑变量之间的关系,如下: 第二步:化简写出最简逻辑表达式,得:F=AB+BC+CA 第三步:列出功能真值表 第四步:写出逻辑功能说明 当输入A 、B 、C 中有2个或3个为1时,输出Y 为1,否则输出Y 为0。所以这个电路实际上是一种3人表决用的组合电路:只要有2票或3票同意,表决就通过。 2.组合逻辑电路的设计 组合逻辑电路的设计是根据给定的实际逻辑功能,找出实现该功能的逻辑电路。步骤如下: (1)根据给出的条件,找出什么是逻辑变量,什么是逻辑函数,用字母设出,另外用0 和1各表示一种状态,找出逻辑函数和逻辑变量之间的关系; (2)根据逻辑函数和逻辑变量之间的关系列出真值表,并根据真值表写出逻辑表达式; (3)化简逻辑函数; (4)根据最简逻辑表达式画出逻辑电路; (5)验证所作的逻辑电路是否能满足设计的要求(特别是有约束条件时要验证约束条 件中的最小项对电路工作状态的影响)。 C AB F =1BC F =2CA F =3AC BC AB F F F F 321==

组合竞争冒险现象 定义:门电路两个输入信号同时向相反的逻辑电平跳变的现象称为竞争。我们 把由于竞争而在电路输出端可能产生尖峰脉冲的现象叫做竞争-冒险现象。 如图(a)的例子,当输入信号A从1跳变为0时,如果B从0跳变为1,而且B 首先上升,就会出现尖峰脉冲,如图(b)所示。 影响:信号在转换瞬间电路传输信号的速度对电路工作状态产生的组合冒险现 象的影响,有时还比较严重,甚至会发生逻辑错误,产生错误的动作。 当电路对输入信号跳变情况的传输速度相同时,输出波形保持低电平。当电路对输入信号跳变情况的传输速度不相同时,A输入信号还没有降到UIL(max)以下,B输入信号已经跳到UIL(max)以上,在这个瞬间两输入信号同为“1”,输出信号Y也是1,出现了如图(a)所示的正尖波信号,因该信号违反了稳态条件下与门电路的逻辑关系,所以,该信号为不受欢迎的干扰信号。同理也可讨论图(b)所示的或门电路在瞬态出现的负尖波信号。这些干扰信号统称为电压毛刺或噪声。 解决方法: 1.接入滤波电容 见图,为接入滤波电容消除毛刺的影响。毛刺很窄,其宽度可以和门的传输时

间相比拟,因此常在输出端并联滤波电容C。但C的引入会使输出波形边沿变斜,故参数要选择合适,一般由实验确定。 2.引入选通脉冲 毛刺仅发生在输入信号变化的瞬间,因此在这段时间内先将门封住,待电路进入稳态后,再加选通脉冲选取输出结果。该方法简单易行,但选通信号的作用时间和极性等一定要合适。例如,见图,在组合电路中的输出门的一个输入端,加入一个选通信号,即可有效地消除任何冒险现象的影响。 3.修改逻辑设计 如图(a)所示逻辑函数F=AB+A C ,在B=C=1时,F=A+A将产生偏“1”冒 险。增加多余项BC,则当B=C=1 时,F恒为1,所以消除了冒险。即卡诺图化简时多圈了一个卡诺圈,如图(b)所示。相切处增加了一个BC圈,消除了相切部分的影响。 在负载电路对竞争-冒险所产生的尖峰脉冲不敏感时,如负载为发光器件,竞争-冒险所产生的尖峰脉冲对电路的工作没有影响,可不必考虑这一问题。

FPGA实现嵌入式系统

北京理工大学雷达技术研究所

陈禾

主要内容

嵌入式系统概念与组成 基于FPGA的嵌入式系统设计 系统集成开发环境

嵌入式系统—定义

计算系统无处不在,由个人计算机、笔记本 电脑、工作站、大型机和服务器等构成计算 系统并不奇怪,但是,更广泛的是为完全不 同的目的构造的计算系统,它们嵌入在更大 的电子器件内,分别完成特定的功能,而不 被器件的使用者所识别。 对于这样的嵌入计算系统,简称为嵌入式系 统,可以定义为除了计算机或电脑之外的几 乎任何的计算系统。 这个不很精确的定义,可以使我们着手考察 嵌入系统设计者所面临的挑战。

嵌入式系统的一般特性

嵌入系统一般功能单一,重复执行一个特定的 程序,除非嵌入系统的程序用新的程序版本更 新,或者因尺寸限制它有几个程序倒进和倒出。 对嵌入系统的约束特别严格,诸如成本、尺寸、 性能和功耗等作为实现的特性,嵌入系统要求 成本是极低的价格,尺寸限制到最小、但达到 实时快速地处理数据,且消耗最少的功率,能 延长电池受命,也不需要冷却等。 其它如NRE成本、灵活性、样机的时间、上市 的时间、可维护性、准确性和安全性。 反应和实时性:许多嵌入系统必须对系统环境 的变化连续地反应,且要无滞后地实时计算确 定的结果。

嵌入式系统应用

嵌入式系统组成

硬件

嵌入式系统实现的基础

应用程序

实现特定任务和功能

操作系统(可选)

对应用软件进行管理 使硬件对应用软件透明

竞争冒险原理 (一)一般竞争冒险的产生及消除 1. 理论上分析组合逻辑电路时, 都没有考虑门电路的延迟时间对电路产生的影响。 实 际上,从信号输入到输出稳定都需要一定的时间。由于从输入到输出的过程中,不 同通路上门的级数不同, 或者门电路平均延迟时间的差异, 使信号从输入经不同通 路传输到输出级的时间不同。由于这个原因,可能会使逻辑电路产生错误输出。通 常把这 种现象称为竞争冒险。 2. 竞争冒险现象有两种情况,分别是 0型竞争冒险现象和 1型竞争冒险现象。 (1) 0型竞争冒险现象 如下图所示: 输出函数L A A ,在电路达到稳定时,即静态时,输出 L 总是1。然而在 A 变化时(动态时),从图12-2可见,在输出L 的某些瞬间会出现 0,即当A 经历 1变0的 变化时,L 出现窄脉冲,即电路存在静态 0型竞争冒险现象。或门 G2的 两个输入信号分别由 G1和A 端两个路径在不同时刻到达的现象,通常称为竞争, 由此产生输出干扰脉冲的现象称为冒险。 (2) 1型竞争冒险现象 如下图所示: 输出L AA ,在电路达到稳定时,即静态时,输出 L 总是0。然而在A 变化时 (动态时),从图12-4可见,在输出L 的某些瞬间会出现 1,即当A 经历0变1的 变化时,L 出现窄脉冲,即电路存在静态 1型竞争冒险现象。 3. 总结 当电路中存在由反相器产生的互补信号,且在互补信号的状态发生变化时可能出 现竞争冒险现象。 4. 消除竞争冒险的方法 (1) 发现并消掉互补变量 G1 L 」——11 — 图12-4波形图 图12-1 0型竞争冒险电路图 图12-2 波形图 12-3 1型竞争冒险电路图

/*FPGA实现的程序:(verilog) 贴子回复于:2008-4-27 15:26:01*/ module AD0809(clk500K, //脉宽(至少100ns) rst_n, EOC, //约100us后EOC变为高电平转换结束 START, //启动信号,上升沿有效(至少100ns) OE, //高电平打开三态缓冲器输出转换数据 ALE, //高电平有效,选择信道口 ADDA, //因为ADDB,ADDC都接地了,这里只有ADDA为变量 DATA, //转换数据 DATA_R); output START,OE,ALE,ADDA; input EOC,clk500K,rst_n; input[7:0] DATA; output[7:0] DATA_R; reg START,OE,ALE,ADDA; reg[7:0] DATA_R; reg[4:0] CS,NS; parameter IDLE=5'b00001,START_H=5'b00010,START_L=5'b00100,CHECK_END=5'b01000,GET_DATA=5'b100 00; always @(posedge clk500K) case(CS) IDLE: NS=START_H; START_H: NS=START_L; START_L: NS=CHECK_END; CHECK_END: if(EOC) NS=GET_DATA; else NS=CHECK_END; GET_DATA: NS=IDLE; default: NS=IDLE; endcase always @(posedge clk500K) if(!rst_n) CS<=IDLE;

实验四组合逻辑电路中的竞争冒险现象解析 一实验目的 1学会分析组合逻辑电路中有无竞争冒险现象。 2掌握采用修改逻辑电路设计的方法消除冒险现象。 二实验仪器 (1)双踪示波器 (2)双路直流稳压电源 (3)探测器 三实验原理 四实验步骤 1打开Multisim10电子线路仿真界面,在TTL集成电路器件库中,按电路原理图取出元器件;在仪器库中取出示波器以及方波信号源、探针等。按实验电路图4—1连接好。 2打开工作开关。展开示波器操作界面,观察到有关波形后,调整扫描时间、灵敏度等,使示波器A、B通道展示波形适当,并画出有关波形。 打开工作开关后可见探针闪亮。 打开示波器调整扫描时间和灵敏度等观察到波形如图A:

调整示波器的时间尺度,得出图B:

3根据波形,分析出现的问题及其原因。 电路原理图函数表达式F= C A AB +。图A 、B 的实验电路为B 、C 接高电平5V ,即B=C=1,此时F= A A +,输出为0,,然而由图A 可知电路存在“1”态冒险,即电路存在竞争冒险。 图B 为将图A 放大后的图像,可知输出端滞后于输入端。 4采用增加冗余项的方法消除上述电路中竞争冒险现象。画出修改后电路,并进行验证。 增加冗余项修改后的电路图(a ): 修改后输入输出波形图(b ):

原来表达式F= C A AB +增加冗余项后得F= BC C A AB ++=F= C A AB +*BC ,则电路图如上图(a ),其输入输出图像如图(b ),由图(b )可知,增加冗余项后,输出图像为一直线,即增加冗余项的方法已消除竞争冒险现象。 5用示波器观察电路修改后工作时的输出波形,将电路修改前后波形比较分析。 消除互补相乘项修改后的电路图(c ): 修改后输入输出波形图(d ):

FPGA实现嵌入式系统 摘要:在许多领域中广泛应用的嵌入式计算系统(简称为嵌入式系统),是在更大的电子器件中嵌入的重复完成特定功能的计算系统,它经常不被器件的使用者所识别,但在各种常用的电子器件中能够找到这些嵌入式系统。以可编程门阵列(FPGA)来实现可配置的嵌入式系统已越来越广泛,本文主要详细介绍了以FPGA实现嵌入式系统的前景。 关键词:嵌入式;FPGA;嵌入式操作系统。 FPGA Embedded Systems LI Bo (College of Electrical and Electronic Engineering,Wuhan Institute of Technology,Wuhan 430200,China) Abstract:In many embedded computing systems widely used in the field(referred to as embedded systems),is an electronic device in larger repeat embedded computing system to accomplish a specific function,it is often not recognized by the user of the device,but in a variety of conventional electronic devices can be found in these embedded systems.Programmable gate array(FPGA)to implement a configurable embedded systems has become increasingly widespread,this paper introduces the prospect to FPGA implementation of embedded systems. Key words:Embedded;FPGA;Embedded operating system. 1引言 随着计算与通信的融合以及广泛的多媒体处理需求,嵌入式系统得到了前所未有的蓬勃发展。嵌入式系统是以专用芯片为核心的专用系统,其特点是面向用户、面向应用、面向产品,软、硬件量体裁衣,满足行业应用个性化的要求,而这也是FPGA器件的特点。因此基于FPGA的可配置嵌入式系统开发技术以及相应的片上可编程系统(SOPC)解决方案,不仅可融入微处理器技术、数字信号处理技术、可编程系统级芯片设计和软硬件协同设计技术,还能提供了基于嵌入式智能平台的嵌入式系统的设计方法,还降低了设计难度、缩短了研发周期,必将成为未来的主流趋势之一。 从系统对上市时间的要求、可定制特性以及集成度等方面考虑,FPGA在嵌入式系统中获得广泛应用,已经从早期的军事、通信系统等应用扩展到低成本消费电子类等产品中。目前,FPGA在嵌入式系统中主要有3种使用方式:(1)状态机模式:无外设、无总线结构且无实时操作系统,达到最低的成本,常应用于VGA和LCD控制等,满足用户的最基本需求。 (2)单片机模式:包括一定的外设,可以利用实时操作系统和总线结构,以中等的成本,达到中等的性能,常用于控制和仪表。 (3)定制嵌入模式:高度集成扩充的外设,实时操作系统和总线结构,可达到高性能,常应用于网络和无线通信等。 2FPGA实现嵌入式系统的优势 嵌入式嵌入式系统经历了从单片计算机、工业控制计算机、集中分布式控制系统,进而发展到嵌入式智能平台的几个发展阶段。从独立单机使用发展到联