基于ARM和FPGA的高速数据采集卡的设计与实现(1).

- 格式:doc

- 大小:791.00 KB

- 文档页数:19

基于嵌入式的高速数据采集系统的设计作者:欧阳娣来源:《电子世界》2012年第19期【摘要】本文设计了一种基于嵌入式高精度高速数据采集模块,利用高速多路模拟开关选择8路模拟信号输入,实现程序控制采集任意1路或者轮流采集1~8路信号。

论文介绍了系统设计的总体方案及详细的软硬件设计。

【关键词】高精度;数据采集;USB总线1.引言数据采集在现代工业生产及科学研究中的重要地位日益突出,并且对实时高速数据采集的要求也不断提高。

在信号测量、图像处理、音频信号处理等一些高速、高精度的测量中,都需要进行高速数据采集。

基于计算机和嵌入式的分布式数据采集系统架构以其开发成本低、开放性、运算能力、通讯能力强、易于使用,逐渐成为设计应用的主流[1],而目前在微机系统中,外设与CPU的连接存在接口标准各自独立、互不兼容、无法共享的问题,并且安装、配置亦很麻烦,而通用串行总线(USB)的优良特性对此提供了极佳的解决方案[1]。

2.系统硬件设计如图1,系统的工作方式为,模拟信号输入部分实现采样多路信号的选择,同时对输入的模拟信号进行调理后送入A/D采样,而利用FPGA作为逻辑控制器实现系统内器件逻辑控制信号的产生,并且控制A/D的采样频率。

在FPGA内部配置双口RAM实现数据缓冲。

嵌入式处理器负责读取数据,并通过USB总线传输到计算机,嵌入式处理器还负责整个系统的协调工作[2]。

2.1 模拟输入和调理电路信号输入通道为多通道输入,系统可以采用ADG608高速多路模拟开关组成,由1条片选线和3条地址线实现从8路单端信号中选择其中一路,送入后级电路处理。

同时,在高速数据采集系统中,由于现场输入信号大小范围广,因而需要将信号放大或者衰减,满足A/D转换器模拟输入要求(0~5V),并尽可能的使A/D转换后有效位数大。

AD8551是一款低漂移,单电源的轨对轨输入/输出运算放大器,可由+2.7~+5V的单电源驱动。

它具有极低的失调、漂移和偏置电流[3]。

基于DSP+FPGA的实时信号采集系统设计与实现周新淳【摘要】为了提高对实时信号采集的准确性和无偏性,提出一种基于DSP+FPGA 的实时信号采集系统设计方案.系统采用4个换能器基阵并联组成信号采集阵列单元,对采集的原始信号通过模拟信号预处理机进行放大滤波处理,采用TMS32010DSP芯片作为信号处理器核心芯片实现实时信号采集和处理,包括信号频谱分析和目标信息模拟,由DSP控制D/A转换器进行数/模转换,通过FPGA实现数据存储,在PC机上实时显示采样数据和DSP处理结果;通过仿真实验进行性能测试,结果表明,该信号采集系统能有效实现实时信号采集和处理,抗干扰能力较强.%In order to improve the accuracy and bias of real-time signal acquisition,a real-time signal acquisition system based on DSP +-FPGA is proposed.The system adopts 4 transducer array to build parallel array signal acquisition unit,the original signal acquisition amplification filtering through analog signal pretreatment,using TMS32010DSP chip as the core of signal processor chip to realize real-time signal acquisition andprocessing,including the signal spectrum analysis and target information simulation,controlled by DSP D/A converter DAC,through the realization of FPGA data storage,real-time display on the PC and DSP sampling data processing results.The performance of the system is tested by simulation.The results show that the signal acquisition system can effectively realize the real-time signal acquisition and processing,the anti-interference ability is strong.【期刊名称】《计算机测量与控制》【年(卷),期】2017(025)008【总页数】4页(P210-213)【关键词】DSP;FPGA;信号采集;系统设计【作者】周新淳【作者单位】宝鸡文理学院物理与光电技术学院,陕西宝鸡721016【正文语种】中文【中图分类】TN911实时信号采集是实现信号处理和数据分析的第一步,通过对信号发生源的实时信号采集,在军事和民用方面都具有广泛的用途。

摘要随着机器视觉的广泛应用,以及工业4.0和“中国制造2025”的提出,在数字图像的采集、传输、处理等领域也提出了越来越高的要求。

传统的基于ISA接口、PCI接口、串行和并行等接口的图像采集卡已经不能满足人们对于高分辨率、实时性的图像采集的需求了。

一种基于FPGA和USB3.0高速接口,进行实时高速图像采集传输的研究越来越成为国内外在高速图像采集研究领域的一个新的热点。

针对高速传输和实时传输这两点要求,通过采用FPGA作为核心控制芯片与USB3.0高速接口协调工作的架构,实现高帧率、高分辨率、实时性的高速图像的采集和传输,并由上位机进行可视化操作和数据的保存。

整体系统采用先硬件后软件的设计方式进行设计,并对系统各模块进行了测试和仿真验证。

通过在FPGA 内部实现滤波和边缘检测等图像预处理操作,验证了FPGA独特的并行数据处理方式在信号及图像处理方面的巨大优势。

在系统硬件设计部分,采用OV5640传感器作为采集前端,选用Altera的Cyclone IV E系列FPGA作为系统控制芯片,由DDR2存储芯片进行数据缓存,采用Cypress公司的USB3.0集成型USB3.0芯片作为数据高速接口,完成了各模块的电路设计和采集卡PCB实物制作。

系统软件设计,主要分为FPGA逻辑程序部分、USB3.0固件程序部分和上位机应用软件部分。

通过在FPGA上搭建“软核”的方式,由Qsys系统完成OV5640的配置和初始化工作。

由GPIF II接口完成FPGA和FX3之间的数据通路。

通过编写状态机完成Slave FIFO的时序控制,在Eclipse中完成USB3.0固件程序的设计和开发。

上位机采用VS2013软件通过MFC方式设计,从而完成整体图像采集数据通路,并在上位机中显示和保存。

整体设计实现预期要求,各模块功能正常,USB3.0传输速度稳定在320MB/s,通过上位机保存至PC机硬盘的图像分辨率大小为1920*1080,与传感器寄存器设置一致,采集卡图像采集帧率为30fps,滤波及边缘检测预处理符合要求,采集系统具有实际应用价值和研究意义。

基于FPGA的图像处理系统设计与实现图像处理是计算机视觉领域中的重要技术之一,可以对图像进行增强、滤波、分割、识别等操作,广泛应用于医学图像处理、工业检测、安防监控等领域。

而FPGA(Field Programmable Gate Array)可编程门阵列,则是一种自由可编程的数字电路,具有并行处理能力和灵活性。

本文将介绍基于FPGA的图像处理系统的设计与实现。

一、系统设计流程1. 系统需求分析:首先需要明确图像处理系统的具体需求,例如实时性、处理的图像类型、处理的算法等。

根据需求,选择合适的FPGA芯片和外设。

2. 图像采集与预处理:使用图像传感器或摄像头采集图像数据,然后对图像进行预处理,如去噪、增强、颜色空间转换等,从而提高后续处理的准确性和效果。

3. 图像处理算法设计与优化:根据具体的图像处理需求,选择适合的图像处理算法,并对算法进行优化,以提高处理速度和效率。

常用的图像处理算法包括滤波、边缘检测、图像分割等。

4. FPGA硬件设计:基于选定的FPGA芯片,设计硬件电路,包括图像存储、图像处理模块、通信接口等。

通过使用硬件描述语言(如Verilog、VHDL)进行功能模块设计,并进行仿真和验证。

5. 系统集成与编程:将设计好的硬件电路与软件进行集成,包括FPGA程序编写、软件驱动开发、系统调试等。

确保系统的稳定运行和功能实现。

6. 系统测试与优化:对整个系统进行完整的测试和验证,包括功能性测试、性能测试、稳定性测试等。

根据测试结果,对系统进行优化,提高系统的性能和可靠性。

二、关键技术及挑战1. FPGA芯片选择:不同的FPGA芯片具有不同的资源和性能特点,需要根据系统需求选择合适的芯片。

一方面需要考虑芯片的处理能力和资源利用率,以满足图像处理算法的实时性和效果。

另一方面,还需要考虑芯片的功耗和成本,以便在实际应用中具有可行性。

2. 图像处理算法优化:在FPGA上实现图像处理算法需要考虑到算法的计算复杂度和存储开销。

基于FPGA的红外图像实时采集系统设计与实现摘要:随着红外图像在军事、航天、安防等领域的广泛应用,对红外图像的实时采集和处理需求越来越高。

本文基于FPGA设计并实现了一个红外图像实时采集系统,通过系统硬件框架、图像采集流程设计以及软硬件协同优化等方面的探究,实现了高效、稳定的红外图像实时采集和传输,为相关领域的探究和应用提供了重要支持。

一、引言红外图像技术是一种利用物体发射的红外辐射进行成像分析的技术,具有透过阴郁、烟雾等不利环境的能力。

它在军事、航天、安防等领域具有重要应用价值。

红外图像的实时采集和处理对于这些领域的探究和应用至关重要,然而传统的红外图像采集系统存在采集速度慢、波动大、传输距离限制等问题。

因此,设计并实现一种基于FPGA的红外图像实时采集系统具有重要意义。

二、系统框架设计基于FPGA的红外图像实时采集系统主要由硬件和软件两个部分组成。

硬件部分包括红外探测器、FPGA开发板、存储器、图像传输模块等;软件部分主要包括图像采集控制程序和数据处理程序。

硬件框架设计接受分层结构,分为红外图像采集层、控制层、存储层和传输层四个部分。

红外图像采集层包括红外探测器和模拟-数字转换电路,负责将红外辐射信号转换为数字信号。

控制层包括FPGA芯片和时钟控制电路,负责采集信号的控制和同步。

存储层包括高速存储器和图像缓存,负责暂存采集到的红外图像数据。

传输层包括数据传输电路和网络接口,负责将采集到的图像数据传输到外部设备。

三、图像采集流程设计图像采集流程是指将红外图像转换为数字信号并存储的过程。

在红外图像采集层,红外探测器将红外辐射信号转换为模拟信号,经过模拟-数字转换电路转换成数字信号。

在控制层,FPGA芯片控制采集信号的采样频率和位宽,通过时钟控制电路实现同步。

在存储层,高速存储器负责将采集到的图像数据暂存起来,图像缓存则将暂存的图像数据进行处理和压缩。

在传输层,数据传输电路将处理和压缩后的图像数据传输到外部设备。

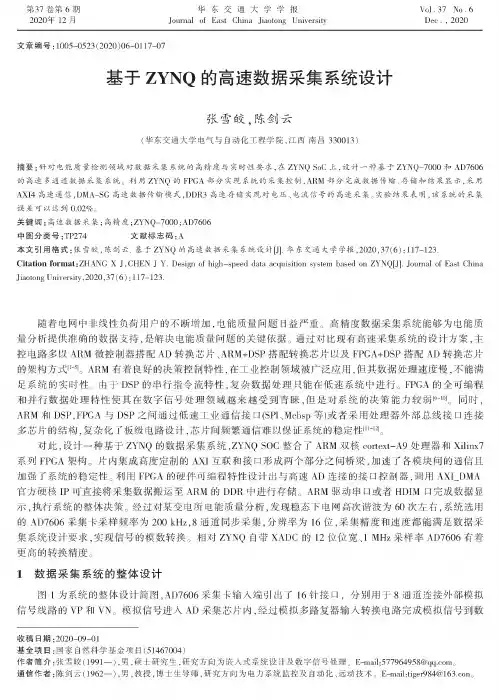

第37卷第6期2020年12月华东交通大学学报Journal of East China Jiaotong UniversityVol.37No.6Dec.,2020文章编号:1005-0523(2020)06-0117-07基于ZYNQ的高速数据采集系统设计张雪皎,陈剑云(华东交通大学电气与自动化工程学院,江西南昌330013)摘要:针对电能质量检测领域对数据采集系统的高精度与实时性要求,在ZYNQ SoC上,设计一种基于ZYNQ-7000和AD7606的高速多通道数据采集系统。

PQ ZYNQ的FPGA部分实现系统84集控制,ARM部分完成数据传输、存储和结果显示,4用AXI4高速通信,DMA-SG高速数据传输模式,DDR3高速存储实现对电压、电流信号的高速4集。

实验结果表明,该系统的4集误差可n达到0.02%。

关键词:高速数据4集;高精度;ZYNQ-7000;AD7606中图分类号:TP274文献标志码:A本文引用格式:张雪皎,陈剑云.基于ZYNQ的高速数据4集系统设计[J].华东交通大学学报,2020,37(6):117-123.Citation format:ZHANG X J,CHEN J Y.Design of high-speed data acquisition system based on ZYNQ[J].Journal of East China Jiaotong University,2020,37(6) :117-123.随着电网中非线性负荷用户的不断增加,电能质量问%数系统能够为电能质量分析提供准确的数据支持,是解决电能质量问题的关键依据%通系统的设计方案,控电ARM控AD、ARM+DSP及FPGA+DSP AD的方式冋。

ARM着的决控性,在工业控用,但其数据处理,能足系统的实时性。

由于DSP的性,复杂数处理能在低速系统中%FPGA的程数处理性使其在数字信号处理,但是系统的决策能力较弱[6-10]。

基于PC的高速数据采集卡设计一、引言数据采集(Data Acquisition)技术是信息科学的一个重要分支,主要研究数字化信息的采集、存储、处理等方面的内容。

随着电子技术的不断发展和人们对信息量需求的不断扩大,对高速、大容量的数据采集系统的需求也越来越高,以往的数据采集系统多采用单片机系统实现,由于单片机的速度和容量的限制,难于设计高速大容量的数据采集卡。

近年来,由于PC机的广泛应用,采用PC机实现数据采集系统已成必然趋势,因此,笔者研制了基于PC的高速数据采集卡。

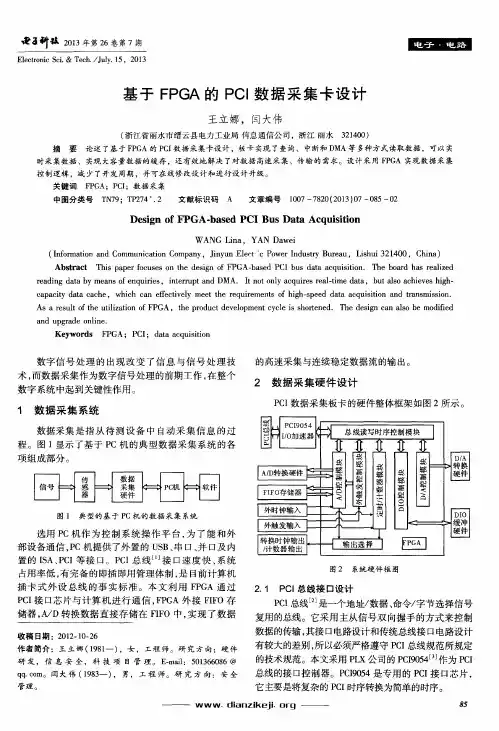

图1数据采集卡硬件结构图二、硬件结构及功能本数据采集卡是采集高频地质雷达信号,数据采集电路分为模拟电路和数字电路两部分,其实现框图如图1所示:其中接口及地址译码电路是为数据采集卡中各部分电路分配系统地址、提供启动信号和必要的控制信号;前置放大器是一個台阶增益为2的256倍程控增益放大器,是对来自雷达发射波采样保持后的信号进行阻抗匹配,并进行程控增益放大,使该信号的电压幅度尽可能接近A/D转换器的输入电压满度值,以便得到信噪比较高的数字化输出结果;A/D转换器是16位的,是将前置程控增益放大器输出的模拟信号数字化;延时电路1是用于启动天线发射子系统发射高频高压雷达脉冲信号,该延时是可编程的,它主要用来消除电路自身和传输线路带来的时滞影响,使得发射启动信号与接收启动信号之间的时间差控制在有效范围内。

延时电路2是在系统启动脉冲触发下,延迟一个可编程时间段后,产生一个触发脉冲,用于启动天线接收子系统的采样保持和数据采集卡的A/D转换。

微机总线采用ISA总线,ISA总线是在PC总线的基础上发展起来的,但比PC总线在性能上有了较大的提高,其布线要求没有PCI接口板的要求高,又能满足本数据采集系统的速度要求。

ISA为工业标准总线,该总线较PC总线在性能上有了较大的提高,如其寻址空间的范围、数据总线的宽度、中断处理能力等都有很大的提高。

ISA信号线分为5类:数据线、地址线、控制线、状态线、辅助线和电源线,只简介本数据采集卡用到的信号线。

高精度4通道同步数据采集系统设计与实现的开题报告一、选题背景数据采集系统是现代自动化领域的重要组成部分,广泛应用于工业控制、科学研究和实验室测试等领域。

随着科技和工业不断进步,数据采集系统也面临着不断提高精度和可靠性的需求。

特别是在一些高精度实验中,数据采集系统的精度直接影响到实验的准确性和可信度。

因此,设计一种高精度的数据采集系统,具有重要的意义。

在实际应用中,很多实验需要同时采集多个信号,并实现同步采集和处理。

例如高精度的声学信号处理、多通道的心电图数据采集、医学图像处理等领域都需要实现同步的数据采集。

传统的数据采集系统难以满足这些应用的要求,因此需要设计一种高精度4通道同步数据采集系统。

二、选题意义1. 增强数据采集系统的精度和可靠性设计高精度4通道同步数据采集系统可以提高数据采集的准确性和可靠性,满足一些高精度实验的要求。

2. 推动科学技术进步高精度4通道同步数据采集系统可以用于一些高精度实验中,具有推动科学技术进步的作用。

3. 增强数据采集系统在实际应用中的适用性现代化工、电力、交通、军事等领域的自动化系统需要高精度的数据采集系统来实现各项操作,设计高精度4通道同步数据采集系统可以推动数据采集系统在实际应用中的适用性。

三、研究内容和技术路线本项目旨在完成一种高精度4通道同步数据采集系统,主要研究内容包括:1. 确定数据采集系统的参数和技术指标。

2. 选择合适的硬件平台,进行数据采集卡的选型。

3. 利用FPGA进行数据采集卡的开发,实现多通道同步采集和处理。

4. 设计数据采集系统的软件界面,实现数据的实时显示和存储。

本项目将采用以下技术路线:1. 硬件采用高速ADC芯片与FPGA模块结合实现高速的多通道数据采集。

2. 软件采用基于Python的高效数据处理算法,同时结合图像处理技术实现数据显示等功能。

四、预期成果1. 完成一种高精度、高可靠性的4通道同步数据采集系统。

2. 实现数据采集系统的硬件设计和软件设计。

基于USB接口数据采集卡的设计与实现USB接口数据采集卡是一种常用于电子设备和计算机之间进行数据交互的设备。

它具有方便、快捷、稳定等特点,并且可以通过USB接口直接与计算机连接。

下面是一个USB接口数据采集卡的设计与实现的详细介绍:一、设计思路USB接口数据采集卡主要由AD转换器、微控制器、USB控制器以及外部电路等组成。

其主要工作原理是通过AD转换器将模拟信号转换为数字信号,然后使用微控制器对数字信号进行处理和存储,最后利用USB接口和计算机进行数据交互。

二、硬件设计2. 微控制器:选择适合USB通信的微控制器,如ATmega32U4、该微控制器具有丰富的外设功能和高速USB接口,能够满足数据采集的要求。

B控制器:选择成熟的USB控制器芯片,如CH340G。

它能够实现USB接口的逻辑转换,使得USB接口能够连接到计算机上。

4.外部电路:包括电源电路、时钟电路、滤波电路等。

其中,电源电路为采集卡提供工作电压和电流,时钟电路为微控制器提供时序信号。

三、软件设计1. USB驱动程序:设计和实现USB接口的驱动程序,使得计算机能够与采集卡进行数据交互。

可以使用如libusb等库函数简化开发过程。

2.数据处理程序:在微控制器中编写数据处理程序,包括数据采集、数据存储、数据传输等功能。

采集到的模拟信号通过AD转换器转换为数字数据,然后存储在微控制器的内部存储器中,最后通过USB接口传输给计算机。

3.上位机程序:设计和实现计算机上的上位机程序,用于接收和处理采集卡传输的数据。

通过该程序,用户可以实时监测和分析采集卡采集到的数据。

四、实现步骤1.进行硬件电路设计和布局,包括电源电路、时钟电路、AD转换器等。

2.利用开发板进行相关软件编程,并将测试程序烧录到微控制器中。

3.进行硬件的连接、测试和调试,确保硬件电路和软件功能正常。

4.设计并实现上位机程序,运行该程序进行数据采集和分析。

五、实现效果经过以上步骤,USB接口数据采集卡设计与实现完毕。

基于ARM11的视频采集与编码系统的设计摘要:基于嵌入式技术的无线视频监控以其灵活性、高集成性、便捷性等诸多优点必将取代传统的有线视频监控。

针对目前视频监控的实际需求,结合嵌入式技术、图像处理技术,设计并实现了一种可靠性高、成本低的嵌入式视频采集及编码系统。

它是视频监控的前端,是无线视频监控系统的一个子系统。

系统选用S3C6410微处理器作为核心板的控制器,采用USB接口的摄像头进行采集,利用S3C6410的硬件编解码模块进行H.264编码。

根据系统的功能要求,开发了zc301摄像头和MFC的设备驱动程序,并采用内存映射方式和双缓冲思想编写了基于V4L的视频采集程序。

探讨了H.264的编码特性和码流结构,利用MFC驱动中的API函数,开发了基于H.264算法的视频编码程序。

测试表明,设计的系统视频采集效率高、图像连续性好、运行稳定。

关键词:嵌入式系统;ARM11;S3C6410;视频采集;视频编码;H.264ABSTRACT:In the future, Wireless video monitoring system based on embedded technology, with many advantages such as flexibility, integration, convenience and so on, will replace existing wired video monitoring system inevitably. Aiming at actual demand of present video monitoring, this paper designs and realizes a reliable and cheap embedded video capturing and compression system, with the combination of embedded technology and image processing technology. This system is the front end of video monitoring and a subsystem of wireless video monitoring system. This system chooses S3C6410 as the kernel board's controller uses the camera with USB interface to capture pictures and encodes the video data using the codec of S3C6410. According to functional requirements of the system, device drivers of MFC and zc301 camera are developed, and video capturing application based on V4L using Memory Mapping and the idea of the double buffer are also developed. After a brief study on the feature and stream structure of H.264, video encoding application based on H.264 with the MFC driver’s API is completed. The test shows that this system has a high efficiency to capture video data, has good continuity for pictures and can run stably.KEY WORD:Embedded system; ARM11; S3C6410; Video capturing; Video encoding; H.264引言视频具有表达客观事物直观、生动、形象,信息丰富等优点,它在各行各业的应用日益受到人们的关注。

具有U2.0接口的高速数据采集卡设计摘要:讨论基于U接口的高速数据采集卡的设计与实现。

详细讲述数据采集卡的硬件部分设计,并简要介绍固件程序、驱动程序和应用软件的设计. 引言XX 数据采集在现代生产及科学研究中的重要地位日益突出,并且实时高速数据采集的要求也不断提高。

在信号测量、图像处理、音频信号处理等一些高速、高精度的测量中,都需要进行高速数据采集。

现在通用的高速数据采集卡一般多是PCI卡或**卡,这些采集卡存在很多缺点,比如安装麻烦,价格昂贵,尤其是受计算机插槽数量、地址、中断**的限制,可扩展性差。

通用串行总线U是用来连接设备与计算机之间的新式标准接口总线。

它是一种快速、双向、同步传输、廉价的并可以实现热拔插的串行接口。

U技术是为实现计算机和通信集成而提出的一种用于扩充PC体系结构的标准。

基于U接口的高速数据采集卡,充分利用了U总线的优点,它也必将被越来越多的用户所接受。

XX1U数据采集卡原理XX1.1 UU是英文Uversal Serial Bus的缩写,中文含义是“通用串行总线”.它支持在主机与**式**样即插即用的外设之间进行数据传输.它由主机预定传输数据的标准协议,在总线上的**种设备分享U总线带宽。

当总线上的外设和主机在运行时,允许自由添加、设置、使用以及一个或多个外设.U总线技术的提出就是想利用单一的总线技术,来满足多种应用领域的需要。

U1。

1协议支持两种传输速度,即低速1.5Mbps和高速12Mbps.为了在高速接口之争中占有一席之地,2000年发布了U2.0协议,它向下兼容U1。

1协议,数据的最高传输速率提高到480Mbps,这就使U对打印机和其它需要快速大容量数据的外设更具吸引力.XX为了满足实际数据采集U传输速度较高的需要,选择了Cypress的内置U 接口微控制器芯片EZU FX2系列,开发了具有U接口的高速数据采集卡。

XX 1。

2系统框图U系统是一个主从系统,而非对等(peer-to—peer)系统。

fpga求职简历FPGA(现场可编程门阵列)技术近年来在计算机科学领域崭露头角,其在硬件设计和数字信号处理方面的卓越性能和灵活性备受行业瞩目。

对于那些对于FPGA设计和开发有兴趣并希望在这一领域寻求职业机会的人来说,编写一份精致的求职简历是申请工作时至关重要的一环。

个人信息姓名:张三性别:男联系方式:手机号码、电子邮箱居住地:中国某城市教育背景硕士学历:某某大学计算机工程系学习方向:FPGA设计和应用研究课题:硬件加速的高性能数字信号处理器设计本科学历:某某大学计算机科学与技术专业技能和专长1. FPGA设计和开发:具有良好的FPGA基本理论知识和硬件描述语言(如VHDL、Verilog)编写能力。

熟悉FPGA设计流程,包括功能分析、电路设计、仿真验证和调试等环节。

2. 数字信号处理:掌握数字滤波器设计、傅里叶变换和离散时间信号处理等相关知识。

熟练应用MATLAB等工具进行信号仿真和处理。

3. 嵌入式系统开发:熟悉ARM架构和嵌入式系统设计,具备图像处理、通信接口和实时控制等方面的开发经验。

4. 编程技能:精通C/C++和Python编程语言,熟练使用EDA工具集和各种软硬件开发工具。

5. 团队合作和交流能力:具备良好的团队协作和沟通能力,能够与多学科专业人员合作,解决复杂问题。

项目经历1. 硬件加速的视觉目标检测系统设计- 负责设计并实现基于FPGA的视频图像处理模块,用于实时目标检测。

- 探索并优化卷积神经网络算法在FPGA上的部署,通过并行计算和定点化优化提高系统性能。

- 利用Xilinx Vivado工具集进行电路设计、验证和调试,最终实现了高效快速的目标检测系统。

2. 基于FPGA的高速数据采集卡设计- 参与团队开发,负责高速数据采集卡的硬件设计和验证。

- 使用Verilog语言设计和实现数据接收和处理模块,实现了高速数据采集和实时数据处理的功能。

- 调试和优化电路,确保数据采集的准确性和稳定性。

基于FPGAad数据采集存储处理报告(含Verilog源代码)基于FPGA AD数据采集存储处理项目报告(XILINX ALTEARA 都可用)组员:华、文、杰一、实验目的本次实验利用Basys2开发板完成一个开发小项目,即开发AD数据采集存储处理系统,旨在掌握FPGA开发基本方法以及锻炼解决开发过程中出现问题的能力。

二、关键词Basys2、FPGA、AD转换、RAM、串口通信、MATLAB处理三、方案设计要实现本次项目,首先确定器件,其次根据器件时序写出模块的使用程序,最后综合成一个工程,然后进行仿真,上板实验。

本次实验的器件:32M8位模数转换器、Basys2开发板、串口转RS232cp2102模块、基于三极管的电平转换电路。

选择好器件后,根据器件的时序完成模块的代码书写。

写好AD模块、串口通信模块后,现在就需要处理采样速率与串口通讯速率不匹配的问题了。

根据香农采样定理,采样频率得高于信号频率的两倍才能完成信号复现,我们这里使用25M的高速采样频率,而串口dps9600传送一个位104us明显比采样慢许多。

所以这里需要解决速率不匹配的问题。

我们想到可以利用FPGA的RAM先存储采样来的数据,然后再提取数据经过串口通信送至PC经由MATLAB处理。

本次小项目最为关键的是控制好采样与串口通信的时序问题。

关于时序的控制,留到模块介绍里面说明。

方案小结:本次实验基于片内RAM存储AD采样过来的数据,然后待采样完成后提取数据串口通信至PC,最后经由matlab处理。

四、模块介绍1.Verilog开发程序介绍如下给出基于QuartusII绘制出的Block Diagram图,涵盖了所有的模块以及模块之间的连线。

图4.1 综合模块图如下给出程序目录(txt格式):现在分别介绍各个模块的端口以及功能。

AD外设:电路图、实物图、接口这个外设提供最大32M采样速率,包括一个模拟信号输入和一个采样时钟输入以及八个数字信号输出。

清华大学 硕士毕业论文报告 课程名称: 嵌入式系统课程设计 专业班级: 应用电子技术09201班 学生姓名: 崔剑 指导教师: 袁 里 弛 完成时间: 2011年12月26日 报告成绩:

湖南文理学院电气与信息工程学院 目录 第一章 系统设计方案和主要器件选型 ................................................ 2 1.1 系统设计方案 ..................................................... 2 1.2 ADC芯片选型 ..................................................... 2 1.3 DA芯片选型 ...................................................... 2 1.4 FPGA芯片选型 .................................................... 3 1.5 主控CPU选型 ..................................................... 3 第二章 数据采集与触发电路设计 ........................................................... 4 2.1 前端采集电路设计 ................................................. 4 2.2 触发电路与触发控制 ............................................... 5 2.3 SDRAM控制器设计 ................................................. 6 第三章 各芯片间的数据传输与处理....................................................... 7 3.1 采集卡各芯片速度等级的划分和数据流向 ............................. 7 3.2 ARM与FPGA通信 .................................................. 7 3.3 数据的模拟输出 ................................................... 8 第四章 设计总结....................................................................................13 参考文献 ................................................................................................... 13 附录1 ARM外围电路 ......................................................................... 14 附录2 FPGA外围电路 ........................................................................ 15 附录3 ARM读取显示程序 ................................. 20 - 2 - 湖南文理学院电气与信息工程学院 第一章 系统设计方案和主要器件选型 1.1 系统设计方案 整个系统是由前端模拟通道、触发电路、FPGA数据采集预处理、数据模拟输出和ARM数据处理显示五部分组成。FPGA数据采集预处理分为A/D数据采集、触发控制、帧控制、SDRAM控制器和ARM数据交换五个部分,模拟数据经过A/D装换后在FPGA中缓冲,缓冲之后使用触发控制将采集到的数据分成512个数据点组成的数据帧,数据按照帧的顺序传输,经过SDRAM存储后,通过ARM与FPGA中的共享存储区传输给ARM。具体的数据采集系统的硬件结构图如下图2-1所示: 图2-1 数据采集卡硬件结构图 1.2 ADC芯片选型 A/D转换器是整个采集系统的核心,系统前端模拟电压调理电路、FPGA数据采集和后端的采集控制部分都与A/D直接相关,A/D芯片的选择不但关系到系统设计的性能,而且直接决定了整板设计的难度。 1.3 DA芯片选型 为了输出高性能的模拟信号,DAC采用采样率高达175M的高速DAC。AD970X系列DAC针对低功耗特性进行了优化,同时仍保持出色的动态性能,适合用于手持便携式仪器等需要有效地合成宽带信号的场合。AD9707 精度高达14位 ,采样率为175MSPS,内部集成边沿触发式输入锁存器,1V温度补偿带隙基准电压源和自校准功能,使AD9707能提供真14位INL与DNL性能。

- 3 - 湖南文理学院电气与信息工程学院 1.4 FPGA芯片选型 在现代采集系统中FPGA往往被用做通信系统的中枢,负责了大量的数据采集和前期处理和控制工作,FPGA作为系统的中间级主芯片承担着承前启后的重大任务。 1.4.1 FPGA的特点及选型 常见的FPGA一般由六部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。 1.4.2 FPGA的设计步骤 1.电路设计与输入 2.功能仿真 3.综合优化 4.综合后仿真 5.实现与布局布线 6.时序仿真和验证 7.板级仿真与验证 8.调试与加载配置 1.4.3 FPGA核心电路设计 FPGA各系列的最小系统板的单元组成基本相同,仅具体电路中存在着差异。一般可以把其组成分为七部分:FPGA主芯片、PROM存储芯片、电源电路、全局时钟发生电路、JTAG接口电路、下载模式选择电路和接口引出插针。以该最小系统板作为控制核心,外加所需的接口电路就可以实现各种设计。 1.5 主控CPU选型 主控CPU相当与人的心脏,整个系统运行的快慢与它有直接关系,常见的嵌入式处理器有单片机、ARM、DSP等,它们都有各自的特点,运用的场合各有不同,设计的难度也不一样。主控CPU的选择是一个综合的过程,在选择时它必须有以下特点: 1. CPU运算速度快,不能拖慢整个系统采集的效率。 2. CPU内嵌LCD控制器可以驱动TFT-LCD,利于降低系统设计难度。 3. 所选处理器比较常见,在其他设计中有广泛应用,便于代码移植,简化设计。 4. 基于此CPU的开发板购买方便,价格便宜,代码丰富。 - 4 - 湖南文理学院电气与信息工程学院 第二章 数据采集与触发电路设计 2.1 前端采集电路设计 2.1.1 AD前端调理电路 前端调理电路目的就是将被测信号调理到AD9480模拟输入的电压范围。被测信号经过前端阻抗变换网络之后,进入后级运算放大器,后级选择高阻抗低噪声运算放大器ADA4817,输入阻抗高达500GΩ。 下图2-1为AD8351单端转差分的典型电路: 图2-1 AD8351单端转差分的典型电路 下图2-2为AD9480功能模块图: 图2-2 AD9480功能模块图

- 5 - 湖南文理学院电气与信息工程学院 2.1.2 FPGA数据采集 设计中使用FPGA内部的RAM来缓冲AD输出的数据,EP3C25内部的RAM资源总共有608Kbits,使用这些内部的RAM作为数据缓冲单元,既可以节约成本,又可以提高硬件采集的性能。使用FPGA内部的RAM资源,设计中可以非常容易的构建前端数据缓冲所需要的双口RAM或者FIFO。 下图2-3为典型的双口RAM模块图。 2-3 典型的双口RAM模块图 2.2 触发电路与触发控制 为了保证采集数据的稳定,一般的数据采集系统中都会有触发电路,它能提供了一个稳定的触发相位点,使得重构的波形能够在上位机的显示屏上稳定显示,还保证我们能观测的感兴趣的波形。 2.2.1 触发分析 触发的目的是同步,触发的过程是比较。 图2-4 基本的触发结构图

- 6 - 湖南文理学院电气与信息工程学院 2.2.2 触发控制 典型的触发信号为比较器输出的脉冲信号,触发控制是根据触发脉冲的起始位置,采集起始位置之后的一帧数据,由于每一次触发信号产生时,采集的数据都 是在一个固定的值,因此将每次触发后的512个数据点组合为一帧,在显示上就会出现一个稳定的数据波形。整个控制和实现上述功能的过程就是触发控制。 2.4 SDRAM控制器设计 CMDACKBA[1:0]CS[1:0] CKERASCASWE

2.4.1 SDRAM控制器结构 图2-5 SDRAM控制器系统结构 1.控制接口模块 图2-6 接口模块的结构图

CMDACK - 7 - 湖南文理学院电气与信息工程学院 第三章 各芯片间的数据传输与处理 3.1 采集卡各芯片速度等级的划分和数据流向 按照整个系统各部分的速度,我们将系统简单的划分为三个速度等级,不管是程序设计还是PCB设计都要充分的考虑到各个速度等级的特点,才能设计出合理可靠的系统,具体划分情况如下图3-1所示: 图3-1 系统速度等级划分图 中速为了提高采集、存储和显示的效率,根据各个芯片的特点,运用了下面几种处理方式来提高效率: 1.在FPGA中构建一个多缓冲单元的乒乓机制采集模块,提高FPGA采集的效率,并降低了中间级传输的速度,利于中间级的数据处理。 2.在中间级FPGA与后端ARM之间的通信中,使用DMA模式,大大提高了数据传输的速率,并解放了ARM,使其可以从容的进行数据处理和显示工作。 3.在ARM接收数据后对采集的数据帧进行控制,保证数据传输的可靠性和正确性。 3.2 ARM与FPGA通信 在数据采集卡中ARM主要负责数据显示和数据分析,处理的速度处于MS级;而FPGA在系统中处于数据的高速采集和高速处理,处理的速度是ns级。两个处理器的之间的数据传输属于典型的异步数据通信,它们之间通信的速度之间决定了系统处理数据的效率。FPGA与ARM之间属于大量数据交换,以异步并行读取的方式为例介绍ARM与FPGA的通信,实际设计中使用DMA方式来实现ARM与FPGA之间的大数据量通信。 3.2.1 ARM存储系统分析 S3C2410A存储控制器提供访问外部存储器所需要的存储器控制信号。S3C2410A支

- 8 - 湖南文理学院电气与信息工程学院 持大、小端模式,将存储空间分为8个组(Bank),每组大小是128M,共计1GB,如图3-2所示。