实验11 通信模块设计

11.1 实验目的

1.掌握用CPLD实现通信系统中的常用基带信号码型变换电路的方法。

2. 掌握用CPLD实现通信系统中的位同步、帧同步电路的方法。

3.掌握用CPLD实现信道编译码电路的方法。

11.2 实验原理

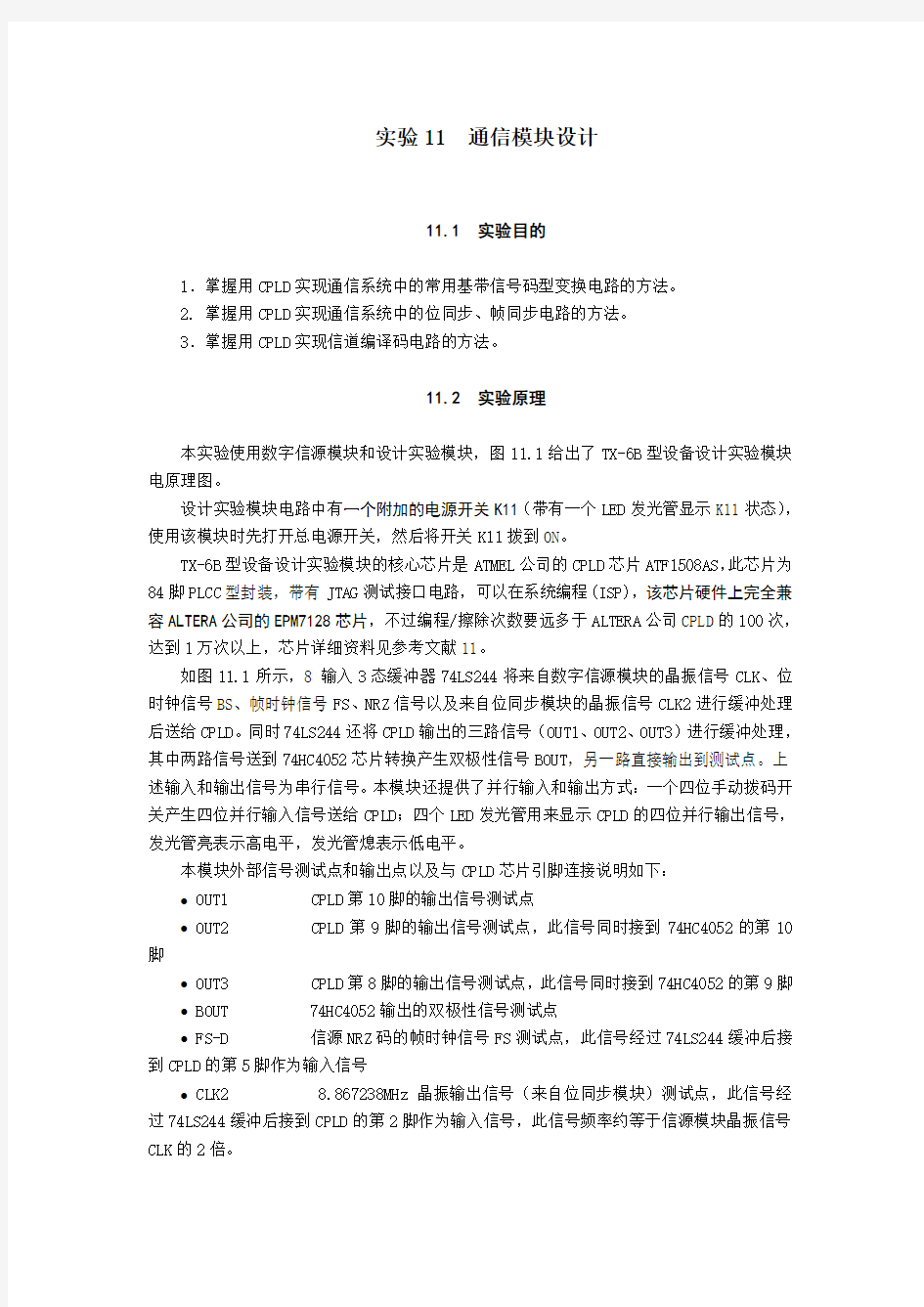

本实验使用数字信源模块和设计实验模块,图11.1给出了TX-6B型设备设计实验模块电原理图。

设计实验模块电路中有一个附加的电源开关K11(带有一个LED发光管显示K11状态),使用该模块时先打开总电源开关,然后将开关K11拨到ON。

TX-6B型设备设计实验模块的核心芯片是ATMEL公司的CPLD芯片ATF1508AS,此芯片为84脚PLCC型封装,带有JTAG测试接口电路,可以在系统编程(ISP),该芯片硬件上完全兼容ALTERA公司的EPM7128芯片,不过编程/擦除次数要远多于ALTERA公司CPLD的100次,达到1万次以上,芯片详细资料见参考文献11。

如图11.1所示,8 输入3态缓冲器74LS244将来自数字信源模块的晶振信号CLK、位时钟信号BS、帧时钟信号FS、NRZ信号以及来自位同步模块的晶振信号CLK2进行缓冲处理后送给CPLD。同时74LS244还将CPLD输出的三路信号(OUT1、OUT2、OUT3)进行缓冲处理,其中两路信号送到74HC4052芯片转换产生双极性信号BOUT,另一路直接输出到测试点。上述输入和输出信号为串行信号。本模块还提供了并行输入和输出方式:一个四位手动拨码开关产生四位并行输入信号送给CPLD;四个LED发光管用来显示CPLD的四位并行输出信号,发光管亮表示高电平,发光管熄表示低电平。

本模块外部信号测试点和输出点以及与CPLD芯片引脚连接说明如下:

? OUT1 CPLD第10脚的输出信号测试点

? OUT2 CPLD第9脚的输出信号测试点,此信号同时接到74HC4052的第10脚

? OUT3 CPLD第8脚的输出信号测试点,此信号同时接到74HC4052的第9脚? BOUT 74HC4052输出的双极性信号测试点

? FS-D 信源NRZ码的帧时钟信号FS测试点,此信号经过74LS244缓冲后接到CPLD的第5脚作为输入信号

? CLK2 8.867238MHz晶振输出信号(来自位同步模块)测试点,此信号经过74LS244缓冲后接到CPLD的第2脚作为输入信号,此信号频率约等于信源模块晶振信号CLK的2倍。

1A121A241A361A482A1112A2132A3152A4171Y1181Y2161Y3141Y4122Y192Y272Y352Y4

3

1G 12G

19

U95

74LS244

X0

12

X1

14

X215X311Y3

4

A 10B

9

VEE

7X

13

INH

6U96

74HC4052

-5V

VCC

1234

5

678K10

OP4

OP3OP2OP1VCC

K11

+5V IN

1K x 5

VCC

1K x 4

I N 1

I N 2I N 3I N 4I N 1I N 2I N 3I N 4O P 1

O P 2O P 3O P 4VCC

BS-OUT NRZ-OUT

CLK2FS CLK

100 x 3

BO UT

O UT 3

O UT 2O UT 1FS-D

CLK2来自信源来自位同步来自信源来自信源来自信源

I /O E 2/G C L K 22I N /G C L K 183

N /O E 184I N P U T /G L C R 1T C

K 62I O 17I O 28I O 45I O 57I O 58I O 60I O 61I O 63I O 64I O 65I O 67I O 68I O 69I O 70I O 73I O 74I O 75I O 76I O 77I O 79I O

80I O

81I O 33I O 34I O 35I O 36I O 37I O 39I O 40I O 41I O 44I O 6

I O 46I O 48I O 49I O 50

I O 51

I O 52I O 54I O 55I O 56I O 8I O 9I O 10

I O 11I O 12I O 15I O 16I O

4I O 18I O 20I O 21I O 22I O 24

I O 25I O 27

I O 5I O 29

I O

3

0I O

31T D I

14

T D O

71

T M S 23U94

EPM7128SLC(ATF1508AS)

12345678910

JTAG2

HEADER 5X2

图11.1 TX-6B 型设备设计实验模块电原理图

设计实验模块中CPLD 芯片ATF1508AS 的引脚资源分配定义如下:

? 第2脚 通用I/O 口兼作GCLK2。实验模块中定义为输入口,已接位同步模块

的晶振信号CLK2

? 第5脚 通用I/O 口。实验模块中定义为输入口,已接信源NRZ 码的帧时钟信

号FS

? 第8脚 通用I/O 口,实验模块中定义为输出口,对应本模块外部输出点O UT3 ? 第9脚 通用I/O 口,实验模块中定义为输出口,对应本模块外部输出点O UT2 ? 第10脚 通用I/O 口,实验模块中定义为输出口,对应本模块外部输出点O UT1 ? 第11脚 通用I/O 口,实验模块中定义为输入口,已接信源模块的输出信号

NRZ-O UT

?第15脚通用I/O口,实验模块中定义为输出口,已接LED发光管O P1,高电平驱动O P1亮

?第16脚通用I/O口,实验模块中定义为输出口,已接LED发光管O P2,高电平驱动O P2亮

?第17脚通用I/O口,实验模块中定义为输出口,已接LED发光管O P3,高电平驱动O P3亮

?第18脚通用I/O口,实验模块中定义为输出口,已接LED发光管O P4,高电平驱动O P4亮

?第20脚通用I/O口,实验模块中定义为输入口,已接拨码开关IN4(开关K10的第4位),IN4置O N时该引脚为+5V高电平,IN4置O FF时该引脚

为0V低电平

?第21脚通用I/O口,实验模块中定义为输入口,已接拨码开关IN3(开关K10的第3位),IN3置O N时该引脚为+5V高电平,IN3置O FF时该引脚

为0V低电平

?第22脚通用I/O口,实验模块中定义为输入口,已接拨码开关IN2(开关K10的第2位),IN2置O N时该引脚为+5V高电平,IN2置O FF时该引脚

为0V低电平

?第28脚通用I/O口,实验模块中定义为输入口,已接拨码开关IN1(开关K10的第1位),IN1置O N时(向上拨)该引脚为+5V高电平,IN1置O FF

时该引脚为0V低电平

?第14脚 JTAG口TDIN,实验模块中已接JTAG2口插座对应引脚

?第23脚 JTAG口TMS,实验模块中已接JTAG2口插座对应引脚

?第62脚 JTAG口TCK,实验模块中已接JTAG2口插座对应引脚

?第71脚 JTAG口TD O UT,实验模块中已接JTAG2口插座对应引脚

?第81脚通用I/O口兼作GCLK3,实验模块中定义为输入口,已接信源模块NRZ 码的位时钟信号BS-O UT

?第83脚通用I/O口兼作GCLK1。实验模块中定义为输入口,已接信源模块晶振信号CLK

除外部输出点,其他特别规定的输入/输出口已在电路板上作好布线连接,编程时直接利用,不要挪用或改用。剩下没有分配的通用I/O口没有引出,所以不方便使用。

为了保护CPLD芯片,在CPLD的一些输出/输入端使用了74LS244芯片作缓冲驱动。74LS244的8个输入/输出脚对应关系如表11.1所示。

表11.1 74LS244输入/输出脚对应关系

输入脚 2 4 6 8 11 13 15 17

输出脚18 16 14 12 9 7 5 3 实验系统提供了配套JTAG口编程下载线,将计算机并口(打印机接口)和实验板上的

JTAG口连接,即可通过计算机软件操作进行在系统编程。

CPLD的开发设计一般在相应开发软件中完成。由于ATMEL公司的ATF1508AS芯片硬件上完全兼容ALTERA公司的EPM7128芯片,故可以使用ALTERA公司著名的集成综合开发工具MAX+plusII来完成关键的CPLD软件设计过程。

在CPLD开发软件中编写硬件描述语言源程序,再通过语法检查、器件选择(选择MAX7000系列的EMP7128)、管脚分配、逻辑综合等编译过程后,生成编程文件(ALTERA系列是以.POF 为文件名后缀)。接下来,将得到的ALTERA公司的编程文件用转换软件(pof2jed.exe)转换成ATMEL公司的编程文件(.jed文件),然后用ATMEL公司的下载软件(Atmelisp.exe)通过下载线和JTAG口将编程文件下载到CPLD芯片中。此处下载线也可以直接使用ALTERA 公司的Byteblaster下载线,当然下载软件中要作相应设定。

CPLD的开发设计详细过程不是本课程内容,此处不再赘述,读者可查阅相关参考文献,学习相应软件操作及其CPLD开发过程。

11.3 实验内容及实验步骤

1. 熟悉设计实验模块和CPLD的开发软件MAX+plusII。

2. 利用提供的输入信号和资源,用硬件描述语言来设计实现通信系统中某些模块功能,如:常用的几种基带信号码型变换、循环码的编译码、卷积码的编译码、位同步提取、帧同步提取等。

3.通过管脚设定、逻辑综合、功能仿真、设计实现、时序仿真等设计步骤,生成编程文件,完成软件设计步骤。

4. 将得到的编程软件转换为ATMEL公司的编程文件,通过下载线将其下载到设计实验模块,通过观察硬件输出信号验证结果。

376.3远程通信模块接口协议

ICS29.020 Q/GDW 国家电网公司企业标准 Q/GDW 1376.3—2012 电力用户用电信息采集系统通信协议 第3部分:采集终端远程通信模块接口协 议 power user electric energy data acquisition system communication protocol Part 3: acquire terminal telecommunication modules interface XXXX-XX-XX发布XXXX-XX-XX实施

前言 Q/GDW 1376—2012《电力用户用电信息采集系统通信协议》是根据国家电网公司2012年度企业标准制修订计划任务(国家电网科[2012]66号)的安排,对Q/GDW 376—2009《电力用户用电信息采集系统通信协议》的修订。 与原标准相比,本次修订做了如下重大调整和修订: ——增加了磁场异常事件记录; ——增加了终端对时事件记录; ——增加了集中器与本地通信模块交互流程; ——增加了采集终端远程通信模块接口协议(Q/GDW 1376的第3部分)。 Q/GDW 1376—2012《电力用户用电信息采集系统通信协议》分为下列3个部分: ——Q/GDW 1376.1《电力用户用电信息采集系统通信协议第1部分:主站与采集终端通信协议》; ——Q/GDW 1376.2《电力用户用电信息采集系统通

信协议第2部分:集中器本地通信模块接口协议》; ——Q/GDW 1376.3《电力用户用电信息采集系统通信协议第3部分:采集终端远程通信模块接口协议》。 Q/GDW 1376—2012实施后代替Q/GDW 376—2009。 本部分是Q/GDW 1376—2012《电力用户用电信息采集系统通信协议》的第3部分。 本部分是《电力用户用电信息采集系统》系列标准之一,规定了采集终端远程通信模块的接口、功能要求,以及AT命令集。 本部分由国家电网公司营销部提出并负责解释; 本部分由国家电网公司科技部归口。 本部分起草单位:中国电力科学研究院、浙江省电力公司 本部分主要起草人:刘宣、郑安刚、王伟峰、杜蜀薇、杜新纲、葛得辉、孟宇、巫钟兴、唐悦Q/GDW 376于2009年12月7日首次发布,本次为第一次修订。

前言 随着Internet的普及和以太网的迅速发展, 基于以太网的设备控制越来越多。加之电子技术的飞快发展,各种工业过程数字仪表应运而生。以太网是目前应用非常广泛的网络通信技术,它具有丰富而完善的通讯协议,支持现场设备的热拔插, 提高系统运行的稳定性和抗干扰性, 安装、维护成本低。 用以太网实现嵌入式系统的网络连接有多种方案,传统的多器件以太网连接解决方案,是通过MCU扩展以太网控制器来实现的,必要时还需要扩展外部RAM和ROM,虽然这个计划中的应用还不是很困难,但有大量的外部元件,系统开销较大, 它以ATmega16单片机和带芯片ENC28J60和集成网络变压器的接口模块HR91105为核心。分析了ATmega16的功能和特点,介绍ENC28J60芯片的结构特性和主要性能,并给出了接口的硬件设计和软件设计方案。在此基础上。这个方案不仅成本低,而且能实现500Kbps以上的传输速率,满足了嵌入式系统的Internet 控制要求。但设计师在为远程控制或监控系统提供以太网接入时,可选的以太网控制器均是专为个人计算系统设计的,那些超过80引脚封装的以太网控制器大量运用于上述情况,这些器件不仅结构复杂, 面积庞大, 且系统开销较大。无法很好地满足嵌入式网络应用系统。在测控领域,以单片机为核心 符合IEEE802.3协议的ENC28J60只有28引脚,却具有早期器件相应的功能,满足系统设计的要求,ENC28J60以太网控制器采用业界标准的RJ45串行接口,只需4条连线即可与主控单片机连接,使得嵌入式应用系统的以太网接口变得极其简便。不过到目前为止,基ENC28J60以太网应用却不是很多。在测控领域,以单片机为核心的各种智能监控、测试系统因其高性价比等原因正得到越来越广泛的应用。本项研究的目的是要利用ENC28J60在ATmega16+ENC28J60平台上实现以太网通信。对于没有开放总线的单片机,虽然有可能是其他以太网控制器连接模拟并行总线,但不管从效率还是性能上来看,都不如用RJ45接口或采用一个通用I/O口模拟RJ45接口连接ENC28J60的方案。随着国民经济的快速发展,互联网络硬件、软件也迅猛发展,网络用户的发展已成倍增长。利用廉价的AVR单片机来控制ENC28J60实现以太网通讯这一做法,在使用计算机网络进行互联的各种家用电器及设备,仪器仪表,工业生产数据采集与控制设备逐步地走向网络化,以共享网络中巨大的信息资源的大背景下,仍然具有十分重要的意义。它适用于现有的网络传输系统,有着广泛的应用前景,特别是数据采集、数据传输领域。

XFP模块电路设计 一、应用要求 1、多速率应用:TELECOM(SONET OC-192 and G.709 “OTU-2”) DATACOM(10 Gb/s Ethernet and 10 Gb/s Fibre Channel) 2、XFI(9.95Gb/s~11.7Gb/s)高速信号可以在改良的FR4电路板上传输 300mm或普通的FR4电路板上传输200mm。 3、热插拔智能化,能够提供模块的实时工作状态的监视值 二、指标要求 3、封装结构:按照XFP-MSA的要求 三、方案选择 1、发射器件的选择:采用公司成熟的TO封装工艺开发的发射器件。 2、接收组件的选择:采用公司成熟的TO封装工艺开发的接收组件。

四、电路设计 1、原理框图 LOS Data In TxDis SCL SDA TxFault

2、原理图设计 3、PCB设计 (1)传输线设计: 在PCB设计中采用微带线来进行信号传输,保证高深信号在PCB上传输不发生波形畸变,我们通过AppCAD模拟可得到微带线的宽度和各微带线之间的间距。在10Gb/s的工作速率下,信号波长已经可以与器件尺寸相比拟,基于电路性能、器件选择和电磁兼容等因素的考虑,必须以网络散射分析(S参数)、信号完整性分析、电磁仿真分析、电路仿真分析等手段,来综合考量实际电路系统的工作性能。对电路板、元器件进行结构性电磁仿真并精确提取相应的SPICE电路模型参数,作为电路设计的依据,以此有效减小电感器件在高频设计应用中的误差影响。而且现在国外的产品技术参数大多包含有S参数,通常可用于精确的高频应用分析。信号传输微带线的等效分析见下图。

浅析通信射频模块控制电路设计引言 通信系统的快速发展使射频模块和基带之间的数据速度得到了极大的提高。通信射频模块中的基带信号包含了自动增益、自动功率和自动频率等调节信息,这些调节信息都是通信系统的基础。对误码率进行解决的话,传统方法有FEC(前向纠错码)或者ARQ(自动重传请求算法),FEC算法带宽较大,ARQ算法带宽较小。但是两种算法在实际的计算中会因为数据重传请求以及相应过程为其带来较大的延迟,除了这两种算法,还有CRC校验算法也在通信射频模块控制电路中有较为广泛的应用。 1无线终端系统设计 无线终端系统示意图如图1所示。CBM:通信基带模块;CRMCC:射频模块控制电路;CRM:通信射频模块。通信基带模块主要负责信源编码和解码;射频模块控制电路主要接收来自通信射频模块的基带控制信号,并将其生成射频模块控制信号(RFCS),通过射频模块控制信号对通信射频模块进行控制,并向通信射频模块返回信号接收回馈信息(SRCFM)。射频模块会在射频模块信号控制下,接收来自基带传输的通信数据。 2常见的纠错算法 一个标准的时序信号会显示正常的信号示意,DATA信号是最高有效位,可以对信号进行优先传输,原始的DATA信号所传输的信号是二进制,相对于其他质量的DATA信号,CLK信号的最高位并没有

被采样,DATA信号可以在其他的时间保持高电平,并将最后的采样结果表示为8位的二进制。如果该数据用于控制信号功率,对于功率信号而言,增加的倍数较多,对通信系统将会造成十分严重的影响。移动通信会随着终端和基站之间的距离而随时发生变换,AGC和AFC 参数需要进行修正设置,对于出现的传输错误以及数据跳变等操作,通信射频模块控制电路需要对其作出正确的反应。同时为了更好地解决基带和射频模块之间存在的误码问题,可以采用FEC(前向纠错码)或者ARQ(自动重传请求算法)。ARQ(自动重传请求算法)有几种典型的技术方式,比如停止等待、回退N步以及选择重传等方式,其中回退N步方式与选择重选方式在正常的工作环境下具有较好的性能,但是应用到射频控制模块中,存在无法实现等待回传数据的问题,限制了自动重传请求算法的实际应用。FEC(前向纠错码)算法在实际的使用中,误码率为1/2或3/4,原始码率能够达到200%,但是占用的额外带宽较大,对于信道有限的通信射频控制模块而言无法得到更好的实现效果。 3自适应滤波器 自适应滤波器与普通的滤波器不同,自适应滤波器会根据外部的环境变化而发生变化,通过改变自身的冲激响应来获取最佳的滤波效果;同时,自适应滤波器还包含了普通滤波器的硬件电路。滤波器的自适应算法可以根据上一个阶段的滤波参数适应来自外界的信号变化,从而达到最佳的性能要求,自适应滤波器是线性变化的过程。自适应滤波器包含了数字滤波器和自适应滤波算法两部分,数字滤波器

基于MRF24J40的IEEE802.15.4无线收发电 路设计 时间:2010-11-30 19:05:33 来源:作者:黄智伟何娜 IEEE802.15.4无线收发器MRF24J40芯片内部包含有SPI接口、控制寄存器、MAC 模块、PHY驱动器四个主要的功能模块,支持IEEE802.15.4,MiWiTM,ZigBee等协议,工作在2.405~2.48 GHz ISM频段,接收灵敏度为-91 dBm,最大输入电平为+5 dBm,输出功率为+0 dBm,功率控制范围为38.75 dB,集成有20 MHz和32.768 kHz主控振荡器,MAC/基带部分采用硬件CSMA-CA结构,自动ACK6和FCS检测,CTR、CCM和CBC-MAC 模式采用硬件加密(AES-128),电源电压范围为2.4~3.6 V,接收模式电流消耗为18 mA,发射模式电流消耗为22 mA,睡眠模式电流消耗为2μA。 MRF24J40采用6 mm×6 mm QFN-40封装,引脚端封装形式如图1所示。图中:引脚端RFP和RFN分别为芯片的RF差分输入/输出正端和负端,两者都是模拟输入/输出端口,与系统天线相连接;VDD为电源电压输入引脚端,每个电源电压输入引脚端都必须连接一个电源去耦电容;GND为接地引脚端,必须低阻抗的连接到电路的接地板;GPIOO~GPIO5是通用数字I/O口,其中GPIO0也被用来作为外部功率放大器使能控制,GPIO1和GPIO2也被用来作为外部TX/RX开关控制;RESET为复位引脚端,低电平有效;WAKE为外部唤醒触发输入端;INT为到微控制器的中断引脚端;SDO,SDI,SCK和CS是MRF24J40的SPI接口输入输出引脚端,其中SDO是MRF24J40的串行数据输出,SDI是MRF24J40的串行接口数据输入,SCK是串行接口的时钟,CS是串行接口使能控制引脚端;LPOSC1和LPOSC2为32 kHz晶振输入正端和负端;OSC1和OSC2为20 MHz晶振输入正端和负端;CLKOUT为20/10/5/2.5 MHz时钟输出端;LCAP引脚端用来连接一个180 pF的PLL环路滤波器电容;XIP和RXQP为接收I通道和Q通道输出正端。 2 MRF24J40构成的IEEE802.15.4无线收发电路 MRF24J40构成的IEEE802.15.4无线收发电路如图2所示,各电源电压引脚端根据需要分

cc1100/RF1100SE、NRF905、NRF903、nRF24L01无线收发模块开发指南简介 cc1100/RF1100SE微功率无线数传模块 基本特点: (1) 工作电压:~,推荐接近,但是不超过(推荐) (2) 315、433、868、915MHz的ISM 和SRD频段 (3) 最高工作速率500Kbps,支持2-FSK、GFSK和MSK调制方式 (4) 可软件修改波特率参数,更好地满足客户在不同条件下的使用要求高波特率:更快的数据传输速率 低波特率:更强的抗干扰性和穿透能力,更远的传输距离 (5) 高灵敏度(下-110dBm,1%数据包误码率) (6) 内置硬件CRC 检错和点对多点通信地址控制 (7) 较低的电流消耗(RX中,,,433MHz) (8) 可编程控制的输出功率,对所有的支持频率可达+10dBm (9) 无线唤醒功能,支持低功率电磁波激活功能,无线唤醒低功耗睡眠状态的设备 (10) 支持传输前自动清理信道访问(CCA),即载波侦听系统 (11) 快速频率变动合成器带来的合适的频率跳跃系统 (12) 模块可软件设地址,软件编程非常方便 (13) 标准DIP间距接口,便于嵌入式应用 (14) 单独的64字节RX和TX数据FIFO (15) 传输距离:开阔地传输300~500米(视具体环境和通信波特率设定情况等而定) (16) 模块尺寸:29mm *12mm( 上述尺寸不含天线,标配4.5CM长柱状天线) cc1100/RF1100SE微功率无线数传模块应用领域:极低功率UHF无线收发器,315/433/868/915MHz的ISM/SRD波段系统, AMR-自动仪表读数,电子消费产品,远程遥控控制,低功率遥感勘测,住宅和建筑自动控制,无线警报和安全系统, 工业监测和控制,无线传感器网络,无线唤醒功能,低功耗手持终端产品等 详细的cc1100/RF1100SE模块开发文档可到下载 NRF905无线收发模块 基本特点: (1) 433Mhz 开放 ISM 频段免许可证使用 (2) 接收发送功能合一,收发完成中断标志 (3) 170个频道,可满足多点通讯和跳频通讯需求,实现组网通讯,TDMA-CDMA-FDMA (4) 内置硬件8/16位CRC校验,开发更简单,数据传输可靠稳定 (5) 工作电压,低功耗,待机模式仅 (6) 接收灵敏度达-100dBm (7) 收发模式切换时间 < 650us

4.4 GPRS无线传输数据终端硬件设计 GPRS模块主要包括模数转换、数据处理和通信模块等。GPRS传输模块选择的是索尼爱立信的GR64。GR64是索尼爱立信新推出的一款内嵌TCP/IP协议栈的GSM/GPRS模块,支持GPRS CLASS 10,内嵌的ARM9微控制器可以开放给用户。GR64具有丰富的存储资源;256KB的脚本空间可同时容纳2个脚本,可用于CSD 方式下脚本远程升级,至少50KB的数据NVM空间和100KB RAM;丰富的功能库涵盖所有的底层驱动,用户只须编写自己的应用程序。为开发基于GPRS网络的TCP/IP应用,索尼爱立信提供了一套完整工具,其机对机通信商业解决方案(M2mpower Business Solution)是一个强有力的支持环境,专为促进提高成本效益比率的无线机对机应用的研发而设计。M2mpower使开发者通过运用特定的开发工具,能够更容易地将无线应用直接嵌入兼容的索尼爱立信机对机产品中。GR64提供丰富的接口:对外有2个自适应波特率和帧格式的串口,其中UARTI 用于AT命令控制或本地脚本下载,UART3为通用串口;另外,还有USB2.0、SPI、I2C、天线、音频接口,12根I/O线(8根复用),AD/DA转换器,蜂鸣器和实时时钟等内置外设。 4.4.1 GR64模块 本设计选用Sony/Ericsson的GR64做为远程传输的GPRS模块。GR64是Sony/Ericsson公司2006年4月上市的新一代可编程无线通信模块,它带有GSM/GPRS全套语音和数据功能。 GR64模块具有超小的体积,所有功能都集中在一块集成的芯片内;较低的功耗,工作电压范围是3.2~4.5 V,数据传输时平均电流330mA,功率为2W,休眠状态时平均电流约为1.6 mA;内嵌TCP/IP协议栈且支持数据透明传输,这使得GR64模块进行数据传输变得非常便捷,同时又有利于用户的二次开发。

RS-232通信模块 4.1 5.1设计目的及任务 设计目的:理解 MCS-51 串口的工作原理;理解 RS-232 总线的逻辑电平与 TTL 电平相互转换的方式;理解 PC 机与单片机串行通信的方式;熟悉RS-232 串口的特点和数据传输方式;熟悉 KEIL uv2、uv3 环境下的程序调试。 设计任务:设计一个单片机与PC 机通过 RS-232 通信的接口电路。功能指标: 1. 能完成单片机逻辑电平与 RS-232 逻辑电平的转换; 2. 通信速率:2400Bit/s,N.8.1 方式; 3. 具备双工通信功能。 设计要求:所设计的接口电路应满足E DP 实 验仪系统设计要求,并能与整个系统有效结合。以下是一个设计范例及其相应电路的讲解,仅供 参考。 4.1 5.2 RS-232串行总线通信的基本原理 单片机和PC 机的串行通信一般采用RS-232、RS-422 或RS-485 总线标准接口,也有采用非标准的20mA 电流环的。为保证通信的可靠,在选择接口时必须注意以下几点: ●通信的最高速率; ●下位机和上位机之间的通信距离; ●因线路干扰带来的影响,因此单片机系统 的抗干扰能力也是一个重要的因素;●组网方式,即可以保证正常通信下的最大通信端口数量;

●通信协议,包括数据格式(如常用的 N 8 1)、校验格式(累加和校验、奇偶校验、CRC 冗余码校验等)、通信方式的等等。 1 . RS-232串行总线接口 RS-232 是EIA(美国电子工业协会)四十年前为公用电话网络数据通信而制定的标准,由于 RS232 的发送和接收是“对地”而言的,采用非平衡模式传输,存在共地 1

电源模块设计分析 电源模块是可以直接贴装在印刷电路板上的电源供应器(参看图1),其特点是可为专用集成电路(ASIC)、数字信号处理器(DSP)、微处理器、存储器、现场可编程门阵列(FP GA) 及其他数字或模拟负载提供供电。一般来说,这类模块称为负载点(POL) 电源供应系统或使用点电源供应系统(PUPS)。由于模块式结构的优点甚多,因此高性能电信、网络联系及数据通信等系统都广泛采用各种模块。虽然采用模块有很多优点,但工程师设计电源模块以至大部分板上直流/直流转换器时,往往忽略可靠性及测量方面的问题。本文将深入探讨这些问题,并分别提出相关的解决方案。 图1,电源供应器 采用电源模块的优点 目前不同的供应商在市场上推出多种不同的电源模块,而不同产品的输入电压、输出功率、功能及拓扑结构等都各不相同。采用电源模块可以节省开发时间,使产品可以更快推出市场,因此电源模块比集成式的解决方案优胜。电源模块还有以下多个优点: ● 每一模块可以分别加以严格测试,以确保其高度可靠,其中包括通电测试,以便剔除不合规格的产品。相较之下,集成式的解决方案便较难测试,因为整个供电系统与电路上的其他功能系统紧密联系一起。 ● 不同的供应商可以按照现有的技术标准设计同一大小的模块,为设计电源供应器的工程师提供多种不同的选择。 ● 每一模块的设计及测试都按照标准性能的规定进行,有助减少采用新技术所承受的风险。 ● 若采用集成式的解决方案,一旦电源供应系统出现问题,便需要将整块主机板更换;若采用模块式的设计,只要将问题模块更换便可,这样有助节省成本及开发时间。

容易被忽略的电源模块设计问题 虽然采用模块式的设计有以上的多个优点,但模块式设计以至板上直流/直流转换器设计也有本身的问题,很多人对这些问题认识不足,或不给予足够的重视。以下是其中的部分问题: ● 输出噪音的测量; ● 磁力系统的设计; ● 同步降压转换器的击穿现象; ● 印刷电路板的可靠性。 这些问题会将在下文中一一加以讨论,同时还会介绍多种可解决这些问题的简单技术。 输出噪音的测量技术 所有采用开关模式的电源供应器都会输出噪音。开关频率越高,便越需要采用正确的测量技术,以确保所量度的数据准确可靠。量度输出噪音及其他重要数据时,可以采用图2 所示的Tektronix 探针探头(一般称为冷喷嘴探头),以确保测量数字准确可靠,而且符合预测。这种测量技术也确保接地环路可减至最小。 图2,测量输出噪音数字 进行测量时我们也要将测量仪表可能会出现传播延迟这个因素计算在内。大部分电流探头的传播延迟都大于电压探头。因此必须同时显示电压及电流波形的测量便无法确保测量数字的准确度,除非利用人手将不同的延迟加以均衡。 电流探头也会将电感输入电路之内。典型的电流探头会输入600nH 的电感。对于高频的电路设计来说,由于电路可承受的电感不能超过1mH,因此,经由探头输入的电感会影响di/dt 电流测量的准确性,甚至令测量数字出现很大的误差。若电感器已饱和,则可采用

1 绪论 1.1 研究背景 通信是指不同的独立系统利用线路互相交换数据,它的主要目的是将数据从一端传送到另一端,实现数据的交换。在现代工业控制中,通常采用计算机作为上位机与下层的实时控制与监测设备进行通讯。现场数据必须通过一个数据收集器传给上位机,同样上位机向现场设备发命令也必须通过数据收集器。串行通信因其结构简单、执行速度快、抗干扰能力强等优点,已被广泛应用于数据采集和过程控制等领域。 计算机与外界的信息交换称为通信。基本的通信方式有并行通信和串行通信两种。串行通信是指一条信息额各位数据被逐位按顺序传送的通信方式。串行通信的特点是:数据位传送,按位顺序进行,最少只需要一根传输线即可完成,成本低但传送速度快,串行通信的距离可以从几米到几千米。 随着计算机技术尤其是单片微型机技术的发展,人们已越来越多地采用单片机来对一些工业控制系统中如温度、流量和压力等参数进行监测和控制。PC机具有强大的监控和管理能力,而单片机则具有快速及灵和的控制特点,通过PC 机的RS-232串行接口与外部设备进行通信,是许多测控系统中常用的一种通信解决方案。而随着USB接口技术的成熟和使用的普及,由于USB 接口有着 RS-232(DB-9)串口无法比拟的优点,RS-232(DB-9)串口正在逐步地为USB 接口所替代。而在现在的大多数笔记本电脑中,出于节省物理空间和用处不大等原因,RS-232(DB-9)串口已不再设置,这就约束了基于RS-232(DB-9)串口与PC 机联络的单片机设备的使用围。当前USB接口逐步取代RS-232(DB-9)串口已是大势所趋,单片机同计算机的USB通信在实际工作中的应用围也将越来越广。本文所介

开题报告 电气工程及其自动化 基于以太网的智能家居通信模块设计 一、选题的背景与意义: 智能家电远程控制系统是一种利用网络通讯技术、智能控制技术、电子技术等多种技术为一体的现代家电控制系统。智能家电远程控制系统的出现可以减少人们对保姆的依赖,提高家用电器的使用灵活性,大大减少家用电器的使用对人们在时间上、空间上造成的束缚,从而提高人们的整体生活水平。总而言之,智能家电远程控制是未来家电发展的必然趋势。 实际智能家电如:家庭局域网、电话小交换、电视分配、灯光控制系统、家电远程控制系统、电动窗帘等。 现代家庭有多种家用电器,分布于一套房子的各个角落。要实现家电的远程控制,必须建立一个小型的控制网络来集中进行控制。 以太网技术已经愈来愈广泛地运用于智能家居系统。本设计目标通过以太网接口,实现上位机与通信模块的数据传输。 二、研究的基本内容与拟解决的主要问题 本课题主要内容是完成通过上位机与通信模块的数据传输。该课题涉及C语言、数字电路、模拟电路、单片机、嵌入式系统、PCB综合布线等方面知识。 基本内容: 1、掌握TCP/IP协议相关技术。 2、选用合适的芯片,能有效地实现以太网数据的收发。 3、编写WEB程序,通过WEB服务访问接口。通过浏览器键入IP地址,网页直观显示部分功能。 三、设计的总体方框图 总体方案如图1所示:

图1 总体方案 3.1器件选择: 3.1.1太网控制器的选择和分析 目前市场上大部分以太网控制器都是专为个人计算系统设计的,既复杂、又占空间,封装均超过80 引脚,本方案以太网控制器采用Microchip 的ENC28J60 芯片,其为嵌入式应用提供一种低引脚数、低成本且高效易用的远程通讯解决方案。ENC28J6符合IEEE802.3 协议,且只有28 引脚,这样可以大大简化相关设计,并可以减小板空间。此外,ENC28J60 以太网控制器采用业界标准的SPI 串行接口,只需4 线便可与主控单片机进行通讯,ENC28J60 以太网控制器的主要功能包括: ①符合IEEE 802.3 协议,集成10 Mb/s 以太网物理层器件(PHY)及媒介接入控制器(MAC可按业界标准的以太网协议可靠地收发信息包数据; ②支持单播、组播和广播数据包,可编程数据包过滤,并在以下事件的逻辑“与”和“或”结果为真时唤醒主机,减轻主控单片机的处理负荷; ③10 Mb/s SPI 接口:业界标准的串行通讯端口,低至18 引脚的8 位单片机也具有网络连接功能; ④可编程8 KB 双端口SRAM 缓冲器:以高效的方式进行信息包的存储、检索和修改,以减轻主控单片机的内存负荷。该缓冲存储器提供了灵活可靠的数据管理机制。 封装类型:

48V/50A开关电源整流模块主电路设计 高频开关电源系统具有体积小,重量轻,高效节能,输出纹波小,输出杂音电压小和动态响应性能好等很多优点,现已开始逐步地取代整流式电源而成为现代通讯设备的新型基础电源系统。随着电子技术,电力电子技术,自动控制技术和计算机控制技术的发展,高频开关电源系统的性能也越来越好。通信用开关电源系统作为开关式稳压电源的一种形式,它的设计内容和设计方法都具有自己的特殊性。 要设计一套通信用开关电源系统,首先要明白对它的全面要求,然后再设计系统的各个部分。高频开关电源主回路和控制回路所用的电路形式,元器件,控制方式都发展很快。它们的设计具有特殊的内容和方法。 1设计要求和具体电路设计 通信基础开关电源系统的关键部分是开关电源整流模块。整流模块的规格很多,结合在工 作中遇到的实际情况,提出该模块设计的硬指标如下: 1) 电网允许的电压波动范围 单相交流输入,有效值波动范围:220 V±20%,即176~264 V;频率:45~65 Hz。 2) 直流输出电压,电流 输出电压:标称-48V,调节范围:浮充,43~56?5V;均充,45~58V。 输出电流:额定值:50A。 3) 保护和告警性能 ①当输入电压低到170 VAC或高到270 VAC,或散热器温度高到75 ℃时,自动关机。 ②当模块直流输出电压高到60 V,或输出电流高到58~60 A时,自动关机。 ③当输出电流高到53~55 A时,自动限流,负载继续加大时,调低输出电压。

4) 效率和功率因数 模块的效率不低于88%,功率因数不低于0.99。 5) 其他指标 模块的其他性能指标都要满足“YD/T731”和“入网检验实施细则”等行业标准。 由于模块的输出功率不大,可采用如下的基本方案来设计主电路: 1) 单相交流输入,采用高频有源功率因数校正技术,以提高功率因数; 2) 采用双正激变换电路拓扑形式,工作可靠性高; 3) 主开关管采用 V MOSFET,逆变开关频率取为50 kHz; 4) 采用复合隔离的逆变压器,一只变压器双端工作; 5) 采用倍流整流电路,便于绕制变压器。 依照上述方案,即可设计出主电路的基本形式如图1。 图1 48V/50A整流模块DC/DC主电路基本形式 以下即可按照模块设计的要求来确定主电路中各元器件的基本参数。 1) 输出整流管的选择 输出整流二极管的工作波形如图2所示。

4 ?>OnCell G3110/G3150 4-15 ? OnCell G3110/G3150 1 / 2 GSM/GPRS IP ? GSM/GPRS 850/900/1800/1900MHz ? ?? TCP Server ? TCP Client ? UDP ?Real ?COM ? Reverse Real COM ? ǖOnCell Central IP ? ǖ? web ? Telnet ? ? ? OnCell G3110/G3150 RS-232 RS-232/422/485 GSM/GPRS/EDGE IP GSM/GPRS/EDGE ? Real COM ?OnCell G3110/G3150 ??OnCell G3110/G3150 CPU TCP/IP ? ? GPRS TCP/IP ?OnCell G3110/G3150 ? ? ? ? I/O ?? ? DI ? ?OnCell G3110/G3150 ? ? 12 ~ 48VDC ?? 2KV EFT/Surge ? ? 15KV ESD ? ? ? ? ? ǖGSM/GPRS/EDGE ǖ 850/900 1800/1900 MHz EDGE ǖClass 12 GPRS ǖClass 12 GPRS ? ǖClass B GPRS ? ǖCS1 ~ CS4 ǖ1 W GSM 1800/1900, 2 W EGSM 850/900 LAN ǖ1 ǖ10/100Mbps ?RJ45 ?MDI/MDIX ? ǖ 1.5 KV ? SIM SIM ǖ1SIM ǖ3 V ? ǖ G3110ǖRS-232?DB9 ? G3150ǖRS-232(DB9 ??RS-422/485?5 pin ? ǖ1 ESD ? ǖ15 KV EFT/ ? ǖ2 KV ǖ5?6?7?8 ǖ1?1.5?2? =None ? ǖNone ?Even ?Odd ?Space ?Mark ǖRTS/CTS ?XON/XOFF ? ǖ50 bps ~ 921.6 Kbps RS-232ǖTxD ?RxD ?RTS ?CTS ?DTR ?DSR ?DCD ?GND RS-422ǖTx+?Tx-?Rx+?Rx-?GND RS-485-4w ǖTx+?Tx-?Rx+?Rx-?GND RS-485-2w ǖData+?Data-?GND I/O ǖ1 ?1 A @ 24 VDC ǖ2 ? ? ?1?ǖ+13 ~ +30 V ? ?0?ǖ-30 ~ -3 V ǖICMP , TCP/IP , UDP , DHCP , Telnet, DNS, SNMP , HTTP , SMTP , HTTPS, SNTP , ARP , SSL Router/Firewall ǖNAT, port forwarding ǖ? ? ǖAccessible IP list ǖReal COM, Secure Real COM, TCP Server, Secure TCP Server, TCP Client, Secure TCP Client, UDP , RFC2217, Ethernet Modem, Virtual Modem, SMS Tunnel ǖSNMP MIB-II, SNMP Private MIB, SNMPv1/v2c/v3, DDNS, IP Report, Web/Telnet/Serial-Console/SSH ǖProvided for Windows 95/98/ME, Windows NT, Windows 2000/XP/2003/Vista/Server-2008, Windows XP/2003/Vista/Server-2008 x64 Edition Windows Real COM ǖWindows 95/98/ME, Win d ows NT, Windows 2000/XP/2003/Vista/Server 2008, Windows XP/2003/Vista/Server 2008 x64 Edition

基于51单片机的蓝牙模块数据传输设计(修订版) 摘要 本设计以STC89C52单片机为控制核心。经蓝牙模块实现无线连接,发送数据和接收数据,通过LCD1602显示接收的数据和编辑发送的数据,两个单片机通过内部程序实现实时接收、发送和显示,从而完成相关要求。 1方案设定 1-1电路设计框图 图4-1 注:由于STC89C52芯片串口寄存器的容量限制,每次收发只能一个字节。 1-2功能叙述 本作品通过HC-05主从机一体蓝牙模块实现与带蓝牙的设备先通过OPP蓝牙协议来实现配对连接,实现连接配对可通过电路板上的数字按键来实现输入,经

STC89C52单片机处理后通过HC-05蓝牙无线传送到另一方单片机上,通过STC89C52单片机处理后可在LCD1602液晶显示所接受到的数据! 1-3使用说明 在接通电源前,先把蓝牙模块插到单片机上,紧接着启动电源。观察蓝牙模块的指示灯,等待两个单片机之间的连接匹配,待指示灯出现双闪后就匹配连接成功。接下来可根据自己想要发送数据在单片机的按键区域(0~9)按下,按下后显示屏便出现你所要发送的数据,确认无误之后就按下单片机上的发送按钮即马上发送到另一方单片机上(两个单片机可以互相发送)!

2系统硬件设计 2-1主控制模块 图6-1

2-2蓝牙收发模块 图8-1 2-3液晶显示模块 图9-1 LCD1602资料: 1602采用标准的16脚接口,其中:

第1脚:GND为电源地 第2脚:VCC接5V电源正极 第3脚:V0为液晶显示器对比度调整端,接正电源时对比度最弱,接地电源时对比度最高(对比度过高时会产生“鬼影”,使用时可以通过一个10K的电位器调整对比度)。 第4脚:RS为寄存器选择,高电平1时选择数据寄存器、低电平0时选择指令寄存器。 第5脚:RW为读写信号线,高电平(1)时进行读操作,低电平(0)时进行写操作。第6脚:E(或EN)端为使能(enable)端,高电平(1)时读取信息,负跳 变时执行指令。 第7~14脚:D0~D7为8位双向数据端。第15~16脚:空脚或背灯电 源。 15脚背光正极。 16脚背光负极。 特性: 3.3V或5V工作电压,对比度可调内含复位电路提供各种控制命令,如:清屏、字符闪烁、光标闪烁、显示移位等多种功能有80字节显示数据存储器DDRAM 内建有192个5X7点阵的字型的字符发生器CGROM8个可由用户自定义的5X7的字符发生器CGRAM特征应用微功耗、体积小、显示内容丰富、超薄轻巧,常用在袖珍式仪表和低功耗应用系统中。操作控制 注:关于E=H脉冲——开始时初始化E为0,然后置E为1。 2-4矩阵键盘模块

ICS29.020 Q/GDW 国家电网公司企业标准 Q/GDW 1376.3—2012 电力用户用电信息采集系统通信协议 第3部分:采集终端远程通信模块接口协议 power user electric energy data acquisition system communication protocol Part 3: acquire terminal telecommunication modules interface XXXX - XX - XX发布XXXX - XX - XX实施

目次 前言................................................................................ II 1 范围 (1) 2 规范性引用文件 (1) 3 术语、定义和缩略语 (1) 4 接口 (2) 4.1 远程通信模块与终端的接口 (2) 4.2 通信模块与SIM卡的接口 (3) 4.3 通信模块网络工作状态指示 (3) 5 功能要求 (3) 5.1 基本业务功能 (3) 5.2 串行口多路复用 (3) 6 命令集 (3) 6.1 标准命令集 (3) 6.2 扩展命令集 (3) 6.3 非透明数据传输命令集 (8) 6.4 透明数据传输命令集 (13) 6.5 主动上报命令集 (14) 6.6 FTP功能命令集 (16) 6.7 锁频相关命令集 (19) 6.8 卫星定位相关命令 (21) 6.9 错误代码 (21) 附录A(资料性附录)标准命令集 (23) 编制说明 (33)

前言 Q/GDW 1376—2012《电力用户用电信息采集系统通信协议》是根据国家电网公司2012年度企业标准制修订计划任务(国家电网科[2012]66号)的安排,对Q/GDW 376—2009《电力用户用电信息采集系统通信协议》的修订。 与原标准相比,本次修订做了如下重大调整和修订: ——增加了磁场异常事件记录; ——增加了终端对时事件记录; ——增加了集中器与本地通信模块交互流程; ——增加了采集终端远程通信模块接口协议(Q/GDW 1376的第3部分)。 Q/GDW 1376—2012《电力用户用电信息采集系统通信协议》分为下列3个部分: ——Q/GDW 1376.1《电力用户用电信息采集系统通信协议第1部分:主站与采集终端通信协议》; ——Q/GDW 1376.2《电力用户用电信息采集系统通信协议第2部分:集中器本地通信模块接口协议》; ——Q/GDW 1376.3《电力用户用电信息采集系统通信协议第3部分:采集终端远程通信模块接口协议》。 Q/GDW 1376—2012实施后代替Q/GDW 376—2009。 本部分是Q/GDW 1376—2012《电力用户用电信息采集系统通信协议》的第3部分。 本部分是《电力用户用电信息采集系统》系列标准之一,规定了采集终端远程通信模块的接口、功能要求,以及AT命令集。 本部分由国家电网公司营销部提出并负责解释; 本部分由国家电网公司科技部归口。 本部分起草单位:中国电力科学研究院、浙江省电力公司 本部分主要起草人:刘宣、郑安刚、王伟峰、杜蜀薇、杜新纲、葛得辉、孟宇、巫钟兴、唐悦Q/GDW 376于2009年12月7日首次发布,本次为第一次修订。

前言 无线方案适用于布线繁杂或者不允许布线的场合,目前在遥控遥测、门禁系统、无线抄表、小区传呼、工业数据采集、无线遥控系统、无线鼠标键盘等应用领域,都采用了无线方式进行远距离数据传输。目前,蓝牙技术和技术已经较为成熟的应用在无线数据传输领域,形成了相应的标准。然而,这些芯片相对昂贵,同时在应用中,需要做很多设计和测试工作来确保与标准的兼容性,如果目标应用是点到点的专用链路,如无线鼠标到键盘,这个代价就显得毫无必要。 本无线数据传输系统采用挪威公司推出的工作于2.4频段的24L01射频芯片。与蓝牙和相比,24L01射频芯片没有复杂的通信协议,它完全对用户透明,同种产品之间可以自由通信。更重要的是,24L01射频芯片比蓝牙和所用芯片更便宜。系统由单片机32F103控制无线数字传输芯片24L01,通过无线方式进行数据双向远程传输,两端采用全双工方式通信,该系统具有成本低,功耗低,软件设计简单以及通信可靠等优点。

1. 总体设计方案 无线通信技术迅速发展,有多种通讯方案可供选择,这里从实用,经济和实现等方面进行综合的考虑分析,选出合适的设计方案。 1.1 无线通信方式的比较和选择 方案一:采用模块进行通信,模块需要借助移动卫星或者手机卡,虽说能够远距离传输,但是其成本较大、且需要内置卡,通信过程中需要收费,后期成本较高。 方案二:采用公司2430无线通信模块,此模块采用总线模式,传输速率可达250,且内部集成高性能8051内核。但是此模块价格较贵,且协议相对较为复杂。 方案三:采用24L01无线射频模块进行通信,24L01是一款高速低功耗的无线通信模块。他能传输上千米的距离(加),而且价格较便宜,采用总线通信模式电路简单,操作方便。 考虑到系统的复杂性和程序的复杂度,我们采用方案三作为本系统的通信模块。 1.2 微控制器的比较和选择 方案一:采用传统的89S52单片机作为主控芯片。此芯片价格便宜、操作简便,低功耗,比较经济实惠,但是应用很局限,且要求较高时传统的89S52单片机达不到要求。 方案二:采用公司生产的430F149系列单片机作为主控芯片。此单片机是一款高性能的低功耗的16位单片机,具有非常强大的功能,且内置高速12位。但其价格比较昂贵,而且是贴片封装,不利于焊接,需要制板,大大增加了成本和开发周期。 方案三:基于公司3内核的32F103系列处理器,采用串行单线调试和,通过调试器你可以直接从获取调试信息,从而使产品设计大大简化,主要应用于要求高性能、低成本、低功耗的产品。 根据系统需要,从性能和价格上综合考虑我们选择方案三,即用32F103作为本系统的主控芯片。 1.3 串行通信方式比较和选择 485串行通信:该接口是采用平衡驱动器和差分接收器的组合,抗噪声干扰性好。具有多机通信能力,这样用户可以利用单一的485接口方便地建立起设备网络。接口组成的半双工网络,一般只需二根信号线,所以它的接口均采用屏蔽双绞线传输,数据信

实验四串口接收模块电路设计 一、实验目的: 1、熟练使用ISE设计工具。 2、理解串口传输协议。理解采用“自顶向下”设计思路,分解模块的方法。 3、在ISE使用Verilog HDL设计串口接收模块,完成仿真、下载。 二、原理分析 (一)串口传输协议概述 设计完成异步串口通信通用异步收发是一种典型的异步串口通信,简称UART。串口通信时序如图1所示。 图1 通用异步收发时序图 由图1可以看出,在没有数据传送时,通信线会一直处于高电平,即逻辑1状态;当有数据传送时,数据帧以起始位开始,以停止位结束。起始位为低电平,即逻辑0状态;停止位为高电平,即逻辑1状态,其持续时间可选为1位、1.5位或2位(本次设计选择持续时间1位)。接收端在接收到停止位后,知道一帧数据已经传完,转为等待数据接收状态;只要再接收到0状态,即为新一帧数据的起始状态。 数据帧的数据位低位(LSB)在前,高位(MSB)在后,根据不同的编码规则,数据位可能为5位、6位、7位或者8位(本次设计数据位定位8位)。校验位也可根据需要选择奇校验、偶校验或者不要校验(本次设计不要校验位)。 (二)串口时序分析 串口通讯常用“波特率”表述串口传输速率,常用的参数有9600 bps 和115200 bps等。在硬件传输角度看,波特率表征了传输一位数据所需要的时间。例如:波特率是9600 bps,传输一位数据的时间是1/9600= 0.000104166666666667秒。如果FPGA系统时钟是20MHZ,则一位数据传输时间相当于(1/9600)/(1/20M)=2083个20MHZ时钟周期。 设一帧数据位数=1(开始位)+8(数据位)+1(校验位)+1(结束位)=11位,所以传输一帧数据的时间是11*1/9600=0.00114583333333333333333333333333秒。 为了稳定采集串口数据帧的数据,需要在每位数据的“中间时刻”采样,由此,需要在每位数据开始时刻对时钟进行计数,若系统时钟是20MHZ,则在计数至2083/2=1042时采样此时刻的数值。 三、系统分析: 为实现串口接收电路,FPGA应该完成: 1、及时发现数据传输的开始,并判断每一位的开始。 2、按照“在数据位中间采样”的要求,确认采样时刻。 3、将采样得到串行数据转换为并行数据。