Quartus_ii_11.0教程(包含modelsim仿真)

- 格式:docx

- 大小:1.01 MB

- 文档页数:20

Modelsim ae 仿真/?_c11_BlogPart_BlogPart=blogview&_c =BlogPart&partqs=cat%3DModelsim仿真验证是CPLD/FPGA设计中的重要一环,QuartusII软件本身带有仿真功能,但是无法使用testbench,而且功能相对简单,对于复杂的设计,画波形图显然不是明智的选择,一般选择Mentor Graphics Corporation的modelsim作为仿真工具。

仿真一般分为功能仿真,前仿真与后仿真。

根据设计需要,编写完代码(Verilog hdl,Vhdl,system Verilog )后,首先进行功能仿真,验证所写代码是否能完成设计功能;前仿真又称为综合后仿真,即在QuartusII完成综合后,验证设计的功能;后仿真又称为时序仿真活布局布线后仿真,是加入延时后的仿真。

对于编译时间较短的小规模设计,一般只进行功能仿真与后仿真。

modelsim有很多版本,ae,pe,le,xe,se等,其中se功能最为强大,见下图:其中ae版本是altera的定制版本,已经包含了altera元器件的编译库,对于altera公司的器件仿真,使用比较简单。

下面以一个设计实例介绍modelsim的仿真过程,工具版本:QuartusII8.1,Modelsim Altera6.1g p1,设计语言使用verilog。

NativeLink 技术在 Quartus II 软件和其它 EDA 工具之间无缝地传送信息,并允许在 Quartus II 软件中自动运行 EDA 工具,所以有两种方式进行QuartusII 与 modelsim的联合设计仿真:QuartusII 软件直接调用modelsim仿真,这种方式步骤简单,但是不方便调试;QuartusII产生modelsim仿真所需要的.vo,.sdo文件,运用 modelsim仿真,这种方式比较麻烦,但是便于调试过程中程序,testbench的更改,一般推荐采用这种方式。

quartus和modelsim中使用mif和hex文件

.mif和.hex文件都是Quartus支持的数据文件格式,常被用作内存初始化文件。

可是,M odelSim却不支持.mif文件,只支持.hex文件格式,这意味着如果你的设计采用了.mif文件

,你的设计将无法在ModelSim中进行仿真。

所以,我们需要用Quartus打开.mif文件,再另存为.hex,然后才能使用。

.hex文件时,需要对ModelSim做如下配置:

1、将quartus50\eda\mentor \modelsim下的convert_hex2ver.dll拷贝至ModelSim的win32 目录下。

2、打开ModelSim安装根目录下的modelsim.ini文件,找到; List of dynamically loaded objects for Verilog PLI applications,在它的下面添加如下一行:

Veriuser = D:/Modeltech_5.7f/win32/convert_hex2ver.dll

经过这样两步后,ModelSim才支持对.hex文件的仿真。

另外我再插一句,modelsim.ini有两个,一个是你的工程里,一个是默认的modelsim安

装目录下面,其实只改工程里的就够了,但是我建议大家要改都改,将来有新工程就不用再

改了。

改了之后一定记得重新启动modelsim,如果还不能用,把工程删了新建一个!

这样肯定能用。

此文档部分内容需要下载才能看见办法:下载此文档全选文档把字体颜色设为黑色即能看见之前看不见的部分Quartus II9.0:/software/quartus2/90sp2/90sp2_quartus_free.exe NIOS II EDS(IDE):ftp:///outgoing/release/90_nios2eds_windows.exe Modelsim:ftp:///outgoing/release/90_modelsim_ase_windows.exeQuartus II 9.1:/akdlm/software/acds/9.1sp2/350/download/91sp2_qu artus_free.exe?token=1386332548_f5dc25adec8b49e66f5eec46a3627bfb&None&f ileExt=.exeNIOS II9.1 EDS(IDE):/akdlm/software/quartus2/91/91_nios2eds_windows.ex e?token=1386335030_1e614163966f8664a364af928416cfb8&None&fileExt=.exe Modelsim:/akdlm/software/quartus2/91sp2/91sp2_modelsim_ae_ windows.exe?token=1386336488_cf044bec8df1aa2a453cc91ba0d45d88&None&fi leExt=.exeQuartus II 10.0:/akdlm/software/acds/10.0/220/standalone/10.0_quart us_free_windows_rev2.exe?token=1386332689_3bc5790488199805fc4b67ed20c34 f4a&None&fileExt=.exeNIOS II10.0 EDS(IDE):/akdlm/software/acds/10.0/220/standalone/10.0_nios2 eds_windows_rev2.exe?token=1386335095_e63663ce893eb225d3ae5e4d49c9f9ba &None&fileExt=.exeModelsim:/akdlm/software/acds/10.0sp1/262/standalone/10.0sp 1_modelsim_ae_windows.exe?token=1386336547_5f335a2d2bc282733152ea5811 9d7624&None&fileExt=.exeQuartus II10.1:/akdlm/software/acds/10.1sp1/197/standalone/10.1sp 1_quartus_free_windows.exe?token=1386332766_4c81ec9f3546c59752af0571bf96 ef8e&None&fileExt=.exeNIOS II10.1 EDS(IDE):/akdlm/software/acds/10.1/153/standalone/10.1_nios2 eds_windows.exe?token=1386335168_ea81eca8dbe2ea7431a85f8e0f29a229&Non e&fileExt=.exeModelsim:/akdlm/software/acds/10.1sp1/197/standalone/10.1sp 1_modelsim_ae_windows.exe?token=1386336588_71b7a7e57bc396a406fd13b176 ea111d&None&fileExt=.exeQuartus II 11.0(此版本内含nios):/akdlm/software/acds/11.0sp1/208/standalone/11.0sp 1_quartus_free_windows.exe?token=1386332838_26157d7f9857465ce5932d149fe b3c40&None&fileExt=.exeModelsim:/akdlm/software/acds/11.0sp1/208/standalone/11.0sp 1_modelsim_ae_windows.exe?token=1386336640_acaa8ef1e313c767144a1864051 d0029&None&fileExt=.exeQuartus II 11.1(此版本内含nios):/akdlm/software/acds/11.1sp2/259/standalone/11.1sp 2_259_quartus_free_windows.exe?token=1386332901_b1eb2141b48c4c465b1481d c14689eec&None&fileExt=.exeModelsim:/akdlm/software/acds/11.1sp2/259/service_pack/11.1s p2_259_modelsim_ae_windows.exe?token=1386336706_8b0f651301a9b22329d06 affa01024c9&None&fileExt=.exeQuartus II 12.0(此版本内含nios):/akdlm/software/acds/12.0sp2/263/standalone/12.0sp 2_263_quartus_free_windows.exe?token=1386332972_34819b9946f53405d88833d 10be08e4a&None&fileExt=.exeModelsim:/akdlm/software/acds/12.0sp2/263/service_pack/12.0s p2_263_modelsim_ae_windows.exe?token=1386336772_292ecea31229d46c38a03 4a4b92138ee&None&fileExt=.exeQuartus II 12.1(此版本内含nios):/akdlm/software/acdsinst/12.1/177/standalone/12.1_1 77_quartus_free_windows.exe?token=1386333089_86a679e1f7423dde0a3ce18af0 df0e53&None&fileExt=.exeModelsim:/akdlm/software/acdsinst/12.1sp1/243/standalone/12. 1sp1_243_modelsim_ae_windows.exe?token=1386336805_79c7e8c44f750290af4c3 7ec42c32b7f&None&fileExt=.exeQuartus II 13.0(此版本内含nios):/akdlm/software/acdsinst/13.0/156/ib_installers/Quart usSetupWeb-13.0.0.156.exeModelsim13.0:/akdlm/software/acdsinst/13.0/156/ib_installers/Model SimSetup-13.0.0.156.exeQuartus II 13.1(此版本内含nios):/akdlm/software/acdsinst/13.1/162/ib_installers/Quart usSetupWeb-13.1.0.162.exeModelsim13.1:/akdlm/software/acdsinst/13.1/162/ib_installers/Model SimSetup-13.1.0.162.exeTHANKS !!!致力为企业和个人提供合同协议,策划案计划书,学习课件等等打造全网一站式需求欢迎您的下载,资料仅供参考。

实验一 EDA开发环境配置一、实验目的1.掌握EDA开发软件的安装与配置;2.掌握EDA功能仿真工具的安装与配置。

二、实验器材电子计算机1台(系统要求windows 7 32/64)、Quartus II 11.0 for Windows软件安装包(附带devices设备支持软件包)、modelsim_se_10.0c 软件安装包。

三、实验原理本次实验主要讲解EDA电路综合工具Quartus II 11.0和EDA逻辑验证工具modelsim_se_10.0c在Windows 7操作系统下的安装与配置过程,软件的安装顺序依次是:1)Quartus II 11.0 for Windows7主程序11.0_quartus_windows2)Quartus II 11.0 for Windows7设备支持包11.0_devices_windows3)Quartus II 11.0 for Windows7主程序升级包11.0sp1_quartus_windows4)破解Quartus II 11.05)逻辑功能仿真软件modelsim-win32/64-10.0c-se6)破解modelsim注意,请严格按照改顺序进行安装!四、实验步骤1.安装Quartus II主程序1) 请确认计算机安装的操作系统是windows 7 32/64bit,系统盘剩余空间在10GB以上,程序安装包存放在不含中文和空格的路径下,退出所有防火墙(如各类管家,卫士)和杀毒软件;双击11.0_quartus_windows.exe文件进行Quartus II 11.0主程序的安装;2)双击11.0_quartus_windows.exe文件后跳出如图1-1所示对话框,点击”Install”按钮进行主程序解压;图1-1 解压操作界面3)解压完成后出现如图1-2所示界面,按照红框提示选中相关选项,点击”Next”;图1-2安装提示界面4)接下来出现如图1-3所示用户协议界面,按照红框提示选中相关选项,点击”Next”;图1-3用户协议界面5)设置程序的安装路径,如图1-4上方红框内部所示,建议保持默认路径,如果需要修改安装路径,请注意路径中不要出现中文以及空格。

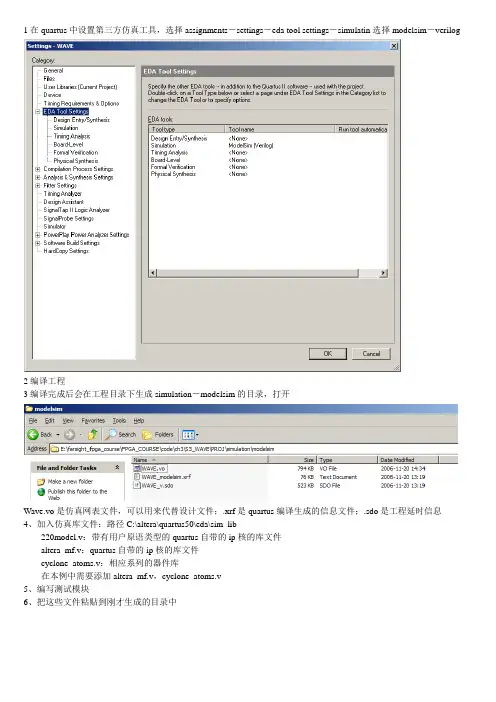

1在quartus中设置第三方仿真工具,选择assignments-settings-eda tool settings-simulatin选择modelsim-verilog2编译工程3编译完成后会在工程目录下生成simulation-modelsim的目录,打开Wave.vo是仿真网表文件,可以用来代替设计文件;.xrf是quartus编译生成的信息文件;.sdo是工程延时信息4、加入仿真库文件:路径C:\altera\quartus50\eda\sim_lib220model.v:带有用户原语类型的quartus自带的ip核的库文件altera_mf.v:quartus自带的ip核的库文件cyclone_atoms.v:相应系列的器件库在本例中需要添加altera_mf.v,cyclone_atoms.v5、编写测试模块6、把这些文件粘贴到刚才生成的目录中7、打开modelsim8、选择file-new-project9、指定工程名称,路径,工作目录10、添加设计文件(1)(2)(3)(4)11、编译工程全部编译功能仿真12、修改wave.vo文件把延时信息注释掉//initial $sdf_annotate("WA VE_v.sdo");13、重新编译wave.vo14、选择simulate开始仿真15、选择顶层模块,然后确定16、右键选择添加信号到波形图17、在命令行中敲入run 1ms回车,开始仿真18、观察波形二进制显示十进制显示没有延时时序仿真19、把wave.vo的修改过的注释改回来,重新编译20选择simulate21、选择sdf标签22、加入.sdo文件,把下面的sdf options都选中23、选择ok进行仿真24、和功能仿真一样加入波形图,仿真25、看延时。

1.下载convert_hex2ver.dll文件,convert_hex2ver.dll就是把hex文件转换成ModelSim 能认出来的ver文件的动态链接库文件。

新版本的QuartusII中已经不带此文件了。

需要在网上找一份。

(老版本的软件里带了此文件(路径:quartusXX/eda/mentor/modelsim/),应当可以用。

)2.将convert_hex2ver.dll文件放在modelsim安装路径的win32目录下;3. 在ModelSim安装的目录下找到modelsim.ini文件,将其只读属性去掉,在“; List of dynamically loaded objects for Verilog PLI applications,”后填入一行Veriuser = convert_hex2ver.dll。

保存文件,将只读属性改回来。

4. 修改Rom.v文件中”altsyncram_component.init_file = ”后的XX.hex的路径(必须为hex文件的绝对路径)5. 最后就是进行正常的modelsim仿真。

(比如库的创建和文件添加的操作,对于IP核别忘了添加220model.v和altera_mf.v这两个文件,在quartus安装目录eda/sim_lib下)ModelSim不支持mif文件,这就意味着如果你要这样做的话,只有先把mif另存为hex,再用上面的办法。

mif文件转hex的方法:用quartuus打开现有的mif文件,然后新建一个hex文件,存储的宽度和深度必须匹配,将mif文件和hex文件的地址和数据的格式设置为一致,然后在mif编辑界面直接选中全部数据,进行复制,最后在hex编辑界面选中全都数据,粘贴后保存即可。

quartusii编程语法摘要:一、quartusii 编程语法简介二、quartusii 编程基础1.设计输入2.逻辑电路描述3.编译和仿真三、quartusii 编程进阶1.高级功能模块2.优化设计3.时序分析四、quartusii 编程实践1.实例分析2.常见问题及解决方法五、quartusii 编程在我国的发展与应用正文:quartusii 是一款由Altera 公司开发的FPGA 设计开发软件,广泛应用于数字电路设计、ASIC 设计等领域。

本篇文章将为您介绍quartusii 编程语法。

一、quartusii 编程语法简介quartusii 编程语法主要包括设计输入、逻辑电路描述、编译和仿真三个方面。

设计输入是指通过文本或图形方式描述数字电路的设计需求;逻辑电路描述则是指通过文本或图形方式实现逻辑电路的描述;编译和仿真是指将设计输入转化为可执行的硬件描述语言,并进行仿真验证。

二、quartusii 编程基础1.设计输入在quartusii 中,设计输入主要包括原理图、文本和波形文件等。

原理图是一种通过图形方式描述数字电路的方式,可以直观地表示数字电路的结构和连接关系。

文本输入则是一种通过文本方式描述数字电路的方式,可以详细地描述数字电路的逻辑功能和时序关系。

波形文件则是一种通过图形方式描述数字电路的时序波形,可以用于验证数字电路的时序功能。

2.逻辑电路描述在quartusii 中,逻辑电路描述主要包括逻辑门、触发器、寄存器、计数器等功能模块。

逻辑电路描述时,需要遵循一定的语法规则,例如使用“module”定义模块,使用“input”和“output”定义输入和输出端口等。

3.编译和仿真在quartusii 中,编译和仿真是指将设计输入转化为可执行的硬件描述语言,并进行仿真验证。

编译时,quartusii 会将设计输入转化为Verilog 或VHDL 等硬件描述语言,并生成对应的.v 文件。

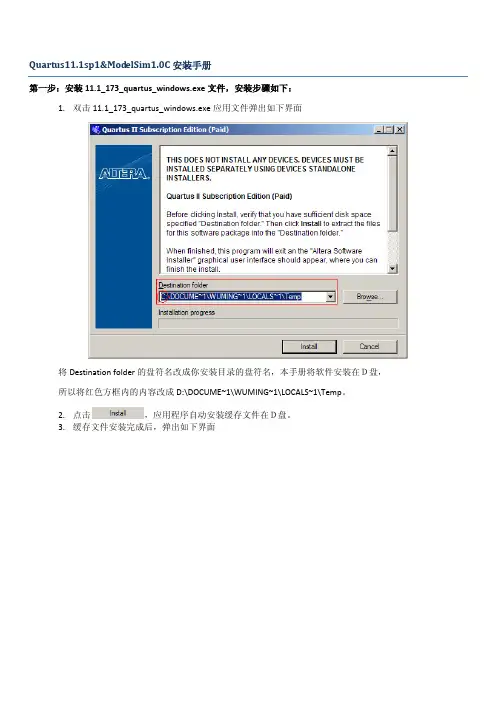

Quartus11.1sp1&ModelSim1.0C安装手册第一步:安装11.1_173_quartus_windows.exe文件,安装步骤如下:1.双击11.1_173_quartus_windows.exe应用文件弹出如下界面将Destination folder的盘符名改成你安装目录的盘符名,本手册将软件安装在D盘,所以将红色方框内的内容改成D:\DOCUME~1\WUMING~1\LOCALS~1\Temp。

2.点击,应用程序自动安装缓存文件在D盘。

3.缓存文件安装完成后,弹出如下界面直接点击4.勾选,然后点击。

5.弹出如下界面将Destination Directory改成D:\altera\11.1。

然后点击。

6.点击。

7.点击,软件自动将安装在D:\altera\11.1路径下。

这个过程大概需要10分钟左右。

8.软件安装成功后,会弹出如下两个界面:这个提示是问软件已经安装完毕,是否清除安装前的缓存文件,这里点击Yes。

这里点击OK即可。

9.点击,即可完成本软件的安装。

第二步:对软件进行破解1.双击D:\TOOL\quartus ii 11.1\Crack_QII_11.1_Windows\Crack_QII_11.1_Windows密码12345\Crack_QII_11.1_x86目录下的Quartus_11.1_x86破解器(内部版).exe文件,弹出对话框2.点击,弹出对话框3.点击,定位到安装目录下的bin目录下的sys_cpt.dll文件。

4.点击,系统自动生成一个license文件。

5.点击,然后点击,退出破解器。

6.用记事本打开生成的License文件,用你的以太网卡号代理里面的XXXXXXXXXXXXXX,然后保存即可完成破解。

到目前为止,我们已经完成了QuartusII11.1的安装。

!!!第三步:安装器件系统里面有11.1_173_devices_cyclone_max_legacy_windows和11.1_173_devices_stratix_hardcopy_windows两个器件包,其中11.1_173_devices_cyclone_max_legacy_windows中包含了cyclone、max系列的器件,11.1_173_devices_stratix_hardcopy_windows中包含了stratix等高端器件。

QuartusII11.0工程升级为QuartusII13.1 仿真NativeLink Error错误解决方法(北京郭树忠)因系统功能扩展,需要重新对某一程序模块进行仿真,由于目前使用的QuartusII13.1仿真软件与原工程软件使用的QuartusII11.0仿真软件版本不同,在工程升级编译完成后运行仿真软件时,出现了NativeLink Error错误,经过反复检查,找到了原因,问题得以顺利解决。

为此,整理了此文档,分享给大家,希望给开展类似工作的同学们节省部分时间。

一、过程原工程环境:QuartusII11.0,ModelSim SE-64 10.0c;新工程环境:QuartusII13.1,ModelSim-Altera starter Edition 13.1.0.162。

在将QuartusII11.0的软件工程在QuartusII13.1下编译完成后,选择Tools->Run Simulation Tool->RTL Simulation,运行仿真软件,如图1.启动仿真窗口所示。

图1.启动仿真窗口仿真软件窗口出现错误提示:NativeLink Error.You selected ModelSim as Simulation software in EDA Tool Settings, However NativeLink Found ModelSim-Altera in the path –correct path or change EDA Tools Settings and try again.如图2.NativeLink Error错误提示窗口。

图2. NativeLink Error错误提示窗口因仿真软件版本不同,仿真软件安装目录也不同,因此出NativeLink Error 错误提示后首先想到的是在EDA Tools Settings中配置仿真软件路径,并在全局变量中设置license_file 文件路径LM_LICENSE_FILE=c:\altera\13.1\ modelsim_ase\LICENSE_DELLXPX.TXT。

使用ModleSim 进行前仿真和后仿真前言由于Quartus 9.1SP1已经说明在Quartus的后续版本不再支持内置的仿真工具,而且Quartus自带的波形仿真工具实在很差,且不能加载testbench,所以使用ModelSim-Altera进行仿真。

本文使用工具的版本是,Quartus II 9.1 sp1, ModelSim Altera 6.4a。

皆以全部破解。

本文的例程是基于特权的《深入浅出玩转FPGA》lesson9,无符号16位乘法器。

要使用Quartus中的Tools -> Run EDA Simulatin Tools -> EDA RTL Simulatio,直接调用ModleSim则需要在Tools -> Options 里设置ModelSim的路径。

如图:使用ModelSim进行前仿真前仿真既功能仿真,在特权配套的lesson9讲解视频中已经做过讲解。

1:在Quartus中选择Assignments -> Settings。

在EDA Tool Settings 选择Simulation,设置Tool name为ModelSim-Altera,Format for output netlist选择Verilog(会生成.vo的Verilog输出文件,若选择VHDL则会生成.vho的VHDL输出文件),其它的可以默认就行。

如图12:添加testbench文件。

点击上图中的TestBenches,选择New新建一个,Test bench name和Top level module in test bench中填入测试文件的模块名,Design instance name in test bench 填入测试文件中例化的源文件模块的例化模块名。

在Testbench files 里点Add,添加已经写好的TestBench测试文件。

如图2:点OK返回。

3,点击Tools -> Run EDA Simulatin Tools -> EDA RTL Simulatio,Quartus会直接调用ModleSim,且vtf_test中的信号已经加入wave中,点RUN all,会运行显示波形。

Modelsim SE 6.6d1、按照正常程序安装过程安装Modelsim SE 6.6d2、在破解文件夹中点击make.bat生成license.dat文件。

3、然后把生成的license.dat和mgls.dll两个文件拷贝到Modelsim 安装目录的win32文件夹下。

我的Modelsim安装在D盘,所以拷贝到D:\modeltech_6.6d\win324、添加环境变量。

在计算机上右键,选择属性,然后进入高级系统设置。

在高级选项页中选择环境变量。

5、在下面的系统变量中选择新建,然后设置变量名为LM_LICENSE_FILE,变量值指向刚才复制到Modelsim目录下的license.dat文件。

注意事项:由于网上的破解文件版本不一,可能导致无法成功破解,或是提示mgls.dll文件错误。

遇到此类问题可以尝试使用其他版本的破解文件或是重新生成license.dat文件,然后重新替换到Modelsim目录下。

安装包里可能会包含着几个版本的破解文件。

Quartus II 12.0对于32位和64位系统,软件的安装是一致的,只需直接安装即可。

但是对于两者的破解是有区别的。

1、点击setup进行安装,所有设置选择默认选项即可。

2、对于32位系统,拷贝Quartus_12.0_x86破解器和sys_cpt.dll文件到Quartus安装目录的bin文件夹下。

例如:D:\altera\12.0\quartus\bin3、然后再bin文件夹内运行Quartus_12.0_x86破解器,生成的license文件放到bin文件夹下。

4、然后进入Quartus II 12.0,可以先使用30天的试用方式打开。

然后选择Tools/ License Setup。

5、复制NIC ID到刚才生成的license文件内替换到文件中的XXXXXXX。

笔记本中显示有两个ID,只选择使用一个即可。

注意事项:破解完成后打开软件,如果提示sys_cpt.dll错误,可以使用其他的sys_cpt.dll 文件替换。

一、准备工作首先需要EDA综合工具生成用于功能或时序仿真的网表文件(VHDL 为.vho,Verilog为.vo),以及使用EDA仿真工具进行时序仿真时所需要的包含时序延时信息的标准延时格式输出文件(.sdo)。

这里我们以EDA工具为ALTERA的Quartus II 9.0为例,使用Verilog DHL,讲解如何使用Quartus II 9.0生成ModelSim 6.2b时序仿真所需的.vo及.sdo文件。

这里我们先使用EDA工具对工程进行综合,综合通过后进行如下操作。

1、设置仿真工具的路径。

设置用户存放ModelSim的路径,选择菜单栏的Tools-->Options,如下图所示:在Options窗口下,选择左栏Category下的General-->EDA Tools Options,则右栏出现相应的仿真工具。

我们选择ModelSim,并设置路径(该路径为用户存放ModelSim的路径),完成后单击OK。

如下图所示:选择菜单栏的Assignments-->EDA Tools Settings,如下图所示:此时我们进入相应的状态栏,选择左栏Category下的EDA Tools Options-->Simulation,在Tool name选择ModelSim,其他Format for output netlist选择Verilog,其它使用默认参数。

完成后单击OK。

如下如所示:至此,再次进行综合,在工程路径下的simulation/modelsim将生成后仿真(也称时序仿真)所需的网表文件(.vo)及延时文件(.sdo)。

二、ModelSim进行时序仿真1、打开ModelSim,修改存放编译后库文件的位置。

选择菜单栏File-->Change Directory,如下图所示。

第一次需要编译,以后只需要调用该库文件就行,不需要重新编译(前提是使用该库支持,后面将介绍我们编译的库支持资源)。

Modelsim 仿真方法总结Modeling 仿真工具是Model公司开发的。

它支持Verilog、VHDL以及他们的混合仿真。

Modelsim各版本的使用方法大体一致,Modelsim仿真主要分为前仿真和后仿真。

下面来具体介绍modelsim的仿真方法,涉及quartus-modelsim联合(使用)仿真的差异会特别提示。

前仿真与后仿真说明1.1 前仿真前仿真也称为功能仿真、行为仿真。

旨在验证电路的功能是否符合设计要求,其特点是不考虑延迟(包括门延迟与线延迟),主要验证电路与理想情况是否一致。

前仿真需要用到RTL级代码(由源代码经过综合后产生)与Testbench。

1.2)后仿真后仿真也称为时序仿真或者布局布线仿真。

是指在电路已经映射到特定的工艺环境以后,综合考虑门延迟与线延迟的影响,验证电路在一定的时序条件下是否存在时序违规以及能否满足设计构想的过程。

需要用到的文件是——从布局布线结果中抽象出来的门级网表、testbench和后缀名为sdo或者sdf的标准时延文件。

注:扩展名为sdo和sdf的标准时延文件包含门延迟与实际布线延迟,能较好的反应芯片的实际工作情况。

二)modelsim仿真主要有以下几个步骤:(1)建立库并映射库到物理目录;(2)编译源代码(包括Testbench);(3)执行仿真;解释:①库:modelsim中有两类仿真库。

一种是工作库,默认名为work;另一种是资源库。

Work库中存放当前工程下所有已经编译过的文件,所以编译前一定要建立一个work 库。

资源库存放work库中已经编译文件所要调用的资源,这样的资源可能有很多,它们被存放在不同的资源库内。

(例如要想对综合在cyclone芯片中的设计做后仿真,就需要有一个名为cyclone_ver的资源库。

)映射库用于将已经预编译好的文件所在目录映射为一个modelsim可识别的库。

(此即是为仿真库建立一个逻辑映像的行为过程,后面会提到,在modelsim中新建库时,create a new library and a logical mapping to it或a map to an existing libraryd的提示)上述三个步骤是大的框架,前仿真和后仿真均是按照这个框架进行的,建立modelsim工程对前后仿真来说都不是必须的。

Quartus II 13.1与自带modelsim_Altera 10.0d仿真软件的联调Step11、编写好Verilog代码后,编译(点),直到没有错误为止;2、接下来生成testbench文件,Processing →Start →Start Test Bench Template Writer,注意下方Message栏中,EDA Netlist Writer是否生成成功,成功的提示如下:Step21、接下来完成调用modelsim_Altera 10.0d的设置1.首先要在quartus 2中正确填入modelsim程序的地址:Tools →Options →General →EDA Tool Options ,如下图:2.因为我调用的是Modelsim-Altera,所以填入Modelsim-Altera程序所在地址:D:\altera\13.1\modelsim_ase\win32aloem(注:一般只是盘符不一样,我装在D 盘,如果你装在C盘,那地址就是C:\altera\13.1\modelsim_ase\win32aloem)3.接下来,就是正确载入测试文件了,载入前,先要修改testbench:(测试文件只是模板,要自己加入时钟信号,输入信号,即添加激励,否则无法出现仿真波形)Assignments →Settings 出现如下界面:i.勾选下图的小方格,当在Quartus中编译快完成时,自带调出Modelsim_Altera;ii.如果你的代码是用Verilog写的,则此处要选Verilog HDL;iii.下面这个选项是仿真时间单位:`timescale 仿真时间单位/时间精度(eg: `timescale 100ns/10ns)仿真时间单位和时间精度,就比如常见的刻度尺,仿真时间单位以cm为单位,时间精度以mm为单位,所以仿真时间单位是大于或等于时间精度的。

iv.选择Compile test bench ,点Test Benches…v.出现下图,点New…vi.出现下图:vii.先填写下图,点File name 空格旁的,添加生成的Testbench文件,格式是 .vt ,点Add 完成添加。

Quartus ii 10.0教程 说明 本文的部分章节,来源于本人翻译的Terasic DE2-115的英文入门文档。

平台 硬件:艾米电子EP2C8-2010增强版套件 软件:Quartus II 10.0 + ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition

内容 典型的CAD流程 开始 新建工程 录入Verilog设计 编译设计 引脚分配 仿真设计电路 编程及配置到FPGA器件 测试设计电路

典型的CAD流程 计算机辅助设计(CAD)软件,使得运用可编程逻辑器件实现所需逻辑电路,变得容易。比如现场可编程门阵列(FPGA)。典型的FPGA CAD设计流程如图1所示。 图1 典型的FPGA CAD设计流程

CAD流程包含以下步骤: 设计输入——所需电路可通过原理图方式或硬件描述语言方式(如Verilog或VHDL)进行设计。 综合——输入的设计被综合进入由逻辑元素(LEs,FPGA芯片提供)组成的电路中。 功能仿真——综合电路被测试以验证其功能是否正确,次仿真不考虑时序因素。 布局布线——CAD Fitter工具决定网表中定义的LEs如何布置成FPGA芯片中的实际LEs。 时序分析——分析已布局布线电路中的不同路径的传播延迟,用以指示所需电路的性能。 时序仿真——测试已布局布线电路,验证其是否在功能和时序上都正确。 编程及配置——设计的电路,通过编程配置开关,被实现到一个物理的FPGA芯片。配置开关用于配置LEs和建立所需线路连接。

本指南介绍Quartus II软件的基本特征。展示如何使用Verilog硬件描述语言来设计和实现电路。使用GUI来实现Quartus II指令。通过本份指南,读者将学习到: 新建工程 使用Verilog代码录入设计 将综合的电路布局到Altera FPGA 分配电路的输入输出到FPGA上的指定引脚 仿真设计电路 编程配置艾米电子EP2C8核心板上的FPGA芯片

1. 开始 在Quartus II中设计的每个逻辑电路或子电路,叫做一个工程。软件每次运行一个工程,并将所有信息保存在单一文件夹中。欲开始一个新的逻辑电路设计,第一步就是新建一个文件夹来保存文件。为了保存本指南的设计文件,在D盘新建introtutorial文件夹。指南者运行的范例为一个简单的双路灯控电路。 打开Quartus II软件,将看到类似于图2的画面。该显示画面包括若干窗口,用户可使用鼠标选择,以访问Quartus II软件的相关功能。Quartus II提供的大多数命令都可用菜单形式来访问。例如,在图2中,在File标签下点击左键,可打开如图3所示的菜单。用左键单击Exit可退出Quartus II软件。 图2 Quartus II主体显示

图3 File菜单一例

对于有些命令,需要连续访问两个或以上的菜单才可以使用。

1.1 Quartus II在线帮助 Quartus II软件提供了容易理解的在线文档,可解答许多在使用软件时遇到的问题。用户可通过选择Help>Search来快速访问帮助话题,在打开的对话框中,可以输入关键字。另外一个方法是,内容感应帮助,以快速查找指定话题的文档。在大多数的应用中,按住键盘上的F1键将打开一个显示该应用的可用命令的帮助窗口。

2 新建工程 按如下步骤新建工程: 1. 选择File>New Project Wizard,以打开图4所示窗口,可通过Don't show me this introduction again跳过此窗口步骤。单击Next,出现图5所示窗口。

图4 引导的任务显示

图5 创建新的工程

2. 选择工作文件夹introtutorial,也可以使用您自己设定的文件夹。工程必须有一个名字,通常情况下,与顶层设计实体的名字相同。如图5所示,选择light作为工程名和顶层实体名。单击Next。因为还没有创建introtutorial文件夹,Quartus II弹出一个对话框,询问是否新建所需文件夹,如图6所示。单击Yes,将会引出图7所示的窗口。

图6 创建新的工程文件夹与否?

图7 添加用户指定设计文件

3. 如果没有已存在的设计文件,单击Next,将会打开如图8所示的画面。

图8 选择器件家族和指定的器件

4. 艾米电子EP2C8核心板采用的器件为Cyclone II EP2C8Q208C8。此处选择Cyclone II器件家族,器件为PQFP封装,有208个引脚,速度等级为8。单击Next,出现图9所示画面。 图9 指定第三方EDA工具

5. 用户可指定一些第三方EDA工具。持续Simulation选用ModelSim-Altera,格式为Verilog HDL。单击Next,出现图10所示窗口。

6. 设置一览如图10所示。单击Finish,返回Quartus II主体窗口。标题栏将显示light工程,如图11所示。

图10 工程设置一览

图11 Quartus II显示已建工程

3 使用Verilog代码设计输入 作为一个设计范例,我们将采用双路的灯控电路,如图12所示。此灯可由两个按键中的任一按键来控制,x1和x2,按键的闭合相应的逻辑值为1。真值表也同时在图中给出。注意输入x1和x2是异或的关系,但是我们仍然用门来显示。

图12 灯控电路

所需电路,如图13所示,使用Verilog代码来描述。注意,Verilog模块叫做light,这个图5所示的名称是一致的。此代码的编辑可以使用任何可存储ASCII码的文本编辑器,或者使用Quartus II自带的编辑器。当然,文件的名称可以任意取;而和顶层Verilog模块的名称一致,是一个设计惯例。文件名称必须带.v扩展名,用以指示此文件为Verilog文件。所有,我们使用light.v这个名称。

图13 图12所示电路的Verilog代码

3.1 使用Quartus II 文本编辑器 本节将展示如何使用Quartus II文本编辑器。如果你喜欢使用其他文本编辑器来创建Verilog源文件,可以逃过此节。选择File>New打开图14所示窗口,选择Verilog HDL File,并单击OK。这将打开文本编辑器窗口。第一步是指定所创建的文件的名称。选择File>Save As,打开图15所示的对话框。选择存储类型为Verilog HDL File,填写名称为light.v。单击Save,打开图16所示窗口。输入图13所示的代码。使用Ctrl+s保存该文件。 图14 选择新建的文件类型

图15 命名文件

图16 文本编辑器窗口

3.1.1 使用Verilog模板 对于设计者来说,Verilog的语法有时很难被记住。为了解决问题,文本编辑器提供了Verilog模板集。这些模板提供了不同类型的Verilog表达的范例,譬如module声明、always块和设置语句的陈述。可以通过Edit>Insert Template>Verilog HDL来浏览这些模板,以熟悉这些资源,这是相当值得的。

3.3 添加设计文件到工程中 正如图7所讨论的那样,我们可以告诉Quartus II软件,哪些文件是当前工程的一部分。要查看当前的light工程中已包含的文件列表,选择Assignment>Setting>File,这将打开图17所示画面。另外一个可用的方法是选择标签Project>Add/Remove Files in Project。 使用Quartus II文本编辑器创建文件时,勾上Add file to current project选项,所创建文件即自动加入到工程文件列表。如果使用的不是Quartus II自带的文本编辑器,那么图17,列表中就没有所创建的文件,此时必须手动添加文件到工程文件列表中。欲添加文件到工程文件列表中,单击图17中的File Name:的按钮,弹出图18所示对话框,选择light.v,单击Open。再次查看图17画面,此时所添加的文件就已经在文件列表了。需要注意的是,在大多数案例中,Quartus II软件可根据各个实体自动找到正确的文件,即使某些文件没有被认真地添加到工程中。 然而,对于包含许多文件的复杂工程,按照上述方法,添加指定所需文件到工程中,是一个很好的设计惯例。 图17 设置窗口 图18 选择文件

4 编译设计电路 在light.v中Verilog代码,要经过几个Quartus II工具的处理:分析代码、综合电路以及生成目标芯片的实现内容。这些应用程序被聚集在一起,且被称作编译器。

选择Processing>Start Compilation运行编译器,或者单击 按钮运行。在编译过程中,Quartus II的左边会显示不同阶段的进度。编译成功(或不成功)后,会弹出一个对话框。

单击OK确认。Qartus II会显示图19所示画面的编译报告。当编译成功后,也可以通过 按钮手动打开编译报告。