组合逻辑控制器设计

- 格式:doc

- 大小:301.96 KB

- 文档页数:14

基于PLC的钻孔组合机床控制系统设计摘要:钻孔组合机床是一种常用的加工设备,其控制系统对于机床的工作效率和加工质量有着重要的影响。

本文基于PLC(可编程逻辑控制器)技术,设计了一种钻孔组合机床控制系统,并对系统进行了仿真和实验验证。

实验结果表明,该控制系统能够稳定可靠地控制钻孔组合机床的工作,并且具有较高的精度和效率。

关键词:PLC;钻孔组合机床;控制系统;仿真;实验验证一、引言钻孔组合机床是一种常用的加工设备,广泛应用于各行各业。

传统的钻孔组合机床控制系统多采用电磁继电器和电路控制的方式,具有控制精度低、可靠性差等缺点。

而PLC技术具有编程灵活、控制精度高、可靠性好等优点,因此在钻孔组合机床控制系统中得到了广泛应用。

本文基于PLC技术,设计了一种钻孔组合机床控制系统,并对系统进行了仿真和实验验证。

二、PLC钻孔组合机床控制系统的设计1.控制系统硬件设计PLC钻孔组合机床控制系统的硬件部分包括PLC主控模块、人机界面模块、执行机构模块等。

PLC主控模块实现对整个控制系统各部分的控制指令的解码和执行;人机界面模块为操作员提供了直观的控制界面;执行机构模块负责实际的加工操作。

2.控制系统软件设计PLC钻孔组合机床控制系统的软件部分主要包括控制程序的编写和参数设置。

控制程序的编写是整个软件设计的核心,包括自动控制程序、手动控制程序、故障检测程序等。

参数设置是根据具体的机床和工件进行的,包括钻孔深度、钻孔速度等参数的设置。

三、PLC钻孔组合机床控制系统的仿真为了验证设计的控制系统的正确性和可行性,本文进行了系统的仿真。

仿真结果表明,控制系统能够稳定可靠地控制钻孔组合机床的工作,并且具有较高的精度和效率。

四、PLC钻孔组合机床控制系统的实验验证根据仿真结果,设计了实验验证方案,并进行了实验。

实验结果表明,控制系统能够稳定可靠地控制钻孔组合机床的工作,实现了钻孔深度和钻孔速度的准确控制。

五、总结通过本文的研究,基于PLC的钻孔组合机床控制系统设计得到了较好的结果。

实验题目存储器部件教学实验一、实验目的:1. 熟悉ROM芯片和RAM芯片在功能和使用方法等方面的相同和差异之处。

学习用编程器设备向EEPROM芯片内写入一批数据的过程和方法。

2. 理解并熟悉通过字、位扩展技术实现扩展存储器系统容量的方案。

3. 了解静态存储器系统使用的各种控制信号之间正常的时序关系。

4. 了解如何通过读、写存储顺的指令实现对58C65 ROM芯片的读、写操作。

加深理解存储器部件在计算机整机系统中的作用。

二、实验设备与器材:TEC-XP+教学实验系统和仿真终端软件PCEC。

三、实验说明和原理:1、内存储器原理内存储器是计算机中存放正在运行中的程序和相关数据的部件。

在教学计算机存储器部件设计中,出于简化和容易实现的目的,选用静态存储器芯片实现内存储器的存储体,包括唯读存储区和随读写存储区两部分,ROM存储区选用4片长度8位、容易8KB的58C65芯片实现,RAM存储区选用2片长度8位、容量2KB的6116芯片实现,每2个8位的芯片合成一组用于组成16位长度的内存字,6个芯片被分成3组,其地址空间分配关系是:0-1777h用于第一组ROM,固化监控程序,2000-2777h用于RAM,保存用户程序和用户数据,其高端的一些单元作监控程序的数据区,第二组ROM的地址范围可以由用户选择,主要用于完成扩展内存容量的教学实验。

地址总线的低13位送到ROM芯片的地址线引脚,用于选择芯片内的一个存储字。

用于实现存储字的高位字节的3个芯片的数据线引脚、实现低位字节的3个芯片的数据线引脚分别连接在一起接到数据总线的高、低位字节,是实现存储器数据读写的信息通路。

数据总线要通过一个双向三态门电路与CPU一侧的内部总线IB 相连接,已完成存储器、接口电路和CPU之间的数据通讯。

2、扩展教学机的存储空间四、实验内容:1) 要完成存储器容量扩展的教学实验,需为扩展存储器选择一个地址,并注意读写和OE等控制信号的正确状态。

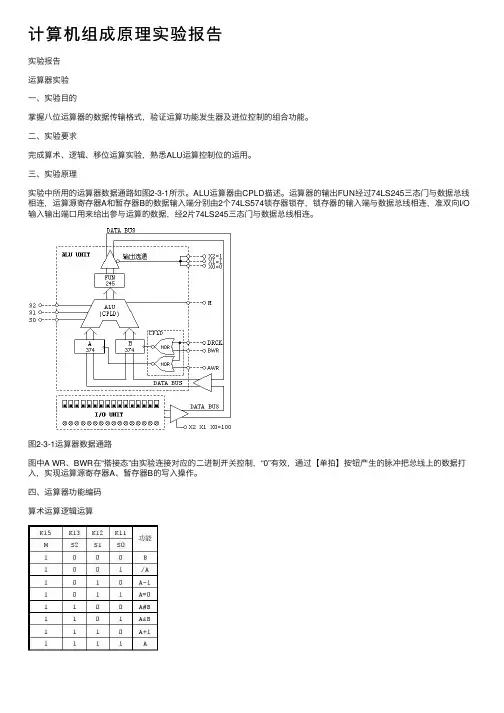

计算机组成原理实验报告实验报告运算器实验⼀、实验⽬的掌握⼋位运算器的数据传输格式,验证运算功能发⽣器及进位控制的组合功能。

⼆、实验要求完成算术、逻辑、移位运算实验,熟悉ALU运算控制位的运⽤。

三、实验原理实验中所⽤的运算器数据通路如图2-3-1所⽰。

ALU运算器由CPLD描述。

运算器的输出FUN经过74LS245三态门与数据总线相连,运算源寄存器A和暂存器B的数据输⼊端分别由2个74LS574锁存器锁存,锁存器的输⼊端与数据总线相连,准双向I/O 输⼊输出端⼝⽤来给出参与运算的数据,经2⽚74LS245三态门与数据总线相连。

图2-3-1运算器数据通路图中A WR、BWR在“搭接态”由实验连接对应的⼆进制开关控制,“0”有效,通过【单拍】按钮产⽣的脉冲把总线上的数据打⼊,实现运算源寄存器A、暂存器B的写⼊操作。

四、运算器功能编码算术运算逻辑运算K23~K0置“1”,灭M23~M0控位显⽰灯。

然后按下表要求“搭接”部件控制路。

表2.3.2 运算实验电路搭接表算术运算1.运算源寄存器写流程通过I/O单元“S7~S0”开关向累加器A和暂存器B置数,具体操作步骤如下:2.运算源寄存器读流程关闭A、B写使能,令K18=K17=“1”,按下流程分别读A、B。

3.加法与减法运算令M S2 S1 S0(K15 K13~K11=0100),为算术加,FUN及总线单元显⽰A+B的结果令M S2 S1 S0(K15 K13~K11=0101),为算术减,FUN及总线单元显⽰A-B的结果。

逻辑运算1.运算源寄存器写流程通过“I/O输⼊输出单元”开关向寄存器A和B置数,具体操作步骤如下:2.运算源寄存器读流程关闭A、B写使能,令K17= K18=1,按下流程分别读A、B。

①若运算控制位设为(M S2 S1 S0=1111)则F=A,即A内容送到数据总线。

②若运算控制位设为(M S2 S1 S0=1000)则F=B,即B内容送到数据总线。

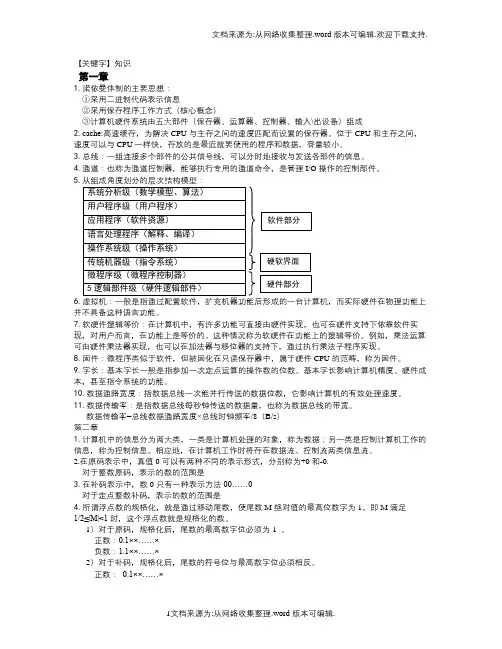

【关键字】知识第一章1.诺依曼体制的主要思想:①采用二进制代码表示信息②采用保存程序工作方式(核心概念)③计算机硬件系统由五大部件(保存器、运算器、控制器、输入\出设备)组成2.cache:高速缓存,为解决CPU 与主存之间的速度匹配而设置的保存器。

位于CPU 和主存之间,速度可以与CPU 一样快,存放的是最近就要使用的程序和数据,容量较小。

3.总线:一组连接多个部件的公共信号线,可以分时地接收与发送各部件的信息。

4.通道:也称为通道控制器,能够执行专用的通道命令,是管理I/O 操作的控制部件。

5.从组成角度划分的层次结构模型:并不具备这种语言功能。

7.软硬件逻辑等价:在计算机中,有许多功能可直接由硬件实现,也可在硬件支持下依靠软件实现,对用户而言,在功能上是等价的。

这种情况称为软硬件在功能上的逻辑等价。

例如,乘法运算可由硬件乘法器实现,也可以在加法器与移位器的支持下,通过执行乘法子程序实现。

8.固件:微程序类似于软件,但被固化在只读保存器中,属于硬件CPU 的范畴,称为固件。

9.字长:基本字长一般是指参加一次定点运算的操作数的位数。

基本字长影响计算机精度、硬件成本,甚至指令系统的功能。

10.数据通路宽度:指数据总线一次能并行传送的数据位数,它影响计算机的有效处理速度。

11.数据传输率:是指数据总线每秒钟传送的数据量,也称为数据总线的带宽。

数据传输率=总线数据通路宽度×总线时钟频率/8(B/s )第二章1.计算机中的信息分为两大类,一类是计算机处理的对象,称为数据;另一类是控制计算机工作的信息,称为控制信息。

相应地,在计算机工作时将存在数据流、控制流两类信息流。

2.在原码表示中,真值0可以有两种不同的表示形式,分别称为+0和-0.对于整数原码,表示的数的范围是3.在补码表示中,数0只有一种表示方法00 0对于定点整数补码,表示的数的范围是4.所谓浮点数的规格化,就是通过移动尾数,使尾数M 绝对值的最高位数字为1。

东北大学秦皇岛分校计算机与通信工程学院计算机组成原理课程设计专业名称计算机科学与技术班级学号学生姓名指导教师设计时间2014.12.22~2015.1.2课程设计任务书专业:计算机科学与技术学号:学生姓名(签名):设计题目:8位模型机设计-指令系统及通用寄存器设计一、设计实验条件综合楼808实验室二、设计任务及要求总的设计目标是:设计一个8 位的模型机,其组成为:总线结构:单总线,数据总线位数8位、地址总线8位;●存储器:内存容量64K*8bit●控制器:用硬联线控制器实现26位微操作控制信号●运算器:单累加器,实现加、减等8种操作外设:●输入:用开关输入二进制量●输出:7段数码管和LED显示指令系统规模:64 条指令,7种类型,5种寻址方式本组任务是:1.设计12、15、22、32号指令;2.模型机的通用寄存器R1设计;3.BCD编码器的设计。

三、设计报告的内容1.设计题目与设计任务(设计任务书)设计内容如下:1、指令系统设计:ADDC A, #II 将立即数II加入累加器A中带进位SUB A, EM 从A中减去存储器EM地址的值AND A, @R? 累加器A“与”间址存储器的值MOV A, #II 将立即数II送到累加器A中2、模型机硬件设计:通用寄存器R13、逻辑电路设计:BCD码编码器2.前言(绪论)(设计的目的、意义等)1.融会贯通计算机组成原理课程的内容,通过知识的综合运用,加深对计算机系统各个模块的工作原理及相互联系的认识;2.学习运用VHDL进行FPGA/CPLD设计的基本步骤和方法,熟悉EDA的设计、模拟调试工具的使用,体会FPGA/CPLD技术相对于传统开发技术的优点;3.培养科学研究的独立工作能力,取得工程设计与组装调试的实践经验。

3.设计主体(各部分设计内容、分析、结论等)【系统设计】1、模型机逻辑框图图1 模拟机整体逻辑框图图2 XCV200芯片引脚图3 CPU逻辑框图2、指令系统设计:ADDC A, #II 将立即数II加入累加器A中带进位助记符:ADDC A, #II类型:算数运算指令寻址方式:立即数寻址指令格式:第一字节001011XX第二字节立即数:SUB A, EM 从A中减去存储器EM地址的值助记符:SUB A, EM类型:算数运算指令寻址方式:存储器直接寻址指令格式:第一字节001110XX第二字节存储地址:AND A, @R? 累加器A“与”间址存储器的值助记符:AND A, @R?类型:算数运算指令寻址方式:寄存器间接寻址指令格式:第一字节010101XX:MOV A, #II 将立即数II送到累加器A中助记符:MOV A, #II类型:数据传送指令寻址方式:立即数寻址指令格式:第一字节011111XX第二字节立即数3、微操作控制信号:外部设备读信号,当给出了外设的地址后,输出此信号,从指定外设读数据。

控制器的工作原理控制器是指按照预定顺序改变主电路或控制电路的接线和改变电路中电阻值来控制电动机的启动、调速、制动和反向的主令装置。

由程序计数器、指令寄存器、指令译码器、时序产生器和操作控制器组成,它是发布命令的“决策机构”,即完成协调和指挥整个计算机系统的操作。

控制器分组合逻辑控制器和微程序控制器,两种控制器各有长处和短处。

组合逻辑控制器设计麻烦,结构复杂,一旦设计完成,就不能再修改或扩充,但它的速度快。

微程序控制器设计方便,结构简单,修改或扩充都方便,修改一条机器指令的功能,只需重编所对应的微程序;要增加一条机器指令,只需在控制存储器中增加一段微程序,但是,它是通过执行一段微程。

具体对比如下:组合逻辑控制器又称硬布线控制器,由逻辑电路构成,完全靠硬件来实现指令的功能。

电磁吸盘控制器:交流电压380V经变压器降压后,经过整流器整流变成110V 直流后经控制装置进入吸盘此时吸盘被充磁,退磁时通入反向电压线路,控制器达到退磁功能。

门禁控制器:门禁控制器工作在两种模式之下。

一种是巡检模式,另一种是识别模式。

在巡检模式下,控制器不断向读卡器发送查询代码,并接收读卡器的回复命令。

这种模式会一直保持下去,直至读卡器感应到卡片。

当读卡器感应到卡片后,读卡器对控制器的巡检命令产生不同的回复,在这个回复命令中,读卡器将读到的感应卡内码数据传送到门禁控制器,使门禁控制器进入到识别模式。

在门禁控制器的识别模式下,门禁控制器分析感应卡内码,同设备内存储的卡片数据进行比对,并实施后续动作。

门禁控制器完成接收数据的动作后,会发送命令回复读卡器,使读卡器恢复状态,同时,门禁控制器重新回到巡检模式。

上海质祈机电设备有限公司成立于2013年,位于上海市普陀区,专业从事于燃烧机及其配件,配件主要有油泵、电磁阀、控制器、风压开关、气压开关、过滤器、调压阀、伺服马达、检漏装置、点火变压器、点火棒、火焰探测器、电磁泵、执行器、加热棒。

主要品牌有冬斯(DUNGS)、西门子(SIEMENS)、桑泰克(suntec)、帕克(Parker)、考菲(COFI)、飞达(fida)、霍尼韦尔(Honeywell)等。

DJ-CPTH计算机组成原理实验系统实验指导阜阳师范学院计算机与信息学院2008年3月目录目录 (1)实验一认识实验装置 (2)实验二寄存器实验 (10)实验三运算器实验 (18)实验四数据输出和移位实验 (22)实验五存储器实验 (26)实验六uPC和PC 实验 (32)实验七微程序存储器uM实验 (37)实验八模型机综合实验一 (39)实验九模型机综合实验二 (46)实验十微程序设计实验 (55)实验十一扩展实验 (60)附录1:CPTH 集成开发环境使用 (63)附录2:指令/微指令表(insfile1.mic) (68)附录3:实验用芯片介绍 (79)实验一认识实验装置实验目的:了解实验仪的特点及组成;掌握实验仪键盘的使用。

实验器材:DJ-CPTH实验仪实验要求:1、认真填写预习报告,包括对实验仪器组成的理解、实验操作步骤等。

2、实验之后写出实验报告,包括实验过程中遇到的问题,解决方法,实验后的心得体会及对该次实验的建议与意见。

实验原理及步骤:一、DJ-CPTH特点1、采用总线结构总线结构的计算机具有结构清晰,扩展方便等优点。

DJ-CPTH实验系统使用三组总线即地址总线ABUS、数据总线DBUS、指令总线IBUS和控制信号,CPU、主存、外设和管理单片机等部件之间通过外部数据总线传输,CPU内部则通过内部数据总线传输信息。

各部件之间,通过三态缓冲器作接口连接,这样一方面增强总线驱动能力,另一方面在模型机停机时,三态门输出浮空,能保证不管模型机的CPU工作是否正常,管理单片机总能读/写主存或控存。

2、计算机功能模块化设计DJ-CPTH为实验者提供运算器模块ALU,众多寄存器模块(A,W,IA ,ST,MAR,R0…R3等),程序计数器模块PC,指令部件模块IR,主存模块EM,微程序控制模块〈控存〉uM,微地址计数器模块UPC,组合逻辑控制模块及I/O等控制模块。

各模块间的电源线、地线、地址总线和数据总线等已分别连通,模块内各芯片间数据通路也已连好,各模块的控制信号及必要的输出信号已被引出到主板插孔,供实验者按自己的设计进行连接。

定时控制器的逻辑电路设计可以基于数字逻辑门电路实现。

以下是一个简单的定时控制器逻辑电路设计示例,用于控制某个设备在特定时间内工作或停止:

1. 逻辑门选择

-使用集成电路中的逻辑门(如与门、或门、非门等)来设计定时控制器的逻辑电路。

-可根据具体需求选择合适的逻辑门进行组合。

2. 时钟信号输入

-设计一个时钟信号发生器或者使用外部时钟信号作为输入,用于控制定时器的计时和触发。

3. 定时器部分

-设计一个计时器部分,用于计时特定的时间间隔。

可以采用计数器或者其他形式的计时电路。

-当计时器达到设定的时间后,输出一个触发信号。

4. 控制逻辑

-设计控制逻辑部分,根据触发信号的输出状态来控制目标设备的工作状态。

-可以设计一个开关控制电路,使目标设备在触发信号有效时工作,

触发信号无效时停止工作。

5. 脉冲延时器

-可以设计脉冲延时器部分,用于延迟或者控制脉冲信号的传输,从而实现更灵活的定时控制功能。

6. 电源管理

-考虑定时控制器的电源管理问题,确保电路稳定可靠地工作。

7. 测试与调试

-设计完成后进行电路原理图绘制并进行仿真测试,验证电路设计的正确性和稳定性。

-在实际硬件上搭建电路,进行调试和优化,确保定时控制器功能正常。

以上是一个简单的定时控制器逻辑电路设计示例,实际设计中可能会涉及更复杂的功能和电路部分。

设计定时控制器需要充分考虑功能需求、稳定性和可靠性等因素,同时注重电路的优化和测试工作,确保设计的定时控制器符合预期的功能和性能要求。

JSSN 1 0o9-3044 Compu ̄rKnowledgeAnd Technology电脑知识与技术 Vo1.4,No.1,October 2008,PP.213—215

E—mail:kfyj@cccc.net.CI1 http://www.dnzs.net.en Tel:+86—55 l一5690963 5690964

通用逻辑控制器的设计 王妍萍.罗霄 (北京服装学院工业设计与信息工程系,北京100029) 摘要:该文介绍了一种以单片机为核心,C51编程语言为开发工具来构建一个能实现9种逻辑功能的通用逻辑控制器的设计过程, 该通用逻辑控制器能够代替定时器、继电器等设备,更经济、更快速、更灵活地解决简单西关量控制任务。程序按照状态变化进行设 计开发。目前该产品已投入批量生产,使用效果良好。 关键词:单片机;C51;逻辑控制;通用逻辑控制器 中图分类号:TP368 文献梧识码:A 文章编号:1oo9—3044(2008)28—0213—03

The Design of General Logic Controller WANG Yan—ping,LUO Xiao (Beijing Institute of ClotNng Technology,Beijing 100029,China) Abstract:In this paper,a design of general logic controller with basic logic funcdon by programming tool which base on C51 program— ruing language software and microcontroller hardware,are introduced.This logic control/er CaD replace Timer and Relay.They are easier, faster,and more convenient in resolving ordinary task of digital value contro1.Program was designed by state transform.It has been put into production in batches. Key words:microcontroller;C5 1;logic control;general logic controHer 通用逻辑控制器,又称为智能继电器。目前国外公司有相关产品,由于价格较高,功能复杂,在一些场合下并不适用。本次开发 的通用逻辑控制器,具有定时器、继电器、时钟和接触器所实现的功能,产品成本低,在小型电器系统里可以独立完成控制,也可作 为控制系统中的一部分,使得控制柜的体积变得更小,而且随时能够根据工艺要求扩展其功能。

第三章组合逻辑电路基本要求:熟练掌握组合逻辑电路的分析方法;掌握组合逻辑电路的设计方法;理解全加器、译码器、编码器、数据选择器、数据比较器的概念和功能,并掌握它们的分析与实现方法;了解组合逻辑电路中的险象本章主要内容:组合逻辑电路的分析方法和设计方法。

本章重点:组合逻辑电路的分析方法组合逻辑电路的设计方法常用逻辑部件的功能本章难点:组合逻辑电路的设计一、组合逻辑电路的特点若一个逻辑电路,在任一时刻的输出仅取决于该时刻输入变量取值组合,而与电路以前的状态无关,则电路称为组合逻辑电路(简称组合电路)。

可用一组逻辑函数描述。

组合电路根据输出变量分为单输出组合逻辑电路和多输出组合逻辑电路。

注意:1.电路中不存在输出端到输入端的反馈通路。

2.电路不包含记忆元件。

3.电路的输出状态只由输入状态决定。

二、组合逻辑电路的分析方法分析的含义:给出一个组合逻辑电路,分析它的逻辑功能。

分析的步骤: 1.根据给出的逻辑电路图,逐级推导,得到输出变量相对于输入变量的逻辑函数。

2.对逻辑函数化简。

3.由逻辑函数列出对应的真值表。

4.由真值表判断组合电路的逻辑功能。

三、组合电路的分析举例1、试分析图3-1所示的单输出组合逻辑电路的功能解:(1)由G1、G2、G3各个门电路的输入输出关系,推出整个电路的表达式:Z1=ABCF=Z1+Z2 (2)对该逻辑表达式进行化简:(3)根据化简后的函数表达式,列出真值表3-1。

(4)从真值表中可以看出:当A、B、C三个输入一致时(或者全为“0”、或者全为“1”),输出才为“1”,否则输出为“0”。

所以,这个组合逻辑电路具有检测“输入不一致”的功能,也称为“不一致电路”。

2.试分析图3-2所示的输出组合逻辑电路的功能解:(1)由G1、G2、G3、G4、G5各个门电路的输入、输出关系,推出整个组合逻辑电路的表达式:(2)对该逻辑表达式进行化简:(3)根据化简后的函数表达式,列出真值表3-2。

(4)若设A、B各为一位二进制加数,则从真值表中可以看出,S为两加数相加后的一位和、C为两加数相加后的进位值。

计组部分重要概念整理冯诺依曼计算机的特点:1计算机有运算器、存储器、控制器、输入设备和输出设备五大部件组成2指令和数据以同等地位存放于存储器内。

并可按地址访问。

3指令和数据均可用二进制表示4指令由操作码和地址吗组成。

操作码表示操作的性质、地址码表示操作数在存储器中的位置5指令在存储器中按顺序存放。

通常,指令时顺序执行的。

在特殊情况下,可根据运算结果或指定的条件来改变运算顺序。

6机器以运算器为中心。

输入输出设备和存储器之间的数据传送通过运算器完成。

典型的冯诺依曼计算机是以运算器为中心的,现代的计算机已转化为以存储器为中心的。

计算机硬件的主要技术指标:机器字长:寄存器的位数存储容量:存储单元个数*存储字长=MAR*MDR运算速度:主频MIPS(百万)时钟周期CPI存储器的层次结构主要体现在什么地方?为什么要分这些层次?1)存储器的层次结构主要体现在Cache—主存和主存—辅存这两个存储层次上。

2)Cache—主存层次主要解决CPU和主存速度不匹配的问题,在存储系统中主要对CPU访存起加速作用。

从CPU的角度看,该层次的速度接近于Cache,而容量和每位价格却接近于主存。

这就答案要点决了存储器的高速度和低成本之间的矛盾;主存—辅存层次主要解决存储系统的容量问题,在存储系统中主要起扩容作用。

从程序员的角度看,其所使用的存储器的容量和每位价格接近于辅存,而速度接近于主存。

该层次答案要点决了大容量和低成本之间的矛盾。

试比较静态RAM和动态RAM。

答案要点:1)静态RAM的特点:依靠双稳态触发器保存信息,不断电信息不丢失;功耗较大,集成度较低,速度快,每位价格高,适合于作Cache或存取速度要求较高的小容量主存。

2)动态RAM的特点:依靠电容存储电荷来保存信息,需刷新电路进行动态刷新;功耗较小,集成度高,每位价格较低,适合于作大容量主存。

什么叫刷新?为什么要刷新?说明刷新有几种方法。

说明动态RAM各种刷新方式的特点。

实验四微控制器实验一、实验目旳1.熟悉微控制器的的控制原理。

2.掌握微控制器的实现方法。

二、实验要求通过控制器实验,理解计算机内部工作过程,建立计算机整机工作概念。

三、控制器组成控制器是计算机的指挥和控制中心,由它把计算机的运算器、存储器、I/O设备等联系成一个有机的系统,并根据程序所特定的微指令序列对各部件的具体要求,适时地发出各种命令,控制计算机各部件有条不紊的进行工作。

如图4-1所示,本系统控制器由组合逻辑与存储逻辑集合组成。

两者按独立控制器的规范与标准设计,既可单独控制,亦可交替互补(混合)控制,在国内率先把PLA控制理念融入微控制器的设计与实现中。

图4-1控制器组成框图1.组合逻辑型如图2-4-13所示的PLD框为组合逻辑型控制器,由可编程器件XC9572独立组成,在器件编程环境的支撑下完成微操作控制信号的设计与下载。

以取得最高操作速度为设计目标,它的缺点是繁锁、杂乱、缺乏规律性,且不易修改和扩充,缺乏灵活性。

组合逻辑控制器实质上是一个组合逻辑电骆,它将一组输入逻辑信号转換成一组输出控制信号,可称为硬布线控制器。

2.存储逻辑型如图4-1所示的CM框为存储逻辑型微程序控制器,它是采用存储逻辑来实现的,也就是把微操作信号代码化,使每条机器指令转化成为一段微程序,存入控制存储器中,微操作控制信号由微指令产生。

微程序控制器的设计思想和组合逻辑的设计思想截然不同。

它具有设计规整,调试、维修以及更改、扩充指令方便的优点,易于实现自动化设计,已成为当前控制器的主流。

但是,由于它增加了一级控制存储器,所以指令的执行速度比组合逻辑控制器慢。

3. 组合逻辑与存储逻辑结型如图4-1所示,本系统控制器由组合逻辑与存储逻辑集合组成PLA 控制器,它是吸收前两种的设计思想来实现的。

PLA 控制器实际上也是一种组合逻辑控制器,但它又与常规的组合逻辑控制器的硬联结构不同,它是程序可编的,某一微操作控制信号由存储逻辑控制器产生。

内蒙古大学 《计算机组成原理》 实验设计报告

设计题目:组合逻辑控制器设计 班级:13软件二班 小组组长:张曦(0131124497) 小组成员:李聪、高浪、沈冲、王佳煜 、罗旭亮

指导老师:刘彩霞 一、实验设计目的: 设计一个指令格式如下图的组合逻辑控制器。

二、实验设计原理及思路: 1、cup数据通路图如下:

ALUACMM

ADD0ARDRIRPC

SBIB

GR(R0,R1)

操作码 8 9 7 0 0:CLA 寻址方式 寄存器编号 直接寻址地址 0:寄存器直接 0:R0 1:R1

1 2、指令微流程图如下: T0:PC-SB,SB-AR,RDT1:DR-SB,SB-IRT2:PC+1

IR(9)=0(CLA)IR(9)=1(ADD)

T0:0-ACIR(8)=1

(存储器直接寻址)

T0:(IR(0))-SB,SB-ALU.R,AC-ALU.LT1:ADD,ALU.O-AC

T0:IR(0-7)-SB,SB-AR,RD

T1:DR-SB,SB-ALU.R,AC-ALU.LT2:ADD,ALU.O-AC

IR(8)=0(寄存器直接寻址)

其中微命令如下: PC-SB DR-SB IR(0)-SB IR(0-7)-SB

SB-AR SB-IR SB-ALU.R

0-AC ALU.0-AC

AC-ALU.L PC+1 RD ADD 3、微命令编码设计 3 2 2 1 1 1 1

4、此地址部分设计: NAC字段:2位 00:顺序;01:无条件跳转;10:指令跳转;11:add寻址方式跳转 NA字段:4位

共9跳微指令所以NA占4位 5、控制存储器存储空间分配: 三、实验代码(C++): #include #include using namespace std;

int findchar(char ch,char str[],int n) { int i=0; while(str[i]!=ch&&ii++; if(i==n) {i=1;return 1;} return 0; } void caozuo(int wcx[10][17],int zl[]) { int i=0; for(i=0;i<17;i++) cout if(zl[1]==1) { for(i=0;i<17;i++) cout for(i=0;i<17;i++) cout } AC[0]=cn; return; } void ADD_2(int AC[],int R0[],int n=0) { int i; for(i=0;i<8;i++) { R0[i]=AC[i+1]; } return; } main() { int wcx[10][17]= { 0,0,1,0,1,0,0,0,0,1,0,0,0,-1,-1,-1,-1, 0,1,0,1,0,0,0,0,0,0,0,0,0,-1,-1,-1,-1, 0,0,0,0,0,0,0,0,1,0,0,1,0,0,1,0,0, //取指 0,0,0,0,0,0,1,0,0,0,0,0,1,0,0,0,0, //CLR 0,0,0,0,0,0,0,0,0,0,0,1,1,0,1,1,1, //ADD寻址 0,1,1,1,1,0,0,1,0,0,0,0,0,-1,-1,-1,-1,//ADD寄存器 0,0,0,0,0,1,0,0,0,0,1,0,1,0,0,0,0, 1,0,0,0,1,0,0,0,0,1,0,0,1,0,1,1,1,//ADD存储器 0,1,0,1,1,0,0,1,0,0,0,0,1,1,0,0,0, 0,0,0,0,0,1,0,0,0,0,1,0,1,0,0,0,0 }; char ch[1000]; char s[3][1000]; const char *d = " ,"; char *p; while(1) { int i=0,n=0; int R0[8]={0},R1[8]={0},AC[9]={0}; int x[100],e; int zl[10]={0}; int zl2[10]={0}; cout<<"请输入命令:" } else { if(findchar(' ',ch,strlen(ch))!=0) n=1; if(findchar(',',ch,strlen(ch))!=0) n=2; else n=3; p = strtok(ch,d); for(i=0;i{ strcpy(s[i],p); p=strtok(NULL,d); } e=n; /////////////////////////////////////////////////////////////// while(1) { if(strcmp(s[0],"ADD")==0||strcmp(s[0],"add")==0) { zl[0]=1; zl2[0]=1; } if(e==1) break; if(e==2) { if(strcmp(s[1],"r0")==0||strcmp(s[1],"R0")==0) { zl[1]=0; zl[9]=0; ADD_1(R0,AC); } else if(strcmp(s[1],"r1")==0||strcmp(s[1],"R1")==0) { zl[1]=0; zl[9]=1; ADD_1(R1,AC); } else { zl[1]=1; for(i=0;i{ x[i]=int(s[1][i])-48; for(int j=2;j<10;j++) zl[j]=1; }