实验9 数据存储器扩展实验

一、实验目的

1、掌握外部总线扩展技术;

2、了解数据存储器的接口特点;

3、熟悉外部数据存储器的扩展方法和使用特性。

二、实验说明

实验箱上MCS-51 单片机扩展外部存储器的原理电路如图3.2.1 所示,这也是MCS-51 单片机扩展外部存储器的一般方法。图3.2.1 中U2 为74LS573 锁存器,由于MCS51 的P0 口在对外部扩展总线操作时为数据和地址复用的,先输出低8 位地址,后用作数据总线。单片机利用地址锁存使能信号ALE 控制74LS573锁存先行到达的低8 位地址信号。

U4 可以为62C64(8KB)或62C128(16KB)、62C256(32KB)型数据存储器,这几种RAM 器件的引脚都是向下兼容的,当插入较小容量器件时,高位地址没有作用。实验箱通用板上实际插入的是62C256 型器件,扩展32KB 数据存储器。

U4的片选信号“RCS”可由地址译码器件U5提供,其电路连接原理见图1.3.5。根据自己的设计,选择对应的地址信号作为片选信号。当实际使用的地址不多时,也可以直接用单片机的最高位地址信号A15(P2.7)作为片选信号,则最高位地址信号A15为0时,62256片选信号有效,对应的内部存储空间地址范围为0000H~7FFFH。

三、实验任务与要求

1、将Keil 软件设置成硬件仿真模式(联机仿真);

2、自行编写对外部数据存储器读写指令,观察写入的数值与读出的数值是否相符;

四、实验程序及结果

实验代码如下:

ORG 0000H

MOV DPTR, #7000H

MOV A,#11H

MOVX @DPTR,A

NOP

MOV A,00H

MOVX A,@DPTR

END

分步运行时,累加器A的值依次变化为:0a=0x0000H,0a=0x0011H,0a=0x0000H,0a=0x0011H。可见外部存储器扩展正常。

五、思考题:

1、请说明单片机ALE信号的作用。

答:ALE信号为地址锁存使能信号,当ALE为高电平时,先行到达的低8位地址信

号被74LS573锁存,这时P0可以发出和接受8位数据,即达到P0口的地址和数据

总线的复用。

实验14 指示灯的外部中断控制

一、实验目的

1、了解MCS51 单片机外部中断有关寄存器的作用;

2、掌握外部中断的编程方法;

3、熟悉外部中断与基本I/O 功能的综合应用方法。

二、实验说明

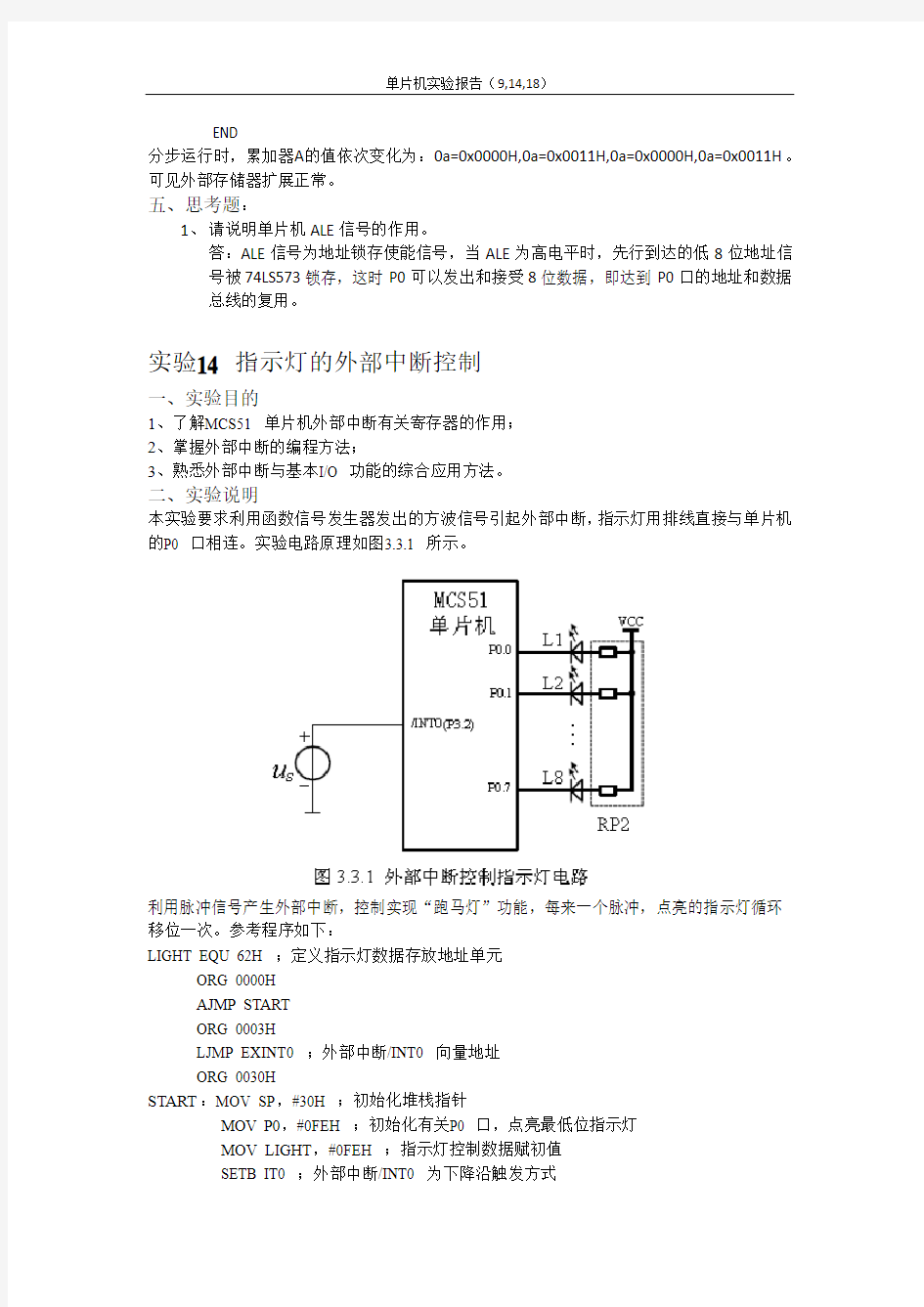

本实验要求利用函数信号发生器发出的方波信号引起外部中断,指示灯用排线直接与单片机的P0 口相连。实验电路原理如图3.3.1 所示。

利用脉冲信号产生外部中断,控制实现“跑马灯”功能,每来一个脉冲,点亮的指示灯循环移位一次。参考程序如下:

LIGHT EQU 62H ;定义指示灯数据存放地址单元

ORG 0000H

AJMP START

ORG 0003H

LJMP EXINT0 ;外部中断/INT0 向量地址

ORG 0030H

START:MOV SP,#30H ;初始化堆栈指针

MOV P0,#0FEH ;初始化有关P0 口,点亮最低位指示灯

MOV LIGHT,#0FEH ;指示灯控制数据赋初值

SETB IT0 ;外部中断/INT0 为下降沿触发方式

SETB EX0 ;允许外部中断/INT0 产生中断

SETB EA ;开总中断

MAIN:AJMP $ ;死循环,动态听见

;外部中断/INT0 服务子程序

EXINT0:PUSH ACC ;保护现场

MOV A,LIGHT ;去指示灯点亮数据

RL A ;循环左移一位

MOV LIGHT,A ;移位后写回

MOV P0,A ;同时输出到P0 口,改变指示灯点亮状态

POP ACC ;恢复现场

RETI ;中断返回

三、实验任务与要求

1、读懂参考程序,理解外部中断的实现方法;

2、要求来一个脉冲时,指示灯全亮,下一个脉冲时指示灯全熄,如此交替循环。请编程实现,并调试运行。

四、实验流程图与结果

程序运行流程图:

程序如下:

LIGHT EQU 62H

ORG 0000H

AJMP START

ORG 0003H

LJMP EXINT0

ORG 0030H

START:MOV SP,#30H

MOV P0,#0FEH

MOV LIGHT,#00H

SETB IT0

SETB EX0

SETB EA

MAIN: AJMP $

EXINT0:PUSH ACC

MOV A,LIGHT

CPL A

MOV LIGHT,A

MOV P0,A

POP ACC

RETI

END

运行时,八个指示灯交替循环地点亮和熄灭。

四、思考题

1、外部中断有哪几种触发方式?为什么实验参考程序不用电平触发方式?

答:外部中断方式有两种:上升沿触发和电平触发方式。由于电平触发时,系统不能自动清除IE1标志的数据,这样会导致中断状态返回时,电平仍然未清除,从而再次触发中断,导致系统错误。

2、控制外部中断有寄存器的哪些位?各位分别起什么作用?

答:控制中断的寄存器有中断允许控制器和中断优先级控制器,其包含的位级作用如下:

中断允许控制器:IE

EA(IE.7):总允许位

(IE.6:保留)

ET2(IE.5):定时器2中断允许位(只适用于8052及其增强型)

ES(IE.4):串行中断允许位

ET1(IE.3):定时器1中断允许位

EX1(IE.2):外部中断1允许位

ET0(IE.1):定时器0中断允许位

EX0(IE.0):外部中断0允许位

中断优先级控制器:IP

(IP.7:保留)

(IP.6:保留)

PT2(IP.5):若=1,定时器2中断设为高优先级(只适用于8052及其增强型)

PS(IP.4):若=1,串行中断设为高优先级

PT1(IP.3):若=1,定时器1中断设为高优先级

PX1(IP.2):若=1,外部中断1设为高优先级

PT0(IP.1):若=1,定时器0中断设为高优先级

PX0(IP.0):若=1,外部中断0设为高优先级

实验18 定时器控制继电器

一、实验目的

1、了解继电器的原理和作用;

2、掌握定时器中断的编程方法;

3、学习利用定时器中断控制继电器的基本方法。

二、实验说明

继电器是电气测量和控制电路中常见的执行元件。利用单片机控制继电器操作的电路原理如图3.4.1 所示。

ULN2003 为继电器驱动器件,每路输出端可以驱动500mA 电流,继电器线圈的工作电流约为10mA。图3.4.1 中左侧的大虚线框内为ULN2003 的内部电路,在输出引脚和电源之间带有一个续流二极管。

图3.4.1 右侧小虚线框内为继电器内部电路。将继电器的线圈一端连接到电源VCC,另一端连接到ULN2003 的输出端。

单片机的P1.7 接到ULN2003 的输入端,利用单片机的P1.7 控制继电器动作。当P1.7 输出高电平时,ULN2003 的输出为低电平,从而继电器线圈得电,输出开关被电磁力吸合。当P1.7 输出低电平时,ULN2003 的输出为高电平,继电器线圈没有电流流过,输出开关被弹簧弹开。

继电器输出开关,工作电压和电流依继电器的型号不同而各异,一般都为交流220V/5A 以上,可用于控制操作各种电器设备。实验箱上继电器的线圈与电源、ULN2003 之间的连接电路,在印刷电路板内部已经连接好,见图1.3.11 所示。

实验时继电器用于控制一个LED 指示灯,图3.4.1 中的LED 指示灯电路部分,需自行连接。

定时器T1 中断用于定时控制继电器,每隔20 秒改变一次继电器状态。LED 数码管显示器以秒为单位显示时间。

基于上述要求编写的实验参考程序如下:

;参考程序

TIMC0 EQU 70H

TIMC1 EQU 71H

TIMC2 EQU 72H

TIMC3 EQU 73H

ORG 0000H

AJMP START

ORG 001BH

LJMP TIM1

ORG 0030H

START:MOV SP,#30H

MOV TMOD,#20H ;T1 工作于定时方式2

MOV TL1,#6

MOV TH1,#6 ;装载定时初值

SETB ET1 ;允许T1 中断

SETB TR1 ;启动T1

SETB EA ;开总中断

MAIN:MOV A,TIMC0

CJNE A,#40,MAIN1 ;不到10ms 跳转

MOV TIMC0,#0 ;清零250μs 计数器

INC TIMC1 ;10ms 计数器增1

MOV A,TIMC1

CJNE A,#100,MAIN1 ;***

;到1s 则跳转

MOV TIMC1,#0 ;清零10ms 计数器

INC TIMC2 ;s 计数器增1

MOV A,TIMC2

CJNE A,#20,MAIN1 ;不到20s 则跳转

MOV TIMC2,#0

CPL P1.7 ;改变继电器状态

MAIN1:AJMP MAIN

;**************************

;定时器T1 中断服务子程序

;**************************

TIM1:PUSH PSW

PUSH ACC ;保护现场

INC TIMC0

POP ACC ;恢复现场

POP PSW

RETI

三、实验任务与要求

1、自行设计LED 数码管显示电路,并搭接显示和继电器控制电路,完成实验,验证参考程序;

2、修改实验参考程序,让LED 指示灯每2 分钟改变一次点亮状态,LED 数码管分别显示分、秒;

四、实验流程图与运行程序

TIMC0 EQU 70H

TIMC1 EQU 71H

TIMC2 EQU 72H

TIMC3 EQU 73H

TIMC4 EQU 74H

D_DAT0 EQU 6AH

D_DAT1 EQU 6BH

D_DAT2 EQU 6CH

D_DAT3 EQU 6DH

D_DAT4 EQU 6EH

D_DAT5 EQU 6FH

ORG 0000H

AJMP START

ORG 001BH

LJMP TIM1

ORG 0030H

START: MOV D_DAT0,#0 MOV D_DAT1,#0

MOV D_DAT2,#0

MOV D_DAT3,#0

MOV TIMC0,#0

MOV TIMC1,#0

MOV TIMC2,#0

MOV TIMC3,#0

MOV TIMC4,#0

MOV SP,#30H

MOV TMOD,#20H

MOV TL1,#6

MOV TH1,#6

SETB ET1

SETB TR1

SETB EA

MOV R0,#D_DAT0

MOV R1,#01H

MAIN:MOV A,TIMC0 CJNE A,#40,MAIN1 MOV TIMC0,#0

INC TIMC1

MOV A,TIMC1

CJNE A,#100,MAIN1 MOV TIMC1,#0

INC TIMC2

LCALL HTD

MOV A,TIMC2

CJNE A,#60,MAIN1 INC TIMC3

INC TIMC4

LCALL HTD1

MOV TIMC2,#0

MOV A,TIMC4

CJNE A,#2,MAIN1

CPL P1.7

MOV TIMC4,#0

MAIN1: AJMP MAIN

TIM1: PUSH PSW

PUSH ACC

LCALL DISP

INC TIMC0

POP ACC

POP PSW

RETI

DISP: MOV A,R1

MOV D_DAT3,#10

MOV D_DAT2,#10

MOV P0,A

SETB P1.2

NOP

CLR P1.2

MOV A,@R0

MOV DPTR,#DISPD

MOVC A,@A+DPTR

MOV P0,A

SETB P1.1

NOP

CLR P1.1

INC R0

MOV A,R1

CLR C

RLC A

MOV R1,A

CJNE R1,#40H,DISP1

MOV R0,#D_DAT0

MOV R1,#1

DISP1: NOP

RET

DISPD: DB 3FH,06H,5BH,4FH,66H,6DH,7DH,07H,7FH,6FH,0 HTD: MOV D_DAT4,#00H

MOV D_DAT5,#00H

CLR C

MOV A,TIMC2

MOV B,#10

DIV AB

MOV D_DAT4,A

MOV D_DAT5,B ;

RETI

HTD1: MOV D_DAT0,#00H

MOV D_DAT1,#00H

CLR C

MOV A,TIMC3

MOV B,#10

DIV AB

MOV D_DAT0,A

MOV D_DAT1,B ;

RETI

END

程序流程图:判断:TIMC0=40?

判断:TIMC0=40?

试验程序运行时,数码管显示呈现00(分钟) 00(秒钟)的跳转,并且在间隔两分钟时,LED的状态发生改变。

四、思考题

1、现有一台220V/1000W 的电炉,能否用实验箱上的继电器控制?

答:继电器的输出开关的工作电压和电流为220V/5A以上,故而可以对220V/1000W的电炉实现控制。

福建工程学院软件学院 题目:51开发洗衣机 班级:物联网工程1202 成员: 座号:04 28 指导老师: 日期:年月日课设报告

目录 1摘要 (1) 2.设计需求 (1) 2.1功能需求 (1) 2.1.1 基本功能 (1) 2.1.2扩展功能 (1) 2.2 设计要求 (2) 2.2.1 单片机芯片部件功能 (2) 2.2.2 LCD数码显示管部件功能 (2) 2.2.3 按键部件功能 (2) 2.2.4 蜂鸣器部件功能 (2) 3硬件设计及描述 (2) 3.1总体描述 (2) 3.2系统总体框图 (3) 3.3Proteus电路图 (3) 3.4各部分硬件介绍 (4) 3.4.1晶振Protues仿真 (4) 3.4.2LCDProtues仿真 (5) 3.4.3 按键Protues仿真 (5) 3.4.4上拉电阻Protues仿真 (6) 3.4.5C51芯片Protues仿真 (6) 3.4.6上电复位电路Protues仿真 (8) 3.4.7蜂鸣器Protues仿真 (9) 4 软件设计流程及描述 (10) 4.1程序流程图 (10) 4.2函数模块及功能 (10) 5功能实现 (11) 5.1程序烧入上电调试 (11) 5.2时间递增跳变 (12) 5.3比分更变 (13) 5.4比赛得分复位 (14) 5.5比赛时间复位 (14) 6 心得体会 (15) 7源程序代码: (16)

1摘要 是为了方便足球比赛时计时与计分及时与准确公开而引申出的实用产品。在此设计中接入了一个1602液晶显示屏,第一行用来记录赛程的时间,第二行用于显示比赛的得分情况。赛程计时用倒计时来计时。在比赛结束时按下相应按键蜂鸣器会响起,提醒比赛时间结束。 这次试验运用C语言进行编程,编程后利用Keil uVision来进行编译,再生成.hex文件装入芯片中,采用Proteus软件来仿真,检验功能是否能够正常实现,最后利用单片机MCS-51实机来实现功能。 本设计以AT89S51单片机作为核心,综合应用单片机定时器、中断、LCD1602 液晶显示等知识,设计一款单片机和简单外设控制的足球计分器应用,同时显示当前的比赛进行时间,比赛队伍,比分状况。 2.设计需求 2.1功能需求 2.1.1 基本功能 (1)屏上显示比赛已运行时间 (2)屏上显示A队和B队的得分 (3)屏上显示上下半场(H-L) (4)通过按键控制比分的增减 2.1.2扩展功能 (1)按键实现比赛场次的更换 (2)按键实现比赛计时的复位 (3)按键实现比赛比分的复位 (4)在比赛结束时,蜂鸣器在主裁判的控制下响起

静态存储器扩展实验报告告圳大学实验报深

微机原理与接口技术 课程名称: 静态存储器扩展实验实验项目名称: 信息工程学院学院: 专业:电子信息工程

指导教师:周建华 32012130334 学号:班级:电子洪燕报告人:班 2014/5/21 实验时间: 实验报告提交时间:2014/5/26 教务部制. 一.实验目的与要求: 1. 了解存储器扩展的方法和存储器的读/写。 2. 掌握CPU对16位存储器的访问方法。

二.实验设备 PC机一台,TD-PITE实验装置或TD-PITC实验装置一套,示波器一台。 三.实验原理VCC28A141WE27A122A1326A73A8254A6存储器是用来存储信息的A924A55A1123A46OE22A3762256A10218A2CS209A1部件,是计算机的重要组成部D719A010D618D011D517D112D416D213D315GND14管组成的是由MOS分,静态RAM触发器电路,每个触发器可以存放1位

信息。只要不掉电,所储存的信息就不会丢失。因此,静态RAM工作稳定,不要外加刷新电路,使用方便。 但一般SRAM 的每一个触发器是由6个晶体管组成,SRAM 芯片的集成度不会太高,目前较常用的有6116(2K×8位),图4.1 62256引脚图6268位)622532位。本验平台上选. 用的是62256,两片组成32K×16位的形式,共64K字节。 62256的外部引脚图如图4.1所示。 本系统采用准32位CPU,具有16位外部

数据总线,即D0、D1、…、D15,地址总线为BHE#(#表示该信号低电平有效)、BLE #、A1、A2、…、A20。存储器分为奇体和偶体,分别由字节允许线BHE#和BLE#选通。 存储器中,从偶地址开始存放的字称为规则字,从奇地址开始存放的字称为非规则字。处理器访问规则字只需要一个时钟周期,BHE#和BLE#同时有效,从而同时选通存储器奇体和偶体。处理器访问非规则字却需要

计算机原理与设计 实验报告 实验二存储器实验 :XXX 学号:2013551728

班级:13级软件工程2班 实验日期:2014年10 月29 日 1.FPGA中ROM定制与读出实验 一.实验目的 1、掌握FPGA中ROM的设置,作为只读存储器ROM的工作特性和配置方法。 2、用文本编辑器编辑mif文件配置ROM,学习将程序代码以mif格式文件加载于ROM中; 3、在初始化存储器编辑窗口编辑mif文件配置ROM; 4、验证FPGA中ROM的功能。 二.实验原理 ALTERA的FPGA中有许多可调用的模块库,可构成如rom、ram、fifo等存储器结构。CPU 中的重要部件,如RAM、ROM可直接调用他们构成,因此在FPGA中利用嵌入式阵列块EAB 可以构成各种结构的存储器,ROM是其中的一种。ROM有5组信号:地址信号address[ ]、数据信号q[ ]、时钟信号inclock、outclock、允许信号memenable,其参数都是可以设定的。由于ROM是只读存储器,所以它的数据口是单向的输出端口,ROM中的数据是在对FPGA 现场配置时,通过配置文件一起写入存储单元的。图2-1-1中的ROM有3组信号:inclk——输入时钟脉冲;instruction[31..0]——lpm_ROM的32位数据输出端;a[4..0]——lpm_ROM的5位读出地址。 实验中主要应掌握以下三方面的内容: (1)ROM的参数设置; (2)ROM中数据的写入,即FILE初始化文件的编写;

(3)ROM的实际应用,在GW48_CP+实验台上的调试方法。 三.实验步骤 (1)新建工程。工程名是scinstmem.qpf。 (2)用初始化存储器编辑窗口编辑ROM配置文件(文件名.mif)。这里预先给出后面将要用到的指令存储器初始化文件:scinstmem.mif 。如下图,scinstmem.mif中的数据是机器指令代码。 scinstmem.mif中的数据 (3)模块设计。用图形编辑,使用工具Mega Wizard Plug-In Manager,定制指令存储器rom 宏功能块。设置地址总线宽度address[]和数据总线宽度q[],分别为5位和32位,并添加输入输出引脚,如图设置和连接。 ROM的结构图 在设置rom数据参数选择项file的对应窗口中(下图),用键盘输入ROM配置文件的路径(scinstmem.mif),然后设置在系统ROM/RAM读写允许,以便能对FPGA中的ROM在系统读写。

计算机科学与技术系 实验报告 专业名称计算机科学与技术 课程名称计算机组成与结构 项目名称静态随机存储器实验 班级 学号 姓名 同组人员无 实验日期 2015-10-24

一、实验目的与要求 掌握静态随机存储器RAM 工作特性及数据的读写方法 二、实验逻辑原理图与分析 2.1 实验逻辑原理图及分析 实验所用的静态存储器由一片6116(2K ×8bit)构成(位于MEM 单元),如下 图所示。6116有三个控制线:CS(片选线)、OE(读线)、WE(写线),当片选有效(CS=0)时,OE=0时进行读操作,WE=0时进行写操作,本实验将CS 常接地线。 由于存储器(MEM)最终是要挂接到CPU 上,所以其还需要一个读写控制逻辑,使得CPU 能控制MEM 的读写,实验中的读写控制逻辑如下图所示,由于T3的参与,可以保证MEM 的写脉宽与T3一致,T3由时序单元的TS3给出。IOM 用来选择是对I/O 还是对MEM 进行读写操作,RD=1时为读,WR=1时为写。 XMRD XIOR XIOW XMWR RD IOM WE T3 读写控制逻辑 实验原理图如下如所示,存储器数据线接至数据总线,数据总线上接有8 个LED 灯显示D7…D0的内容。地址线接至地址总线,地址总线上接有8个LED 灯显示A7…A0的内容,地址由地址锁存器(74LS273,位于PC&AR 单元)给出。数据开关(位于IN 单元)经一个三态门(74LS245)连至数据总线,分时给出地址和数据。地址寄存器为8位,接入6116的地址A7…A0,6116的高三位地址A10…A8接地,所以其实际容量为256字节。

实验十四存储器扩展机读写实验 一、实验目的 (1)通过阅读并测试示例程序,完成程序设计题,熟悉静态RAM的扩展方法。 (2)了解8086/8088与存储器的连接,掌握扩展存储器的读写方法。 二、实验内容 1.实验原理(62256RAM介绍) 62256是32*8的静态存储器,管脚如图所示。其中:A0~A14为地址线,DB0~DB7为数据线,/cs为存储器的片选,/OE为存储器数据输出选通信号,/WE为数据写入存储器信号。62256工作方式如下图。 /CS /WE /OE 方式DB-~DB7 H X X 未选中高阻 L H H 读写禁止高阻 L L H 写IN L H L 读OUT 2.实验内容 设计扩展存储电器的硬件连接图并编制程序,讲字符A~Z循环存入62256扩展RAM 中,让后再检查扩展存储器中的内容。 三、程序设计 编写升序,将4KB扩展存储器交替写入55H和0AAH。 程序如下: RAMADDR EQU 0000H RAMOFF EQU 9000H COUNT EQU 800H CODE SEGMENT ASSUME CS:CODE START: PROC NEAR MOV AX,RAMADDR MOV DS,AX MOV BX,RAMOFF MOV CX,COUNT MOV DL,55h MOV AX ,0AAH REP: MOV [BX],DL INC BX MOV [BX],AX INC BX LOOP REP JMP $ CODE ENDS END START 四、实验结果 通过在软件上调试,运行时能够看到内存地址的改变,证明此扩展的程序成功实现了。 五、实验心得

本科生实验报告 实验课程单片微机原理与应用 学院名称ZZZZZ学院 专业名称电气工程及其自动化 学生姓名ZZZZ 学生学号ZZZZZ 指导教师ZZZ 实验地点6c902 实验成绩 二〇一六年三月二〇一六年五月

实验一单片机集成开发环境应用一实验目的 熟悉单片机集成开发软件(Keil); 掌握单片机实验板的使用; 掌握单片机P1口使用; 二实验内容 1、集成开发环境Keil介绍及开发流程 KEIL uVISION4是美国Keil Software公司出品的51系列兼容单片机C语言软件开发系统,是众多单片机开发软件之一,它支持众多不同公司的MCS51架构的芯片,它集编辑,编译,仿真等于一体,同时还支持,PLM(产品全生命周期管理),汇编和C语言的程序设计,它的界面和常用的微软VC++的界面相似,界面友好,易学易用,在调试程序,软件仿真方面也有很强大的功能。 以上简单介绍了KEIL51软件,要使用KEIL51软件,必需先要安装它。KEIL51是一个商业的软件,对于我们这些普通爱好者可以到KEIL中国代理周立功公司的网站上下载一份能编译2K的DEMO版软件,基本可以满足一般的个人学习和小型应用的开发。 安装好后,让我们一起来建立一个小程序项目吧。即使你手中还没有一块实验板,甚至没有一块单片机,不过没有关系我们可以通过KEIL软件仿真看到程序运行的结果。 首先当然是运行KEIL51软件。运行几秒后,出现如图1-1的屏幕。

图1-1 2、建立第一个项目 点击工程菜单,选择弹出的下拉式菜单中的NewuVision Project,如图1-2。接着弹出一个标准Windows 文件对话窗口,如图1-3。在“文件名”中输入您的第一个C 程序项目名称,“保存”文件。这是KEIL uVision4项目文件,以后我们可以直接点击此文件以打开先前做的项目。 图1-2 New Project菜单

操作系统实验报告 存储器管理 学院电信学院 专业计算机科学与技术 班级 14级计科一班 实验题目动态分区分配 实验组别第三组 指导老师曹华

一、实验目的 了解动态分区分配方式中使用的数据结构和分配算法,并进一步加深对动态分区存储管理方式及其实现过程的理解。 二、实验内容 用C语言分别实现采用首次适应算法和最佳适应算法的动态分区分配过程alloc()和回收过程free()。其中,空闲分区通过分区链来管理,在进行内存分配时,系统优先使用空闲区低端的空间。 请分别用首次适应算法和最佳适应算法进行内存块的分配和回收,要求每次分配和回收后显示出空闲内存分区链的情况。 三、实验主要仪器设备 软件环境:VC++6编程环境 四、实验原理及设计方案 1.实验原理: 可变分区调度算法有:最先适应分配算法,循环首次适应算法,最佳适应算法,最坏适应算法。 首次适应算法(First-fit):当要分配内存空间时,就查表,在各空闲区中查找满足大小要求的可用块。只要找到第一个足以满足要求的空闲块就停止查找,并把它分配出去; 如果该空闲空间与所需空间大小一样,则从空闲表中取消该项;如果还有剩余,则余下的部分仍留在空闲表中,但应修改区分大小和分区始址。 用户提出内存空间的申请:系统根据申请者的要求,按照一定的分配策略分析内存空间的使用情况,找出能满足请求的空闲区,分给申请者;当程序执行完毕或主动归还内存资源时,系统要收回它所占用的内存空间或它归还的部分内存空间。 最佳适应算法(Best-fit):当要分配内存空间时,就查找空闲表中满足要求的空闲块,并使得剩余块是最小的。然后把它分配出去,若大小恰好合适,则直按分配;若有剩余块,则仍保留该余下的空闲分区,并修改分区大小的起始地址。 内存回收:将释放作业所在内存块的状态改为空闲状态,删除其作业名,设置为空,并判断该空闲块是否与其他空闲块相连,若释放的内存空间与空闲块相连时,则合并为同一个空闲块,同时修改分区大小及起始地址。 每当一个进程被创建时,内存分配程序首先要查找空闲内存分区链,从中寻找一个合适的空闲块进行划分,并修改空闲内存分区链,系统根据回收区的首址,从空闲区链中找到相应的插入点,此时出现如下四种情况: (1)回收区与插入点的前一个空闲区F1相邻接,此时可将回收区直接与F1合并,并修改F1的大小; (2)回收区与插入点的后一个空闲分区F2相邻接,此时可将回收区直接与F2合并,并用回收区的首址作为新空闲区的首址,大小为二者之和; (3)回收区同时与插入点的前后两个空闲分区邻接,此时需将三者合并; (4)回收区不与任何一个空闲区邻接,此时应建一新的表项 2.主要数据结构的说明 定义一个空闲区说明表结构

实验一:扩展存储器读写实验 一.实验要求 编制简单程序,对实验板上提供的外部存贮器(62256)进行读写操作。 二.实验目的 1.学习片外存储器扩展方法。 2.学习数据存储器不同的读写方法。 三.实验电路及连线 将P1.0接至L1。CS256连GND孔。 四.实验说明 1.单片机系统中,对片外存贮器的读写操作是最基本的操作。用户藉此来熟悉MCS51单片机编程的基本规则、基本指令的使用和使用本仿真实验系统调试程序的方法。 用户编程可以参考示例程序和流程框图。本示例程序中对片外存贮器中一固定地址单元进行读写操作,并比较读写结果是否一致。不一致则说明读写操作不可靠或该存储器单元不可靠,程序转入出错处理代码段(本示例程序通过熄灭一个发光二极管来表示出错)。读写数据的选用,本例采用的是55(0101,0101)与AA(1010,1010)。一般采用这两个数据的读写操作就可查出数据总线的短路、断路等,在实际调试用户电路时非常有效。 用户调试该程序时,可以灵活使用单步、断点和变量观察等方法,来观察程序执行的流程和各中间变量的值。 2.在I状态下执行MEM1程序,对实验机数据进行读写,若L1灯亮说明RAM读

写正常。 3.也可进入LCA51的调试工具菜单中的对话窗口,用监控命令方式读写RAM,在I状态执行SX0000↓ 55,SPACE,屏幕上应显示55,再键入AA,SPACE,屏幕上也应显示AA,以上过程执行效果与编程执行效果完全相同。 注:SX是实验机对外部数据空间读写命令。 4.本例中,62256片选接地时,存储器空间为0000~7FFFH。 五.实验程序框图 实验示例程序流程框图如下: 六.实验源程序: ORG 0000H LJMP START ORG 0040H START:

《单片机与接口技术》实验报告 信息工程学院 2016年9月

辽东学院信息技术学院 《单片机与接口技术》实验报告 姓名:王瑛 学号: 0913140319 班级: B1403 专业:网络工程 层次:本科 2016年9月

目录 实验题目:实验环境的初识、使用及调试方法(第一章) 实验题目:单片机工程初步实验(第二章) 实验题目:基本指令实验(第三章)4 实验题目:定时器/计数器实验(第五章)4 实验题目:中断实验(第六章)4 实验题目:输入接口实验(第八章)4 实验题目:I/O口扩展实验(第九章)4 实验题目:串行通信实验(第十一章)4 实验题目:A/D,D/A转换实验(第十七章)4

实验题目:实验环境的初识、使用及调试方法实验 实验类型:验证性实验课时: 1 时间:2016年10月24日 一、实验内容和要求 了解单片机的基础知识 了解51单片机的组成和工作方法 掌握项目工程的建立、编辑、编译和下载的过程方法 熟练单片机开发调试工具和方法 二、实验结果及分析 单片机最小系统的构成: Keil集成开发环境:

STC-ISP:

实验题目:单片机工程初步实验 实验类型:验证性实验课时: 1 时间:2016 年10 月24 日一、实验内容和要求 点亮一个LED小灯 程序下载到单片机中 二、实验结果及分析 1、点亮一个LED小灯 点亮LED小灯的程序: #include

信息与管理科学学院计算机科学与技术 实验报告 课程名称:计算机组成原理 实验名称:存储器读写和总线控制实验 姓名:班级:指导教师:学号: 实验室:组成原理实验室 日期: 2013-11-22

一、实验目的 1、掌握半导体静态随机存储器RAM的特性和使用方法。 2、掌握地址和数据在计算机总线的传送关系。 3、了解运算器和存储器如何协同工作。 二、实验环境 EL-JY-II型计算机组成原理实验系统一套,排线若干。 三、实验内容 学习静态RAM的存储方式,往RAM的任意地址里存放数据,然后读出并检查结果是否正确。 四、实验操作过程 开关控制操作方式实验 注:为了避免总线冲突,首先将控制开关电路的所有开关拨到输出高电平“1”状态,所有对应的指示灯亮。 本实验中所有控制开关拨动,相应指示灯亮代表高电平“1”,指示灯灭代表低电平“0”。连线时应注意:对于横排座,应使排线插头上的箭头面向自己插在横排座上;对于竖排座,应使排线插头上的箭头面向左边插在竖排座上。 1、按图3-1接线图接线: 图3-1 实验三开关实验接线 2、拨动清零开关CLR,使其指示灯显示状态为亮—灭—亮。 3、往存储器写数据:

以往存储器的(FF ) 地址单元写入数据“AABB ”为例,操作过程如下: 4、按上述步骤按表3-2所列地址写入相应的数据 表3-2 5、从存储器里读数据: 以从存储器的(FF ) 地址单元读出数据“AABB ”为例,操作过程如下: (操作) (显示) (操作) (显示) (操作) (显6、按上述步骤读出表3-2数据,验证其正确性。 五、实验结果及结论 通过按照实验的要求以及具体步骤,对数据进行了严格的检验,结果是正确的,具体数据如图所示:

51单片机流水灯试验 一、实验目的 1.了解51单片机的引脚结构。 2.根据所学汇编语言编写代码实现LED灯的流水功能。 3.利用开发板下载hex文件后验证功能。 二、实验器材 个人电脑,80c51单片机,开发板 三、实验原理 单片机流水的实质是单片机各引脚在规定的时间逐个上电,使LED灯能逐个亮起来但过了该引脚通电的时间后便灭灯的过程,实验中使用了单片机的P2端口,对8个LED灯进行控制,要实现逐个亮灯即将P2的各端口逐一置零,中间使用时间间隔隔开各灯的亮灭。使用rl或rr a实现位的转换。 A寄存器的位经过rr a之后转换如下所示: 然后将A寄存器转换一次便送给P2即MOV P2,A便将转换后的数送到了P2口,不断循环下去,便实现了逐位置一操作。 四、实验电路图

五、通过仿真实验正确性 代码如下:ORG 0 MOV A,#00000001B LOOP:MOV P2,A RL A ACALL DELAY SJMP LOOP DELAY:MOV R1,#255 DEL2:MOV R2,#250 DEL1:DJNZ R2,DEL1 DJNZ R1,DEL2 RET End 实验结果:

六、实验总结 这次试验我通过Proteus仿真实现对流水灯功能的实现。受益匪浅,对80c51的功能和结构有了深层次的了解,我深刻的明白,要想完全了解c51还有一定距离,但我会一如既往的同困难作斗争。在实验中,我遇到了不少困难,比如不知道怎么将程序写进单片机中,写好程序的却总出错,不知道什么原因,原来没有生成hex文件。这些错误令我明白以后在试验中要步步细心,避免出错。

实习五虚拟存储器 一、实习内容 模拟分页式虚拟存储管理中硬件的地址转换和缺页中断,以及选择页面调度算法处理缺页中断。 二、实习目的 在计算机系统中,为了提高主存利用率,往往把辅助存储器(如磁盘)作为主存储器的扩充,使多道运行的作业的全部逻辑地址空间总和可以超出主存的绝对地址空间。用这种办法扩充的主存储器称为虚拟存储器。通过本实习帮助同学理解在分页式存储管理中怎样实现虚拟存储器。 三、实习题目 本实习有三个题,其中第一题必做,第二、第三题中可任选一个。 第一题:模拟分页式存储管理中硬件的地址转换和产生缺页中断。 [提示]: (1) 分页式虚拟存储系统是把作业信息的副本存放在磁盘上,当作业被选中时,可把作业的开始几页先装入主存且启动执行。为此,在为作业建立页表时,应说明哪些页已在主存,哪些页尚未装入主存,页表的格式为: 其中,标志——用来表示对应页是否已经装入主存,标志位=1,则表示该页已经在主存,标志位=0,则表示该页尚未装入主存。 主存块号——用来表示已经装入主存的页所占的块号。 在磁盘上的位置——用来指出作业副本的每一页被存放在磁盘上的位置。 (2) 作业执行时,指令中的逻辑地址指出了参加运算的操作数存放的页号和单元号,硬件的地址转换机构按页号查页表,若该页对应标志为“1”,则表示该页已在主存,这时根据关系式: 绝对地址=块号 块长+单元号 计算出欲访问的主存单元地址。如果块长为2的幂次,则可把块号作为高地址部分,把单元号作为低地址部分,两者拼接而成绝对地址。按计算出的绝对地址可以取到操作数,完成一条指令的执行。若访问的页对应标志为“0”,则表示该页不在主存,这时硬件发“缺页中断”信号,由操作系统按该页在磁盘上的位置,把该页信息从磁盘读出装入主存后再重新执行这条指令。 (3) 设计一个“地址转换”程序来模拟硬件的地址转换工作。当访问的页在主存时,则形成绝对地址,但不去模拟指令的执行,而用输出转换后的地址来代替一条指令的执行。当访问的页不在主存时,则输出“*该页页号”,表示产生了一次缺页中断。该模拟程序的算法如图5-1。 (4) 假定主存的每块长度为128个字节;现有一个共七页的作业,其中第0页至第3

科技学院 课程设计实验报告 ( 2014--2015年度第一学期) 名称:计算机组成原理综合实验题目:存储器和I/O扩展实验 院系:信息工程系 班级: 学号: 学生姓名: 指导教师:李梅王晓霞 设计周数:一周 成绩: 日期:2015 年1 月

一、目的与要求 1. 内存储器部件实验 (1)熟悉ROM芯片和RAM芯片在功能和使用方法等方面的相同和差异之处;学习用编程器设备向EEPROM芯片内写入一批数据的过程和方法。 (2)理解并熟悉通过字、位扩展技术实现扩展存储器系统容量的方案; (3)了解静态存储器系统使用的各种控制信号之间正常的时序关系; (4)了解如何通过读、写存储器的指令实现对58C65 ROM芯片的读、写操作; (5)加深理解存储器部件在计算机整机系统中的作用。 2. I/O口扩展实验 学习串行口的正确设置和使用。 二、实验正文 1.主存储器实验内容 1.1实验的教学计算机的存储器部件设计(说明只读存储器的容量、随机读写器的容量,各选用了什么型号及规格的芯片、以及地址空间的分布) 在教学计算机存储器部件设计中,出于简化和容易实现的目的,选用静态存储器芯片实现内存储器的存储体,包括唯读存储区(ROM,存放监控程序等) 和随读写存储区(RAM)两部分,ROM存储区选用4片长度8位、容量8KB 的58C65芯片实现,RAM存储区选用2片长度8位、容量2KB的6116芯片 实现,每2个8位的芯片合成一组用于组成16位长度的内存字,6个芯片被分 成3组,其地址空间分配关系是:0-1777h用于第一组ROM,固化监控程序, 2000-2777h用于RAM,保存用户程序和用户数据,其高端的一些单元作为监 控程序的数据区,第二组ROM的地址范围可以由用户选择,主要用于完成扩 展内存容量(存储器的字、位扩展)的教学实验。 1.2扩展8K字的存储空间,需要多少片58C65芯片,58C65芯片进行读写时的特殊要求 要扩展8K字的存储空间,需要使用2片(每一片有8KB容量,即芯片内由8192个单元、每个单元由8个二进制位组成)存储器芯片实现。对 58C65 ROM芯片执行读操作时,需要保证正确的片选信号(/CE)为低点平, 使能控制信号(/OE)为低电平,读写命令信号(/WE)为高电平,读58C65 ROM 芯片的读出时间与读RAM芯片的读出时间相同,无特殊要求;对58C65 ROM 芯片执行写操作时,需要保证正确的片选信号(/CE)为低电平,使能控制信 号(/OE)为高电平,读写命令信号(/WE)为低电平,写58C65 ROM芯片的 维持时间要比写RAM芯片的操作时间长得多。为了防止对58C65 ROM芯片执 行误写操作,可通过把芯片的使能控制引脚(/OE)接地来保证,或者确保读 写命令信号(/WE)恒为高电平。 1.3在实验中思考为何能用E命令直接写58C65芯片的存储单元,而A命令则有时不正确;

实验一 CPU片内(外)清零 1.CPU片内RAM清零 一、实验目的: 掌握MCS-51汇编语言的设计,了解单片机的寻址方式以及调试方法。二、实验内容: 把单片机片内的30H~7FH单元清零。 三、实验框图: 四、实验步骤: 用连续或者单步的方式运行程序,检查30H-7FH执行前后的内容变化。五、参考实验程序: 程序名称:PNQL.ASM ORG 0000H JMP MAIN ORG 0030H MAIN: MOV R0,#30H ;30H送R0寄存器 CLR1: MOV A,#00H ;00送累加器A MOV @R0,A ;00 送到30H-7FH单元 INC R0 ;R0加1 CJNE R0,#7FH,CLR1 ;不到7F字节再清 WAIT: LJMP WAIT END 六、实验思考: 如果把30H-7FH的内容改为99H,如何修改程序。

2.CPU 片外RAM清零 一、实验目的: 掌握MCS-51汇编语言的设计,了解单片机的寻址方式以及调试方法。 二、实验内容: 把外部扩展的RAM的0000H-00FFH单元内容清零。 三、实验框图: 四、实验步骤: 用连续或者单步的方式运行程序,检查0000H-00FFH执行前后的内容变化。 五、参考实验程序: 程序名称:PWQL.ASM ORG 0000H MAIN: MOV SP,#60H MOV DPTR,#0000H ;0000H送DPTR寄存器 MOV R6,#0FFH ;FFH送R6寄存器(计数) CLR1: MOV A,#00H ;00送累加器A MOVX @DPTR,A ;00 送到0000H-00FFH单元 INC DPTR ;DPTR+1 DJNZ R6,CLR1 ;不到FF个字节再清 WAIT: SJMP WAIT END 六、实验思考: 把1-10先对应存入片内0030H起始的单元内,然后再从片内取出,对应存入片外7FFFH起始的单元中去。

淮海工学院计算机科学系实验报告书 课程名:《操作系统》 题目:虚拟存储器管理 页面置换算法模拟实验 班级: 学号: 姓名:

一、实验目的与要求 1.目的: 请求页式虚存管理是常用的虚拟存储管理方案之一。通过请求页式虚存管理中对页面置换算法的模拟,有助于理解虚拟存储技术的特点,并加深对请求页式虚存管理的页面调度算法的理解。 2.要求: 本实验要求使用C语言编程模拟一个拥有若干个虚页的进程在给定的若干个实页中运行、并在缺页中断发生时分别使用FIFO和LRU算法进行页面置换的情形。其中虚页的个数可以事先给定(例如10个),对这些虚页访问的页地址流(其长度可以事先给定,例如20次虚页访问)可以由程序随机产生,也可以事先保存在文件中。要求程序运行时屏幕能显示出置换过程中的状态信息并输出访问结束时的页面命中率。程序应允许通过为该进程分配不同的实页数,来比较两种置换算法的稳定性。 二、实验说明 1.设计中虚页和实页的表示 本设计利用C语言的结构体来描述虚页和实页的结构。 在虚页结构中,pn代表虚页号,因为共10个虚页,所以pn的取值范围是0—9。pfn代表实页号,当一虚页未装入实页时,此项值为-1;当该虚页已装入某一实页时,此项值为所装入的实页的实页号pfn。time项在FIFO算法中不使用,在LRU中用来存放对该虚页的最近访问时间。 在实页结构中中,pn代表虚页号,表示pn所代表的虚页目前正放在此实页中。pfn代表实页号,取值范围(0—n-1)由动态指派的实页数n所决定。next是一个指向实页结构体的指针,用于多个实页以链表形式组织起来,关于实页链表的组织详见下面第4点。 2.关于缺页次数的统计 为计算命中率,需要统计在20次的虚页访问中命中的次数。为此,程序应设置一个计数器count,来统计虚页命中发生的次数。每当所访问的虚页的pfn项值不为-1,表示此虚页已被装入某实页内, 此虚页被命中,count加1。最终命中率=count/20*100%。 3.LRU算法中“最近最久未用”页面的确定 为了能找到“最近最久未用”的虚页面,程序中可引入一个时间计数器countime,每当要访问 一个虚页面时,countime的值加1,然后将所要访问的虚页的time项值设置为增值后的当前

南昌航空大学实验报 二0 一七年5月3日 课程名称:数据库概论实验名称:存储器与触发器 班级: XX X 姓名:XXX 同组人: 指导教师评定:________________________________________ 签名:__________________ 一、实验环境 1. Windows2000或以上版本; 2. SQLServer2000 或2005。 二、实验目的 1. 掌握存储过程的创建,修改,使用,删除; 2. 掌握触发器的创建,修改,使用,删除。 三、实验步骤及参考源代码 1.创建过程代码: CREATEPROCEDURI_P_Proc( @ccna varchar (10), @cnochar (4) OUTPU,T@cna varchar (10) OUTPU,T@pnavarchar (20) OUTPU,T@numint OUTPUT

AS SELECT@cna=cna, @cno=cp. cno, @pna=pna, @num=num FROMcp , customer , paper WHEREcustomer . cno=cp. cno ANDpaper . pno=cp. pno ANDcna =@ccna; 6.执行存储过程C_P_Pro,实现对李涛,钱金浩等不同顾客的订阅信息查询 execute C_P_Proc @nam=e' 李涛' execute C_P_Proc @nam=e' 钱金浩' 7,删除存储过程C_P_Prcc DROPPROCEDURCE_P_PROC (4)在DingBao数据库中针对PAPER创建插入触发器TR_PAPER_I删除触发器TR_PAPER_D修改触发器TR_PAPER_J具体要求如下。 <1>对PAPER的插入触发器:插入报纸记录,单价为负值或为空时,设定为10 元。 CREATE TRIGGER TR_PAPER_I ON paper FOR INSERT AS DECLARE @ippr FLOAT; declare @ipno int;

实验五存储器读写实验报告 实验报告 课程名:《计算机组成原理》题目:实验五存储器读写班级:计算机+ 自动化0901班姓名:张哲玮,郑俊飞 《计算机组成原理》实验报告- 1 - 实验五、存储器读写实验 一、目的与要求 (1)掌握存储器的工作特性 (2)熟悉静态存储器的操作过程,验证存储器的读写方法 二、实验原理及原理图 (1)?静态存储器芯片6116的逻辑功能 6116是一种数据宽度为8位(8个二进制位),容量为2048字节的静态存储器芯片,封在24引脚的封装中,封装型式如图2-7所示。6116芯片有8根双向三态数据线D7-D0,所谓三态是指输入状态,输出状态和高阻状态,高阻状态数据线处于一种特殊的“断开”状态;11根地址线A10-A0,指示芯片内部2048个存储单元号;3根控制线CS片选控制信号,低电平时,芯片可进行读写操作,高电平时,芯片保存信息不能进行读写;WE 为写入控制信号,低电平时,把数据线上的信息存入地址线A10-A0指示的存储单元中;0E为输出使能控制信号,低电平时,把地址线A10-A0指示的存储单元中的数据读出送到数据线上。

6116芯片控制信号逻辑功能表 (2).存储器实验单元电路 因为在计算机组成原理实验中仅用了256个存储单元,所以6116芯片的3根地址线A11-A8接地也没有多片联用问题,片选信号CS接地使芯片总是处于被选中状态。芯片的WE和0E信号分别连接实验台的存储器写信号M-W和存储器读信号M-Ro这种简化了控制过程的实验电路可方便实验进行。 存储器部件电路图 (3)?存储器实验电路 存储器读\写实验需三部分电路共同完成:存储器单元(MEM UNIT),地址寄存器单元(ADDRESS UNIT)和输入,输出单元(INPUT/OUTPIT UNIT).存储器单元6116芯片为中心构成,地址寄存器单元主要由一片74LS273组成,控制信号B-AR的作用是把总线上的数据送入地址寄存器,向存储器单元电路提供地址信息,输入,输出单元作用与以前相同。

微控制器技术创新设计实验报告 :学号:班级: 一、项目背景 使用单片机AT89C52和ADC0808设计一个数字电压表,能够测量0-5V之间的直流电压值,四位数码显示。在单片机的作用下,能监测两路的输入电压值,用8位串行A/D转换器,8位分辨率,逐次逼近型,基准电压为5V;显示精度0.001伏。 二、项目整体方案设计 ADC0808 是含8 位A/D 转换器、8 路多路开关,以及与微型计算机兼容的控制逻辑的CMOS组件,其转换方法为逐次逼近型。ADC0808的精度为1/2LSB。在AD 转换器内部有一个高阻抗斩波稳定比较器,一个带模拟开关树组的256 电阻分压器,以及一个逐次通近型寄存器。8 路的模拟开关的通断由地址锁存器和译码器控制,可以在8 个通道中任意访问一个单边的模拟信号。

三、硬件设计 四、软件设计 #include

sbit CS0=P2^0; sbit CS1=P2^1; sbit CS2=P2^2; sbit CS3=P2^3; uint adval,volt; uchar tab[]={0xC0,0xF9,0xA4,0xB0,0x99,0x92,0x82,0xF8, 0x80,0x90,0x88,0x83,0xC6,0xA1,0x86,0x8E}; void delayms(uint ms) { uchar j; while(ms --) { for(j=0;j<120;j++); } } void ADC_read() { START=0; START=1; START=0; while(EOC==0); OE=1;

计算机组成原理 实验五《存储器设计》 实验报告 姓名:吴速碘黄紫微 学号:13052053 13052067 班级:计算机二班 日期2015、5、25

实验五存储器设计 一、实验目的 1、掌握RAM和ROM的Verilog语言描述方法; 2、学习用宏模块的方法定制RAM和ROM。 二、实验任务 1、设计并实现一个128*16 的单端口的RAM; 2、设计并实现一个128*16的ROM; 3、设计并实现一个双端口的128*16的RAM 4、设计并实现一个16*32的FIFO。 5、设计并实现正弦信号发生器,见“正弦信号发生器实验指南”。 三、实验步骤 1 编写Verilog代码(见附页) 2功能仿真 进行分析与综合,排除语法上的错误 建立波形仿真文件,输入激励 生成功能仿真网表 进行功能仿真,观察输出结果 3选择器件 DE2_70开发板的使用者请选择EP2C70F896C6 4绑定管脚 5 下载验证 DE2_70开发板的下载:使用USB-Blaster进行下载 四、实验内容 五、实验思考题 1、分析存储器采用三态输出的原因是什么? 存储器的输出端是连接在数据总线上的。数据总线相当于一条车流频繁的大马路,必须在绿灯条件下,车辆才能进入这条大马路,否则要撞车发生交通事故。同 理,存储器中的数据是不能随意传送到数据总线上的。例如,若数据总线上的数 据是“1”(高电平5V),存储器中的数据是“0”(低电平0V),两种数据若碰到一 起就会发生短路而损坏单片机。因此,存储器输出端口不仅能呈现“l”和“0”两 种状态,还应具有第三种状态“高阻"态。呈“高阻"态时,输出端口相当于断开,对数据总线不起作用,此时数据总线可被其他器件占用。当其他器件呈“高阻”态 时,存储器在片选允许和输出允许的条件下,才能将自己的数据输出到数据总线 上。 2、单端口和双端口的区别是什么? 单端口ram是ram的读写只有一个端口,同时只能读或者只能写。 双端口ram是ram读端口和写端口分开,一个端口能读,另一个端口可以同时写。 3、什么情况下考虑采用双端口存储器?

深圳大学实验报告 课程名称:_____________ 微机计算机设计__________________ 实验项目名称:静态存储器扩展实验______________ 学院:_________________ 信息工程学院____________________ 专业:_________________ 电子信息工程____________________ 指导教师:____________________________________________ 报告人:________ 学号:2009100000班级:<1>班 实验时间:_______ 2011.05. 05 实验报告提交时间:2011. 05. 31 教务处制 一、实验目的 1. 了解存储器扩展的方法和存储器的读/ 写。 2. 掌握CPU寸16位存储器的访问方法。 二、实验要求

编写实验程序,将OOOOH H OOOFH共16个数写入SRAM的从0000H起始的一段空间中,然后通过系统命令查看该存储空间,检测写入数据是否正确。 三、实验设备 PC 机一台,TD-PITE 实验装置或TD-PITC 实验装置一套。 四、实验原理 1、存储器是用来存储信息的部件,是计算机的重要组成部分,静态RAM是由MOS 管组成的触发器电路,每个触发器可以存放1 位信息。只要不掉电,所储存的信息就不会丢失。此,静态RAM工作稳定,不要外加刷新电路,使用方便。 2、本实验使用两片的62256芯片,共64K字节。本系统采用准32位CPU具有16 位外部数据总线,即D0 D1、…、D15,地址总线为BHE^(#表示该信号低电平有效)、BLE#、A1、A2、…、A20。存储器分为奇体和偶体,分别由字节允许线BH四和BLE#选通。存储器中,从偶地址开始存放的字称为规则字,从奇地址开始存放的字称为非规则字。处理器访问规则字只需要一个时钟周期,BH即和BLE #同时有效,从而同时选通存储器奇体和偶体。处理器访问非规则字却需要两个时钟周期,第一个时钟周期BH即有效,访问奇字节;第二个时钟周期BLE#有效,访问偶字节。处理器访问字节只需要一个时钟周期,视其存放单元为奇或偶,而BH四或BLE#有效,从而选通奇体或偶体。 五、实验过程 1、按图接线好电路。 2. 编写实验程序,经编译、链接无误后装入系统。 实验部分代码如下: STACK SEGMENT STACK DW 32 DUP(?) STACK ENDS CODE SEGMENT START PROC FAR ASSUME CS:CODE MOV AX, 8OOOH ; MOV DS, AX AAO: MOV SI, OOOOH ; MOV CX, OO1OH MOV AX, OOOOH AA1: MOV [SI], AX