用Verilog语言实现奇数倍分频电路 3分频 5分频 7分频

- 格式:docx

- 大小:19.16 KB

- 文档页数:7

时钟任意奇数及偶数倍分频1 原理偶数倍分频:占空比50%的偶数倍分频通过计数器计数是完全可以实现的。

比如,进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数,以此循环下去。

此方法可以实现任意的偶数分频。

如下下图,50MHz时钟,6分频:奇数倍分频:对于实现占空比为50%的N倍奇数分频,首先用时钟上升沿触发计数器进行计数,计数从零开始,到(N-1)/2进行输出时钟翻转,然后计数到N-1再次进行翻转得到一个占空比非50%奇数N分频时钟。

再者同时进行下降沿触发的计数,计数从零开始,到(N -1)/2进行输出时钟翻转,然后计数到N-1再次进行翻转得到一个占空比非50%奇数N分频时钟。

两个占空比非50%的N分频时钟相或运算,得到占空比为50%的奇数N分频时钟。

如下下图,50MHz时钟,5分频:2 CPLD代码2.1 任意偶数倍分频module odd_div(clk, //全局时钟rst, //全局异步复位clk_odd, //分频后的时钟输出/*for Test*/count //分频计数器);input clk,rst;output clk_odd;/*for Test*/output[3:0] count;reg clk_odd;reg[3:0] count; //分频计数器,示分频倍数需要的计数器决定计数器位数parameter N = 6; //分频倍数,N为偶数always @ (posedge clk or negedge rst)beginif(rst == 1'b0)begincount <= 1'b0;clk_odd <= 1'b0; //分频时钟先输出低电平endelsebeginif ( count < N/2-1) //计数未到N/2-1时,计数加1begincount <= count + 1'b1;endelse //计数到N/2-1时,计数清0,输出时钟反转。

FPGA分频与倍频的简单总结(涉及⾃⼰设计,调⽤时钟IP核,调⽤MMCM原语模块)原理介绍1、分频FPGA设计中时钟分频是重要的基础知识,对于分频通常是利⽤计数器来实现想要的时钟频率,由此可知分频后的频率周期更⼤。

⼀般⽽⾔实现偶数系数的分频在程序设计上较为容易,⽽奇数分频则相对复杂⼀些,⼩数分频则更难⼀些。

1)偶分频系数=时钟输⼊频率/时钟输出频率=50MHz/5MHz=10,则计数器在输⼊时钟的上升沿或者下降沿从0~(10-1)计数,⽽输出时钟在计数到4和9时翻转。

2)奇分频系数=50MHz/10MHz=5,则两个计数器分别在输⼊时钟的上升沿和下降沿从0~ (5-1)计数,⽽相应的上升沿和下降沿触发的输出时钟在计数到1和4时翻转,最后将两个输出时钟进⾏或运算从⽽得到占空⽐为50%的5分频输出时钟。

下图所⽰为50MHz输⼊时钟进⾏10分频和5分频的仿真波形2、倍频两种思路:PLL(锁相环)或者利⽤门延时来搭建注意:此仿真是利⽤FPGA内部电路延迟来实现的倍频需要在后仿真下才能看到波形,在⾏为仿真下⽆法得到输出波形。

⼀、时钟IP的分频倍频相关参数说明输⼊时钟:clk_in1(125MHz)输出时钟:clk_out1(50MHz),clk_out2(74.25MHz)则VCO Freq=1262.5MHz=clk_in1*CLKFBOUT_MULT_F/DIVCLK_DIVIDE=125*50.5/5clk_out1(50MHz)=VCO_Freq/Divide=1265.5/25.250clk_out2(74.25MHz)=VCO_Freq/Divide=1265.5/17⼆、MMCME4_ADVMMCME4是⼀种混合信号块,⽤于⽀持频率合成、时钟⽹络设计和减少抖动。

基于相同的VCO频率,时钟输出可以有单独的分频、相移和占空⽐。

此外,MMCME4还⽀持动态移相和分数除法(1)Verilog 初始化模板MMCME4_ADV #(.BANDWIDTH("OPTIMIZED"), // Jitter programming.CLKFBOUT_MULT_F(5.0), // Multiply value for all CLKOUT.CLKFBOUT_PHASE(0.0), // Phase offset in degrees of CLKFB.CLKFBOUT_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKIN1_PERIOD(0.0), // Input clock period in ns to ps resolution (i.e. 33.333 is 30 MHz)..CLKIN2_PERIOD(0.0), // Input clock period in ns to ps resolution (i.e. 33.333 is 30 MHz)..CLKOUT0_DIVIDE_F(1.0), // Divide amount for CLKOUT0.CLKOUT0_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT0.CLKOUT0_PHASE(0.0), // Phase offset for CLKOUT0.CLKOUT0_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT1_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT1_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT1_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT1_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT2_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT2_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT2_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT2_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT3_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT3_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT3_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT3_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT4_CASCADE("FALSE"), // Divide amount for CLKOUT (1-128).CLKOUT4_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT4_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT4_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT4_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT5_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT5_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT5_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT5_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT6_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT6_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT6_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT6_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).COMPENSATION("AUTO"), // Clock input compensation.DIVCLK_DIVIDE(1), // Master division value.IS_CLKFBIN_INVERTED(1'b0), // Optional inversion for CLKFBIN.IS_CLKIN1_INVERTED(1'b0), // Optional inversion for CLKIN1.IS_CLKIN2_INVERTED(1'b0), // Optional inversion for CLKIN2.IS_CLKINSEL_INVERTED(1'b0), // Optional inversion for CLKINSEL.IS_PSEN_INVERTED(1'b0), // Optional inversion for PSEN.IS_PSINCDEC_INVERTED(1'b0), // Optional inversion for PSINCDEC.IS_PWRDWN_INVERTED(1'b0), // Optional inversion for PWRDWN.IS_RST_INVERTED(1'b0), // Optional inversion for RST.REF_JITTER1(0.0), // Reference input jitter in UI (0.000-0.999)..REF_JITTER2(0.0), // Reference input jitter in UI (0.000-0.999)..SS_EN("FALSE"), // Enables spread spectrum.SS_MODE("CENTER_HIGH"), // Spread spectrum frequency deviation and the spread type .SS_MOD_PERIOD(10000), // Spread spectrum modulation period (ns).STARTUP_WAIT("FALSE") // Delays DONE until MMCM is locked)MMCME4_ADV_inst (.CDDCDONE(CDDCDONE), // 1-bit output: Clock dynamic divide done.CLKFBOUT(CLKFBOUT), // 1-bit output: Feedback clock.CLKFBOUTB(CLKFBOUTB), // 1-bit output: Inverted CLKFBOUT.CLKFBSTOPPED(CLKFBSTOPPED), // 1-bit output: Feedback clock stopped.CLKINSTOPPED(CLKINSTOPPED), // 1-bit output: Input clock stopped.CLKOUT0(CLKOUT0), // 1-bit output: CLKOUT0.CLKOUT0B(CLKOUT0B), // 1-bit output: Inverted CLKOUT0.CLKOUT1(CLKOUT1), // 1-bit output: CLKOUT1.CLKOUT1B(CLKOUT1B), // 1-bit output: Inverted CLKOUT1.CLKOUT2(CLKOUT2), // 1-bit output: CLKOUT2.CLKOUT2B(CLKOUT2B), // 1-bit output: Inverted CLKOUT2.CLKOUT3(CLKOUT3), // 1-bit output: CLKOUT3.CLKOUT3B(CLKOUT3B), // 1-bit output: Inverted CLKOUT3.CLKOUT4(CLKOUT4), // 1-bit output: CLKOUT4.CLKOUT5(CLKOUT5), // 1-bit output: CLKOUT5.CLKOUT6(CLKOUT6), // 1-bit output: CLKOUT6.DO(DO), // 16-bit output: DRP data output.DRDY(DRDY), // 1-bit output: DRP ready.LOCKED(LOCKED), // 1-bit output: LOCK.PSDONE(PSDONE), // 1-bit output: Phase shift done.CDDCREQ(CDDCREQ), // 1-bit input: Request to dynamic divide clock.CLKFBIN(CLKFBIN), // 1-bit input: Feedback clock.CLKIN1(CLKIN1), // 1-bit input: Primary clock.CLKIN2(CLKIN2), // 1-bit input: Secondary clock.CLKINSEL(CLKINSEL), // 1-bit input: Clock select, High=CLKIN1 Low=CLKIN2.DADDR(DADDR), // 7-bit input: DRP address.DCLK(DCLK), // 1-bit input: DRP clock.DEN(DEN), // 1-bit input: DRP enable.DI(DI), // 16-bit input: DRP data input.DWE(DWE), // 1-bit input: DRP write enable.PSCLK(PSCLK), // 1-bit input: Phase shift clock.PSEN(PSEN), // 1-bit input: Phase shift enable.PSINCDEC(PSINCDEC), // 1-bit input: Phase shift increment/decrement.PWRDWN(PWRDWN), // 1-bit input: Power-down.RST(RST) // 1-bit input: Reset);(2)本实验仿真所⽤参数配置说明及部分端⼝调⽤1、参数配置说明本实验通过输⼊时钟CLKIN1(150MHz),实现输出反馈时钟CLKFBOUT(150MHz)、输出时钟CLKOUT0(74.25MHz)、输出时钟CLKOUT1(74.25MHz)、输出时钟CLKOUT2(59.4MHz)、输出时钟CLKOUT3(49.5MHz)。

module clk_div(//-----------input-----------iCLK,div,//-----------output----------oCLK);//-----------input-----------parameter WIDE=14;input iCLK;input[WIDE-1:0]div;//-----------output-----------output oCLK;wire oCLK_odd;wire oCLK_even;assign oCLK=div[0]?oCLK_odd:oCLK_even;div_odd DUTo (.iCLK(iCLK),.oCLK(oCLK_odd),.div(div)); div_even DUTe (.iCLK(iCLK),.oCLK(oCLK_even),.div(div));endmodule// oddmodule div_odd(//--------input--------iCLK,div,//--------output--------oCLK);//--------input--------parameter WIDE=14;input iCLK;input[WIDE-1:0]div;//--------output--------output oCLK;reg outCLK;/*=========================== solve 1=========================== reg cout;reg[WIDE-1:0] cnt;initial cnt=0;wire inCLK;reg cc;initial cc=0;always @(posedge cout)cc<=~cc;assign inCLK = iCLK^cc;always @(posedge inCLK)beginif(cnt<(div[WIDE-1:1]))begincnt<=cnt+1;cout<=1'b0;endelsebegincnt<=0;cout<=1'b1;endendalways @(negedge iCLK)outCLK <= cout;assign oCLK=cc;*///======================== //solve 2//======================== reg[WIDE-1:0] cnt_a;initial cnt_a=0;reg[WIDE-1:0] cnt_b;initial cnt_b=0; reg cout_a;reg cout_b;always @(negedge iCLK)beginelse if(cnt_a<=(div[WIDE-1:1]))begincnt_a=cnt_a+1;cout_a=1'b1;endelse if(cnt_a>(div[WIDE-1:1])&&cnt_a<(div[WIDE-1:0]-1))begincout_a=1'b0;cnt_a=cnt_a+1;endelsebegincnt_a=0;endendalways @(posedge iCLK)beginif(cnt_b<=(div[WIDE-1:1]))begincnt_b=cnt_b+1;cout_b=1'b1;endelse if(cnt_b>(div[WIDE-1:1])&&cnt_b<(div[WIDE-1:0]-1))begincout_b=1'b0;cnt_b=cnt_b+1;endelsebegincnt_b=0;endendassign oCLK = cout_a&cout_b;endmodule//evenmodule div_even(//--------input--------iCLK,div,//--------output--------oCLK);//--------input--------parameter WIDE=14;input iCLK;input[WIDE-1:0]div;//--------output--------output oCLK;reg oCLK;initial oCLK = 1'b0;reg[WIDE-1:0] cnt;initial oCLK = 0;always @(posedge iCLK)beginif(cnt<(div[WIDE-1:1]-1))cnt <= cnt + 1;elsebegincnt <= 0;oCLK <= ~oCLK;endendendmodule//============================//testbench//============================/*module clk_div_test;//-----------input-----------parameter WIDE=14;reg iCLK;reg[WIDE-1:0] div;//-----------output-----------wire oCLK;clk_div cc(.iCLK(iCLK),.div(div),.oCLK(oCLK));always #20 iCLK = ~iCLK;initialbeginiCLK = 0;div=14'd7;#1000 $stop;endendmodule*/module clk_div14bits(clk,a,clkout);input clk,a;output clkout;reg clkout;wire oCLK1,oCLK2;clk_div cc1(.div(14'd8),.iCLK(iCLK),.oCLK(oCLK1)); clk_div cc2(.div(14'd9),.iCLK(iCLK),.oCLK(oCLK2));always @(a or posedge clkin)beginif(a==1)clkout=oCLK1;elseclkout=oCLK2;endendmodule//测试代码//testbenchmodule clk_div14bits_test;//-----------input-----------parameter WIDE=14;reg clk;reg[WIDE-1:0] div;//-----------output-----------wire oCLK;clk_div14bits cc3(.clk(clk),.a(a),.clkout(clkout)); always #20 clk = ~clk;initialbeginiCLK = 0;div=14'd7;#1000 $stop;EndModelsim仿真结果1.七分频2.四分频。

实验六Verilog设计分频器/计数器电路一、实验目的1进一步掌握最基本时序电路的实现方法;2学习分频器/计数器时序电路程序的编写方法;3进一步学习同步和异步时序电路程序的编写方法。

二、实验内容1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为5个clock周期的低电平,5个clock周期的高电平),文件命名为fenpinqi10.v。

2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为couter10.v。

3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。

4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5.v。

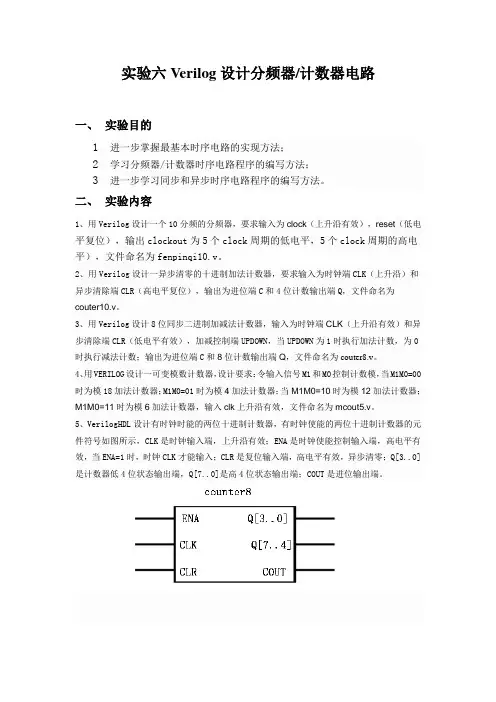

5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q[3..0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端。

三、实验步骤:第一个实验:1、打开QuartusII,新建一个工程f_fenpinq10yjq2、新建一个Verilog HDL文件3、输入程序:module fenpinqi10(clk,reset,clkout);input clk,reset;output clkout;reg clkout;reg[2:0] cnt;always @(posedge clk , negedge reset)beginif(!reset)begin clkout<=0;cnt<=0;endelse if(cnt==4)begin cnt<=0;clkout<=~clkout;endelse cnt<=cnt+1;endendmodule4、设置顶层实体名(点settings>general >下拉选fenpinqi10)5、编译6、执行file>Create/Update>Create Symbol Files for Current Flie为VHDI设计文件生成原件符号7、建立波形文件8、导入引脚9、仿真结果如下:总结:仿真结果与实验一的题意相符,所以仿真正确。

用Verilog语言实现奇数倍分频电路3分频5分频7分频Verilog是一种硬件描述语言(HDL),用于描述数字电路的行为和结构。

使用Verilog语言实现奇数倍分频电路可以分为以下几个步骤:1.定义输入和输出端口通过module关键字定义一个模块,并指定输入和输出端口的信号。

```verilogmodule OddDividerinput clk,output reg out_3x,output reg out_5x,output reg out_7x```2.定义局部变量和计数器定义一个局部变量和一个计数器,用于跟踪时钟周期并确定何时输出。

```verilogreg [2:0] count;```3.实现分频逻辑使用always块,根据计数器的值判断何时输出,并在输出端口上更新信号。

```verilogif (count == 3'b000) beginout_3x <= !out_3x;endif (count == 3'b001) beginout_5x <= !out_5x;endif (count == 3'b010) beginout_7x <= !out_7x;endcount <= count + 1;end```4.结束模块使用endmodule关键字结束模块定义。

```verilogendmodule完整的Verilog代码如下:```verilogmodule OddDividerinput clk,output reg out_3x,output reg out_5x,output reg out_7xreg [2:0] count;if (count == 3'b000) begin out_3x <= !out_3x;endif (count == 3'b001) begin out_5x <= !out_5x;endif (count == 3'b010) begin out_7x <= !out_7x;endcount <= count + 1;endmodule```以上代码实现了一个奇数倍分频电路,其中输入时钟信号为`clk`,输出分别是3倍分频的信号`out_3x`,5倍分频的信号`out_5x`和7倍分频的信号`out_7x`。

eda 7分频代码

在 EDA(电子设计自动化)中,可以使用 Verilog 或 VHDL 等硬件描述语言来实现 7 分频电路。

以下是一个使用 Verilog 实现 7 分频的简单示例代码:

```verilog

module七分频( input clk, output clk_out );

reg [6:0] count;

reg clk_out;

always @(posedge clk) begin

if (count == 6'd6) begin

count <= 6'd0;

clk_out <= ~clk_out;

end else begin

count <= count + 1'd1;

end

end

endmodule

```

上述代码中,我们使用了一个计数器`count`来对输入时钟`clk`进行计数。

当计数器的值达到 6 时,我们将输出时钟`clk_out`取反,并将计数器重置为 0。

这样就实现了 7 分频的功能。

在实际应用中,可能需要根据具体的需求对代码进行修改。

例如,如果需要使用异步复位信号来重置计数器,可以添加一个复位信号`rst`,并在代码中添加相应的复位逻辑。

请注意,上述代码只是一个简单的示例,实际的 7 分频电路可能需要考虑更多的细节和优化。

在设计实际电路时,建议使用专业的 EDA 工具进行综合、仿真和验证,以确保电路的正确性和可靠性。

任意分数Verilog实现网上常见的多为小数分频,分数分频也为有规律的分频,如N/2、M-1/N等。

而像M/N型分数分频却很少。

现介绍一下本人的分数分频实现方法,如果不当之处敬请指教。

分数分频实现基本上都是靠吞脉冲方法实现,如5/2分频,就可以分成一个2分频,一个3分频接替出现,这样(2+3)/2就是5/2分频。

下面以68/9为例介绍下怎么计算。

68=9*7+5,即商为7,余数为5。

可以推出68/9分频,可以看成5个8分频和4个7分频,即(5*8+4*7)/9=68/9。

这个7分频和8分频中的数字7和8就是从商中得出来的。

那5个8分频和4个7分频中的数字5和4就是从余数中的出来的,5是余数,4是(9-5)。

分子:numerator。

分母denominator。

商quotient。

余数remainder。

(翻译不是很准确,表达下意思就行了,呵呵)。

numerator=quotient*denominator+remainder.那么numerator/ denominat or分频就可以通过remainder个(quotient+1)分频和(denominator -remaind er)个quotient分频组成。

还是以68/9为例。

我们得出了5个8分频和4个7分频可以实现这个分数分频,但这5个8分频和4个7分频怎么放置呢?先放5个8分频,再放4个7分频,这样绝对是不行的。

为了均匀的放置这两种频率,我从小数分频中学到一种方法。

找个临时变量temp(程序中用的是sum)。

初始化为0。

每次分频完让它加上余数,判断是否大于分母,如果小于分母,择输出7分频,否则输出8分频,并且将这个值减去分母(让它小于分母)。

这样temp值就变成了5 1 6 2 7 3 8 4 0 5……分频值就成了7 8 7 8 7 8 7 8 8 7 8 7 8 7 8 7 8 8……可以统计一下7分频和8分频的比例就正好是4:5,这样就实现了分数分频。

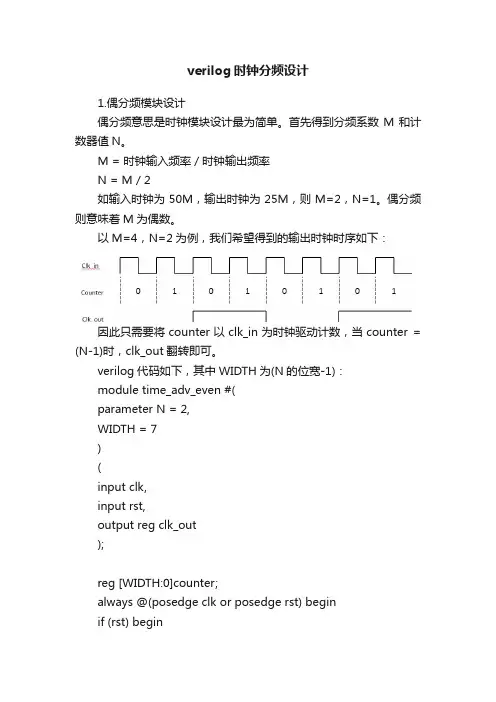

verilog时钟分频设计1.偶分频模块设计偶分频意思是时钟模块设计最为简单。

首先得到分频系数M和计数器值N。

M = 时钟输入频率 / 时钟输出频率N = M / 2如输入时钟为50M,输出时钟为25M,则M=2,N=1。

偶分频则意味着M为偶数。

以M=4,N=2为例,我们希望得到的输出时钟时序如下:因此只需要将counter以clk_in为时钟驱动计数,当counter = (N-1)时,clk_out翻转即可。

verilog代码如下,其中WIDTH为(N的位宽-1):module time_adv_even #(parameter N = 2,WIDTH = 7)(input clk,input rst,output reg clk_out);reg [WIDTH:0]counter;always @(posedge clk or posedge rst) beginif (rst) begin// resetcounter <= 0;endelse if (counter == N-1) begincounter <= 0;endelse begincounter <= counter + 1;endendalways @(posedge clk or posedge rst) beginif (rst) begin// resetclk_out <= 0;endelse if (counter == N-1) beginclk_out <= !clk_out;endendendmoduletestbench测试8分频即N=4,ISE仿真结果如下:2.奇分频模块设计奇分频需要通过两个时钟共同得到。

首先得到分频系数M和计数器值N。

M = 时钟输入频率 / 时钟输出频率N = (M-1) / 2如输入时钟为50M,输出时钟为10M,则M=5,N=2。

奇分频则意味着M为奇数。

基于FPGA的整数倍分频器设计

1、前言

分频器是FPGA设计中使用频率非常高的基本单元之一。

尽管目前在大部分设计中还广泛使用集成锁相环(如Altera的PLL,Xilinx的DLL)来进行时钟的分频、倍频以及相移设计,但是,对于时钟要求不太严格的设计,通过自主设计进行时钟分频的实现方法仍然非常流行。

首先这种方法可以节省锁相环资源,再者这种方式只消耗不多的逻辑单元就可以达到对时钟的操作目的。

2、整数倍分频器的设计

2.1 偶数倍分频

偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。

如需要N分频器(N 为偶数),就可以由待分频的时钟触发计数器进行计数,当计数器从0计数到N/2-1时,将输出时钟进行翻转,并给计数器一个复位信号,以使下一个时钟开始从零计数。

以此循环,就可以实现偶数倍分频。

以10分频为例,相应的verilog代码如下:

regclk_div10;

reg [2:0]cnt;

always@(posedge clk or posedge rst)begin

if(rst)begin //复位

cnt《=0;

clk_div10《=0;

end

elseif(cnt==4)begin

cnt《=0; //清零

clk_div10《=~clk_div10; //时钟翻转

end

else。

Verilog语言实现5分频电路的设计1.行为建模方法:使用行为建模方法,可以通过描述电路的功能行为来实现5分频电路。

以下是使用Verilog语言进行行为建模的代码示例:```verilogmodule DivideBy5input wire clk,output wire clk_outreg [2:0] counter;counter <= 0;clk_out <= ~clk_out;end else begincounter <= counter + 1;endendendmodule```在该示例中,定义了一个模块`DivideBy5`,包含一个输入端口`clk`和一个输出端口`clk_out`,分别用于输入时钟信号和输出分频后的时钟信号。

`reg [2:0] counter`是一个3位的寄存器,用于计数。

当计数达到5时,即计数器的值为5,会将`counter`复位为0,并将输出时钟信号`clk_out`取反。

否则,计数器的值会自增12.结构建模方法:使用结构建模方法,可以通过组合和顺序电路的连接方式来实现5分频电路。

以下是使用Verilog语言进行结构建模的代码示例:```verilogmodule DivideBy5input wire clk,output wire clk_outwire clk_out_2;wire clk_out_3;wire clk_out_4;DivideBy2 div_by_2 ( .clk(clk), .clk_out(clk_out_2) );DivideBy2 div_by_3 ( .clk(clk_out_2), .clk_out(clk_out_3) );DivideBy2 div_by_4 ( .clk(clk_out_3), .clk_out(clk_out_4) );DivideBy2 div_by_5 ( .clk(clk_out_4), .clk_out(clk_out) );endmodulemodule DivideBy2input wire clk,output wire clk_outreg clk_out;clk_out <= ~clk_out;endendmodule```在该示例中,定义了两个模块`DivideBy5`和`DivideBy2`。

VERILOG 分频原理众所周知,分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如altera 的PLL,Xilinx的DLL.来进行时钟的分频,倍频以及相移。

但是对于时钟要求不高的基本设计,通过语言进行时钟的分频相移仍然非常流行,首先这种方法可以节省芯片内部的锁相环资源,再者,消耗不多的逻辑单元就可以达到对时钟操作的目的。

另一方面,通过语言设计进行时钟分频,可以看出设计者对设计语言的理解程度。

因此很多招聘单位在招聘时往往要求应聘者写一个分频器(比如奇数分频)以考核应聘人员的设计水平和理解程度。

下面讲讲对各种分频系数进行分频的方法:第一,偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去。

这种方法可以实现任意的偶数分频。

第二,奇数倍分频:奇数倍分频常常在论坛上有人问起,实际上,奇数倍分频有两种实现方法:首先,完全可以通过计数器来实现,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。

即是在计数值在邻近的1和2进行了两次翻转。

这样实现的三分频占空比为1/3或者2/3。

如果要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。

这种方法可以实现任意的奇数分频。

归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

FPGAer:⼆分频、三分频、五分频写分频就是写计数器。

⼆分频:指把频率分成两部分。

⽐如50MHz的频率,⼆分频后就是25MHz。

由公式T=1/f可知,时钟变为原来的两倍。

综合代码如下:module shizhan(input sys_clk,input sys_rst_n,output reg dri_clk);always @(posedge sys_clk or negedge sys_rst_n)beginif(!sys_rst_n)dri_clk<=1'b0;elsedri_clk<=~dri_clk;endendmoduletb代码如下:`timescale 1ns/1nsmodule shizhan_tb;reg sys_clk;reg sys_rst_n;wire dri_clk;initial beginsys_clk<=1'b0;sys_rst_n<=1'b0;#10 sys_rst_n<=1'b1;endalways #10 sys_clk<=~sys_clk;shizhan u_shizhan(.sys_clk (sys_clk),.sys_rst_n (sys_rst_n),.dri_clk (dri_clk));endmodule实战结果如下:三分频综合代码如下:module clk(input sys_clk,input sys_rst_n,output dri_clk);reg [2:0]cnt;reg dri_clk1;reg dri_clk2;always @(posedge sys_clk or negedge sys_rst_n)beginif(!sys_rst_n)cnt<=3'b0;else if(cnt<2)cnt<=cnt+1;elsecnt<=3'b0;endalways @(posedge sys_clk or negedge sys_rst_n)beginif(!sys_rst_n)begindri_clk1<=1'b0;endelse if(cnt==0)begindri_clk1<=~dri_clk1;endelse if(cnt==1)begindri_clk1<=~dri_clk1;endelsedri_clk1<=dri_clk1;endalways @(negedge sys_clk or negedge sys_rst_n)beginif(!sys_rst_n)dri_clk2<=1'b0;elsedri_clk2<=dri_clk1;endassign dri_clk=dri_clk1|dri_clk2;endmoduletb仿真代码如下:(ps:这个仿真程序跟⼆分频⼀样的,就是名字改成了clk_tb)`timescale 1ns/1nsmodule clk_tb;reg sys_clk;reg sys_rst_n;wire dri_clk;initial beginsys_clk<=1'b0;sys_rst_n<=1'b0;#10 sys_rst_n<=1'b1;endalways #10 sys_clk<=~sys_clk;clk u_clk(.sys_clk (sys_clk),.sys_rst_n (sys_rst_n),.dri_clk (dri_clk));endmodule实战结果:同理,五分频实现如下:综合代码如下:module clk(input sys_clk,input sys_rst_n,output dri_clk);reg [2:0]cnt;reg dri_clk1;reg dri_clk2;always @(posedge sys_clk or negedge sys_rst_n)beginif(!sys_rst_n)cnt<=3'b0;else if(cnt<4)cnt<=cnt+1;elsecnt<=3'b0;endalways @(posedge sys_clk or negedge sys_rst_n)beginif(!sys_rst_n)begindri_clk1<=1'b0;endelse if(cnt==2)begindri_clk1<=~dri_clk1;endelse if(cnt==4)begindri_clk1<=~dri_clk1;endelsedri_clk1<=dri_clk1;endalways @(negedge sys_clk or negedge sys_rst_n)begin if(!sys_rst_n)dri_clk2<=1'b0;elsedri_clk2<=dri_clk1;endassign dri_clk=dri_clk1|dri_clk2;endmodule仿真代码同三分频⼀样。

6. 偶数分频器的设计rate=even(偶数),占空比50%设计原理:定义一个计数器对输入时钟进行计数,(1)在计数的前一半时间里,输出高电平,(2)在计数的后一半时间里,输出低电平,这样输出的信号就是占空比为50%的偶数分频信号。

例如,设计一个6分频电路。

对什么计数?①计数值为0~2输出高电平,②计数值为3~5输出低电平。

上升沿计数一个计数周期0112分频module divder_even(clkin,clkout);parameter n=2;input clkin;output clkout;integer cnt;reg clkout;always@(posedge clkin)beginif(cnt<n-1) cnt<=cnt+1;else cnt<=0;endalways@(cnt)beginif(cnt<n/2) clkout<=1'b1;else clkout<=1'b0;end endmodule计数过程判断赋值过程module divder_even(clkin,clkout);parameter n=2;input clkin;output clkout;integer cnt;reg clkout;always@(posedge clkin)beginif(cnt==n/2-1)begincnt<=0;clkout<=~clkout;endelse cnt<=cnt+1;endendmodule 2分频分析4分频分析二分频四分频知识小结1.移位寄存器的verilog描述。

2.偶数分频的verilog描述。

作业1.设计一个5位串入并出的移位寄存器。

Clear :同步清零;clkin :时钟输入;databit :位输入y[4..0]并行数据输出;2.设计一个4位并入串出的移位寄存器Clear :同步清零;clkin :时钟输入(移位);dataIn :并行数据输入,y :串行数据输出。

分频器对读者的假设已经掌握:∙可编程逻辑基础∙Verilog HDL基础∙使用Verilog设计的Quartus II入门指南∙使用Verilog设计的ModelSIm入门指南内容1 从计数器到分频器此处所说的分频器,即把输入时钟的频率降低后再输出时钟的模块。

今天我们只讨论等占空比的偶数分频和奇数分频,关于小数分频以及倍频将不做介绍,有兴趣的朋友可以自行研究。

在之之前我们先看下前面讲的模-m计数器。

代码1.1 模-m计数器(缺省为模-10计数器)根据这个模-m计数器,我们再写一个testbench。

代码1.2 模m-计数器的testbench(重新配置为模-10计数器)但是我在使用Quartus II + Modelsim_Altera仿真的时候出现了下面的错误提示。

代码2的第10行,变量N未定义,然后第11行用N来索引的q数组也没有定义。

奇怪了,我在Quartus II都能综合通过,而且RTL视图也是正确的,为什么Modelsim_Altera就不可以这样定义呢?咳,把常量(localparam)换成参数(parameter)即可。

代码1.3 改进后的模-m计数器(重新配置为模-10计数器)修改完,在Quartus II 里再综合一下。

接下来就是按照[文档].艾米电子 - 使用Verilog 设计的Quartus II入门指南再做一次仿真。

告诉大家一个技巧,如果执行完一次RTL 级或门级的仿真,那么Quartus II 会为我们的主模块及其testbench生成do 文件的。

这样假如有错误,就无需重新启动Modelsim_Altera ,只需重新load 一下do 文件即可。

(路径格式:Quarter II 工程文件夹\simulation\modelsim \mod_m_bin_counter_run_msim_rtl_verilog.do ) 下面看下RTL 级仿真波形。

下面讨论一下如何测量波形的长度,我们注意两个工具。

汇报总结1、偶数分频偶数倍分频相对简单,可以通过计数器对预分频的脉冲沿计数实现,如果要进行N倍(N为整数)偶数分频,可由预分频的时钟触发计数器计数,当计数器从0计数到N/2—1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数,以此循环下去。

分频的主体程序如下:`define div_en 8module freq_div_even(clk_in,reset,clk_out);input clk_in;input reset;output clk_out;reg clk_out;reg[2:0] count;initialbegincount=0;clk_out=0;endalways@(posedge clk_in)beginif(!reset)begincount<=0;clk_out<=0;endelseif(count==(`div_en/2-1))beginclk_out<=~clk_out;count<=0;endelsebegincount<=count+1;endendendmodule下面定义N为8,对一个脉冲8分频,测试程序如下:`timescale 1ns/1nsmodule testbench;reg reset;reg clk_in;reg[2:0] count;wire clk_out;freq_div_even test(.clk_in(clk_in),.reset(reset),.clk_out(clk_out));initialbeginreset=0;clk_in=0;#5 reset=1;endalways #10 clk_in=~clk_in;endmodule波形图如下:2、奇数分频对于对占空比没有特殊要求的奇数分频,需要对上升沿和下降沿脉冲进行计数,利用下降沿产生的波形移相半个输入脉冲的作用,最后用错位“异或”法实现。

矿产资源开发利用方案编写内容要求及审查大纲

矿产资源开发利用方案编写内容要求及《矿产资源开发利用方案》审查大纲一、概述

㈠矿区位置、隶属关系和企业性质。

如为改扩建矿山, 应说明矿山现状、

特点及存在的主要问题。

㈡编制依据

(1简述项目前期工作进展情况及与有关方面对项目的意向性协议情况。

(2 列出开发利用方案编制所依据的主要基础性资料的名称。

如经储量管理部门认定的矿区地质勘探报告、选矿试验报告、加工利用试验报告、工程地质初评资料、矿区水文资料和供水资料等。

对改、扩建矿山应有生产实际资料, 如矿山总平面现状图、矿床开拓系统图、采场现状图和主要采选设备清单等。

二、矿产品需求现状和预测

㈠该矿产在国内需求情况和市场供应情况

1、矿产品现状及加工利用趋向。

2、国内近、远期的需求量及主要销向预测。

㈡产品价格分析

1、国内矿产品价格现状。

2、矿产品价格稳定性及变化趋势。

三、矿产资源概况

㈠矿区总体概况

1、矿区总体规划情况。

2、矿区矿产资源概况。

3、该设计与矿区总体开发的关系。

㈡该设计项目的资源概况

1、矿床地质及构造特征。

2、矿床开采技术条件及水文地质条件。