算术和逻辑指令

ADC : 带进位的加法

(Ad dition with C arry)

ADC{条件}{S}

dest = op_1 + op_2 + carry

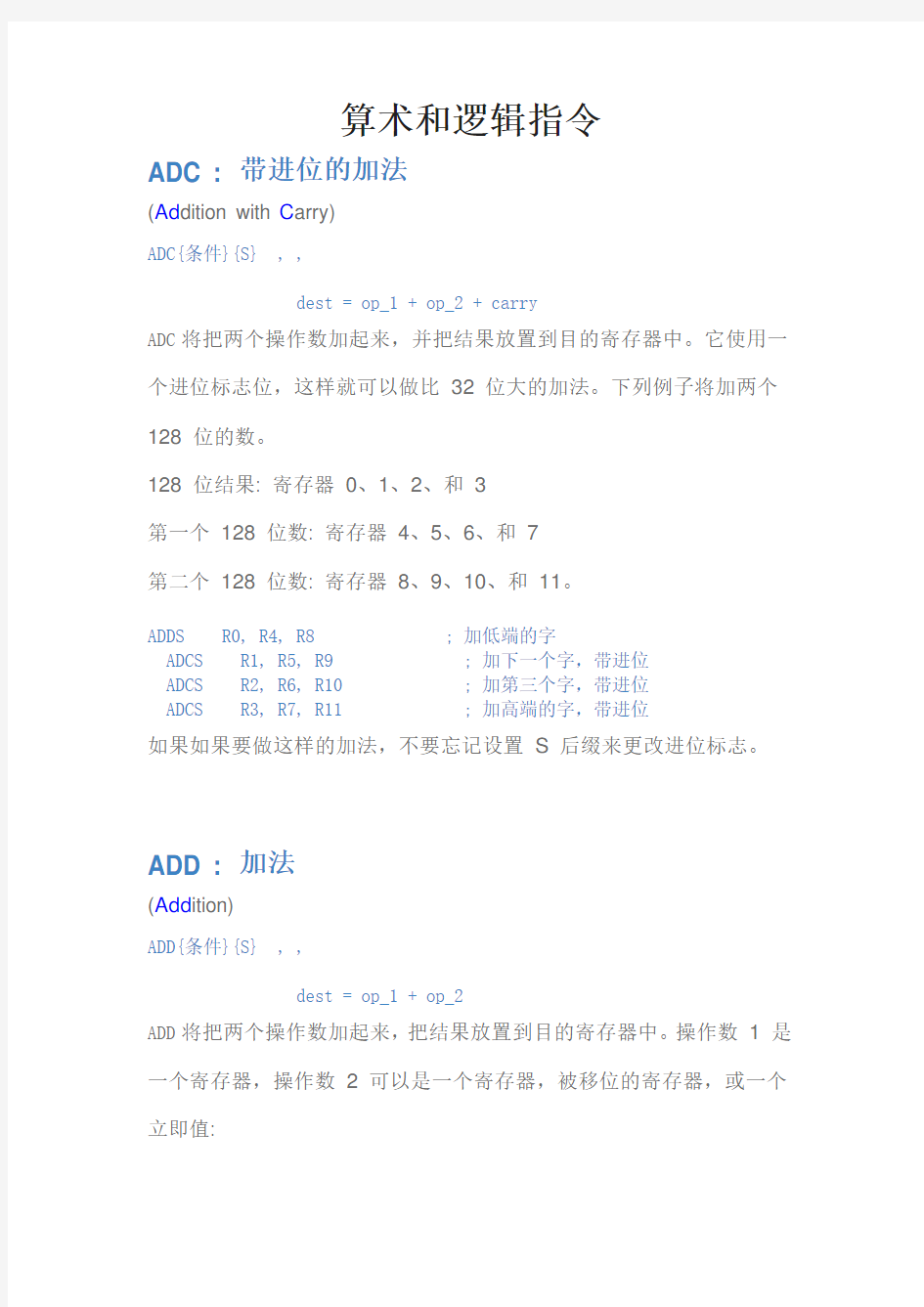

ADC将把两个操作数加起来,并把结果放置到目的寄存器中。它使用一个进位标志位,这样就可以做比 32 位大的加法。下列例子将加两个128 位的数。

128 位结果: 寄存器0、1、2、和 3

第一个 128 位数: 寄存器4、5、6、和 7

第二个 128 位数: 寄存器8、9、10、和 11。

ADDS R0, R4, R8 ; 加低端的字

ADCS R1, R5, R9 ; 加下一个字,带进位

ADCS R2, R6, R10 ; 加第三个字,带进位

ADCS R3, R7, R11 ; 加高端的字,带进位

如果如果要做这样的加法,不要忘记设置 S 后缀来更改进位标志。

ADD : 加法

(Add ition)

ADD{条件}{S}

dest = op_1 + op_2

ADD将把两个操作数加起来,把结果放置到目的寄存器中。操作数 1 是一个寄存器,操作数 2 可以是一个寄存器,被移位的寄存器,或一个立即值:

ADD R0, R1, R2 ; R0 = R1 + R2

ADD R0, R1, #256 ; R0 = R1 + 256

ADD R0, R2, R3,LSL#1 ; R0 = R2 + (R3 << 1)

加法可以在有符号和无符号数上进行。

AND : 逻辑与

(logical AND)

AND{条件}{S}

dest = op_1 AND op_2

AND将在两个操作数上进行逻辑与,把结果放置到目的寄存器中;对屏蔽你要在上面工作的位很有用。操作数 1 是一个寄存器,操作数 2 可以是一个寄存器,被移位的寄存器,或一个立即值:

AND R0, R0, #3 ; R0 = 保持 R0 的位 0 和 1,丢弃其余的位。

AND 的真值表(二者都是 1 则结果为 1):

Op_1 Op_2 结果

0 0 0

0 1 0

1 0 0

1 1 1

BIC : 位清除

(Bi t C lear)

BIC{条件}{S}

dest = op_1 AND (!op_2)

BIC是在一个字中清除位的一种方法,与 OR 位设置是相反的操作。操作数 2 是一个 32 位位掩码(mask)。如果如果在掩码中设置了某一位,则清除这一位。未设置的掩码位指示此位保持不变。

BIC R0, R0, #%1011 ; 清除 R0 中的位 0、1、和 3。保持其余的不变。

BIC 真值表 :

Op_1 Op_2 结果

0 0 0

0 1 0

1 0 1

1 1 0

译注:逻辑表达式为 Op_1 AND NOT Op_2

EOR : 逻辑异或

(logical E xclusive OR)

EOR{条件}{S}

dest = op_1 EOR op_2

EOR将在两个操作数上进行逻辑异或,把结果放置到目的寄存器中;对反转特定的位有用。操作数 1 是一个寄存器,操作数 2 可以是一个寄存器,被移位的寄存器,或一个立即值:

EOR R0, R0, #3 ; 反转 R0 中的位 0 和 1

EOR 真值表(二者不同则结果为 1):

Op_1 Op_2 结果

0 0 0

0 1 1

1 0 1

1 1 0

MOV : 传送

(Mov e)

MOV{条件}{S}

dest = op_1

MOV从另一个寄存器、被移位的寄存器、或一个立即值装载一个值到目的寄存器。你可以指定相同的寄存器来实现 NOP 指令的效果,你还可以专门移位一个寄存器:

MOV R0, R0 ; R0 = R0... NOP 指令

MOV R0, R0, LSL#3 ; R0 = R0 * 8

如果 R15 是目的寄存器,将修改程序计数器或标志。这用于返回到调用代码,方法是把连接寄存器的内容传送到 R15:

MOV PC, R14 ; 退出到调用者

MOVS PC, R14 ; 退出到调用者并恢复标志位

(不遵从 32-bit 体系)

MVN : 传送取反的值

(M o v e N egative)

MVN{条件}{S}

dest = !op_1

MVN从另一个寄存器、被移位的寄存器、或一个立即值装载一个值到目的寄存器。不同之处是在传送之前位被反转了,所以把一个被取反的值传送到一个寄存器中。这是逻辑非操作而不是算术操作,这个取反的值加 1 才是它的取负的值:

MVN R0, #4 ; R0 = -5

MVN R0, #0 ; R0 = -1

ORR : 逻辑或

(logical OR)

ORR{条件}{S}

dest = op_1 OR op_2

OR将在两个操作数上进行逻辑或,把结果放置到目的寄存器中;对设置特定的位有用。操作数 1 是一个寄存器,操作数 2 可以是一个寄存器,被移位的寄存器,或一个立即值:

ORR R0, R0, #3 ; 设置 R0 中位 0 和 1

OR 真值表(二者中存在 1 则结果为 1):

Op_1 Op_2 结果

0 0 0

0 1 1

1 0 1

1 1 1

RSB : 反向减法

(R everse S u b traction)

RSB{条件}{S}

dest = op_2 - op_1

SUB用操作数two 减去操作数one,把结果放置到目的寄存器中。操作数 1 是一个寄存器,操作数 2 可以是一个寄存器,被移位的寄存器,或一个立即值:

RSB R0, R1, R2 ; R0 = R2 - R1

RSB R0, R1, #256 ; R0 = 256 - R1

RSB R0, R2, R3,LSL#1 ; R0 = (R3 << 1) - R2

反向减法可以在有符号或无符号数上进行。

RSC : 带借位的反向减法

(R everse S ubtraction with C arry)

RSC{条件}{S}

dest = op_2 - op_1 - !carry

同于SBC,但倒换了两个操作数的前后位置。

SBC : 带借位的减法

(S u b traction with C arry)

SBC{条件}{S}

dest = op_1 - op_2 - !carry

SBC做两个操作数的减法,把结果放置到目的寄存器中。它使用进位标志来表示借位,这样就可以做大于 32 位的减法。SUB和SBC生成进位标志的方式不同于常规,如果需要借位则清除进位标志。所以,指令要对进位标志进行一个非操作 - 在指令执行期间自动的反转此位。

SUB : 减法

(Sub traction)

SUB{条件}{S}

dest = op_1 - op_2

SUB用操作数one 减去操作数 two,把结果放置到目的寄存器中。操作数 1 是一个寄存器,操作数 2 可以是一个寄存器,被移位的寄存器,或一个立即值:

SUB R0, R1, R2 ; R0 = R1 - R2

SUB R0, R1, #256 ; R0 = R1 - 256

SUB R0, R2, R3,LSL#1 ; R0 = R2 - (R3 << 1)

减法可以在有符号和无符号数上进行。

移位指令

ARM 处理器组建了可以与数据处理指令(ADC、ADD、AND、BIC、CMN、CMP、EOR、MOV、MVN、ORR、RSB、SBC、SUB、TEQ、TST)一起使用的桶式移位器(barrel shifter)。你还可以使用桶式移位器影响在 LDR/STR 操作中的变址值。

译注:移位操作在 ARM 指令集中不作为单独的指令使用,它是指令格式中是一个字段,在汇编语言中表示为指令中的选项。如果数据处理指令的第二个操作数或者单一数据传送指令中的变址是寄存器,则可以对它进行各种移位操作。如果数据处理指令的第二个操作数是立即值,在指令中用 8 位立即值和 4 位循环移位来表示它,所以对大于 255 的立即值,汇编器尝试通过在指令中设置循环移位数量来表示它,如果不能表示则生成一个错误。在逻辑类指令中,逻辑运算指令由指令中 S 位的设置或清除来确定是否影响进位标志,而比较指令的 S 位总是设置的。在单一数据传送指令中指定移位的数量只能用立即值而不能用寄存器。

下面是给不同的移位类型的六个助记符:

LSL 逻辑左移

ASL 算术左移

LSR 逻辑右移

ASR 算术右移

ROR 循环右移

RRX 带扩展的循环右移

ASL和LSL是等同的,可以自由互换。

你可以用一个立即值(从 0 到 31)指定移位数量,或用包含在 0 和 31 之间的一个值的寄存器指定移位数量。

逻辑或算术左移

(L ogical or A rithmetic S hift L eft)

Rx, LSL #n or

Rx, ASL #n or

Rx, LSL Rn or

Rx, ASL Rn

接受 Rx 的内容并按用‘n’或在寄存器 Rn 中指定的数量向高有效位方向移位。最低有效位用零来填充。除了概念上的第 33 位(就是被移出的最小的那位)之外丢弃移出最左端的高位,如果逻辑类指令中 S 位被设置了,则此位将成为从桶式移位器退出时进位标志的值。

考虑下列:

MOV R1, #12

MOV R0, R1, LSL#2

在退出时,R0 是 48。这些指令形成的总和是R0 = #12, LSL#2等同于BASIC 的R0 = 12 << 2

逻辑右移

(L ogical S hift R ight)

Rx, LSR #n or

Rx, LSR Rn

它在概念上与左移相对。把所有位向更低有效位方向移动。如果逻辑类指令中 S 位被设置了,则把最后被移出最右端的那位放置到进位标志中。它同于 BASIC 的register = value >>> shift。

算术右移

(A rithmetic S hift R ight)

Rx, ASR #n or

Rx, ASR Rn

类似于 LSR,但使用要被移位的寄存器(Rx)的第 31 位的值来填充高位,用来保护补码表示中的符号。如果逻辑类指令中 S 位被设置了,则把最后被移出最右端的那位放置到进位标志中。它同于 BASIC

的register = value >> shift。

循环右移

(Ro tate R ight)

Rx, ROR #n or

Rx, ROR Rn

循环右移类似于逻辑右移,但是把从右侧移出去的位放置到左侧,如果逻辑类指令中 S 位被设置了,则同时放置到进位标志中,这就是位的‘循环’。一个移位量为 32 的操作将导致输出与输入完全一致,因为所有位都被移位了 32 个位置,又回到了开始时的位置!

带扩展的循环右移

(R otate R ight with e x tend)

Rx, RRX

这是一个 ROR#0 操作,它向右移动一个位置 - 不同之处是,它使用处理器的进位标志来提供一个要被移位的 33 位的数量。

乘法指令

指令格式

这两个指令与普通算术指令在对操作数的限制上有所不同:

1. 给出的所有操作数、和目的寄存器必须为简单的寄存器。

2. 你不能对操作数 2 使用立即值或被移位的寄存器。

3. 目的寄存器和操作数 1 必须是不同的寄存器。

4. 最后,你不能指定 R15 为目的寄存器。

MLA : 带累加的乘法

(M ultip l ication with A ccumulate)

MLA{条件}{S}

dest = (op_1 * op_2) + op_3

MLA的行为同于MUL,但它把操作数 3 的值加到结果上。这在求总和时有用。

MUL : 乘法

(Mul tiplication)

MUL{条件}{S}

dest = op_1 * op_2

MUL提供 32 位整数乘法。如果操作数是有符号的,可以假定结果也是有符号的。

比较指令

指令格式

译注:CMP 和 CMP 是算术指令,TEQ 和 TST 是逻辑指令。把它们归入一类的原因是它们的 S 位总是设置的,就是说,它们总是影响标志位。

CMN : 比较取负的值

(C o m pare N egative)

CMN{条件}{P}

status = op_1 - (- op_2)

CMN同于CMP,但它允许你与小负值(操作数 2 的取负的值)进行比较,比如难于用其他方法实现的用于结束列表的 -1。这样与 -1 比较将使用:

CMN R0, #1 ; 把 R0 与 -1 进行比较

详情参照CMP指令。

CMP : 比较

(C o mp are)

CMP{条件}{P}

status = op_1 - op_2

CMP允许把一个寄存器的内容如另一个寄存器的内容或立即值进行比较,更改状态标志来允许进行条件执行。它进行一次减法,但不存储结果,而是正确的更改标志。标志表示的是操作数 1 比操作数 2 如何(大小等)。如果操作数 1 大于操作操作数2,则此后的有 GT 后缀的指令将可以执行。

明显的,你不需要显式的指定S后缀来更改状态标志... 如果你指定了它则被忽略。

TEQ : 测试等价

(T est Eq uivalence)

TEQ{条件}{P}

Status = op_1 EOR op_2

TEQ类似于TST。区别是这里的概念上的计算是 EOR 而不是 AND。这提供了一种查看两个操作数是否相同而又不影响进位标志(不象CMP 那样)的方法。加上P后缀的TEQ还可用于改变 R15 中的标志(在 26-bit 模式中)。详情请参照 psr.html,在 32-bit 模式下如何做请参见这里。

TST : 测试位

(T e st bits)

TST{条件}{P}

Status = op_1 AND op_2

TST类似于CMP,不产生放置到目的寄存器中的结果。而是在给出的两个操作数上进行操作并把结果反映到状态标志上。使用TST来检查是否设置了特定的位。操作数 1 是要测试的数据字而操作数 2 是一个位掩码。经过测试后,如果匹配则设置 Zero 标志,否则清除它。象CMP 那样,你不需要指定S后缀。

TST R0, #%1 ; 测试在 R0 中是否设置了位 0。

分支指令

B : 分支

(B ranch)

B{条件} <地址>

B 是最简单的分支。一旦遇到一个 B 指令,ARM 处理器将立即跳转到给定的地址,从那里继续执行。

注意存储在分支指令中的实际的值是相对当前的 R15 的值的一个偏移量;而不是一个绝对地址。

它的值由汇编器来计算,它是 24 位有符号数,左移两位后有符号扩展为 32 位,表示的有效偏移为 26 位(+/- 32 M)。

在其他处理器上,你可能经常见到这样的指令:

OPT 1

LDA &70

CMP #0

BEQ Zero

STA &72

.Zero RTS

(取自 Acorn Electron User Guide issue 1 page 213)

在 ARM 处理器上,它们将变成下面这些东西:

OPT 1

ADR R1, #&70

LDR R0, [R1]

CMP #0

BEQ Zero

STR R0, [R1, #2]

.Zero

MOV PC, R14

这不是一个很好的例子,但你可以构想如何更好的去条件执行而不是分支。另一方面,如果你有大段的代码或者你的代码使用状态标志,那么你可以使用条件执

行来实现各类分支: 这样一个单一的简单条件执行指令可以替代在其他处理器中存在的所有这些分支和跳转指令。

OPT 1

ADR R1, #&70

LDR R0, [R1]

CMP R0, #0

STRNE R0, [R1, #2]

MOV PC, R14

BL : 带连接的分支

(B ranch with L ink)

BL{条件} <地址>

BL 是另一个分支指令。就在分支之前,在寄存器 14 中装载上 R15 的内容。你可以重新装载 R14 到 R15 中来返回到在这个分支之后的那个指令,

它是子例程的一个基本但强力的实现。它的作用在屏幕装载器 2 (例子 4)中得以很好的展现...

.load_new_format

BL switch_screen_mode

BL get_screen_info

BL load_palette

.new_loop

MOV R1, R5

BL read_byte

CMP R0, #255

BLEQ read_loop

STRB R0, [R2, #1]!

...在这里我们见到在装载器循环之前调用了三个子例程。接着,一旦满足了条件执行就在循环中调用了 read_byte 子例程。

条件执行

ARM 处理器的一个非常特殊的特征是它的条件执行。我们指的不是基本的如果进位则分支,ARM 使这个逻辑阶段进一步深化为如果进位则 XXX - 这里的 XXX 是任何东西。

为了举例,下面是 Intel 8086 处理器分支指令的一个列表:

JA Jump if Above

JAE Jump if Above or Equal

JB Jump if Below

JBE Jump if Below or Equal

JC Jump if Carry

JCXZ Jump if CX Zero (CX is a register that can be used for loop counts) JE Jump if Equal

JG Jump if Greater than

JGE Jump if Greater than or Equal

JL Jump if Less than

JLE Jump if Less Than or Equal

JMP JuMP

JNA Jump if Not Above

JNAE Jump if Not Above or Equal

JNB Jump if Not Below

JNBE Jump if Not Below or Equal

JNC Jump if No Carry

JNE Jump if Not Equal

JNG Jump if Not Greater than

JNGE Jump if Not Greater than or Equal

JNL Jump if Not Less than

JNLE Jump if Not Less than or Equal

JNO Jump if Not Overflow

JNP Jump if Not Parity

JNS Jump if Not Sign

JNZ Jump if Not Zero

JO Jump if Overflow

JP Jump if Parity

JPE Jump if Parity Even

JPO Jump if Parity Odd

JS Jump if Sign

JZ Jump if Zero

80386 添加了:

JECXZ Jump if ECX Zero

作为对比,ARM 处理器只提供了:

B 分支

BL 带连接的分支

但 ARM 提供了条件执行,你可以不受这个表面上不灵活的方式的限制:

BEQ Branch if EQual

BNE Branch if Not Equal

BVS Branch if oVerflow Set

BVC Branch if oVerflow Clear

BHI Branch if HIgher

BLS Branch if Lower or the Same

BPL Branch if PLus

BMI Branch if MInus

BCS Branch if Carry Set

BCC Branch if Carry Clear

BGE Branch if Greater than or Equal

BGT Branch if Greater Than

BLE Branch if Less than or Equal

BLT Branch if Less Than

BLEQ Branch with Link if EQual

....

BLLT Branch with Link if Less Than

还有两个代码,

?AL - ALways,缺省条件所以不须指定

?NV - NeVer,不是非常有用。你无论如何不要使用这个代码...

当你发现所有 Bxx 指令实际上是同一个指令的时候,紧要关头就到了。

接着你会想,如果你可以在一个分支指令上加上所有这些条件,那么对一个寄存器装载指令能否加上它们? 答案是可以。

下面是可获得的条件代码的列表:

EQ : 等于

如果一次比较之后设置了 Z 标志。

NE : 不等于

如果一次比较之后清除了 Z 标志。

VS : 溢出设置

如果在一次算术操作之后设置了 V 标志,计算的结果不适合放入一个

32bit 目标寄存器中。

VC : 溢出清除

如果清除了 V 标志,与 VS 相反。

HI : 高于(无符号)

如果一次比较之后设置了 C 标志并清除了 Z 标志。

LS : 低于或同于(无符号)

如果一次比较操作之后清除了 C 标志或设置了 Z 标志。

PL : 正号

如果一次算术操作之后清除了 N。出于定义‘正号’的目的,零是正数的原因是它不是负数...

MI : 负号

如果一次算术操作之后设置了 N 标志。

CS : 进位设置

如果一次算术操作或移位操作之后设置了 C 标志,操作的结果不能表示为 32bit。你可以把 C 标志当作结果的第 33 位。

CC : 进位清除

与 CS 相反。

GE : 大于或等于(有符号)

如果一次比较之后...

设置了 N 标志并设置了 V 标志

或者...

清除了 N 标志并清除了 V 标志。

GT : 大于(有符号)

如果一次比较之后...

设置了 N 标志并设置了 V 标志

或者...

清除了 N 标志并清除了 V 标志

并且...

清除了 Z 标志。

LE : 小于或等于(有符号)

如果一次比较之后...

设置了 N 标志并清除了 V 标志

或者...

清除了 N 标志并设置了 V 标志

并且...

设置了 Z 标志。

LT : 小于(有符号)

如果一次比较之后...

设置了 N 标志并清除了 V 标志。

或者...

清除了 N 标志并设置了 V 标志。

AL : 总是

缺省条件,所以不用明显声明。

NV : 从不

不是特别有用,它表示应当永远不执行这个指令。是穷人的 NOP。

包含 NV 是为了完整性(与 AL 相对),你不应该在你的代码中使用它。 有一个在最后的条件代码 S,它以相反的方式工作。当用于一个指令的时候,导致更改状态标志。这不是自动发生的 - 除非这些指令的目的是设置状态。例如: ADD R0, R0, R1

ADDS R0, R0, R1

ADDEQS R0, R0, R1

第一个例子是一个基本的加法(把 R1 的值增加到 R0),它不影响状态寄存器。 第二个例子是同一个加法,只不过它导致更改状态寄存器。

最后一个例子是同一个加法,更改状态寄存器。不同在于它是一个有条件的指令。只有前一个操作的结果是 EQ (如果设置了 Z 标志)的时候它才执行。

下面是条件执行的一个工作中的例子。你把寄存器 0 与存储在寄存器 10 中内容相比较。

如果不等于 R10,则调用一个软件中断,增加它并分支回来再次做这些。否则清除 R10 并返回到调用它的那部分代码(它的地址存储在 R14)。

\ 条件执行的一个例子

.loop ; 标记循环开始位置

CMP R0, R10 ; 把 R0 与 R10 相比较

SWINE &40017 ; 不等于: 调用 SWI &40017

ADDNE R0, R0, #1 ; 向 R0 加 1

BNE loop ; 分支到 'loop'

MOV R10, #0 ; 等于 : 设置 R10 为零

LDMFD R13!, {R0-R12,PC} ; 返回到调用者

注解:

?SWI 编号就象我写的这样。在 RISC OS 下,它是给 Econet_DoImmediate 的编号。不要字面的接受它,这只是一个例子!

?你可能以前没见过 LDMFD,它从栈中装载多个寄存器。在这个例子中,我们从一个完全正式的栈中装载 R0 至 R12 和 R14。关于寄存器装载和存储的更多信息请参阅 str.html。

?我说要装载 R14。那么为什么要把它放入 PC 中? 原因是此时 R14 存储的值包含返回地址。我们也可以采用:

? LDMFD R13!, {R0-R12,R14}

? MOV PC, R14

?但是直接恢复到 PC 中可以省略这个 MOV 语句。

?最后,这些寄存器很有可能被一个 SWI 调用所占用(依赖于在调用期间执行的代码),所以你最好把你的重要的寄存器压入栈中,以后在恢复它们。

SWI 指令

SWI : 软件中断

(S oft w are I nterrupt)

SWI{条件} <24 位编号>

指令格式

这是一个简单的设施,但可能是最常用的。多数操作系统设施是用 SWI 提供的。

没有 SWI 的 RISC OS 是不可想象的。

Nava Whiteford 解释了 SWI 是如何工作的(最初在 Frobnicate issue 12?)...

SWI 是什么?

SWI 表示 Software Interrupt。在 RISC OS 中使用 SWI 来访问操作系统例程或第三方生产的模块。许多应用使用模块来给其他应用提供低层外部访问。

SWI 的例子有:

?文件器 SWI,它辅助读写磁盘、设置属性等。

?打印机驱动器 SWI,用来辅助使用打印并行端口。

?FreeNet/Acorn TCP/IP 协议栈 SWI,用 TCP/IP 协议在 Internet 上发送和接收数据。

在以这种方式使用的时候,SWI 允许操作系统拥有一个模块结构,这意味着用来

建立完整的操作系统的所需的代码可以被分割成许多小的部分(模块)和一个模

块处理程序(handler)。

当 SWI 处理程序得到对特定的例程编号的一个请求的时候,它找到这个例程的

位置并执行它,并传递(有关的)任何数据。

它是如何工作的?

首先查看一下如何使用它。一个 SWI 指令(汇编语言)看起来如下:

指令格式:指令{条件}{S} {目的Register},{OP1}, {OP2} "{ }"中的内容可选。即,可以不带条件只有目的寄存器,或 只有目的寄存器和操作数1,也可以同时包含所有选项。“S”决定指令的操作是否影响CPSR中条件标志位的值,当没有S时指令不更新CPSR中条件标志位的值 助记符英文全称示例、功能 跳转指令 B Branch 跳转指令 B Label;程序无条件跳转到标号Label处执行 BL Branch with Link 带返回的跳转指令 BL Label ;当程序无条件跳转到标号Label处执行时,同时将当前的PC值保存到 R14中 BLX Branch with Link and exchange 带返回和状态切换的跳转指令 BLX Label;从ARM指令集跳转到指令中所指定的目标地址,并将处理器的工作状 态有ARM状态切换到Thumb状态,该指令同时将PC的当前内容保存到寄存器R14中BX Branch and exchange 带状态切换的跳转指令 BX Label ;跳转到指令中所指定的目标地址,目标地址处的指令既可以是ARM指 令,也可以是Thumb指令 数据处理MOV Move 数据传送 MOV R1,R0,LSL#3;将寄存器R0的值左移3位后传送到R1 MVN Move NOT 数据非传送 MVN R0,#0 ;将立即数0取反传送到寄存器R0中,完成后R0=-1 CMP Compare 比较指令 CMP R1,R0;将寄存器R1的值与寄存器R0的值相减,并根据结果设置CPSR的 标志位 CMN Compare negative 负数比较指令 CMN R1,R0 ;将寄存器R1的值与寄存器R0的值相加,并根据结果设置CPSR的 标志位 TST Test 位测试指令 TST R1,#0xffe ;将寄存器R1的值与立即数0xffe按位与,并根据结果设置CPSR 的标志位 TEQ Test equivalence 相等测试指令 TEQ R1,R2;将寄存器R1的值与寄存器R2的值按位异或,并根据结果设置CPSR 的标志位 ADD Add 加法运算指令 ADD R0,R2,R3,LSL#1; R0 = R2 + (R3 << 1) ADC Add with carry 带进位加法 ADCS R2,R6,R10; R2 = R6+R10+!C,且更新CPSR的进位标志位 SUB Subtract 减法运算指令 SUB R0,R1,#256; R0 = R1 – 256 SBC Subtract with carry 带进位减法指令 SUBS R0,R1,R2 ; R0 = R1 - R2 - !C,并根据结果设置CPSR的进位标志位RSB Reverse subtract 逆向减法指令 RSB R0,R1,R2 ; R0 = R2 – R1 RSC Reverse subtract with carry 带进位逆向减法指令 RSC R0,R1,R2; R0 = R2 – R1 - !C AND And 逻辑与操作指令 AND R0,R0,#3;该指令保持R0的0、1位,其余位清零。 ORR OR 逻辑或操作指令 ORR R0,R0,#3;该指令设置R0的0、1位,其余位保持不变。 EOR Exclusive OR 逻辑异或操作指令 EOR R0,R0,#3 ;该指令反转R0的0、1位,其余位保持不变。 BIC Bit clear 位清除指令 BIC R0,R0,#0b1011;该指令清除 R0 中的位 0、1、和 3,其余的位保持不变。CLZ Count left zero 计算操作数最高端0的个数 乘加指令 MUL Multiply 32位乘法指令 MUL R0,R1,R2 ;R0 = R1 × R2 MLA Multiply and accumulate 32位乘加指令 MLAS R0,R1,R2,R3;R0 = R1 × R2 + R3,同时设置CPSR中的相关条件标志位SMULL Signed multiply long 64位有符号数乘法指令 SMULL R0,R1,R2,R3;R0 = (R2 × R3)的低32位 R1 = (R2 × R3)的 高32位

汇编知识点的要求: 1、能看的懂 2、可以做修改 3、不需要用汇编直接编写程序 汇编代码的应用场合: 1、ARM的启动代码必须要汇编,如:uboot最开始初始化硬件的代码 2、内核在最开始初始化的位置。。。。 一、ARM汇编指令的编码格式 1、编码格式 ARM汇编指令编译成机器码以后,机器码的长度是32bits,这32bits的编码有一个固定的格式。不同ARM 汇编指令,编码格式不同。 2、举例 C: if(a==10) a++; else a--;

汇编1: CMP R0, #10; ADDEQ R0,R0,#1 SUBNE R0,R0,#1 汇编2 SUBS R1, R0, #10; //S ---运算的结果会影响条件码标志位:CPSR:NZCV ADDEQ R0,R0,#1 SUBNE R0,R0,#1 提示: 空指令NOP,实际上是占用CPU的时间,但是执行后,没有什么意义。 NOP ---- MOV R0,R0 3、条件码标识 10 -10 Z = 1 C = 0 N = 0 V = 0 ================================================================================= 二、ARM的寻址方式 1、立即数寻址 操作数,有立即数。 ADD R0,R0,#1

MOV R1,#10 ORR R1,R1,#0xf @ R1=R1 | 0xf BIC R1,R1,#0xf @R1 = R1&(~(0xf)) 错误: ADD R1,#1,#2 注意:立即数合法的条件 在ARM汇编指令中,并不是所有的立即数,立即数是有一定的限制的。 什么样的立即数是合法的??? 1、如果一个立即数是小于256的(即该立即数是8bits以内的,0~255),该立即数是合法的。 2、如果一个立即数是大于等于256,该立即数经过循环左移偶数位,可以得到一个小于256的数,则该立即数合法。 256 = 0x100 ------→左移20位0x10000000----→左移4 0x1 合法 0x111 非法 0x102 非法 0x104 合法 0xfff 0xff00 0x12000 0x450000 0xab 原因: 在数据处理指令编码的时候,立即数用12bits来表示: 高4bits:循环左移左移偶数位除以2 低8bits:循环左移后的结果。 重要问题: ADD R1,R0,#0xffff 非法 解决: LDR R2,=0xffff // R2=0xffff,将立即数0xffff的值传送给R2 ADD R1, R0, R2 2、寄存器寻址 所有的操作数都是寄存器,没有立即数 ADD R0,R0,R1 MOV R1,R0 ORR R1,R1,R0 @ R1=R1 | 0xf BIC R1,R1,R0 @R1 = R1&(~(0xf))

标题:Thumb指令集与ARM指令集的区别 2010-06-21 21:43:58 Thumb指令集 Thumb指令可以看做是ARM指令压缩形式的子集,是针对代码密度【1】的问题而提出的,它具有16为的代码密度。Thumb不是一个完整的体系结构,不能指望处理程序只执行Thumb指令而不支持ARM指令集。因此,Thumb指令只需要支持通用功能,必要时,可借助完善的ARM指令集,例如:所有异常自动进入ARM状态。 在编写Thumb指令时,先要使用伪指令CODE16声明,而且在ARM指令中要使用BX指令跳转到Thumb指令,以切换处理器状态。编写ARM指令时,可使用伪指令CODE32声明。 【1】.代码密度:单位存储空间中包含的指令的个数。例如 ARM指令是32位的,而Thumb指令时16位的,如果在1K 的存储空间中,可以放32条ARM指令,就可以放64条Thumb指令,因此在存放Thunb指令时,代码密度高。 Thumb指令集与ARM指令集的区别 Thumb指令集没有协处理器指令、信号量指令以及访问CPSR或SPSR的指令,没有乘加指令及64位乘法指令等,且指令的第二操作数受到限制;除了跳转指令B有条件执行功能外,其他指令均为无条件执行;大多数Thumb数据处理指令采用2地址格式。Thumb指令集与ARM指令集的区别一般有如下几点: ? 跳转指令 程序相对转移,特别是条件跳转与ARM代码下的跳转相比,在范围上有更多的限制,转向子程序是无条件的转移。 ? 数据处理指令

数据处理指令是对通用寄存器进行操作,在大多数情况下,操作的结果须放入其中一个操作数寄存器中,而不是第三个寄存器中。 数据处理操作比ARM状态的更少,访问寄存器R8—R15受到一定限制。 (除MOV和ADD指令访问寄存器R8—R15外,其他数据处理指令总是更新CPSR中ALU状态标志) 访问寄存器R8—R15的Thumb数据处理指令不能更新CPSR中的ALU状态标志 ? 单寄存器加载和存储指令 在Thumb状态下,单寄存器加载和存储指令只能访问寄存器 R0—R7 ? 批量寄存器加载和存储指令 LDM和STM指令可以将任何范围为R0——R7的寄存器子集加载或存储

目录 一、跳转指令 (4) 1、B指令 (4) 2、BL指令 (4) 3、BLX指令 (4) 4、BX指令 (5) 二、数据处理指令 (5) 1、MOV指令 (5) 2、MVN指令 (5) 3、CMP指令 (6) 4、CMN指令 (6) 5、TST指令 (6) 6、TEQ指令 (7) 7、ADD指令 (7) 8、ADC指令 (7) 9、SUB指令 (7) 10、~~~~C指令 (8) 11、R~~~~指令 (8) 12、RSC指令 (8) 13、AND指令 (9) 14、ORR指令 (9) 15、EOR指令 (9) 16、BIC指令 (9) 三、法指令与乘加指令 (10) 1、MUL指令 (10) 2、MLA指令 (10) 3、SMULL指令 (10) 4、SMLAL指令 (11) 5、UMULL指令 (11) 6、UMLAL指令 (11) 四、程序状态寄存器访问指令 (12) 1、MRS指令 (12) 2、MSR指令 (12) 五、加载/存储指令 (12) 1、LDR指令 (12) 2、LDRB指令 (13) 3、LDRH指令 (14) 4、STR指令 (14) 5、STRB指令 (14) 6、STRH指令 (15) 六、批量数据加载/存储指令 (15) LDM(或STM)指令 (15)

IA (15) IB (15) DA (15) DB (15) FD (15) ED (15) FA (15) EA (15) 七、数据交换指令 (16) 1、SWP指令 (16) 2、SWPB指令 (16) 八、移位指令(操作) (16) 1、LSL(或ASL) (17) 2、LSR (17) 3、ASR (17) 4、ROR (17) 5、RRX (17) 九、协处理器指令 (18) 1、CDP指令 (18) 2、LDC指令 (18) 3、STC指令 (18) 4、MCR指令 (19) 5、MRC指令 (19) 十、异常产生指令 (19) 1、SWI指令 (19) 2、BKPT指令 (20) 一、符号定义(Symbol Definition)伪指令 (20) 1、GBLA、GBLL和GBLS (20) 2、LCLA、LCLL和LCLS (21) 3、SETA、SETL和SETS (22) 4、RLIST (22) 二、数据定义(Data Definition)伪指令 (23) 1、DCB (23) 2、DCW(或DCWU) (23) 3、DCD(或DCDU) (24) 4、DCFD(或DCFDU) (24) 5、DCFS(或DCFSU) (25) 6、DCQ(或DCQU) (25) 7、SPACE (25) 8、MAP (26) 9、FILED (26) 三、汇编控制(Assembly Control)伪指令 (27) 1、IF、ELSE、ENDIF (27) 2、WHILE、WEND (28)

ARM指令集 ARM指令集由数据处理指令、跳转指令、Load/Store指令、程序状态寄存器指令、协处理 器指令和软件中断指令六大类构成。 1、数据处理指令 指令格式功能举例 MOV 数据传送指令MOV{

算术和逻辑指令 ADC : 带进位的加法 (Ad dition with C arry) ADC{条件}{S}

ADD R0, R1, R2 ; R0 = R1 + R2 ADD R0, R1, #256 ; R0 = R1 + 256 ADD R0, R2, R3,LSL#1 ; R0 = R2 + (R3 << 1) 加法可以在有符号和无符号数上进行。 AND : 逻辑与 (logical AND) AND{条件}{S}

好东西,说得非常详细的。要做底层的可以看看 ARM指令集详解 发布: 2010-3-19 11:42 | 作者: Saiu | 来源: MCU嵌入式领域 ARM可以用两套指令集:ARM指令集和Thumb指令集。本文介绍ARM指令集。在介绍ARM指令集之前,先介绍指令的格式。 1 指令格式 (1)基本格式

ARM指令和指令系统: 指令是指示计算机某种操作的命令,指令的集合称为指令系统。指令系统的功能强弱很大程度上决定了这类计算机智能的高低,它集中地反应了微处理器的硬件功能和属性。 ARM指令在机器中的表示格式是用32位的二进制数表示。如ARM中有一条指令为ADDEQS R0,R1,#8; 其二进制代码形式为: 31~28 | 27~25 | 24~21 | 20 | 19~16 | 15~12 | 11~0 0000 | 001 | 0100 | 1 | 0001 | 0000 | 0000 0000 1000 cond |opcode | Rn | Rd | Op2 ARM指令格式一般如下:

ARM指令集详解 ARM可以用两套指令集:ARM指令集和Thumb指令集。本文介绍ARM指令集。在介绍ARM指令集之前,先介绍指令的格式。 1 指令格式 (1)基本格式

ARM指令系统.txt蜜蜂整日忙碌,受到赞扬;蚊子不停奔波,人见人打。多么忙不重要,为什么忙才重要。1.ARM指令的寻址方式有几种?试分别举例说明。 答: 立即数寻址:MOV R0,#15 寄存器寻址:ADD R0,R1,R2 寄存器间接寻址:LDR R0,[R4] 寄存器移位寻址:ADD R0,R1,R2,LSL #1 基址变址寻址:LDR R0,[R1,#4] 多寄存器寻址:LDMIA R0!,{R1-R4} 相对寻址:BL proc ;跳转到子程序proc处执行 … proc MOV R0,#1 堆栈寻址:STMFD R13!,{R0-R4}; LDMFD R13!,{R0-R4}; 2.ARM指令系统对字节、半字、字的存取是如何实现的? LDR/STR 字数据加载/存储指令 LDRB/STRB 字节数据加载/存储指令 LDRH/STRH 半字数据加载/存储指令 LDRSB/LDRSH 有符号数字节/半字加载指令 3.如何从ARM指令集跳转到Thumb指令集? BX指令跳转到指令中所指定的目标地址,并实现状态的切换。 Rm是一个表达目标地址的寄存器。当Rm中的最低位Rm[0]为1时,强制程 序从ARM指令状态跳到Thumb指令状态;当Rm中的最低位Rm[0]为0时, 强制程序从Thumb指令状态跳到ARM指令状态。 4.ARM指令集支持哪几种协处理器指令? CDP LDC STC MCR MRC 5.ARM指令的条件码有多少个?默认条件码是什么? 15个默认条件码是AL 6.ARM指令中的第二操作数有哪几种形式?试举例说明。 寄存器形式 MOV R1,R0 ;将寄存器R0的值传送到寄存器R1 立即数形式 MOV R0,#5 ;将立即数5传送到寄存器R0 被移位的寄存器形式 MOV R1,R0,LSL#3

ARM v7指令集 内容简介:在本文档的汇编语法中,用# 前缀表示立即值,用& 表示十六进制值,用% 表示二进制值,用{花括号} 表示指令中可选的设置字段或位。下面表格中粗体的指令是核心ARM 指令,其他的是值得包含的位和片... 在本文档的汇编语法中,用# 前缀表示立即值,用& 表示十六进制值,用% 表示二进制值,用{花括号} 表示指令中可选的设置字段或位。下面表格中粗体的指令是核心ARM 指令,其他的是值得包含的位和片段、移位选项和汇编器 助记码(mnemonic)... 还列出了协处理器指令。但是用于RISC OS 机器的ARM 处理器不支持协处理器,只在一个可访问的芯片中提供了实际上的协处理器功能。其中包括设置ARM、cache、MMU 的设施,等... 指令意义最早的CPU / 注释 ADC带进位的加法- ADD加法- AND逻辑与- ASL 算术左移这是一个选项,不是指令 ASR 算术右移这是一个选项,不是指令 B分支- BIC位清除- BL带连接的分支- BX 分支到Thumb 代码StrongARM SA1110 ? CDP 协处理器数据操作- CMN比较取负的值- CMP比较值- EOR异或两个值- LDC 装载内存到协处理器- LDM装载多个寄存器- LDR装载寄存器- LDRB装载字节到寄存器- LDRH装载半字到寄存器StrongARM LDRSB装载有符号字节到寄存器StrongARM LDRSH装载有符号半字到寄存器StrongARM LSL 逻辑左移这是一个选项,不是指令 LSR 逻辑右移这是一个选项,不是指令 MCR 协处理器寄存器传送- MLA带累加的乘法- MOV传送值/寄存器到一个寄存器-

常用的ARM指令集 我们知道CPU能直接识别的是机器码,也就是0和1组合的东东。不同的组合代表不同的含义,CPU就做不同的事情。按照道理来说,我们写的代码都应该是0和1组成的东西,但是如果真的是那样,那结果....。人类是聪明的,发明了汇编语言,汇编语言是用一些助记符,来代替机器码。当然,汇编语言是不能给CPU识别的,需要编译器将其编译成机器码。 汇编语言是和特定的CPU关联的,不同的CPU对应不同的汇编指令。好在,现在大多数嵌入式CPU都是使用ARM架构的,这样我们只需要学会ARM的汇编指令集,我们写的汇编程序就可以在这些使用ARM架构的CPU上运行。 ARM的汇编指令很多,很难将其全部记住,其实也没必要,我们只需要学会一些常用的ARM汇编指令即可。其他的用到再去查即可。下面我们就开始,必须知道的ARM指令学习。 一、ARM指令格式 ARM指令的基本格式如下: 其中<>号内是必须的,{}号内的项是可选的。 各项的说明如下: opcode :指令助记符 cond :执行条件 S :是否影响CPSR寄存器的值

Rd :目标寄存器(一般用来存放指令执行最后的结果) Rn :第1个操作数的寄存器 operand2 :第2个操作数 1. 其中,我们必须要研究一下operand2这个操作数,它有如下表现形式 (1)#immed_8r——常数表达式 该常数必须对应8位位图,即一个8位的常数通过循环右移偶数位得到,这个数我们也成立即数。 例如: MOV R0,#1 AND R1,R2,#0x0 例如:0x04800000它可以拿0x12循环右移位10位得到,所以它是一个合法的立即数。 有人会问,是不是每次我都要去判断一个数是不是立即数,我就需要从0x00~0xff里面找出一个数,将它循环右移偶数个位看是否能的得到,那太麻烦了。有没有一些快速识别的方法呢?肯定是有的呀,当然也不能完全依赖哦,最好就是拿编译器验证,不是,编译器就会报

常用ARM指令及汇编包括 1、ARM处理器寻址方式 2、指令集介绍 3、伪指令 4、ARM汇编程序设计 5、C与汇编混合编程 ARM处理器寻址方式 1、寄存器寻址:操作数的值在寄存器中,指令中的地址码字段指出的是寄存器编号,指令执行时直接取出寄存器值操作 MOV R1, R2 ;R2->R1 SUB R0, R1,R2 ;R1-R2 -> R0 2、立即寻址:立即寻址指令中的操作码字段后面的地址码部分就是操作数本身,也就是说,数据就包含在指令当中,取出指令就取出了可以立即使用的操作数 SUBS R0,R0,#1 ;R0-1 -> R0 MOV R0,#0xff00 ;0xff00 -> R0 注:立即数要以"#"为前缀,表示16进制数值时以"0x"表示 3、寄存器偏移寻址:是ARM指令集特有的寻址方式,当第2操作数是寄存器偏移方式时,第2个寄存器操作数在与第1个操作数结合之前选择进行移位操作 MOV R0,R2,LSL #3 ;R2的值左移3位,结果存入R0,即R0 = R2 * 8 ANDS R1,R1,R2,LSL R3 ;R2的值左移R3位,然后和R1相与操作,结果放入R1 寄存器偏移寻址可采用的移位操作如下 (1)、LSL(Logical Shift Left)逻辑左移,寄存器中字的低端空出补0 (2)、LSR(Logical Shift Right)逻辑右移,寄存器中字的高端空出补0 (3)、ASR(Arthmetic Shift Right)算术右移,移位中保持符号位不变,即如果源操作数为正数,字高端空出补0,否则补1 (4)、ROR(Rotate Right)循环右移,由字的低端移出的位填入高端空出的位 (5)、RRX(Rotate Right eXtended by 1 place),操作数右移一位,左侧空位由CPSR的C 填充

ARM处理器的指令集 ARM处理器的指令找了好久都没有找到完整版,在这里我把所有用过的ARM指令都整理下来,方便大家参考。 ADC(不更改状态寄存器): 带进位的加法(Addition with Carry) ADCS(更改状态寄存器)R1, R5, R9 ; R1=R5+R9,带进位 ADD : 加法(Addition) ADD R0, R1, #256 ; R0 = R1 + 256 AND : 逻辑与(logical AND) AND R0, R0, #3 ; R0 = 保持R0 的位0和1,丢弃其余的位。 BIC : 位清除(Bit Clear) BIC R0, R0, #%1011 ; 清除R0 中的位0、1、和3。保持其余的不变。 EOR : 逻辑异或(logical Exclusive OR) EOR R0, R0, #3 ; 反转R0 中的位0 和1 MOV : 传送(Move) MOV PC, R14 ; PC=R14 MOVS PC, R14 ; 退出到调用者并恢复标志位(不遵从32-bit 体系) MVN : 传送取反的值(MoveNegative) MVN R0, #4 ; R0 = -5 ORR : 逻辑或(logical OR) ORR R0, R0, #3 ; 设置R0 中位0 和1 RSB : 反向减法(Reverse Subtraction) RSB R0, R1, R2 ; R0 = R2 - R1 RSC : 带借位的反向减法(Reverse Subtraction with Carry) RSC{条件}{S}

ARM汇编指令集 1 跳转指令 1.1 跳转指令B: B LABLE ;跳转到标号LABEL处 B 0X1111 ;跳转到绝对地址0X1111处 1.2 带连接的跳转指令 BL: START … BL NEXT ;跳转到标号NEXT处,同时保存当前PC到R14中 … ;返回地址 … NEXT… ;子程序入口 MOV PC,R14 ;返回 1.3 带状态切换的跳转指令BX: MOV R0, #0X0201 BX R0 ;程序跳转到0x0200处,微处理器切换到Thumb状态(地址必须是4的倍数,否则产生不可预知的后果) 2算术运算指令 2.1不带进位加法指令ADD ADD R0, R1, R2 ;R0← (R1)+(R2) ADD R0, R1, #112 ;R0← (R1)+ 112 ADD R0, R1, R2, LSL #1 ;R0←(R1)+(R2<<1) ;将R2中的值左移1位,再与R1值相加,结果送R0 2.2带进位加法指令 ADC ADDS R0, R3, R6 ;加最低位字节,不带进位 ADCS R1, R4, R7 ;加第二个字,带进位 ADCS R2, R5,R8 ;加第三个字,带进位 ;三句话实现了96bit加法运算,由于ARM寄存器宽度只有32bit所以分三次相加 2.3 不带进位减法指令SUB ;S—进位标志 SUB R0, R1, R2 ;R0←(R1)- (R2) SUB R0, R1, #112 ;R0←(R1)- 112 SUB R0, R1 ,R2 LSL#1 ;R0←(R1)- (R2<<1) 2.4 带进位减法指令SBC SUBS R0, R3, R6 ;减最低位字节,不带进位 SBCS R1, R4, R7 ;减第二个字,带进位 SBCS R2, R5, R8 ;减第三个字,带进位 ;三句话实现了96bit减法运算,由于ARM寄存器宽度只有32bit所以分三次相减