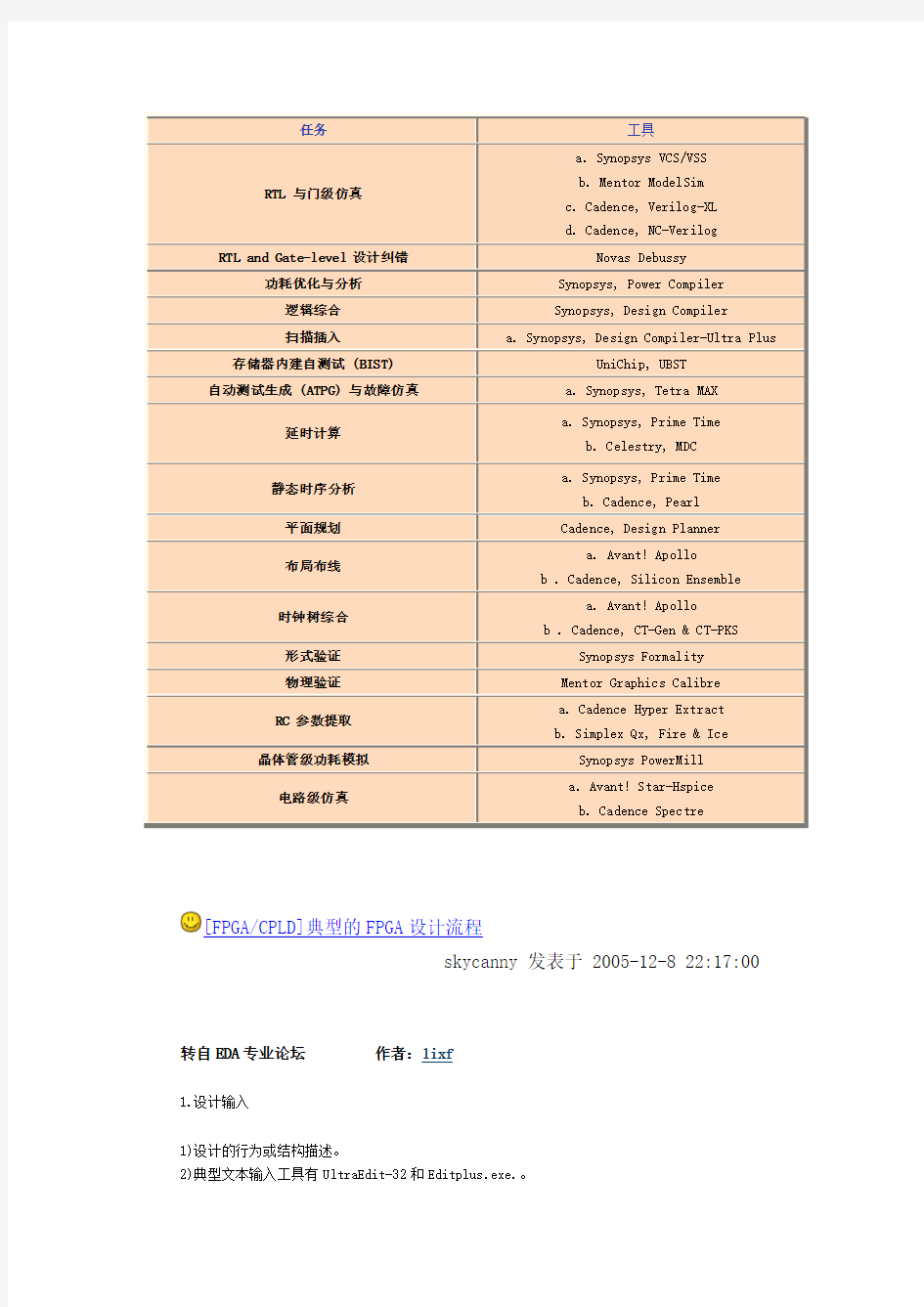

任务工具

RTL 与门级仿真

a. Synopsys VCS/VSS

b. Mentor ModelSim

c. Cadence, Verilog-XL

d. Cadence, NC-Verilog

RTL and Gate-level 设计纠错Novas Debussy

功耗优化与分析Synopsys, Power Compiler 逻辑综合Synopsys, Design Compiler

扫描插入 a. Synopsys, Design Compiler-Ultra Plus 存储器内建自测试 (BIST) UniChip, UBST

自动测试生成 (ATPG) 与故障仿真 a. Synopsys, Tetra MAX

延时计算a. Synopsys, Prime Time

b. Celestry, MDC

静态时序分析a. Synopsys, Prime Time

b. Cadence, Pearl

平面规划Cadence, Design Planner

布局布线

a. Avant! Apollo

b . Cadence, Silicon Ensemble

时钟树综合

a. Avant! Apollo

b . Cadence, CT-Gen & CT-PKS

形式验证Synopsys Formality

物理验证Mentor Graphics Calibre

RC 参数提取a. Cadence Hyper Extract

b. Simplex Qx, Fire & Ice

晶体管级功耗模拟Synopsys PowerMill

电路级仿真a. Avant! Star-Hspice

b. Cadence Spectre

[FPGA/CPLD]典型的FPGA设计流程

skycanny 发表于 2005-12-8 22:17:00

转自EDA专业论坛作者:lixf

1.设计输入

1)设计的行为或结构描述。

2)典型文本输入工具有UltraEdit-32和Editplus.exe.。

3)典型图形化输入工具-Mentor的Renoir。

4)我认为UltraEdit-32最佳。

2.代码调试

1)对设计输入的文件做代码调试,语法检查。

2)典型工具为Debussy。

3.前仿真

1)功能仿真

2)验证逻辑模型(没有使用时间延迟)。

3)典型工具有Mentor公司的ModelSim、Synopsys公司的VCS和VSS、Aldec公司的Active、Ca dense公司的NC。

4)我认为做功能仿真Synopsys公司的VCS和VSS速度最快,并且调试器最好用,Mentor公司的ModelSim对于读写文件速度最快,波形窗口比较好用。

4.综合

1)把设计翻译成原始的目标工艺

2)最优化

3)合适的面积要求和性能要求

4)典型工具有Mentor公司的LeonardoSpectrum、Synopsys公司的DC、Synplicity公司的Synp

lify。

5)推荐初学者使用Mentor公司的LeonardoSpectrum,由于它在只作简单约束综合后的速度和面

积最优,如果你对综合工具比较了解,可以使用Synplicity公司的Synplify。

5.布局和布线

1)映射设计到目标工艺里指定位置

2)指定的布线资源应被使用

3)由于PLD市场目前只剩下Altera,Xilinx,Lattice,Actel,QuickLogic,Atmel六家公司,

其中前5家为专业PLD公司,并且前3家几乎占有了90%的市场份额,而我们一般使用Altera,Xilinx公司的PLD居多,所以典型布局和布线的工具为Altera公司的Quartus II和Maxplus II、Xilinx公司的ISE和Foudation。

4)Maxplus II和Foudation分别为Altera公司和Xilinx公司的第一代产品,所以布局布线一

般使用Quartus II和ISE。

6.后仿真

1)时序仿真

2)验证设计一旦编程或配置将能在目标工艺里工作(使用时间延迟)。

3)所用工具同前仿真所用软件。

7.时序分析

4)一般借助布局布线工具自带的时序分析工具,也可以使用Synopsys公司的 PrimeTime软件和

Mentor Graphics公司的Tau timing analysis软件。

8.验证合乎性能规范1)验证合乎性能规范,如果不满足,回到第一步。

9.版图设计1)验证版版图设计。2)在板编程和测试器件。

(注:本资料素材和资料部分来自网络,仅供参考。请预览后才下载,期待你的好评与关注!)

UED设计流程及方法 “用户体验设计”无疑是这两年互联网行业最炙手可热的话题,而从我们成都UCD书友会火爆的现场来看,也的确如此。那么“用户体验设计”为什么会如此火爆呢?这需要从互联网的Web2.0革命说起。 这场革命,代表了互联网应用关注焦点的变迁,从以内容为王的门户型网站时代,转变为以用户为中心的互联网服务时代。以用户为中心的互联网服务,自然就需要以用户为中心的设计。但是要做到真正的以用户为中心的设计却并不简单。 这是什么意思呢?我想用彩程的实际经历对这个问题做出解释。和很多其它软件企业一样,彩程也是从一些中小型的企业网站、电子商务网站开发业务启程的。当时我们开发一个电子商务类网站的流程是什么样的呢? 首先会由超级打杂老妖出马,跟客户沟通,套出用户的需求,然后由费西或是老妖自己,三下五除二的搞一个首页出来,拿去给用户确认,用户如果点头,那么ok,开始做首页的html切图,然后丢给程序员开始开发,同时,美工继续孤军深入,出各种特征内页,切html,交给程序员开发,如此循环往复。而一旦整个项目开始进行,客户就很少再参与其中了。 于是,这个项目持续运行,直到某一天,程序员说:“好了”,这样,老妖满怀希望的冲到客户那里,很想听到客户对网站认可,但实际的场景往往是: 客户抱怨说,这里我明明是想要个Flash广告,但是却只有一张图片;这个订单系统怎么不好用,为什么不参考淘宝来做呢?我还想要个会员系统,每个会员有自己的个人页面。 这个时候,可怜的老妖只能作出两种选择,要么照单全收,ok,哪里有问题我给你改哪里,要么就是耍死皮,但是后面一种情况一般不会出现,因为老妖不愿因为得罪客户而丢掉奶粉钱。所以,这个原本大家都认为很简单的网站项目就这样被delay下去了。 这样的情况出现的次数多了,让公司首脑小s同学很不满意,于是他开始召集大家思考,这是为什么呢?让我们来看看之前我们的流程:

IC设计完整流程及工具 IC的设计过程可分为两个部分,分别为:前端设计(也称逻辑设计)和后端设计(也称物理设计),这两个部分并没有统一严格的界限,凡涉及到与工艺有关的设计可称为后端设计。 前端设计的主要流程: 1、规格制定 芯片规格,也就像功能列表一样,是客户向芯片设计公司(称为Fabless,无晶圆设计公司)提出的设计要求,包括芯片需要达到的具体功能和性能方面的要求。 2、详细设计 Fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。 3、HDL编码 使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码。 4、仿真验证 仿真验证就是检验编码设计的正确性,检验的标准就是第一步制定的规格。看设计是否精确地满足了规格中的所有要求。规格是设计正确与否的黄金标准,一切违反,不符合规格要求的,就需要重新修改设计和编码。设计和仿真验证是反复迭代的过程,直到验证结果显示完全符合规格标准。仿真验证工具Mentor公司的Modelsim,Synopsys的VCS,还有Cadence的NC-Verilog均可以对RTL级的代码进行设计验证,该部分个人一般使用第一个-Modelsim。该部分称为前仿真,接下来逻辑部分综合之后再一次进行的仿真可称为后仿真。 5、逻辑综合――Design Compiler 仿真验证通过,进行逻辑综合。逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表netlist。综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。逻辑综合需要基于特定的综合库,不同的库中,门电路基

各类三维设计软件介 绍

三维设计软件现在有好多的,不过目前用的最多的是SolidWorks软件。SolidWorks的设计思路十分清晰,设计理念容易理解,模型采用参数化驱动,用数值参数和几何约束来控制三维几何体建模过程,生成三维零件和装配体模型;再根据工程实际需要做出不同的二维视图和各种标注,完成零件工程图和装配工程图。从几何体模型直至工程图的全部设计环节,实现全方位的实时编辑修改,能够应对频繁的设计变更。 PRO/E, 还有MAYA,caxa,sketch up(参数很少,小巧)Auto CAD (三维功能太弱,算不上三维设计软件,平面才是它的天下),SolidWorks,草图大 师,3ds(三维渲染很强) 目前常用三维软件很多,不同行业有不同的软件,各种三维软件各有所长可根据工作需要选择。比较流行的三维软件如:Rhino(Rhinoceros犀牛)、Maya、3ds Max、Softimage/XSI、Lightwave 3D、Cinema 4D、PRO-E等 Maya 是一个包含了许多各种内容的巨大的软件程序。对于一个没有任何使用三维软件程序经验的新用户来说,可能会因为它的内容广泛、复杂而受到打击。对于有一些三维制作经验的用户来说,则可以毫无问题地搞定一切。Maya的工作流程非常得直截了当,与其它的三维程序也没有太大的区别。只需要熟悉一至两个星期,你就会适应Maya的工作环境,因而可以更深一步的探究Maya的各种高级功能,比如节点结构和Mel脚本等。 Softimage/XSI 是一款巨型软件。它的目标是那些企业用户,也就是说,它更适合那些团队合作式的制作环境,而不是那些个人艺术家。籍此原因,我个人认为,这个软件并不特别适合初学者。XSI将电脑的三维动画虚拟能力推向了极至。是最佳的动画工具,除了新的非线性动画功能之外,比之前更容易设定Keyframe的传统动画。是制作电影,广告,3D,建筑表现等方面的强力工具。 Lightwave 对于一个三维领域的新手来说,Lightwave非常容易掌握。因为它所提供的功能更容易使人认为它主要是一个建模软件。对于一个从其它软件转来的初学者,在工具的组织形式上和命名机制上会有一些问题。在Lightwave中,建模工作就像雕刻一样,只需要几天的适应时间,初学者就会对这些工具感到非常地舒服。Lightwave有些特别,它将建模(Modeling:负责建模和贴图)和布局(Layout:动画和特效)分成两大模块来组织,也正是因为这点,丢掉了许多用户。 广泛应用在电影、电视、游戏、网页、广告、印刷、动画等各领域。它的操作简便,易学易用,在生物建模和角色动画方面功能异常强大;基于光线跟踪、光能传递等技术的渲染模块,令它的渲染品质几尽完美。它以其优异性能倍受影视特效制作公司和游戏开发商的青睐。火爆一时的好莱坞大片《TITANIC》中细致逼真的船体模型、《RED PLANET》中的电影特效以及《恐龙危机2》、《生化危机-代号维洛尼卡》等许多经典游戏均由LightWave 3D开发制作完成。 Rhinoceros(Rhino) 是一套专为工业产品及场景设计师所发展的概念设计与模型建构工具,它是第一套将 AGLib NURBS 模型建构技术之强大且完整的能力引进Windows 操作系统的软件,不管您要建构的是汽机车、消费性产品的外型设计或是船壳、机械外装或齿轮、甚至是生物或怪物的外形,Rhino 稳固的技术所提供给使用者的是容易学习与使用、极具弹性及高精确度的模型建构工具。从设计稿、手绘到实际产品,或是只是一个简单的构思,Rhino所提供的曲面工具可以精确地制作所有用来作为彩现、动画、工程图、分析评估以及生产用的模型。Rhino 可以在Windows 的环境下创造、编排或是转译NURBS曲线、表面与实体。在复杂度与尺寸上并没有限制。此外,Rhino并可支持多边网格的制作。 Vue 5 Infinite e-on software公司出品。作为一款为专业艺术家设计的自然景观创作软件,Vue 5 Infinite 提供了强大的性能,整合了所有 Vue 4 Pro 的技术,并新增了超过 110 项的新功能,尤其是 EcoSystem 技术更为创造精细的3D环境提供了无限的可能。Vue 5 Infinite 是几个版本中最有效率,也是在建模、动画、渲染等3D自然环境设计中最高级的解决方案.目前国际界内很多大型电影公司,游戏公司或与景观设计相关的行业都用此软件进行3D自然景观开发. Bryce Bryce是由DAZ推出的一款超强3D自然场景和动画创作软件,它包合了大量自然纹理和物质材质,通过设计与制作能产生极其独特的自然景观。这个革命性的软件在强大和易用中间取得了最优化的平衡,是一个理想的将三维技术融合进您的创作程序的方法,流畅的网络渲染、新的光源效果和树木造型库为您开拓创意的新天堂。全新的网络渲染 - 在网络中渲染一系列动画图像或是单张图片,大大节省时间和金钱。 对于机械行业哪种三维设计软件被最多公司应用。是SolidWorks,UG,PRO-E还是什么。

EDA技术实用教程 第2章 EDA设计流程及其工具

第2章EDA设计流程及其工具本章首先介绍FPGA/CPLD开发 和ASIC设计的流程,然后分别介 绍与这些设计流程中各环节密切 相关的EDA工具软件,最后就 MAX+plusII的基本情况和EDA重 用模块IP作一简述。

原理图/VHDL 文本编辑 综合 FPGA/CPLD 适配 FPGA/CPLD 编程下载 FPGA/CPLD 器件和电路系统 时序与功能门级仿真 1、功能仿真 2、时序仿真 逻辑综合器 结构综合器 1、isp 方式下载 2、JTAG 方式下载 3、针对SRAM 结构的配置 4、OTP 器件编程 功能仿真 2.1 FPGA/CPLD设计流程 应用于FPGA/CPLD 的EDA 开发流程:

2.1.1 设计输入(原理图/HDL文本编辑) 1. 图形输入原理图输入状态图输入波形图输入 2.HDL文本输入 应用HDL的文本输入方法克服了上述原理图输入法存在的所有弊端,为EDA技术的应用和发展打开了一个广阔的天地。 2.1 FPGA/CPLD设计流程

2.1.2 综合 2.1 FPGA/CPLD设计流程 将电路的高级语言转换成低级的,可与FPGA /CPLD 的基本结构相映射的网表文件或程序。 2.1.3 适配 将由综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件,如JEDEC 、Jam 格式的文件。

2.1 FPGA/CPLD设计流程2.1.4 时序仿真与功能仿真 时序仿真功能仿真 2.1.5 编程下载CPLD FPGA 以乘积项结构方式构成以查表法结构方式构成 2.1.6 硬件测试

浅谈数字IC设计技术(一) 摘要:随着数字电路设计的规模以及复杂程度的提高,对其进行设计所花费的时间和费用也随之而提高。根据近年来的统计,对数字系统进行设计所花的时间占到了整个研发过程的60%以上。所以减少设计所花费的实践成本是当前数字电路设计研发的关键,这就必须在设计的方法上有所突破。 关键词:数字系统;IC;设计 一、数字IC设计方法学 在目前CI设计中,基于时序驱动的数字CI设计方法、基于正复用的数字CI设计方法、基于集成平台进行系统级数字CI设计方法是当今数字CI设计比较流行的3种主要设计方法,其中基于正复用的数字CI设计方法是有效提高CI设计的关键技术。它能解决当今芯片设计业所面临的一系列挑战:缩短设计周期,提供性能更好、速度更快、成本更加低廉的数字IC芯片。 基于时序驱动的设计方法,无论是HDL描述还是原理图设计,特征都在于以时序优化为目标的着眼于门级电路结构设计,用全新的电路来实现系统功能;这种方法主要适用于完成小规模ASIC的设计。对于规模较大的系统级电路,即使团队合作,要想始终从门级结构去实现优化设计,也很难保证设计周期短、上市时间快的要求。 基于PI复用的数字CI设计方法,可以满足芯片规模要求越来越大,设计周期要求越来越短的要求,其特征是CI设计中的正功能模块的复用和组合。采用这种方法设计数字CI,数字CI包含了各种正模块的复用,数字CI的开发可分为模块开发和系统集成配合完成。对正复用技术关注的焦点是,如何进行系统功能的结构划分,如何定义片上总线进行模块互连,应该选择那些功能模块,在定义各个功能模块时如何考虑尽可能多地利用现有正资源而不是重新开发,在功能模块设计时考虑怎样定义才能有利于以后的正复用,如何进行系统验证等。基于PI复用的数字CI的设计方法,其主要特征是模块的功能组装,其技术关键在于如下三个方面:一是开发可复用的正软核、硬核;二是怎样做好IP复用,进行功能组装,以满足目标CI的需要;三是怎样验证完成功能组装的数字CI是否满足规格定义的功能和时序。 二、典型的数字IC开发流程 典型的数字CI开发流程主要步骤包含如下24方面的内容: (1)确定IC规格并做好总体方案设计。 (2)RTL代码编写及准备etshtnehc代码。 (3)对于包含存储单元的设计,在RTL代码编写中插入BIST(内建自我测试)电路。 (4)功能仿真以验证设计的功能正确。 (5)完成设计综合,生成门级网表。 (6)完成DFT(可测试设计)设计。 (7)在综合工具下完成模块级的静态时序分析及处理。 (8)形式验证。对比综合网表实现的功能与TRL级描述是否一致。 (9)对整个设计进行Pre一layout静态时序分析。 (10)把综合时的时间约束传递给版图工具。 (11)采样时序驱动的策略进行初始化nooprlna。内容包括单元分布,生成时钟树 (12)把时钟树送给综合工具并插入到初始综合网表。 (13)形式验证。对比插入时钟树综合网表实现的功能与初始综合网表是否一致。 (14)在步骤(11)准布线后提取估计的延迟信息。 (15)把步骤(14)提取出来的延迟信息反标给综合工具和静态时序分析工具。 (16)静态时序分析。利用准布线后提取出来的估计延时信息。 (17)在综合工具中实现现场时序优化(可选项)。

设计流程 IC的设计过程可分为两个部分,分别为:前端设计(也称逻辑设计)和后端设计(也称物理设计),这两个部分并没有统一严格的界限,凡涉及到与工艺有关的设计可称为后端设计。 前端设计的主要流程: 1、规格制定 芯片规格,也就像功能列表一样,是客户向芯片设计公司(称为Fabless,无晶圆设计公司)提出的设计要求,包括芯片需要达到的具体功能和性能方面的要求。 2、详细设计 Fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。 3、HDL编码 使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码。 4、仿真验证 仿真验证就是检验编码设计的正确性,检验的标准就是第一步制定的规格。看设计是否精确地满足了规格中的所有要求。规格是设计正确与否的黄金标准,一切违反,不符合规格要求的,就需要重新修改设计和编码。设计和仿真验证是反复迭代的过程,直到验证结果显示完全符合规格标准。仿真验证工具Mentor公司的Modelsim,Synopsys的VCS,还有Cadence的NC-Verilog均可以对RTL级的代码进行设计验证,该部分个人一般使用第一个-Modelsim。该部分称为前仿真,接下来逻辑部分综合之后再一次进行的仿真可称为后仿真。 5、逻辑综合――Design Compiler

仿真验证通过,进行逻辑综合。逻辑综合的结果就是把设计实现的HDL代码翻译成门 级网表netlist。综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。逻辑综合需要基于特定的综合库,不同的库中,门电路基本标准单元(standard cell)的面积,时序参数是不一样的。所以,选用的综合库不一样,综合出来的电路在时序,面积上是有差异的。一般来说,综合完成后需要再次做仿真验证(这个也称为后仿真,之前的称为前仿真)逻辑综合工具Synopsys的Design Compiler,仿真工具选 择上面的三种仿真工具均可。 6、STA Static Timing Analysis(STA),静态时序分析,这也属于验证范畴,它主要是在时序上对电路进行验证,检查电路是否存在建立时间(setup time)和保持时间(hold time)的违例(violation)。这个是数字电路基础知识,一个寄存器出现这两个时序违例时,是没有办法正确采样数据和输出数据的,所以以寄存器为基础的数字芯片功能肯定会出现问题。STA工具有Synopsys的Prime Time。 7、形式验证 这也是验证范畴,它是从功能上(STA是时序上)对综合后的网表进行验证。常用的就是等价性检查方法,以功能验证后的HDL设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。这样做是为了保证在逻辑综合过程中没有改变原先HDL描述的电路功能。形式验证工具有Synopsys的Formality。前端设计的流程暂时写到这里。从设计程度上来讲,前端设计的结果就是得到了芯片的门级网表电路。 Backend design flow后端设计流程: 1、DFT Design ForTest,可测性设计。芯片内部往往都自带测试电路,DFT的目的就是在设计的时候就考虑将来的测试。DFT的常见方法就是,在设计中插入扫描链,将非扫描单元(如寄存器)变为扫描单元。关于DFT,有些书上有详细介绍,对照图片就好理解一点。DFT工具Synopsys的DFT Compiler

Analog Design Tools Quickly & easily accessible Available online 24/7 1Q 2008

2 https://www.doczj.com/doc/bc16868394.html,/tina-ti T I N A -T I ? TINA-TI ? ? Easy-to-use, powerful analog simulation program based on a PSPICE engine. ? TINA-TI is a fully functional version of TINA, loaded with a library of TI macromodels, including passive and active models. ? Provides support for switching power supply devices.? TINA-TI has no limits to circuit size, numbers of nodes, or numbers of ICs. ? Generates post-simulation results in tables and plots.? Built-In virtual oscilloscope, function generator, and spectrum analyzer.

3ADCPro ? A D C P r o ? https://www.doczj.com/doc/bc16868394.html,/adcpro ? Modular software system for evaluating ADCs without need for expensive logic analyzers. ? Stand-alone tool, suitable for analyzing data sets captured during ADC testing. ? Ability to save and recall data sets. ? Modular design allows additional EVMs and tests to be supported. ? Time, histogram, and frequency domain testing.? ADCPro is able to analyze datasets without any hardware.

在日常工作中,我们经常会需要画流程图,一般来说,大家都会选择使用PPT或者Word文档进行常规的流程图制作,虽然用这些办公软件也可以解一时之急,但终归不够专业方便,还非常费时,那要怎么才能方便快捷的解决问题呢?此时我们需要一个专业的软件来直接制作,这样才可以省时又省力,既方便又美观,分分钟让老板对你刮目相看。 当你对那些简洁美观的流程图感到羡慕不已,是否好奇它们是怎样做出来的,是否想知道需要什么样的专业技能。今天,这一切将变得非常简单,你只需要点击几下鼠标就能制作出属于自己的可视化流程图。而且一切操作都异常简洁。

流程图的基本符号 首先,设计流程图的难点在于对业务逻辑的清晰把握。熟悉整个流程的方方面面。这要求设计者自己对任何活动、事件的流程设计,都要事先对该活动、事件本身进行深入分析,研究内在的属性和规律,在此基础上把握流程设计的环节和时序,做出流程的科学设计。研究内在属性与规律,这是流程设计应该考虑的基本因素。也是设计一个好的流程图的前提条件。

然后再根据事物内在属性和规律进行具体分析,将流程的全过程,按每个阶段的作用、功能的不同,分解为若干小环节,每一个环节都可以用一个进程来表示。在流程图中进程使用方框符号来表达。 既然是流程,每个环节就会有先后顺序,按照每个环节应该经历的时间顺序,将各环节依次排开,并用箭头线连接起来。箭头线在流程图中表示各环节、步骤在顺序中的进展。 对某环节,按需要可在方框中或方框外,作简要注释,也可不作注释。 经常判断是非常重要的,用来表示过程中的一项判定或一个分岔点,判定或分岔的说明写在菱形内,常以问题的形式出现。对该问题的回答决定了判定符号之外引出的路线,每条路线标上相应的回答。 选择好的流程图制作工具 亿图发布第一款支持快捷操作的流程图制作工具从而极大的降低了专业流程设计的门槛,让大多数人可以在很短的时间里绘制出专业的流程图。

1:什么是同步逻辑和异步逻辑?(汉王) 同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。 同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。改变后的状态将一直保持到下一个时钟脉冲的到来,此时无论外部输入x 有无变化,状态表中的每个状态都是稳定的。 异步时序逻辑电路的特点:电路中除可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件,电路中没有统一的时钟,电路状态的改变由外部输入的变化直接引起。 2:同步电路和异步电路的区别: 同步电路:存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化都与所加的时钟脉冲信号同步。 异步电路:电路没有统一的时钟,有些触发器的时钟输入端与时钟脉冲源相连,只有这些触发器的状态变化与时钟脉冲同步,而其他的触发器的状态变化不与时钟脉冲同步。 3:时序设计的实质: 时序设计的实质就是满足每一个触发器的建立/保持时间的要求。 4:建立时间与保持时间的概念? 建立时间:触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间。保持时间:触发器在时钟上升沿到来之后,其数据输入端的数据必须保持不变的最小时间。 5:为什么触发器要满足建立时间和保持时间? 因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在0和1之间变化,这时需要经过一个恢复时间,其输出才能稳定,但稳定后的值并不一定是你的输入值。这就是为什么要用两级触发器来同步异步输入信号。这样做可以防止由于异步输入信号对于本级时钟可能不满足建立保持时间而使本级触发器产生的亚稳态传播到后面逻辑中,导致亚稳态的传播。 (比较容易理解的方式)换个方式理解:需要建立时间是因为触发器的D端像一个锁存器在接受数据,为了稳定的设置前级门的状态需要一段稳定时间;需要保持时间是因为在时钟沿到来之后,触发器要通过反馈来锁存状态,从后级门传到前级门需要时间。 6:什么是亚稳态?为什么两级触发器可以防止亚稳态传播? 这也是一个异步电路同步化的问题。亚稳态是指触发器无法在某个规定的时间段内到达一个可以确认的状态。使用两级触发器来使异步电路同步化的电路其实叫做“一位同步器”,他只能用来对一位异步信号进行同步。两级触发器可防止亚稳态传播的原理:假设第一级触发器的输入不满足其建立保持时间,它在第一个脉冲沿到来后输出的数据就为亚稳态,那么在下一个脉冲沿到来之前,其输出的亚稳态数据在一段恢复时间后必须稳定下来,而且稳定的数据必须满足第二级触发器的建立时间,如果都满足了,在下一个脉冲沿到来时,第二级触发器将不会出现亚稳态,因为其输入端的数据满足其建立保持时间。同步器有效的条件:第一级触发器进入亚稳态后的恢复时间+ 第二级触发器的建立时间< = 时钟周期。

IC设计流程之实现篇——全定制设计 要谈IC设计的流程,首先得搞清楚IC和IC设计的分类。 集成电路芯片从用途上可以分为两大类:通用IC(如CPU、DRAM/SRAM、接口芯片等)和专用IC(ASIC)(Application Specific Integrated Circuit),ASIC是特定用途的IC。从结构上可以分为数字IC、模拟IC和数模混合IC三种,而SOC(System On Chip,从属于数模混合IC)则会成为IC设计的主流。从实现方法上IC设计又可以分为三种,全定制(full custom)、半定制(Semi-custom)和基于可编程器件的IC设计。全定制设计方法是指基于晶体管级,所有器件和互连版图都用手工生成的设计方法,这种方法比较适合大批量生产、要求集成度高、速度快、面积小、功耗低的通用IC或ASIC。基于门阵列(gate-array)和标准单元(standard-cell)的半定制设计由于其成本低、周期短、芯片利用率低而适合于小批量、速度快的芯片。最后一种IC设计方向,则是基于PLD或FPGA器件的IC设计模式,是一种“快速原型设计”,因其易用性和可编程性受到对IC制造工艺不甚熟悉的系统集成用户的欢迎,最大的特点就是只需懂得硬件描述语言就可以使用EDA工具写入芯片功能。从采用的工艺可以分成双极型(bipolar),MOS和其他的特殊工艺。硅(Si)基半导体工艺中的双极型器件由于功耗大、集成度相对低,在近年随亚微米深亚微米工艺的的迅速发展,在速度上对MOS管已不具优势,因而很快被集成度高,功耗低、抗干扰能力强的MOS管所替代。MOSFET工艺又可分为NMOS、PMOS和CMOS三种;其中CMOS工艺发展已经十分成熟,占据IC市场的绝大部分份额。GaAs器件因为其在高频领域(可以在0.35um下很轻松作到10GHz)如微波IC中的广泛应用,其特殊的工艺也得到了深入研究。而应用于视频采集领域的CCD传感器虽然也使用IC一样的平面工艺,但其实现和标准半导体工艺有很大不同。在IC开发中,常常会根据项目的要求(Specifications)、经费和EDA工具以及人力资源、并考虑代工厂的工艺实际,采用不同的实现方法。 其实IC设计这个领域博大精深,所涉及的知识工具领域很广,本系列博文围绕EDA工具展开,以实现方法的不同为主线,来介绍这三种不同的设计方法:全定制、半定制和基于FPGA

. 三维设计软件现在有好多的,不过目前用的最多的是SolidWorks软件。SolidWorks的设计思路十分清晰,设计理念容易理解,模型采用参数化驱动,用数值参数和几何约束来控制三维几何体建模过程,生成三维零件和装配体模型;再根据工程实际需要做出不同的二维视图和各种标注,完成零件工程图和装配工程图。从几何体模型直至工程图的全部设计环节,实现全方位的实时编辑修改,能够应对频繁的设计变更。 PRO/E, 还有MAYA,caxa,sketch up(参数很少,小巧)Auto CAD (三维功能太弱,算不上三维设计软件,平面才是它的天下),SolidWorks,草图大 师,3ds(三维渲染很强) 目前常用三维软件很多,不同行业有不同的软件,各种三维软件各有所长可根据工作需要选择。比较流行的三维软件如:Rhino(Rhinoceros犀牛)、Maya、3ds Max、Softimage/XSI、Lightwave 3D、Cinema 4D、PRO-E等 Maya 是一个包含了许多各种内容的巨大的软件程序。对于一个没有任何使用三维软件程序经验的新用户来说,可能会因为它的内容广泛、复杂而受到打击。对于有一些三维制作经验的用户来说,则可以毫无问题地搞定一切。Maya的工作流程非常得直截了当,与其它的三维程序也没有太大的区别。只需要熟悉一至两个星期,你就会适应Maya的工作环境,因而可以更深一步的探究Maya的各种高级功能,比如节点结构和Mel脚本等。 Softimage/XSI 是一款巨型软件。它的目标是那些企业用户,也就是说,它更适合那些团队合作式的制作环境,而不是那些个人艺术家。籍此原因,我个人认为,这个软件并不特别适合初学者。XSI将电脑的三维动画虚拟能力推向了极至。是最佳的动画工具,除了新的非线性动画功能之外,比之前更容易设定Keyframe的传统动画。是制作电影,广告,3D,建筑表现等方面的强力工具。 Lightwave 对于一个三维领域的新手来说,Lightwave非常容易掌握。因为它所提供的功能更容易使人认为它主要是一个建模软件。对于一个从其它软件转来的初学者,在工具的组织形式上和命名机制上会有一些问题。在Lightwave中,建模工作就像雕刻一样,只需要几天的适应时间,初学者就会对这些工具感到非常地舒服。Lightwave有些特别,它将建模(Modeling:负责建模和贴图)和布局(Layout:动画和特效)分成两大模块来组织,也正是因为这点,丢掉了许多用户。 广泛应用在电影、电视、游戏、网页、广告、印刷、动画等各领域。它的操作简便,易学易用,在生物建模和角色动画方面功能异常强大;基于光线跟踪、光能传递等技术的渲染模块,令它的渲染品质几尽完美。它以其优异性能倍受影视特效制作公司和游戏开发商的青睐。火爆一时的好莱坞大片《TITANIC》中细致逼真的船体模型、《RED PLANET》中的电影特效以及《恐龙危机2》、《生化危机-代号维洛尼卡》等许多经典游戏均由LightWave 3D开发制作完成。 Rhinoceros(Rhino) 是一套专为工业产品及场景设计师所发展的概念设计与模型建构工具,它是第一套将AGLib NURBS 模型建构技术之强大且完整的能力引进Windows 操作系统的软件,不管您要建构的是汽机车、消费性产品的外型设计或是船壳、机械外装或齿轮、甚至是生物或怪物的外形,Rhino 稳固的技术所提供给使用者的是容易学习与使用、极具弹性及高精确度的模型建构工具。从设计稿、手绘到实际产品,或是只是一个简单的构思,Rhino所提供的曲面工具可以精确地制作所有用来作为彩现、动画、工程图、分析评估以及生产用的模型。Rhino 可以在Windows 的环境下创造、编排或是转译NURBS曲线、表面与实体。在复杂度与尺寸上并没有限制。此外,Rhino并可支持多边网格的制作。 Vue 5 Infinite e-on software公司出品。作为一款为专业艺术家设计的自然景观创作软件,Vue 5 Infinite 提供了强大的性能,整合了所有Vue 4 Pro 的技术,并新增了超过110 项的新功能,尤其是EcoSystem 技术更为创造精细的3D环境提供了无限的可能。Vue 5 Infinite 是几个版本中最有效率,也是在建模、动画、渲染等3D自然环境设计中最高级的解决方案.目前国际界内很多大型电影公司,游戏公司或与景观设计相关的行业都用此软件进行3D自然景观开发. Bryce Bryce是由DAZ推出的一款超强3D自然场景和动画创作软件,它包合了大量自然纹理和物质材质,通过设计与制作能产生极其独特的自然景观。这个革命性的软件在强大和易用中间取得了最优化的平衡,是一个理想的将三维技术融合进您的创作程序的方法,流畅的网络渲染、新的光源效果和树木造型库为您开拓创意的新天堂。全新的网络渲染- 在网络中渲染一系列动画图像或是单张图片,大大节省时间和金钱。 对于机械行业哪种三维设计软件被最多公司应用。是SolidWorks,UG,PRO-E还是什么。 NXUG在工业产品中应用广泛,包括汽车、模具、机箱机柜、等等,钣金模块强大,设产品计、开模、数控一条进行 PROE在家用产品行业应用广泛,包括冰箱、洗衣机、电视机等等,软件产品视觉效果很好,产品设计者情有独钟 cait在流体领域应用较多,如飞机、潜艇等,曲面模块强大 SolidWorks贵在综合, AUTOCAD主要用于二维出图。 SolidWorks Pro/E UG同为三维设计软件学哪个最好? Solidworks简单易学,Windows操作界面,很容易上手,但感觉用的时候占内存较多,对电脑配置要求高,它的工程图功能相当强大。 Pro/e相对内存占用稍少,运行较快,功能齐全,便没有前者好学,它也在不断改进操作界面,现在比之前应该好操作一点儿,不过用熟了的话,是感觉不到区别的,主要是对新学者来说。 UG;Solidworks与之是一个内核,没学过,不过看到界面也很友好,应该不难。 最后,其实这些工业设计软件,个人觉得,只要学会一个,其它的可无师自通,有很强的相似性。 SolidWorks易学易用,性价比高,在中国及国外,越来越多的人在学习。好学不代表功能不好。 proe功能比较不错,但汉化不彻底,学起来很费劲。 ug模具方面不错,学起来也超级费劲。价格昂贵, 3D机械模具设计:CATIA,UG,CERO(Proe),Solidedge,Solidworks,inventor 3D工业设计:3ds Max, Maya,Softimage,Solidthinking ;.

软件设计总体思路及主流程图 本系统采用 C 语言编写,主程序主要由四部分构成,系统通电后首先初始化系统,依次完成温度采集、温度处理、数据显示、键盘处理等四项功能。温度采集部分主要完成 4 个温度测试但的温度数据采集任务:温度处理部分主要是将采集到的温度数据与用户设定的各点上下限温度值进行比较处理,并判断是否超出设定的上下限值,如果超出则蜂鸣器报警:数据显示部分主要实现温度数据的显示,显示方式根据设计要求支持 1 到 4 个温度测试点的轮流循环显示和固定显示两种方式:键盘处理部分主要实现用户对系统参数的设置,结合显示部分,实现用户与系统之间的人机接口。系统软件主流程图如下所示:

A/D转换完成中断程序流程图 程序说明: (1)程序实现5次采样,每次检测8个通道 (2)数据的存放格式。 (3)程序的采样周期是通过软件实现的。如果系统处理的人物较多哦,且对 实时性要求较高,则采样中欧器可通过系统扩展8253等定时芯片实现。 A/D转换完成中断功能:将标志位清零,读取转换后的温度数据并存放在RAM中A/D转换完成中断程序流程图如下所示:

肘D 转换完诫中断功昵「将林点拖渭越+渎収黑换启的吐数据井恋做隹RAM '!■_ VD 3 / 6 ■fcA 中斷程序範程SM ■ 丽」、 Tift 1 P 读入甦据 1 标蛊便清爭 > L 「起回) 多路温度测量流程图 LED 显示程序设计 H7-4 转携充成申斷程序灌程醫 B4-3多鮭度测宣电關适程囤

LED显示程序的设计: 动态显示程序流程图如下所示:

测温模块流程图

键盘扫描流程图 按键处理程序通过扫描按键情况,读取键值。主要完成各点温度传感器上下限报警参数设置和显示模式设置。 (1)通过扫描键盘读取键值,流程图如下所示: 4.4?£扫描瀝程国 按键肚理稈序遴过扫推桩键惆况.達取愿值?主要完慮各点温度传感器I- F 股报欝超绘设置和眾示廉试设賈.. <1)通过扫脑僧菠谨取惟惟,流稈图如图卜吝所示; 用1-5谧亂扛折吟已淀吋国

第四章 ISE 6.x 设计工具简介和使用 §4.1概述 本章将详细介绍Xilinx 公司新的高性能设计开发工具ISE(Integrated Software Environment),并以第六版本进行讲解和演示。Xilinx 根据不同的用户,分别提供四种不同功能的设计开发工具:ISE WebPACK,ISE Foundation,ISE BaseX和ISE Alliance。 (1) ISE WebPACK版: 该软件为全免费版,可通过Xilinx网站直接下载。支持包括XC95*/XC95*XL/XC95*XV、CoolRunner XPLA3、CoolRunner-II全系列 CPLD;以及Spartan-II/Spartan-IIE全系列FPGA;Spartan-3系列器件中的XC3S50、XC3S200、XC3S400;Virtex-E部分FPGA(V50E-V300E)器件;Virtex-II部分FPGA(2V40-2V250)器件;Virtex-II Pro部分FPGA(2VP2)器件。集成了XST(Xilinx Synthesis Technology)综合工具。但不支持Core Generator(核生成)工具和PACE(引脚和区域约束编辑器)。 (2) ISE Foundation版: 该软件为完全版。提供了设计开发工具的所有功能.支持Xilinx的全系列逻辑器件产品。并集成了XST(Xilinx Synthesis Technology)综合工具。支持Core Generator(核生成)工具和PACE(引脚和区域约束编辑器)。 (3) ISE BaseX版: 该软件为部分受限版。即支持XC95*/XC95*XL/XC95*XV全系列CPLD; CoolRunner XPLA3全系列CPLD;CoolRunner-II全系列 CPLD;以及Spartan-II/Spartan-IIE全系列FPGA;Spartan-3系列器件中的XC3S50、XC3S200、XC3S400;Virtex/Virtex-E部分FPGA(V50/V50E—V600/V600E)器件;Virtex-II部分FPGA(2V40--2V250)器件;Virtex-II Pro部分FPGA(2VP2、2VP4、2VP7)器件。其他功能与ISE Foundation相同。 (4) ISE Alliance版: 支持Xilinx的全系列逻辑器件产品。但不包含XST(Xilinx Synthesis Technology)综合工具。 此外,在Xilinx最新推出的集成软件环境(ISE)软件ISE 6.1i版和ChipScope Pro 6.1i 版中,可提供比最接近的竞争产品高30%的性能、高25%的逻辑利用率以及低50%的设计成本。并可帮助工程师快速容易地实现时序收敛,从而降低总体设计成本以及整个设计流程所花费的时间。新版本软件允许客户利用Xilinx的下一代增强千兆位 (MultiGigabit)串行I/O 收发器和对采用90nm(纳米)工艺技术的FPGA进行设计。集成了 XPower热能分析软件,能够方便地进行功耗统计和分析。 ISE 6.1i软件还提供了可加强现有可编程设计流程并可适应客户特有设计方法的设计 选项。一种名为高级引脚输出与区域约束编辑器(PACE)的管理工具来简化器件IO规范,包括交互式电压支持和差分对识别指南。ISE Floorplanner(ISE布局规划器)工具中所提供的增量设计、模块化设计、宏生成器和区块规划功能可使设计时间比传统设计方法缩短多达50%。这些都可大大缩短重新编译时间并提供基于小组(team-based)的设计性能优势。ChipScope Pro 6.1i实时验证软件与ISE项目浏览器的集成更为紧密,可更方便地选择和插入验证核心、定义信号监测点,同时为整体设计流程提供实时调试规划能力。新的虚拟

流程图是一种能够帮忙办理者了解实际作业活动的流程图,用于消除作业进程中剩余的作业环节。但是制造作业流程图的软件并不多,或许很多人会挑选用Office Word或PowerPoint来制造,但是这两个软件并非是专业的流程图软件,导致在使用进程中会遇到各种问题,比方线条与方框无法刚好衔接,或许是制造进程冗杂导致体会不佳。 当你对那些简洁美观的流程图感到羡慕不已,是否好奇它们是怎样做出来的,是否想知道需要什么样的专业技能。今天,这一切将变得非常简单,你只需要点击几下鼠标就能制作出属于自己的可视化流程图。而且一切操作都异常简洁。

流程图的基本符号 首先,设计流程图的难点在于对业务逻辑的清晰把握。熟悉整个流程的方方面面。这要求设计者自己对任何活动、事件的流程设计,都要事先对该活动、事件本身进行深入分析,研究内在的属性和规律,在此基础上把握流程设计的环节和时序,做出流程的科学设计。研究内在属性与规律,这是流程设计应该考虑的基本因素。也是设计一个好的流程图的前提条件。

然后再根据事物内在属性和规律进行具体分析,将流程的全过程,按每个阶段的作用、功能的不同,分解为若干小环节,每一个环节都可以用一个进程来表示。在流程图中进程使用方框符号来表达。 既然是流程,每个环节就会有先后顺序,按照每个环节应该经历的时间顺序,将各环节依次排开,并用箭头线连接起来。箭头线在流程图中表示各环节、步骤在顺序中的进展。 对某环节,按需要可在方框中或方框外,作简要注释,也可不作注释。 经常判断是非常重要的,用来表示过程中的一项判定或一个分岔点,判定或分岔的说明写在菱形内,常以问题的形式出现。对该问题的回答决定了判定符号之外引出的路线,每条路线标上相应的回答。 选择好的流程图制作工具 亿图发布第一款支持快捷操作的流程图制作工具从而极大的降低了专业流程设计的门槛,让大多数人可以在很短的时间里绘制出专业的流程图。

2017年数字IC设计工程师招聘面试笔试100 题附答案 1:什么是同步逻辑和异步逻辑?(汉王) 同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。 同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。改变后的状态将一直保持到下一个时钟脉冲的到来,此时无论外部输入x 有无变化,状态表中的每个状态都是稳定的。 异步时序逻辑电路的特点:电路中除可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件,电路中没有统一的时钟,电路状态的改变由外部输入的变化直接引起。 2:同步电路和异步电路的区别: 同步电路:存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化都与所加的时钟脉冲信号同步。 异步电路:电路没有统一的时钟,有些触发器的时钟输入端与时钟脉冲源相连,只有这些触发器的状态变化与时钟脉冲同步,而其他的触发器的状态变化不与时钟脉冲同步。 3:时序设计的实质: 时序设计的实质就是满足每一个触发器的建立/保持时间的要求。

4:建立时间与保持时间的概念? 建立时间:触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间。 保持时间:触发器在时钟上升沿到来之后,其数据输入端的数据必须保持不变的最小时间。 5:为什么触发器要满足建立时间和保持时间? 因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在0和1之间变化,这时需要经过一个恢复时间,其输出才能稳定,但稳定后的值并不一定是你的输入值。这就是为什么要用两级触发器来同步异步输入信号。这样做可以防止由于异步输入信号对于本级时钟可能不满足建立保持时间而使本级触发器产生的亚稳态传播到后面逻辑中,导致亚稳态的传播。 (比较容易理解的方式)换个方式理解:需要建立时间是因为触发器的D端像一个锁存器在接受数据,为了稳定的设置前级门的状态需要一段稳定时间;需要保持时间是因为在时钟沿到来之后,触发器要通过反馈来锁存状态,从后级门传到前级门需要时间。 6:什么是亚稳态?为什么两级触发器可以防止亚稳态传播?