(选做)方案3:4个8位通用寄存器组的设计思路

- 格式:doc

- 大小:60.50 KB

- 文档页数:2

摘要当前,电子信息化高速发展,电子产品成了日常生活中必不可少的一部分。

移位寄存器在大部分电子产品中是必不可少的一部分。

本论文介绍了实现并行存取的四位移位寄存器的设计过程,从电路的构思到整个电路的完成以及其版图的设计都有一个详细的描述。

所设计的寄存器在时钟脉冲的控制下,实现数据的并行输入、并行输出,串行输入并行输出等功能。

整个设计过程全部在LINUX系统下用Cadence软件进行设计的,用Cadence软件进行电路设计并仿真。

最后,利用Cadence软件进行版图的设计,电气规则的检查和LVS的对比匹配验证。

关键词:寄存器;并行存取;版图AbstractAt present, the rapid development of electronic information technology, electronics has become an indispensable part of daily life. Most of the shift register in electronic products is essential. This paper describes the realization of access to the four parallel shift register the design process, from concept to the circuit as a whole circuit of its territory and the completion of the design has a detailed description. The design of the register under the control of the clock, the parallel data input, output parallel, serial input parallel output functions. The entire design process in LINUX system with Cadence software designed and was used Cadence software for circuit design and simulation. Finally, use Cadence software to design the territory, electrical inspection rules and LVS comparison of the match to verify.Key words:register; parallel access; territory目录引言 (1)1 设计要求 (1)2 电路构思及其理论 (1)2.1 设计思路 (1)2.2 设计构思的理论依据 (2)2.2.1 寄存器描述 (2)2.2.2 移位寄存器的特点和分类 (2)3 系统电路的设计及原理说明 (2)3.1 系统框图及说明 (2)3.2 电路设计说明 (3)3.3 关键器件介绍 (4)3.3.1 边沿D触发器 (5)3.3.2 3个二输入与非门构成的选择器 (6)4 仿真验证叙述及效果分析 (6)4.1 电路仿真 (6)4.2电路仿真结果分析 (6)5 工程设计 (7)5.1 Cadence软件介绍 (7)5.2 电路设计 (7)5.3 版图设计及验证 (8)5.3.1 版图设计 (8)5.3.2 版图验证 (9)6 调试测试分析 (10)7 结束语 (10)参考文献 (11)附录 (12)引言当今电子信息化的社会,电子产品在日常生活中随处可见。

思考题:【2-1】80C51单片机由哪几部分组成,试说明ROM和RAM的功能分别是什么?【2-2】在程序运行中,PC的值是。

()A)当前正在执行指令的前一条指令的地址B)当前正在执行指令的地址C)当前正在执行指令的下一条指令的首地址D)控制器中指令寄存器的地址【2-3】判断下列说法是否正确。

(1)PC可以存放一个16位二进制数,因此其寻址范围为0000H~7FFFH。

()(2)单片机系统复位时PC的内容为0000H,因此CPU从程序存储器0000H地址单元取指令,开始执行程序。

()(3)PC可以看成是程序计时器()(4)PC可以看成是程序存储器的地址指针。

()【2-4】试计算当振荡频率为12 MHz和6 MHz时,一个机器周期的长度?试辨析振荡周期、状态周期、机器周期、指令周期之间的关系。

【2-5】单片机的ROM必须具有掉电存储功能,这句话是否正确?【2-6】单片机对RAM的根本要求是快,但掉电可丢失数据,这个表述正确吗?【2-7】试说出80C51的两种时钟电路模式,如果是只有一个单片机工作常使用的是哪一种?如果是两个以上的单片机工作使用哪一种?【2-8】80C51单片机的EA信号有何功能?在使用8031时,EA信号引脚应如何处理?现在使用的80C51系列单片机内部一般均含有ROM,其EA引脚应该怎么接?【2-9】80C51系列单片机的三总线结构包括哪三种?其中作地址总线指的是?作数据总线指的是?属于控制总线的有?P0口的分时复用功能需要依靠锁存器的锁存功能,试举1种常用的低功耗锁存器并将其与单片机正确连接?【2-10】片内RAM低128单元一般划分为哪三个主要部分?对应的字节地址空间是?内部RAM中,可作为工作寄存器区的单元地址为()H~()H。

【2-11】80C51单片机任何一个时间4组通用工作寄存器中只能有一组工作,具体哪一组工作由什么来决定?如何设置才能选用0组通用寄存器?【2-12】80C51单片机具有很强的位(布尔)处理功能,内部RAM中共有多少单元可以位寻址,试写出其字节范围和位地址范围?【2-13】位地址00H与字节地址00H在内存中的位置有什么区别?片内字节地址为2AH单元最低位的位地址是();片内字节地址为88H单元的最低位的位地址为()。

实验五四位多功能移位寄存器的设计四位多功能移位寄存器的设计1、实验⽬的熟悉ISE系列软件的设计流程和基本⼯具使⽤;学习四位多功能移位寄存器的设计;学习VHDL的IF语句应⽤。

2、实验内容移位寄存器是⼀种常⽤的时序电路。

它除了具有存储代码的功能之外,还具有移位功能。

移位功能是指存储在寄存器⾥的代码可再移位脉冲的作⽤下依次左移或右移。

移位寄存器可⽤于寄存代码,还可⽤于数据的串/并转换,并/串转换以及数值运算和处理等。

3、实验器材Spartan 3E开发板。

4、实验说明实验中所需要的源⽂件在本报告附录中。

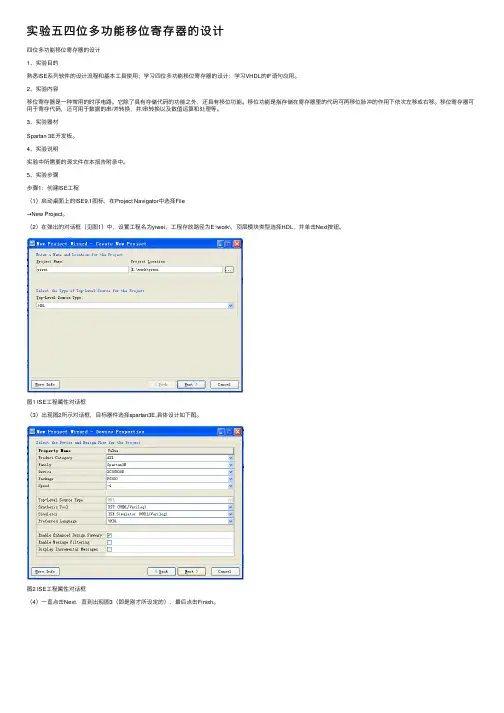

5、实验步骤步骤1:创建ISE⼯程(1)启动桌⾯上的ISE9.1图标,在Project Navigator中选择File→New Project。

(2)在弹出的对话框(见图1)中,设置⼯程名为yiwei,⼯程存放路径为E:\work\,顶层模块类型选择HDL,并单击Next按钮。

图1 ISE⼯程属性对话框(3)出现图2所⽰对话框,⽬标器件选择spartan3E,具体设计如下图。

图2 ISE⼯程属性对话框(4)⼀直点击Next,直到出现图3(即是刚才所设定的),最后点击Finish。

图3 ⼯程设计总表出现图4,这就是所建⽴的⼯程,现在我们需要在⾥⾯完成我们的设计。

图4 ISE⼯程属性对话框步骤2:创建新的VHDL设计⽂件(1)在ISE⽤户界⾯中,选择Project→New Source。

(2)在弹出的对话框(见图5)中,选择VHDL Module作为源程序类型,设置⽂件名为yiwei,并单击“下⼀步”按钮。

图5 VHDL的New Source Wizard(3)点击Next,直到出现图6,直到Finish。

图6 程序总结(4)点击Finish之后出现程序编辑窗⼝,在窗⼝中进⾏程序编辑。

步骤3:利⽤XST进⾏设计综合并仿真(1)点击processes⽬录下的synthesize-XST可以实现综合。

图8 综合后的程序编辑窗⼝(2)综合过后,在信息显⽰窗⼝中会显⽰Process "Synthesize" completedsuccessfully即综合成功。

(一) 单片机的基本机构与工作原理1、单片机与其他常见微机(如PC机)有什么不同?它是什么独特优点?80C51系列单片机在片内集成了哪些主要逻辑功能部件?各个逻辑部件的主要功能是什么?2、80C51系列单片机有哪些信号需要芯片引脚以第二功能的方式提供?3、80C51单片机的“ALE”信号、“/EA”信号有何功能?在使用80C31时,它们的信号引脚应如何处理?4、80C51存储器在结构上有何特点?在物理上和逻辑上各有哪几种地址空间?访问片内RAM和片外RAM的指令格式有何区别?5、片内RAM低128单元划分为哪三个主要部分?各部分主要功能是什么?6、80C51设有4个通用工作寄存器组,有什么特点?如何选用?如何实现工作寄存器现场保护?7、特殊功能寄存器的地址范围是多少?哪些特殊功能寄存器可以位操作?8、堆栈有哪些功能?堆栈指示器(SP)的作用是什么?在程序设计时,为什么还要对SP重新赋值?9、为什么说80C51具有很强的布尔(位)处理功能?共有多少单元可以位寻址?采用布尔处理有哪些优点?10、80C51单片机的时钟周期、机器周期、指令周期有何区别?它们之间有何关系?单片机晶振频率与哪些工作参数有关?11、单片机有几种复位方法?对复位信号有何要求?复位后机器的初始状态如何,即各寄存器的状态如何?12、80C51的4个I/O口P0~P3在使用上有哪些分工和特点?试比较各口的特点?何谓分时复用总线?P3口的第二变异功能有哪些?13、80C51端口P0~P3作通用I/O口时,在输入引脚数据时,应注意什么?14、“读—改—写”指令有何优点?请至少列出五条不同操作的“读—改—写”指令。

15、为什么当P2作为扩展程序存储器的高8位地址后,就不再适宜作通用I/O了?16、程序计数器PC作为不可寻址寄存器,它有哪些特点?地址指针DPTR有哪些特点?与程序计数器PC有何异同?17、程序状态字PSW的含义是什么?如何利用它们?18、80C51单片机运行出错或程序进入死循环,如何摆脱困境?19、单片机在工业控制系统中有哪些掉电保护措施?20、举例说明单片机在工业控制系统中低功耗工作方式的意义及方法。

单片机原理及接口李朝青1.89C51单片机内包括哪些重要逻辑功能部件?答:80C51系列单片机在片内集成了如下重要逻辑功能部件:(l)CPU(中央解决器):8位(2)片内RAM:128B(3)特殊功能寄存器:21个(4)程序存储器:4KB(5)并行I/O口:8位,4个(6)串行接口:全双工,1个(7)定期器/计数器:16位,2个(8)片内时钟电路:1个2.89C51EA端有何用途?答:/EA端接高电平时,CPU只访问片内flash Rom并执行内部程序,存储器。

/EA端接低电平时,CPU只访问外部ROM,并执行片外程序存储器中指令。

/EA 端保持高电平时,CPU执行内部存储器中指令。

3. 89C51存储器分哪几种空间?如何区别不同空间寻址?答:ROM(片内ROM和片外ROM统一编址)(使用MOVC)(数据传送指令)(16bits 地址)(64KB)片外RAM(MOVX)(16bits地址)(64KB)片内RAM(MOV)(8bits地址)(256B)4. 简述89C51片内RAM空间分派。

答:片内RAM有256B低128B是真正RAM区高128B是SFR(特殊功能寄存器)区5. 简述布尔解决存储器空间分派,片内RAM中包括哪些可位寻址单元。

答:片内RAM区从00H~FFH(256B)其中20H~2FH(字节地址)是位寻址区相应位地址是00H~7FH6. 如何简捷地判断89C51正在工作?答:用示波器观测8051XTAL2端与否有脉冲信号输出(判断震荡电路工作与否正常?)ALE(地址锁存容许)(Address Latch Enable)输出是fosc6分频用示波器观测ALE与否有脉冲输出(判断 8051芯片好坏?)观测PSEN(判断8051可以到EPROM 或ROM中读取指令码?)由于/PSEN接外部EPROM(ROM)/OE端子OE=Output Enable(输出容许)7. 89C51如何拟定和变化当前工作寄存器组?答:PSW(程序状态字)(Program Status Word)中RS1和RS0可以给出4中组合用来从4组工作寄存器组中进行选取PSW属于SFR(Special Function Register)(特殊功能寄存器)8. 89C51 P0口用作通用I/O口输入时,若通过TTL“OC”门输入数据,应注意什么?为什么?答:9. 读端口锁存器和“读引脚”有何不同?各使用哪种指令?答:读锁存器(ANL P0,A)就是相称于从存储器中拿数据,而读引脚是从外部拿数据(如MOV A,P1 这条指令就是读引脚,意思就是把端口p1输入数据送给A)传送类MOV,判位转移JB、JNB、这些都属于读引脚,平时实验时经惯用这些指令于外部通信,判断外部键盘等;字节互换XCH、XCHD算术及逻辑运算 ORL、CPL、ANL、ADD、ADDC、SUBB、INC、DEC控制转移CJNE、DJNZ都属于读锁存器。

第一章:1. 给出下列有符号数的原码、反码和补码(假设计算机字长为8位)。

+45 -89 -6 +112答:【+45】原=00101101,【+45】反=00101101,【+45】补=00101101【-89】原=11011001,【-89】反=10100110,【-89】补=10100111【-6】原=10000110,【-6】反=11111001,【-6】补=11111010【+112】原=01110000,【+112】反=01110000,【+112】补=011100002. 指明下列字符在计算机内部的表示形式。

AsENdfJFmdsv120答:41H 73H 45H 4EH 64H 66H 4AH 46H 6DH 64H 73H 76H 31H 32H 30H3.何谓微型计算机硬件?它由哪几部分组成?并简述各部分的作用。

答:微型计算机硬件由中央处理器、存储器、输入/输出设备和系统总线等组成,中央处理器由运算器和控制器组成,是微型计算机运算和控制中心。

存储器是用来存放程序和数据的记忆装置。

输人设备是向计算机输人原始数据和程序的装置。

输出设备是计算机向外界输出信息的装置。

I/O接口电路是外部设备和微型机之间传送信息的部件。

总线是连接多个设备或功能部件的一簇公共信号线,它是计算机各组成部件之间信息交换的通道。

微型计算机的各大功能部件通过总线相连。

4.简述8086CPU的内部结构。

答:8086微处理器的内部分为两个部分:执行单元(EU)和总线接口单元(BIU)。

执行部件由运算器(ALU)、通用寄存器、标志寄存器和EU控制系统等组成。

EU从BIU的指令队列中获得指令,然后执行该指令,完成指今所规定的操作。

总线接口部件BIU由段寄存器、指令指针寄存器、地址形成逻辑、总线控制逻辑和指令队列等组成。

总线接口部件负责从内部存储器的指定区域中取出指令送到指令队列中去排队。

5.何谓总线?总线按功能可分为哪几种?答:总线是连接多个设备或功能部件的一簇公共信号线,它是计算机各组成部件之间信息交换的通道。

目录摘要 (1)1 多功能双向移位寄存器 (2)1.1 基本工作原理 (2)1.2 基本实现方案 (2)2 电路图设计 (4)2.1 电路结构 (4)2.2 真值表 (4)3 Verilog描述8位双向移位寄存器 (6)4 程序仿真 (8)5 总结 (10)参考文献 (11)摘要移位寄存器是基本的同步时序电路,基本的移位寄存器可以实现数据的串行/并行或并行/串行的转换、数值运算以及其他数据处理功能。

在本设计中,使用硬件描述语言Verilog,在EDA工具QuartussII中,设计8位双向移位寄存器硬件电路,根据设计语言进行功能时序仿真,验证设计的正确性与可行性。

关键字:Verilog QuartusII 移位寄存器8位双向移位寄存器电路设计1 多功能双向移位寄存器1.1 基本工作原理移位寄存器是基本的同步时序电路,基本的移位寄存器可以实现数据的串行/并行或并行/串行的转换、数值运算以及其他数据处理功能。

在本设计中定义移位寄存器中的数据从低位触发器移向高位为右移,移向低位为左移。

为了扩展逻辑功能和增加使用的灵活性,某些双向移位寄存器集成电路产品又附加了并行输入、并行输出等功能。

如图1所示是上述几种工作模式的简化示意图。

并行输入并行输出右移串行输入(D IR 左移串行输出(D OL 右移串行输出(D OR ) D IL )0123图1 多功能移位寄存器工作模式简图1.2 基本实现方案图2所示是实现数据保持、右移、左移、并行置入和并行输出的一种电路方案。

图中的D 触发器m FF 是N 为移位寄存器中的第m 位触发器,在其数据输入端插入了一个4选1数据选择器m MUX ,用2位编码输入10S S 、控制m MUX ,来选择触发器输入信号m D 的来源。

当100S S ==时,选择该触发器本身输出的m Q ,次态为1m n nm mQ D Q +==,使触发器保持状态不变;当100,1S S ==时,触发器1m FF -的输出1m Q -被选中,故CP 脉冲上升沿到来时,m FF 存入1m FF -此前的逻辑值,即1m 1n n m Q Q +-=,而1m +1n nm Q Q +=,从而实现右移功能;类似地,当101,0S S ==时,m MUX 选择1m Q +,实现左移功能;而当101S S ==时,则选中并行输入数据m DI ,其次态1n m m Q DI +=,从而完成并行数据的置入功能。

电子课程设计— 8位数码管动态显示电路设计学院:电子信息工程学院专业、班级:姓名:学号:指导老师:2014年12月目录一、设计任务与要求................................................. (3)二、总体框图................................................. (3)三、选择器件................................................. (3)四、功能模块................................................. (9)五、总体设计电路图................................................. . (10)六、心得体会.................................................. .. (12)8位数码管动态显示电路设计一、设计任务与要求1. 设计个8位数码管动态显示电路,动态显示1、2、3、4、5、6、7、8。

2. 要求在某一时刻,仅有一个LED数码管发光。

3. 该数码管发光一段时间后,下一个LED发光,这样8只数码管循环发光。

4. 当循环扫描速度足够快时,由于视觉暂留的原因,就会感觉8只数码管是在持续发光。

5、研究循环地址码发生器的时钟频率和显示闪烁的关系。

二、总体框图设计的总体框图如图2-1所示。

图2-1总体框图三、选择器件 1、数码管数码管是一种由发光二极管组成的断码型显示器件,如图1所示。

U13DCD_HEX图1 数码管数码管里有八个小LED 发光二极管,通过控制不同的LED 的亮灭来显示出不同的字形。

数码管又分为共阴极和共阳极两种类型,其实共阴极就是将八个LED 的阴极连在一起,让其接地,这样给任何一个LED 的另一端高电平,它便能点亮。

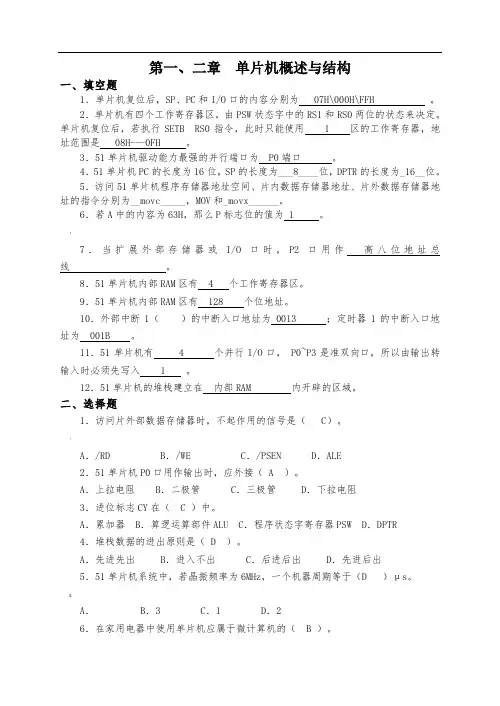

第一、二章单片机概述与结构一、填空题1.单片机复位后,SP、PC和I/O口的内容分别为 07H\000H\FFH 。

2.单片机有四个工作寄存器区,由PSW状态字中的RS1和RS0两位的状态来决定。

单片机复位后,若执行SETB RS0指令,此时只能使用 1 区的工作寄存器,地址范围是 08H---0FH 。

3.51单片机驱动能力最强的并行端口为 P0端口。

4.51单片机PC的长度为16位,SP的长度为___8____位,DPTR的长度为_16__位。

5.访问51单片机程序存储器地址空间、片内数据存储器地址、片外数据存储器地址的指令分别为__movc_____,MOV和_movx______。

6.若A中的内容为63H,那么P标志位的值为 1 。

"7.当扩展外部存储器或I/O口时,P2口用作高八位地址总线。

8.51单片机内部RAM区有 4 个工作寄存器区。

9.51单片机内部RAM区有 128 个位地址。

10.外部中断1()的中断入口地址为 0013 ;定时器1的中断入口地址为 001B 。

11.51单片机有 4 个并行I/O口, P0~P3是准双向口,所以由输出转输入时必须先写入 1 。

12.51单片机的堆栈建立在内部RAM 内开辟的区域。

二、选择题1.访问片外部数据存储器时,不起作用的信号是( C)。

'A./RD B./WE C./PSEN D.ALE2.51单片机P0口用作输出时,应外接( A )。

A.上拉电阻 B.二极管 C.三极管 D.下拉电阻3.进位标志CY在( C )中。

A.累加器 B.算逻运算部件ALU C.程序状态字寄存器PSW D.DPTR4.堆栈数据的进出原则是( D )。

A.先进先出 B.进入不出 C.后进后出 D.先进后出5.51单片机系统中,若晶振频率为6MHz,一个机器周期等于(D )μs。

&A.B.3 C.1 D.26.在家用电器中使用单片机应属于微计算机的( B )。

寄存器的设计与仿真实验在计算机科学与工程领域中,寄存器被广泛用于存储和处理数据。

寄存器是一个用于暂时存储和传输数据的硬件组件,在计算机的指令执行过程中起到关键作用。

本文将探讨寄存器的设计原理与实验仿真。

一、寄存器的基本原理寄存器是计算机的一种具体实现方式,用于存储和传输数据。

它由多个存储单元组成,每个存储单元可以存储一个固定长度的二进制数据。

寄存器以位的形式组织数据,每一位都有其特定的含义和作用。

寄存器的设计原理涉及到以下几个方面:1. 数据宽度:寄存器的数据宽度决定了它能够存储的位数。

常见的寄存器宽度有8位、16位、32位和64位等。

数据宽度的选择需要根据实际应用和计算机系统的需求来确定。

2. 位操作:寄存器可以进行各种位操作,如读取、写入、清零、置位等。

这些操作都是通过电路逻辑门的组合实现的,用于对数据进行处理和控制。

3. 时钟信号:寄存器通过时钟信号来同步数据的读取和写入。

时钟信号保证了数据的稳定传输和正确同步。

4. 输入输出端口:寄存器需要与其他组件进行数据的输入和输出交互。

它可以作为数据的来源或目的地,实现数据的传输与共享。

二、寄存器的设计寄存器的设计是计算机硬件设计中的重要环节。

在设计寄存器时,需要考虑下列因素:1. 数据宽度和寄存器数量:根据计算机系统的需求和性能要求,确定寄存器的数据宽度和数量。

数据宽度的选择需要平衡性能与成本之间的关系。

2. 位操作功能:寄存器的位操作功能需要根据实际应用需求来设计。

常见的位操作功能有读取、写入、清零、置位、移位等。

这些功能需要通过逻辑门电路的组合实现。

3. 时钟信号:寄存器的设计需要考虑时钟信号的生成和分配。

时钟信号的频率和稳定性对寄存器的性能和功耗有重要影响。

4. 输入输出接口:寄存器需要与其他组件进行数据的输入和输出,因此需要设计合适的接口电路。

接口电路需要满足性能、带宽、延迟等方面的要求。

在寄存器的设计过程中,可以使用硬件描述语言(HDL)进行仿真和验证。

题目:基于AT89C52单片机的多模式流水灯设计——程序设计一、概述AT89C52是一个低电压,高性能CMOS 8位单片机,片内含8k bytes的可反复擦写的Flash只读程序存储器和256 bytes的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,片内置通用8位中央处理器和Flash存储单元。

AT89C52有40个引脚,32个外部双向输入/输出(I/O)端口,同时内含2个外中断口,3个16位可编程定时计数器,2个全双工串行通信口,2个读写口线,AT89C52可以按照常规方法进行编程。

P为40 脚双列直插封装的8 位通用微处理器,采用工业标准的C51内核,在内部功能及管脚排布上与通用的8xc52 相同,其主要用于会聚调整时的功能控制。

功能包括对会聚主IC 内部寄存器、数据RAM及外部接口等功能部件的初始化,会聚调整控制,会聚测试图控制,红外遥控信号IR的接收解码及与主板CPU通信等。

主要管脚有:XTAL1(19 脚)和X TAL2(18 脚)为振荡器输入输出端口,外接12MHz 晶振。

RST/Vpd(9 脚)为复位输入端口,外接电阻电容组成的复位电路。

VCC(40 脚)和VSS(20 脚)为供电端口,分别接+5V电源的正负端。

P0~P3 为可编程通用I/O 脚,其功能用途由软件定义。

二、实验原理与设计方案设计平台:AT89C51单片机;PC机,含Keil软件平台,Proteus软件平台;单片机开发板。

如下图2为开发板:设计思路:本系统主要通过P1口来控制LED的闪烁,有10种模式(0~9)可供选择。

通过模式按键来选择需要的闪烁方式,这里主要通过几个计数器来控制,按下一次按键,计数器加1,模式切换到下一种模式。

同时利用数码管将模式显示出来。

另外还有一个加速和减速的按键,系统设定有30种速度可供选择。

按下一次加速键,速度计数器加1,按下一次减速键,速度计数器减1。

8位加法器的设计一个8位加法器的设计需要考虑到以下几个方面:输入端口、输出端口、运算器、控制电路和时序以及综合测试等。

输入端口是加法器的输入,我们需要为每个输入端口分配相应的位数。

对于一个8位加法器,我们需要8个输入端口,每个端口为1位。

可以使用开关或者其他输入设备来控制输入信号。

输出端口是加法器的输出,同样需要为每个输出端口分配相应的位数。

对于一个8位加法器,我们需要8个输出端口,每个端口为1位。

可以使用LED灯等输出设备来显示输出结果。

运算器是加法器的核心部件,负责实现加法运算。

我们需要使用逻辑门电路来实现8位加法。

常见的实现方式是使用二进制加法器来实现,其中包括全加器、半加器等。

控制电路和时序是为了保证加法器的稳定运行。

可以采用时钟信号来对加法器的运算进行控制,时钟信号可以通过一个时钟源或者其他方式来产生。

综合测试是为了确保加法器的正确性。

我们需要设计一个测试电路,输入各种可能的输入信号,并检查输出结果是否符合预期。

以下是一个8位加法器的设计实例:1.输入端口设计:设计8个输入端口,每个端口为1位。

2.输出端口设计:设计一个8位输出端口,用于显示加法结果。

3.运算器设计:使用全加器和半加器组成8位二进制加法器。

首先将每一位的输入与进位相加,得到部分和和进位,然后再将部分和与下一位的输入和进位再相加,依次类推,最后得到8位加法结果。

4.控制电路和时序设计:使用时钟信号来控制加法器的运算。

可以通过一个时钟源或者其他方式来产生时钟信号。

5.综合测试设计:设计一个测试电路,输入各种可能的输入信号,并检查输出结果是否符合预期。

可以使用计算机软件来进行模拟测试。

在设计过程中,需要充分考虑各个部件之间的连接和信息传递,确保输入信号能够正确地经过运算器进行运算,并将运算结果正确地传递到输出端口。

总之,一个8位加法器的设计需要考虑到输入端口、输出端口、运算器、控制电路和时序以及综合测试等方面。

在具体设计过程中,还需要充分考虑其稳定性、可靠性和正确性等因素。

2021年杭州电子科技大学软件工程专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、地址线A15~A0(低),若选取用16K×1位存储芯片构成64KB存储器,则应由地址码()译码产生片选信号。

A.A15,A14B.A0,AlC.A14,A13D.A1,A22、容量为64块的Cache采用组相联映射方式,字块大小为128个字,每4块为一组。

如果主存为4K块,且按字编址,那么主存地址和主存标记的位数分别为()。

A.16,6B.17,6C.18,8 D .19,83、假设机器字长为8位(含两位符号位),若机器数DA日为补码,则算术左移一位和算术右移一位分别得()。

A.B4H EDHB.F4H 6DHC.B5H EDHD.B4H 6DH4、在补码一位乘中,若判断位Y n Y n+1=01,则应执行的操作为()。

A.原部分积加[-x]补,然后右移一位B.原部分积加[x]补,然后右移一位C.原部分积加[-x] 补,然后左移一位D.原部分积加[x]补,然后左移一位5、下列关于浮点数加减法运算的叙述中,正确的是()。

I.对阶操作不会引起阶码上溢或下溢Ⅱ.右归和尾数舍入都可能引起阶码上溢Ⅲ.左归时可能引起阶码下溢IV.尾数溢出时结果不一定溢出A.仅Ⅱ、ⅢB. 仅I、Ⅱ、ⅢC.仅I、Ⅲ、IⅣD. I、Ⅱ、Ⅲ、Ⅳ6、在链式查询方式下,若有N个设备,则()。

A.只需一条总线请求线B.需要N条总线请求线C.视情况而定,可能一条,也可能N条D.以上说法都不对7、某同步总线的时钟频率为100MHz,宽度为32位,地址/数据线复用,每传输一个地址或数据占用一个时钟周期。

若该总线支持突发(猝发)传输方式,则一次“主存写”总线事务传输128位数据所需要的时间至少是()。

A.20nsB.40nsC.50nsD.80ns8、假定编译器对高级语言的某条语句可以编译生成两种不同的指令序列,A、B和C三类指令的CPl和执行两种不同序列所含的三类指令条数见下表。

思考题:【2-1】80C51单片机由哪几部分组成,试说明ROM和RAM的功能分别是什么【2-2】在程序运行中,PC的值是。

()A)当前正在执行指令的前一条指令的地址B)当前正在执行指令的地址C)当前正在执行指令的下一条指令的首地址D)控制器中指令寄存器的地址【2-3】判断下列说法是否正确。

(1)PC可以存放一个16位二进制数,因此其寻址范围为0000H~7FFFH。

()(2)单片机系统复位时PC的内容为0000H,因此CPU从程序存储器0000H地址单元取指令,开始执行程序。

()(3)PC可以看成是程序计时器()(4)PC可以看成是程序存储器的地址指针。

()【2-4】试计算当振荡频率为12 MHz和6 MHz时,一个机器周期的长度试辨析振荡周期、状态周期、机器周期、指令周期之间的关系。

【2-5】单片机的ROM必须具有掉电存储功能,这句话是否正确【2-6】单片机对RAM的根本要求是快,但掉电可丢失数据,这个表述正确吗【2-7】试说出80C51的两种时钟电路模式,如果是只有一个单片机工作常使用的是哪一种如果是两个以上的单片机工作使用哪一种【2-8】80C51单片机的EA信号有何功能在使用8031时,EA信号引脚应如何处理现在使用的80C51系列单片机内部一般均含有ROM,其EA引脚应该怎么接【2-9】80C51系列单片机的三总线结构包括哪三种其中作地址总线指的是作数据总线指的是属于控制总线的有P0口的分时复用功能需要依靠锁存器的锁存功能,试举1种常用的低功耗锁存器并将其与单片机正确连接【2-10】片内RAM低128单元一般划分为哪三个主要部分对应的字节地址空间是内部RAM中,可作为工作寄存器区的单元地址为()H~()H。

【2-11】80C51单片机任何一个时间4组通用工作寄存器中只能有一组工作,具体哪一组工作由什么来决定如何设置才能选用0组通用寄存器【2-12】80C51单片机具有很强的位(布尔)处理功能,内部RAM中共有多少单元可以位寻址,试写出其字节范围和位地址范围【2-13】位地址00H与字节地址00H在内存中的位置有什么区别片内字节地址为2AH单元最低位的位地址是();片内字节地址为88H单元的最低位的位地址为()。

4个8位通用寄存器组的设计与VHDL实现

一、设计目标

设计一个通用寄存器组Reg4-8,里面包含4个寄存器,每个寄存器可以存储8位的数据。

每次读的时候,能同时读出两个数据;每次写的时候,可以写入一个数据。

读/写的寄存器单元由寄存器编号所确定。

二、设计要求

1.当reset信号为0时,初始化各寄存器的值;

2.当reset信号为1时,可以进行寄存器读或写,具体如下:

✧寄存器的写受到时钟上升沿的控制。

即当时钟上升沿来临且写使能信号en=1时,

将输入的8位数据d[7..0]写入到由寄存器选择编号dest_reg[1..0](如dest_reg[1..0]=

“01”)所确定的寄存器(如寄存器R1)中。

其中,[1..0]代表下标从1到0,其它

类推;

✧寄存器的读不受时钟信号的控制。

即只要给出源寄存器选择编号source_reg[1..0]

和目的寄存器选择编号dest_reg[1..0],便同时将这两个对应寄存器单元的数值输

出到双数据总线sr[7..0]和dr[7..0]中,以便同时传2个数据给运算器;

3. 在CPU中,source_reg[1..0]和dest_reg[1..0]实际上都来自于指令,在运算过程中用户是难于操控的;相应地,寄存器的输出结果sr[7..0]和dr[7..0],也都是传送到运算器那里,是不能直接输出的。

但是,在设计的过程中,我们又必须要检测某个寄存器的内容是什么,以测试指令的执行是否正确。

解决此问题的思路是引入一些附加输入输出信号,如可以设置所需测试的寄存器的编号值,然后将结果输出到相应的指示灯上。

本设计中,我们用reg_sel[1..0]作为待测试的寄存器编号,并用reg_out[7..0]作为该寄存器中读出的数据。

三、设计思路

在设计时,首先根据设计目标和要求确定逻辑框图,然后再确定其内部结构。

前者,主要确定输入和输出信号,后者主要确定输出如何利用输入而产生。

1.首先根据上述的设计目标与要求,分析输入输出引脚。

根据设计要求,可知:

(1)进行初始赋值,需要1个1位的初始化信号reset;

(2)进行数据的写,需要1个1位的时钟信号clk、1个8位的输入数据d[7..0]、1个1位的写使能信号en以及1个2位的寄存器选择编号dest_reg[1..0];

(3)进行数据的读,需要源和目的寄存器选择编号各1个,即分别为source_reg[1..0]和dest_reg[1..0],各为2位;读出的8位数据信号各1个,即分别为sr[7..0]和dr[7..0];(4)用于测试用的寄存器选择编号reg_sel[1..0]及其对应的输出reg_out[7..0]。

综上可知,通用寄存器组Reg4-8的输入输出信号可总结为:

输入信号:reset、clk、en,dest_reg[1..0],source_reg[1..0]、d[7..0]、reg_sel[1..0]

输出信号:sr[7..0]、dr[7..0]、reg_out[7..0]

因此,Reg4-8的逻辑框图可以表示如下。

图1 Reg4-8逻辑框图

2.在设计出Reg4-8的逻辑框图后,进一步设计Reg4-8的内部结构。

在设计内部结构时,我们采用结构设计(即调用其它元件来连线实现)的方法。

为此,首先需要确定需要哪些模块,然后再考虑不同模块之间如何连接。

Reg4-8的设计思路,可以采用4个寄存器的通用寄存器组Reg4-16的设计方法,也可以采用16个寄存器的通用寄存器组Reg16-16的设计方法。

各人独自选择,并完成相应的逻辑框图及内部结构设计。

四、VHDL编程实现与TEC-CA平台仿真测试

在完成逻辑框图及内部结构的设计后,参考Reg4-16或Reg16-16的VHDL代码,各人自己编程完成。

完成编程且分配管脚后,在TEC-CA平台上进行仿真测试。

测试方法,亦参考Reg4-16或Reg16-16的测试方法。