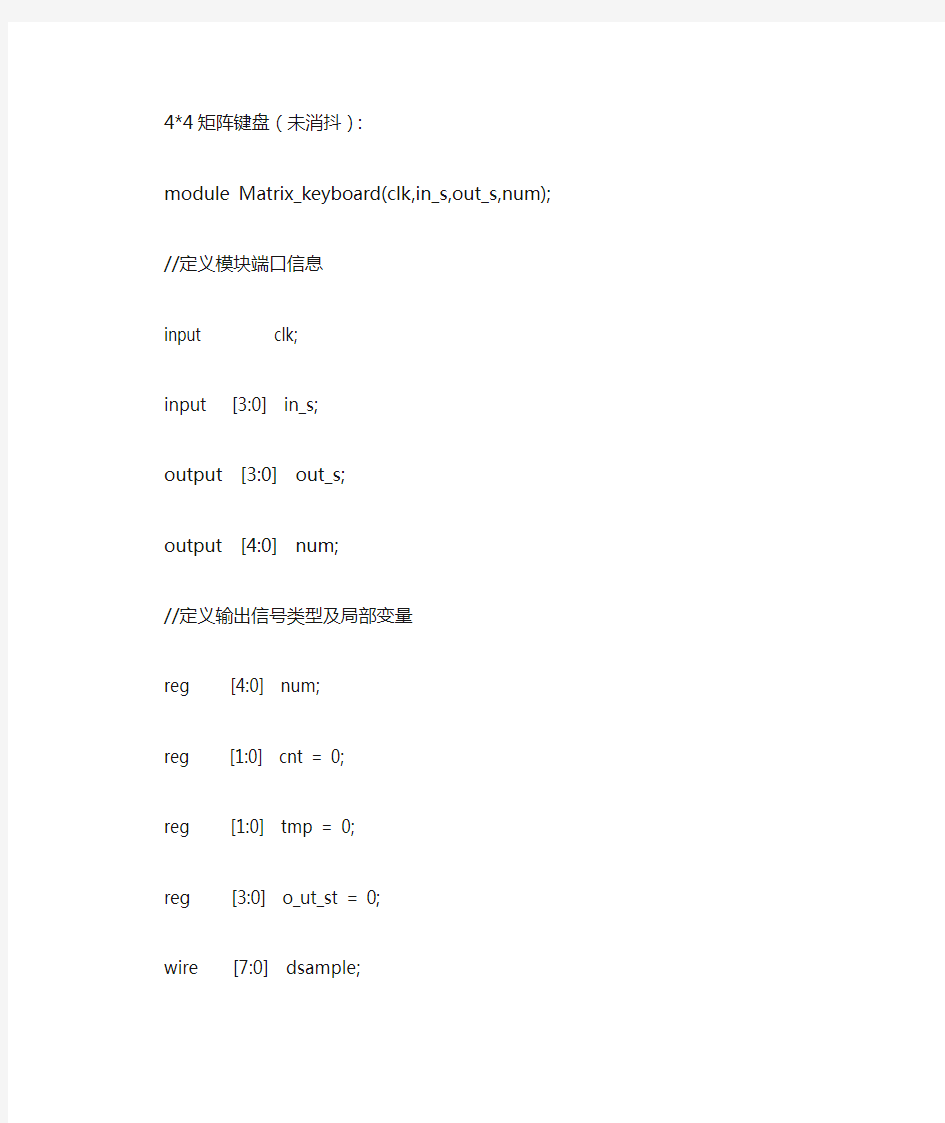

4*4矩阵键盘(未消抖):

module Matrix_keyboard(clk,in_s,out_s,num);

//定义模块端口信息

input clk;

input [3:0] in_s;

output [3:0] out_s;

output [4:0] num;

//定义输出信号类型及局部变量

reg [4:0] num;

reg [1:0] cnt = 0;

reg [1:0] tmp = 0;

reg [3:0] o_ut_st = 0;

wire [7:0] dsample;

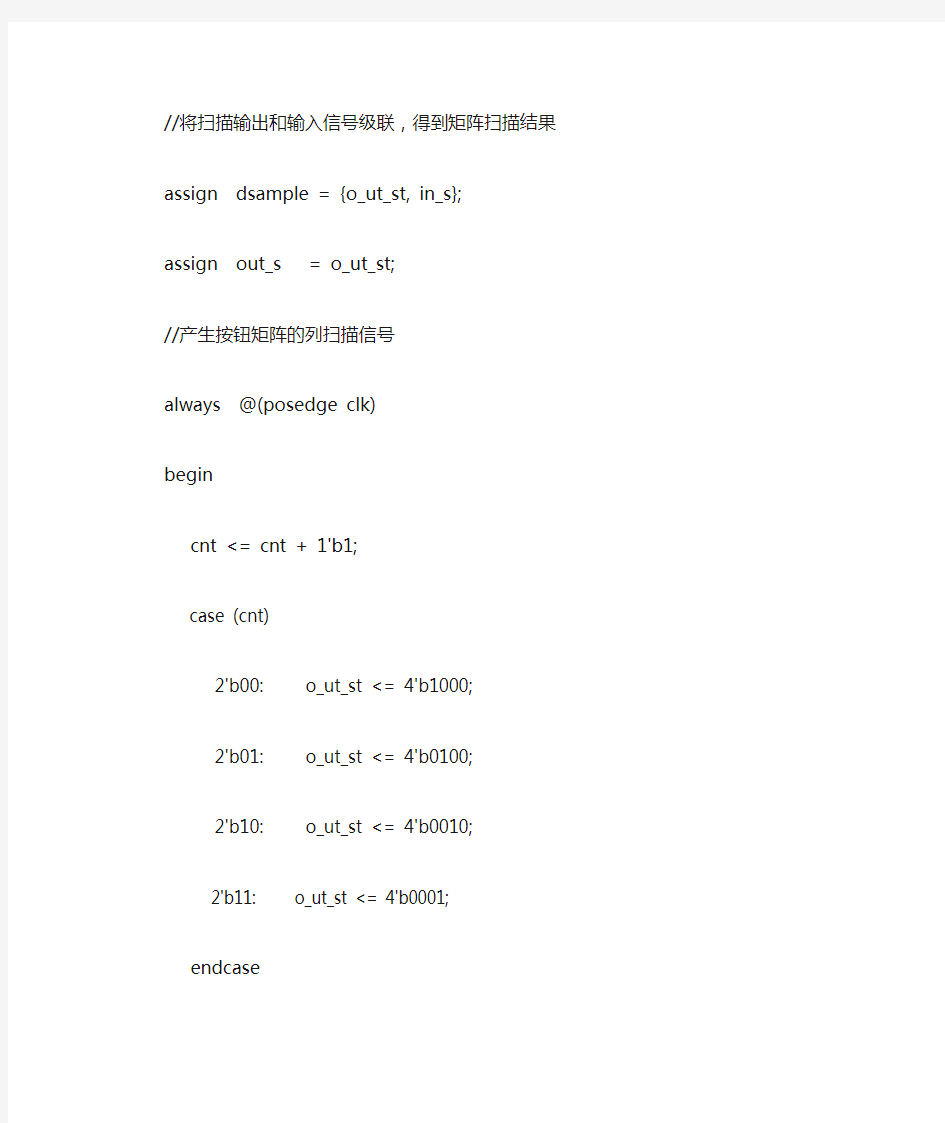

//将扫描输出和输入信号级联,得到矩阵扫描结果

assign dsample = {o_ut_st, in_s};

assign out_s = o_ut_st;

//产生按钮矩阵的列扫描信号

always @(posedge clk)

begin

cnt <= cnt + 1'b1;

case (cnt)

2'b00: o_ut_st <= 4'b1000;

2'b01: o_ut_st <= 4'b0100;

2'b10: o_ut_st <= 4'b0010;

2'b11: o_ut_st <= 4'b0001;

endcase

end

//根据按钮的列扫描信号和行输入信号判断按钮是否被按下always @(posedge clk)

begin

//如果无按钮按下,定义num=16为无效状态

if (in_s == 4'b0000)

begin

if (tmp == 3)

begin

num <= 16; //无按键输入,输出16

tmp <= 0;

end

else

begin

num <= num;

tmp <= tmp + 1'b1; //扫描周期,3个时钟周期

end

end

else

begin

tmp <= 0;

case (dsample)

//第1列扫描结果

8'b1000_0001: num <= 0;

8'b1000_0010: num <= 1;

8'b1000_0100: num <= 2;

8'b1000_1000: num <= 3;

//第2列扫描结果

8'b0100_0001: num <= 4;

8'b0100_0010: num <= 5;

8'b0100_0100: num <= 6;

8'b0100_1000: num <= 7;

//第3列扫描结果

8'b0010_0001: num <= 8;

8'b0010_0010: num <= 9;

8'b0010_0100: num <= 10;

8'b0010_1000: num <= 11;

//第4列扫描结果

8'b0001_0001: num <= 12;

8'b0001_0010: num <= 13;

8'b0001_0100: num <= 14;

8'b0001_1000: num <= 15;

endcase

end

end

endmodule

独立按键消抖程序:

module Btn_without_shake(Clk_50MHz,PB_UP,PB_Out,count_sel); //定义模块端口信息

input Clk_50MHz; //模块时钟50MHz

input PB_UP; //按钮输入

output PB_Out; //去抖后按钮输出

output [1:0] count_sel; //计数器输出

//定义输出信号类型及局部变量

reg [19:0] count_high = 0; //按钮输入高电平计数器

reg [19:0] count_low = 0; //按钮输入低电平计数器

reg PB_reg = 0;

reg [1:0] count_sel_reg = 0;

//输出赋值

assign PB_Out = PB_reg;

assign count_sel = count_sel_reg;

//对输入进行采样,计数

always @(posedge Clk_50MHz)

if(PB_UP == 1'b0)

count_low <= count_low + 1'b1;

else

count_low <= 20'h0_0000;

always @(posedge Clk_50MHz)

if(PB_UP == 1'b1)

count_high <= count_high + 1'b1;

else

count_high <= 20'h0_0000;

//防抖输出

always @(posedge Clk_50MHz)

if(count_high == 20'h7_FFFF) //判断高电平信号是否符合输出条件10ms

PB_reg <= 1'b1; //如果符合条件,则防抖输出高电平

else

if(count_low == 20'h7_FFFF) //判断低电平信号是否符合输出条件10ms

PB_reg <= 1'b0; //如果符合条件,则防抖输出低电平

else

PB_reg <= PB_reg;

//使用去抖输出PB_reg控制count_sel计数

always @(posedge PB_reg)

count_sel_reg <= count_sel_reg + 1'b1;

endmodule

初学,参考书上的《Verilog HDL程序设计与实践》,准备用状态机做一下矩阵键盘,恩,坛子里也有,不过还是自己尝试一下,坛里老牛很多呀!

modulekey_scan( inputclk, inputrst_n, input [3:0] row, // 矩阵键盘行 output reg [3:0] col, // 矩阵键盘列 output reg [7:0] key_val // 键盘值 ); //++++++++++++++++++++++++++++++++++++++ // 分频部分开始 //++++++++++++++++++++++++++++++++++++++ reg [19:0] cnt; // 计数子 always @ (posedgeclk, negedgerst_n) if (!rst_n) cnt<= 0; else cnt<= cnt + 1'b1; wirekey_clk = cnt[19]; // (2^20/50M = 21)ms //-------------------------------------- // 分频部分结束 //-------------------------------------- //++++++++++++++++++++++++++++++++++++++ // 状态机部分开始 //++++++++++++++++++++++++++++++++++++++ // 状态数较少,独热码编码 parameter NO_KEY_PRESSED = 6'b000_001; // 没有按键按下parameter SCAN_COL0 = 6'b000_010; // 扫描第0列parameter SCAN_COL1 = 6'b000_100; // 扫描第1列parameter SCAN_COL2 = 6'b001_000; // 扫描第2列parameter SCAN_COL3 = 6'b010_000; // 扫描第3列parameter KEY_PRESSED = 6'b100_000; // 有按键按下 reg [5:0] current_state, next_state; // 现态、次态 always @ (posedgekey_clk, negedgerst_n) if (!rst_n) current_state<= NO_KEY_PRESSED; else current_state<= next_state;

.. 主控键盘 (SYSTEM KEYBOARD) 使用说明书 (中文版第二版)

Copyright 2009-2012. All Rights Reserved. 注意事项: 1.安装场所 远离高温的热源和环境,避免直接照射。 为确保本机的正常散热,应避开通风不良的场所。 为了防止电击和失火,请勿将本机放置于易燃、易爆的场所。 小心轻放本机避免强烈碰撞、振动等,避免安装在会剧烈震动的场所。避免在过冷、过热的场所间相互搬动本机,以免机器部产生结露,影响机器的使用寿命。 2.避免电击和失火 切记勿用湿手触摸电源开关和本机。 勿将液体溅落在本机上,以免造成机器部短路或失火。 勿将其它设备直接放置于本机上部。 安装过程中进行接线或改线时,都应将电源断开,预防触电。 重要提示: 为了避免损坏,请勿自动拆开机壳,必须委托有资格有专业维修人员在指定的维修单位进行维修。 清洁装置时,请勿使用强力清洗剂,当有灰尘时用干布擦拭装置。 不得在电源电压过高和过低的场合下使用该本机。 务请通读本使用说明书,以便您掌握如正确使用本机。当您读本说明书后,请把它妥善保存好,以备日后参考。如果需要维修,请在当地与经本公司授权的维修站联系。 环境防护: 本机符合电磁辐射标准,对人体无电磁辐射伤害。 申明:

产品的发行和销售由原始购买者在可协议条款下使用; 未经允,任单位和个人不得将该产品全部或部分复制、再生或翻译成其它机器可读形式的电子媒介; 本手册若有任修改恕不另行通知; 因软件版本升级而造成的与本手册不符,以软件为准。 目录 设备概述 (3) 第一部分控制矩阵切换系统 (4) 1.1键盘通电 (4) 1.2键盘操作加锁 (4) 1.3键盘操作解锁 (4) 1.4键盘密码设置 (4) 1.5选择监视器 (5) 1.6选择摄像机 (5) 1.7控制解码器 (5) 1.8控制智能高速球 (6) 1.9操作辅助功能 (7) 1.10系统自由切换 (8) 1.11系统程序切换 (9) 1.12系统同步切换 (10) 1.13系统群组切换 (10) 1.14报警联动 (10) 1.15防区警点 (11) 1.16警点状态 (11) 1.17声音开关 (11) 第二部分控制数字录像机、画面处理器 (11) 2.1进入数字录像机、画面处理器模式 (11) 2.2退出数字录像机、画面处理器模式 (11) 2.3选择数字录像机、画面处理器 (11) 2.4控制数字录像机、画面处理器 (12) 第三部分设置连接 (12) 3.1键盘工作模式 (12)

实验报告 课程名称:_____FPGA实验______指导老师:__竺红卫/陈宏__成绩:__________________ 实验名称:____拨动开关的消抖电路的设计___实验类型:_FPGA实验_同组学生姓名:__ 一、实验目的和要求(必填) 1. 熟悉软件对于消抖的实现原理; 2. 熟悉实验板拨动开关的工作方法。 二、实验内容和原理(必填) 实验板具有4个滑动开关,当开关关上或上拉时,FPGA的管脚连接3.3V电源,即逻辑高电平。断开或下拉时,FPGA管脚接地,逻辑低电平。一般开关的机械闭合时间为2ms,这里没有使用活动的回弹线路,尽管这种线路可以很容易地加到FPGA上。 实验需要实现的功能是:当RESET为低电平,不论SW为低电平或高电平,LED保持全灭;当RESET 为高电平,LED全亮;当RESET保持高电平时,每次SW由高电平变为低电平,对应的LED状态改变,而当SW由低电平变为高电平,对应的LED状态保持不变。 对LED引脚输出高电平时,LED点亮,,反之LED灭。 三、主要仪器设备(必填) 1. 电脑一台; 2. 实验板一块,Xilinx Spartan-3E; 3. 实验板电源一只; 4. 实验板连接电脑的下载线一根。 四、操作方法和实验步骤

对于程序的各个步骤,如新建项目、新建Verilog HDL、新建.ucf文件、Synthesize、Implement Design、Generate Programming File、Configure Target Device等等,在实验一中已经展示过,每一次实验的基本操作步骤都是差不多的,故这里不再重复阐述。 本次实验共有5个源代码需要编写、运行并解释: 1)未加debounce电路的源代码; 2)加了debounce电路的源代码; 3)由未加debounce电路的源代码出发,只添加锁存器的源代码; 4)由未加debounce电路的源代码出发,只添加滤波器的源代码; 5)加了debounce电路,并且一个开关控制3个灯,向上拨动开关时灭,向下亮的源代码。 前四种情况的.ucf文件如下: NET "CLK" LOC="C9"; NET "led_d3" LOC="C11"; NET "led_d4" LOC="F11"; NET "led_d5" LOC="E11"; NET "RST_N" LOC="L13"; NET "sw1" LOC="L14"; NET "sw2" LOC="H18"; NET "sw3" LOC="N17"; 最后一种情况的.ucf文件如下: NET "CLK" LOC="C9"; NET "led_d3" LOC="C11"; NET "led_d4" LOC="F11"; NET "led_d5" LOC="E11"; NET "RST_N" LOC="L13"; NET "sw1" LOC="L14"; 对于最后一种情况,只使用sw1同时控制板上的LD2、LD3、LD4。 五、实验源代码、现象和解释 1)未加debounce电路 源代码: `timescale 1ns/1ns module sw_led(clk, rst_n, sw1, sw2, sw3, led_d3, led_d4, led_d5); input clk; input rst_n; input sw1,sw2,sw3; //低电平有效 output led_d3; output led_d4; output led_d5; reg d1,d2,d3; always @ (posedge clk or negedge rst_n) if ( !rst_n ) begin d1 <= 1'b0; d2 <= 1'b0; d3 <= 1'b0;

按键消抖 1功能概述 按键开关是各种电子设备不可或缺的人机接口,如电脑的键盘等。实际应用中,按键开关通常为机械式弹性开关。当机械点断开、闭合时,由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定接通,断开时也不会马上断开,在闭合和断开的瞬间均伴随有一连串的抖动。为保证系统及时正确识别,必须对这种情况作出相应处理。我们称之为按键消抖。 按键消抖可分为硬件消抖和软件消抖。硬件消抖的原理是在信号输入系统之前消除抖动干扰,在按键较少的情况下比较适宜。如果按键较多,则使用软件消抖。软件消抖的实质在于降低键盘输入端口的采样频率,将高频抖动略去。需要注意的是,软件消抖需要占据一定的系统资源。 尽管硬件消抖和软件消抖能实现按键消抖功能,串行处理的方式都存在一定的局限性,显得不那么完美。而硬件资源丰富的FPGA系统采用并行处理的模式,利用硬件来减轻软件工作量,通过硬件加速软件消抖处理,即可做到软件消抖并行化,因而在按键消抖处理方面具备非常明显的优势。 优秀的设计程序应该是用最简单的代码(架构、信号)实现功能。在本例中,我们的只需要用4个信号界定,并用很短的代码即可。下面我们先来看看功能要求: 在系统设计中,消除按键抖动的方法五花八门,无论是硬件电路和软件设计都十分成熟。在本项目中,我们将用Verilog语言给出具体实现过程,设计一个程序来检查键值,有效滤除按键抖动区间20 ms的毛刺脉冲。 2 设计思路 一般按键所用开关为机械弹性开关,由于机械触点的弹性作用,每个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。因而在闭合及断开的瞬间均伴随有一连串的抖动,如下图。抖动时间的长短由按键的机械特性决定,一般为5 ms~10 ms。 1

按键消抖与时间按键 这篇文章写给正在学51单片机的或者刚入门51单片机准备进阶的的朋友,我们来着重讨论一下按键消抖和时间按键这两项。 我们常用的按键大多都是机械的,机械开关就会出现机械振动,这个由物理学或者实验可以推出来,抖动会在单片机上面出现重复扫描次数,次数多少与单片机的时钟晶振有关,时钟晶振越高单片机执行速度越快,重复次数就越多 整个按键数百ms 按下瞬间,抖动时间大概10ms 弹起瞬间,抖动大概10ms 按键一次出现的电平变化 (上面的时间都是老师说的和书上现成的,没有实际测试,而且不同的按键应该也会有差异,作为学习研究确实不应该,找个时间锅锅会测出这个时间供大家参考,嘿嘿) 由图我们可以看出,按下去瞬间会出现抖动,弹起来也会出现抖动,明显是个阻尼振动,按键扫描程序是按顺序执行的; 首先提出三个问题大家思考一下 1.为什么要消除抖动 2.如何消抖 3.是不是按键都要消抖,不是的话,哪些需要消抖,哪些不需要消抖 4.消抖的时间是不是必须10ms 5.按键消抖的方式是不是一定像书上的那样,如何消抖更节省CPU,且更简单 按键如果不消除抖动,那么单片机检测到的低电平的次数就不止一次,那我们按键一次,单片机会检测到多次,比如我们把按某个按键设置按一次成某个变量加1,结果按一次就加了很多次,这样我们就不能精确的通过按键来调整我们想要的参数,所以我们消除抖动的目的就是要实现按一次按键让单片机读出一次按键操作 消抖分硬件和软件消抖, 硬件消抖有《模拟电子技术》上提到用三态门实现,当然还有周立功那个7920(管理数码管和按键的芯片),当然还有很多硬件电路以及一些按键有自带消抖电路,但是如果要做产

9.3.1 矩阵键盘的工作原理和扫描确认方式 来源:《AVR单片机嵌入式系统原理与应用实践》M16华东师范大学电子系马潮 当键盘中按键数量较多时,为了减少对I/O 口的占用,通常将按键排列成矩阵形式,也称为行列键盘,这是一种常见的连接方式。矩阵式键盘接口见图9-7 所示,它由行线和列线组成,按键位于行、列的交叉点上。当键被按下时,其交点的行线和列线接通,相应的行线或列线上的电平发生变化,MCU 通过检测行或列线上的电平变化可以确定哪个按键被按下。 图9-7 为一个 4 x 3 的行列结构,可以构成12 个键的键盘。如果使用 4 x 4 的行列结构,就能组成一个16 键的键盘。很明显,在按键数量多的场合,矩阵键盘与独立式按键键盘相比可以节省很多的I/O 口线。 矩阵键盘不仅在连接上比单独式按键复杂,它的按键识别方法也比单独式按键复杂。在矩阵键盘的软件接口程序中,常使用的按键识别方法有行扫描法和线反转法。这两种方法的基本思路是采用循环查循的方法,反复查询按键的状态,因此会大量占用MCU 的时间,所以较好的方式也是采用状态机的方法来设计,尽量减少键盘查询过程对MCU 的占用时间。 下面以图9-7 为例,介绍采用行扫描法对矩阵键盘进行判别的思路。图9-7 中,PD0、PD1、PD2 为3 根列线,作为键盘的输入口(工作于输入方式)。PD3、PD4、PD5、PD6 为4根行线,工作于输出方式,由MCU(扫描)控制其输出的电平值。行扫描法也称为逐行扫描查询法,其按键识别的过程如下。 √将全部行线PD3-PD6 置低电平输出,然后读PD0-PD2 三根输入列线中有无低电平出现。只要有低电平出现,则说明有键按下(实际编程时,还要考虑按键的消抖)。如读到的都是高电平,则表示无键按下。 √在确认有键按下后,需要进入确定具体哪一个键闭合的过程。其思路是:依

一、按键消抖 1.1 计数器型消抖电路(一) 计数器型消抖电路(一)是设置一个模值为(N+1)的控制计数器,clk在上升沿时,如果按键开关key_in='1',计数器加1,key_in='0' 时,计数器清零。当计数器值为2时,key_out 输出才为1,其他值为0时。计数器值为N时处于保持状态。因此按键key_in持续时间大于N个clk时钟周期时,计数器输出一个单脉冲,否则没有脉冲输出。如果按键开关抖动产生的毛刺宽度小于N个时钟周期,因而毛刺作用不可能使计数器有输出,防抖动目的得以实现。clk的时钟周期与N的值可以根据按键抖动时间由设计者自行设定。 主要程序结构如下: 图1是N为3的波形仿真图,当按键持续时间大于3个时钟周期,计数器输出一个单脉冲,其宽度为1个时钟周期,小于3个时钟周期的窄脉冲用作模拟抖动干扰,从图1可以看出,抖动不能干扰正常的单脉冲输出。 1 按键抖动产生原因分析 绝大多数按键都是机械式开关结构,由于机械式开关的核心部件为弹性金属簧片,因而在开关切换的瞬间会在接触点出现来回弹跳的现象。虽然只是进行了一次按键,结果在按键信号稳定的前后出现了多个脉冲,如图1所示。如果将这样的信号直接送给微处理器扫描采集的话,将可能把按键稳定前后出现的脉冲信号当作按键信号,这就出现人为的一次按键但微处理器以为多次按键现象。为了确保按键识别的准确

性,在按键信号抖动的情况下不能进入状态输入,为此就必须对按键进行消抖处理,消除抖动时不稳定、随机的电压信号。机械式按键的抖动次数、抖动时间、抖动波形都是随机的。不同类型的按键其最长抖动时间也有差别,抖动时间的长短和按键的机械特性有关,一般为5~10 ms,但是,有些按键的抖动时间可达到20 ms,甚至更长。所以,在具体设计中要具体分析,根据实际情况来调整设计。 2 按键消抖电路的设计 按键消抖一般采用硬件和软件消抖两种方法。硬件消抖是利用电路滤波的原理实现,软件消抖是通过按键延时来实现。在微机系统中一般都采用软件延时的消抖方法。在用可编程逻辑器件FPGA/CPLD设计数字系统中,也可以用VHDL语言设计相应的时序和逻辑电路,对按键信号进行处理,同样可以达到消抖目的。本文利用Altera公司的可编程逻辑器件CPLD和QuartusⅡ,设计性能可靠的按键消抖电路。 2.1 按键消抖电路设计原理 按键消抖的关键是提取稳定的低电平(或高电平)状态,滤除按键稳定前后的抖动脉冲。在用基于VHDL 语言的时序逻辑电路设计按键消抖电路时,可以用一个时钟脉冲信号对按键状态进行取样,当第一次采样到低电平时,启动延时电路,延时结束后,再对按键信号进行连续三次取样,如果三次取样都为低电平,则可以认为按键已经处在稳定状态,这时输出一个低电平的按键确认信号,如果连续三次的取样中,至少有一次是高电平,则认为按键仍处在抖动状态,此时不进行按键确认,按键输出信号为高电平。 2.2 按键消抖电路设计 该控制电路采用VHDL语言的有限状态机的设计方法来描述和实现,其状态转换图如图2所示。

基于verilog按键消抖设计 Aaron malone 关于键盘的基础知识,我就以下面的一点资料带过,因为这个实在是再基础不过的东西了。然后我引两篇我自己的博文,都是关于按键消抖的,代码也正是同目录下project里的。这两篇博文都是ednchina的博客精华,并且在其blog 首页置顶多日,我想对大家会很有帮助的。 键盘的分类 键盘分编码键盘和非编码键盘。键盘上闭合键的识别由专用的硬件编码器实现,并产生键编码号或键值的称为编码键盘,如计算机键盘。而靠软件编程来识别的称为非编码键盘。 在单片机组成的各种系统中,用的最多的是非编码键盘。也有用到编码键盘的。非编码键盘有分为:独立键盘和行列式(又称为矩阵式)键盘。 按键在闭合和断开时,触点会存在抖动现象:

从上面的图形我们知道,在按键按下或者是释放的时候都会出现一个不稳定的抖动时间的,那么如果不处理好这个抖动时间,我们就无法处理好按键编码,所以如何才能有效的消除按键抖动呢?让下面的两篇博文日志给你答案吧。 经典的verilog键盘扫描程序 从最基础的分频程序开始,但看到这个键盘扫描程序后,直呼经典,有相见恨晚的感觉,还想说一句:威百仕( VibesIC ),我很看好你!WHY?待我慢慢道来,这个程序的综合后是0error,0warning。想想自己编码的时候那个warning是满天飞,现在才明白HDL设计有那么讲究了,代码所设计的不仅仅是简单的逻辑以及时序的关系,更重要的是你要在代码中不仅要表现出每一个寄存器,甚至每一个走线。想想我写过的代码,只注意到了前者,从没有注意过后者,还洋洋自得以为自己也算是个高手了,现在想来,实在惭愧啊!学习学习在学习,这也重新激发了我对HDL设计的激情,威百仕给了我一个方向,那我可要开始努力喽! 废话说了一大堆,看程序吧:(本代码经过ise7.1i综合并下载到SP306板上验证通过)

实验十五矩阵键盘接口电路的设计 一、实验目的 1、了解普通4×4键盘扫描的原理。 2、进一步加深七段码管显示过程的理解。 3、了解对输入/输出端口的定义方法。 一、实验原理 实现键盘有两种方案:一是采用现有的一些芯片实现键盘扫描;再就是用软件实现键盘扫描。作为一个嵌入系统设计人员,总是会关心产品成本。目前有很多芯片可以用来实现键盘扫描,但是键盘扫描的软件实现方法有助于缩减一个系统的重复开发成本,且只需要很少的CPU 开销。嵌入式控制器的功能能强,可能充分利用这一资源,这里就介绍一下软键盘的实现方案。 图15-1 简单键盘电路 通常在一个键盘中使用了一个瞬时接触开关,并且用如图15-1 所示的简单电路,微处理器可以容易地检测到闭合。当开关打开时,通过处理器的I/O 口的一个上拉电阻提供逻辑1;当开关闭合时,处理器的/IO 口的输入将被拉低得到逻辑0。可遗憾的是,开关并不完善,因为当它们被按下或者被释放时,并不能够产生一个明确的1 或者0。尽管触点可能看起来稳定而且很快地闭合,但与微处理器快速的运行速度相比,这种动作是比较慢的。当触点闭合时,其弹起就像一个球。弹起效果将产生如图15-2 所示的好几个脉冲。弹起的持续时间通常将维持在5ms~30ms 之间。如果需要多个键,则可以将每个开关连接到微处理器上它自己的输入端口。然而,当开关的数目增加时,这种方法将很快使用完所有的输入端口。

图15-2 按键抖动 键盘上阵列这些开关最有效的方法(当需要5 个以上的键时)就形成了一个如图15-3 所示的二维矩阵。当行和列的数目一样多时,也就是方型的矩阵,将产生一个最优化的布列方式(I/O 端被连接的时候)。一个瞬时接触开关(按钮)放置在每一行与线一列的交叉点。矩阵所需的键的数目显然根据应用程序而不同。每一行由一个输出端口的一位驱动,而每一列由一个电阻器上拉且供给输入端口一位。 图15-3 矩阵键盘 键盘扫描的实现过程如下:对于4×4键盘,通常连接为4行、4列,因此要识别按键,只需要知道是哪一行和哪一列即可,为了完成这一识别过程,我们的思想是,首先固定输出4行为高电平,然后输出4列为低电平,在读入输出的4行的值,通常高电平会被低电平拉低,如果读入的4行均为高电平,那么肯定没有按键按下,否则,如果读入的4行有一位为低电平,那么对应的该行肯定有一个按键按下,这样便可以获取到按键的行值。同理,获取列值也是如此,先输出4列为高电平,然后在输出4行为低电平,再读入列值,如果其中有哪一位为低电平,那么肯定对应的那一列有按键按下。 获取到行值和列值以后,组合成一个8位的数据,根据实现不同的编码在对每个按键进行匹配,找到键值后在7段码管显示。 二、实验内容 本实验要求完成的任务是通过编程实现对4X4矩阵键盘按下键的键值的读取,并在数码管上完成一定功能(如移动等)的显示。按键盘的定义,按下“*”键则在数码管是显示“E”键值。按下“#”键在数码管上显示“F”键值。其它的键则按键盘上的标识进行显示。 在此实验中数码管与FPGA的连接电路和管脚连接在以前的实验中都做了详细说

前几天看了特权同学用Verilog写的按键消抖程序,感觉很经典。在这里将程序贴出来分享一下。 module lcd_button2(clk,rst,seg,wei,sw1,sw2,sw3,sw4);//按键按下,数码管依次显示0-9 input clk; input rst; input sw1,sw2,sw3,sw4; output [3:0] wei; output[7:0] seg; reg [7:0] seg; reg [3:0] wei; integer num; initial begin num = 0; end reg[3:0] key_rst; always @(posedge clk or negedge rst) if(!rst) key_rst <= 4'b1111; else key_rst <= {sw4,sw3,sw2,sw1}; reg[3:0] key_rst_r; always @(posedge clk or negedge rst) if(!rst) key_rst_r <= 4'b111; else key_rst_r <= key_rst; wire[3:0] key_an = key_rst_r & (~key_rst); reg[19:0] cnt; always @(posedge clk or negedge rst) if(!rst) cnt <= 0; else if(key_an) cnt <= 0; else cnt <= cnt+1'b1; reg [3:0] low_sw; always @(posedge clk or negedge rst)

实 验 报 告 实验日期: 学 号: 姓 名: 实验名称: 消抖电路 总 分: 一、实验概述 运用LPM 原件定制DFF 触发器,并调用LPM 定制的DFF 触发器,用VHDL 语言的元件例化实现消抖电路并了解其工作原理。 二、实验原理 1、触发器原理 触发器是一种可存储1位二进制码的逻辑电路,是构成各种时序电路的最基本逻辑单元。触发器有一对互补输出端,输出状态不仅与当前输入有关,还与前一输出状态有关。触发器有两个稳定状态,在一定的外界信号作用下会发生状态翻转。 2、消抖电路原理 脉冲按键与电平按键通常采用机械式开关结构,其核心部件为弹性金属簧片。按键信号在开关拨片与触电接触后经多次弹跳才会稳定,而在按键过程中,可能出现了多个脉冲。因此需要根据实际情况进行按键消抖处理以提取稳定脉冲,在按键过程中提取稳定的电平状态,通过对抖动脉冲多次检测信号按键电平值,并提取一前一后两个信号按键电平值来进行比较,以此来获取开关状态。输出一个周期的脉冲时,要求前一次检测到的电平信号为低电平,后一次检测到的电平信号为高电平时。 3、结构图: 三、实验设计 时钟信号 元件记忆当前的按键信号电平 元件记忆上一次按键信号电平 两次按键的电平进行比较 脉冲信号

1、LPM元件定制DFF触发器 (1)设置lpm_ff元件选择Installed Plug-Ins→Storage→lpm_ff项。 (2)LPM元件定制步骤,设置输入data为1位,clock为时钟信号,类型为D 型。 (3)添加异步清零和异步置1。 (4)aclr异步清零且高电平有效,aset异步置1且高电平有效,二者无效时,q输出由clock上升沿触发更新为data。 (5)调出其vhd文件添加至消抖电路的工程中。 (6)仿真验证并下载。 功能仿真波形分析 参数:end time 为2.0ns,grid size为100ns; 信号:alcr 异步清零且高电平有效,二进制; aset异步置1且高电平有效,二进制; 二者无效,q(二进制)输出由clock(二进制)上升沿触发更新为 data(二进制)。 aclr输入无效,aset 输入有效,q输出1 aclr和aset均无效,q输出1;clock上升时,触发更新为data,q输出0 aclr和 aset均无 效,q输 出1; clock上 升时,触 发更新 为data, q输出1; aclr异步 清零,q 输出0 aclr有 效,aset 无效,清 零得q输 出0;aclr 和aset 均无效, q输出0; clock上 升时,触 发更新 为data, q输出0;

module sw_de(clk,rst_n,sw1_n,sw2_n,sw3_n,led_d1,led_d2,led_d3); input clk; //主时钟信号 50MHz input rst_n; //复位信号 低有效 input sw1_n,sw2_n,sw3_n;//三个独立按键 低表示按下 output led_d1,led_d2,led_d3;//发光二级管,分别由按键控制 //------------------------------------------------------ reg[2:0] key_rst; always @ (posedge clk or negedge rst_n) if(!rst_n) key_rst<=3'b111; else key_rst <= {sw3_n ,sw2_n ,sw1_n}; reg[2:0] key_rst_r;//每个时钟周期的上升沿将low_sw信号锁存到low_sw_r中 always @ (posedge clk or negedge rst_n) if(!rst_n) key_rst_r<=3'b111; else key_rst_r<=key_rst; //当寄存器key_rst由1变为0时,led_an的值变为高,维持一个时钟周期 wire[2:0]key_an=key_rst_r&(~key_rst); //----------------------------------------------------- reg[19:0] cnt;//计数寄存器 always @ (posedge clk or negedge rst_n)/*always块clk时钟的上升沿和rst_n复位信号的下降沿触发执行*/ if (!rst_n) cnt<=20'd0; else if (key_an) cnt<=20'd0; else cnt<=cnt+1'b1; reg[2:0] low_sw;

按键电路:常用的非编码键盘,每个键都是一个常开开关电路。 按键消抖: 通常的按键所用开关为机械弹性开关,当机械触点断开、闭合时,电压信号小型如下图。由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。因而在闭合及断开的瞬间均伴随有一连串的抖动,如下图。抖动时间的长短由按键的机械特性决定,一般为5ms~10ms。这是一个很重要的时间参数,在很多场合都要用到。 按键稳定闭合时间的长短则是由操作人员的按键动作决定的,一般为零点几秒至数秒。键抖动会引起一次按键被误读多次。为确保CPU对键的一次闭合仅作一次处理,必须去除键抖

动。在键闭合稳定时读取键的状态,并且必须判别到键释放稳定后再作处理。按键的抖动,可用硬件或软件两种方法。 <1> 硬件消抖:在键数较少时可用硬件方法消除键抖动。下图所示的RS触发器为常用的硬件去抖。 图中两个“与非”门构成一个RS触发器。当按键未按下时,输出为1;当键按下时,输出为0。此时即使用按键的机械性能,使按键因弹性抖动而产生瞬时断开(抖动跳开B),中要按键不返回原始状态A,双稳态电路的状态不改变,输出保持为0,不会产生抖动的波形。也就是说,即使B 点的电压波形是抖动的,但经双稳态电路之后,其输出为正规的矩形波。这一点通过分析RS触发器的工作过程很容易得到验证。 <2> 软件消抖:如果按键较多,常用软件方法去抖,即检测出键闭合后执行一个延时程序,产生5ms~10ms的延时,让前沿抖动消失后再一次检测键的状态,如果仍保持闭合状态电平,则确认为真正有键按下。当检测到按键释放后,也要给5ms~10ms的延时,待后沿抖动消失后才能转入该键的处理程序。按键消抖

矩阵键盘操作说明 一、系统复位 1按数字键0后,按MON键 2输入99后,按NEXT键 二、键盘视频选择 首先是监视器选择然后是摄像机选择 1、按键盘上的CLEAR键,清除键盘数字输入ENTER区中的数字显示 2、输入所选择的监视器号,该数字在键盘数字输入ENTER区中显示 3、按MON键,该监视器号在键盘监视器MONITOR区中显示 4、同时系统主机将返回该监视器对应的图像号,在键盘的摄像机CAMERA区中显示。 5、输入选择的摄像机号,该数字在键盘数字输入ENTER区中显示 6、按CAM键 7、系统主机将返回该图像号,在键盘的摄像机CAMERA区中显示则选择的图像再选择的 监视器上显示 三、图像区域切换 在指定的监视器上运行一个指定区域的图像切换,该功能可以在任何一个监视上浏览切换所有的图像操作步骤如下: 1、按键盘上CLERA键,清除数字输入ENTER区中的数字显示 2、输入所选择的监视器号,该数字在键盘数字输入ENTER区中显示 3、按MON键,该监视器号在键盘监视器MONITOR区中显示 4、输入区域切换中的开始图像号 5、按ON键,确认开始区域的开始图像 6、输入区域切换中的结束图像号 7按OFF键确定区域切换的结束图像 完成后则该监视器开始区域切换依次按照设定的图像号进行切换如要添加一个图像到切换序列中则: 1和设置区域切换的步骤一样重复1-3步,选择一个监视器,该监视必须已存在一个切换队列 2、输入所希望添加的摄像机图像好,该摄像机图像号必须在系统的最大允许摄像机图像号的范围内 3、按组合键ENTER-ON,ENTER键必须在前面,确定添加的图像。 如要在切换队列中删除一个图像: 1、和设置区域切换的步骤一样重复1-3步,选择一个监视器,该监视必须已存在一个切换队列 2输入所希望添加的摄像机图像好,该摄像机图像号必须在这个序列切换范围内。 3、按组合键ENTER-OFF,ENTER必须在前面,确认删除图像。 四、报警设置 单布防 针对需要布防的防区一个一个的布防,防区布防后,根据监视器与防区触点权限表,自动将该防区分配到与之对应的监视器上。一旦报警,则与之相关的报警监视器就可以对这个报警防区进行响应。具体操作如下1、输入防区号 2、按组合键ARM-ON,ARM键必须先按,对该报警防区进行确认。 全布防。撤防即按ARM-OFF键 1、输入数字键0

实验五按键消抖 一. 实验目的 1. 掌握QuartusII的硬件描述语言设计方法 2. 了解同步计数器的原理及应用 3. 设计一个带使能输入、进位输出及同步清零的增1四位N (N<16)进制同步计数器 二. 准备知识 在按键使用的过程中,常常遇到按键抖动的问题,开关在闭合(断开)的瞬间,不能一接触就一直保持导通(断开),因为开关的机械特性,重要经历接触-断开-再接触-再断开,最终稳定在接触位置,这就是开关的抖动,即虽然只是按下按键一次然后放掉,结果在按键信号稳定前后,竟出现了一些不该存在的噪声,这样就会引起电路的误动作。在很多应用按键的场合,要求具有消抖措施。按键抖动与开关的机械特性有关,其抖动期一般为5-10ms。 键按下 键稳定 前沿抖动后沿抖动 图5.1 按键电平抖动示意图 按键的消除抖动分为硬件消除抖动和软件消除抖动。硬件消除抖动一般采用滤波的方法,通常在按键两端并联一个1~10u左右的电容,有时这样也不能完全消除按键的抖动。软件消除抖动的方法有多种,常用的是延时扫描和定时器扫描。延时扫描其原理为:检测到按键操作后延时一端时间(如10ms)后,再检测是否为仍然为同样的按键操作状态,如果相同,就认为是进行了按键操作,然后对该操作进行相应的处理。定时器扫描的原理是:每隔一端时间(几毫秒)扫描一次键盘,如果连续两次(或3次)的所获得的按键状态相同,就输出按键状态,然后再对这种按键状态进行处理,这里的扫描时间间隔和连续判断按键状态的次数是有关系的,一般总时间要大于按键的抖动期。如果总时间太长,则感觉按键迟钝,太短可能不能完全消除抖动,要根据实际的情况合适的选择。 在实际电路设计中,经常采用的是软硬件相结合对按键进行消除抖动的处理方法。 本实验采用的方法:实验箱按键的硬件电路是共阳极电路,按下按键时输出到FPGA管脚的电平为低电平,松开按键时为高电平。我们采用5ms的定时器扫描FPGA管脚电平,如果连续3次为低电平时,存储连续按键状态的次数CNT的值加1,直到该计数值等于10(或再大一些),就不再累加(防止长按该值溢出而重新计数),此时认为按键已稳定,输出按键操作标志;在该过程中,一旦FPGA管脚电平为低电平就对CNT复位清零并同时对按键操作标志位复位,即一个异步复位。 本实验采用的方法:实验箱按键的硬件电路是共阳极电路,按下按键时输出到FPGA管脚的电平为低电平,松开按键时为高电平。我们采用5ms的定时器扫描采样FPGA管脚电平,如果连续3次为低电平时,可以认为此时按键已稳定,输出一个低电平按键信号;继续采样的过程中如果不能满足连续3次采样为低,则认为键稳定状态结束,这时输出变为高电平(连线3次采用信号相“或”),

按键消抖电路瞬态分析和设计 按键是仪器仪表中普遍采用的人机输入接口电路。在按键电路中必须考虑对按键的抖动进行软件消抖和硬件消抖。软件消抖具有使用硬件数量少的优点,但也具有以下两个缺点:(1)在仪器键盘电路中,多个按键安装在仪器面板上,键盘的输出通过排线连接到主控板上,此时键盘导线寄生电感和寄生电容的存在,寄生电感寄生电容和排线电阻将组成二阶振荡系统,二阶振荡将形成负电平脉冲,而负电平脉冲很容易超出数字芯片的输入最大允许电平范围,导致数字芯片容易损坏。(2)按键闭合和断开时,电压信号下降沿非常陡峭,剧烈变化的电压信号将通过互容传递到相邻导线上。硬件消抖电路的设计主要是要考虑以下三个因素:(1)消除信号的抖动,确保按键电路输出信号的平整;(2)消除信号的下冲,因为下冲电平超出了后续数字芯片的最大输入电平范围;(3)降低信号变化的速度,避免在邻线上引起容性串扰;(4)不影响按键电路的正常功能。常见的硬件消抖电路包括电容滤波消抖和触发器消抖。电容滤波消抖采用电阻和电容组成低通滤波器,具有电路结构简单可靠的优点,因此本文将重点阐述该消抖电路。1 按键消抖电路结构与电路模型图1为某仪器按键电路原理图,按键安装在仪器面板上,通过导线连接到主控板上,按键的一端接上拉电阻并连接后续电路,按键的另一端接地,当按键没有按下时,按键输出高电平,当按键按下时,按键输出低电平。图2为加上滤波电容后的按键电路。 图1 某仪器按键电路 图2 按键消抖电路 图3为按键消抖电路的电路模型。图中R0为连接按键导线的电阻,L 为导线电感,C0为导线对地电容,C f为滤波电容,C p为按键后续电路的输入电容,R i为按键后续电路的输入阻抗,R 为上拉电阻,V CC为电源电压,U为按键消抖电路的输出电压。

4×4矩阵键盘 1.原理说明 一般的4*4矩阵键盘(如图1)一般要8个I/O口(如图1),对于按键较多的硬件系统来说是很浪费的I/O口,本方案仅采用4个I/O和4个普通二极管就可以轻松实现4×4矩阵键盘,方案原理与普通4*4矩阵键盘类似,下面先分析普通矩阵键盘原理,再进一步改进为本方案。 原理如下B4口为低电平,A1~A4,B1~B3为高电平,单片机不停的扫描,假若有键按下如A1与B4交叉处按下则对应的A1被拉低为低电平,可以定义此键号为1,同理以此类推B3口为低电平,其余口为高电平,交叉处按键按下可定义其按键号,将按键号存储在寄存器中,可用查表方法并通过数码管显示按键号。 对于下图(图2)用4个I/O和4个普通二极管初始化PA0.0~PA0.3 均为高电平,在这里二极管作用是当IO口为低电平时可以导通,高电平时截止。程序流程图如下 图1

图2 2.程序介绍如下 void RCC_Configuration(void); { RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA|RCC_APB2Periph_AFIO,ENABLE); } void GPIO_Configuration(void) { GPIO_InitTypeDef GPIO_InitStructure; GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0| GPIO_Pin_1| GPIO_Pin_2| GPIO_Pin_3; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_PP _ OUT; GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; GPIO_Init(GPIOA, &GPIO_InitStructure); } GPIOSetBits() { GPIO_SetBits(GPIOA,GPIO_Pin_0);

按键去抖动 一、实验目的 1、学习基于VHDL 描述状态机的方法; 2、学习 VHDL 语言的规范化编程,学习按键去抖动的原理方法。 二、实验平台 微机一台(Windows XP 系统、安装QuartusⅡ等相关软件)、CPLD 学习板一块、5V 电源线一个、下载线一条。 三、设计要求 机械式轻触按键是常用的一种外围器件,由于机械原因导致的抖动会使得按键输入出现毛 刺。设计一个按键去抖动电路,并用按键作为时钟,结合计数器观察去抖动前后的效果有什么不同。 四设计方案 思路提示:按键去抖动通常采用延时判断的方法,去除按键过程中出现的毛刺。其实现过程是:当查询到按键按下时,延时一段时间再去判断按键是否仍然被按下,若是则此次按键有 效,否则看作是干扰。这可以利用状态机来实现, library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity qudou is port( clk, en: in std_logic; sp: out integer range 0 to 7); end qudou ; architecture behave of qudou is type state is (S0,s1,s2);

signal z: std_logic; signal q: integer range 0 to 2; signal a: integer range 0 to 7; signal s: state; begin p1:process(clk) begin if(clk'event and clk = '1') then if en='1' then if q=2 then q<=q; else q<=q+1; end if; else q<=0; end if; if q=2 then z<='1'; else z<='0'; end if; case s is when s0=> if (z = '0') then s<=s0;a<=a; else s<=s1;a<=a+1; end if; when s1=> if (z='0') then s<=s0;a<=a; else s<=s2;a<=a; end if; when s2=> if (z='0') then s<=s0;a<=a; else s<=s2;a<=a; end if; end case; sp<=a; end if; end process p1; end behave;

河海大学物联网工程学院Verilog HDL项目设计报告 题目拔河游戏机 专业电子科学与技术 学号1562910123、1562910125 授课班号 6292758 学生徐子豪、诗欣 指导教师华迪、齐本胜

摘要和关键字 为了掌握数字系统的设计方法,掌握硬件描述语言——Verilog HDL,掌握模块化设计方法,掌握开发软件的使用方法。选择 基于FPGA开发板设计的拔河游戏机,使用两个按键进行比赛,利用按键按下的快慢作为模拟的双方选手拔河过程,led灯的变化决定绳子的位置,led灯到了一边以后比赛终止,整个过程的难点在于,需要过滤信号,使按键产生的信号稳定,所以程序中需要有按键消抖模块,同时需标识符来控制比赛的开始与结束。关键词:verilog 拔河比赛消抖模块标识符 In order to master the design method of digital system, we must master the hardware description language -- Verilog HDL, grasp the modular design method and master the way of developing software. Choice Tug of war game FPGA development board based on the design, the use of two button game, using key press speed as both

players tug of war of simulation, change led lamp decide the position of the rope, LED lights to the side after the end game, the difficulty lies in the whole process, need to filter the signal, the stable signal generated by the keys so, the procedure requires a key debounce module, also need to control the game's identifier and end start. Key words: Verilog tug shake-off module identifier. 一、系统设计 1 . 实验要求 设计拔河游戏电路,用按键与LED表示输入与输出。 (1)初始时,16个LED中间的两个点亮,然后游戏双方不停按动按键,点亮的两个LED向按动按键慢的一方移动;(2)每按动一下按键,LED向对方移动一格; (3)只要LED移动到头,游戏结束; (4)工作时钟100Hz即可; (5)完成全部流程:设计规文档、模块设计、代码输入、功能仿真、约束与综合、布局布线、时序仿真、下载验证等。