课题三数字频率计逻辑电路设计

一﹑简述

在进行模拟﹑数字电路的设计﹑安装和调试过程中,经常要用到数字频率计。

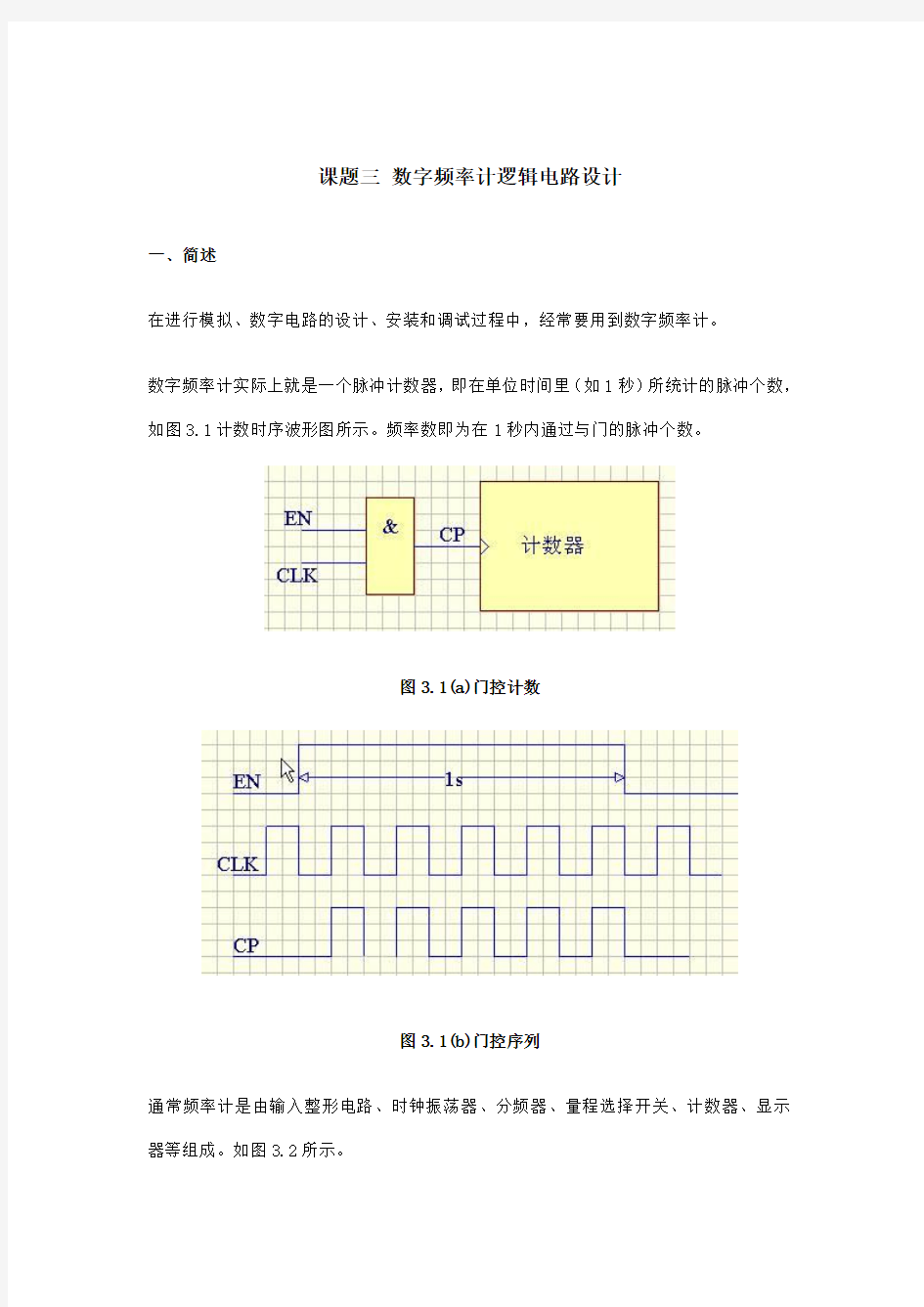

数字频率计实际上就是一个脉冲计数器,即在单位时间里(如1秒)所统计的脉冲个数,如图3.1计数时序波形图所示。频率数即为在1秒内通过与门的脉冲个数。

图3.1(a)门控计数

图3.1(b)门控序列

通常频率计是由输入整形电路﹑时钟振荡器﹑分频器﹑量程选择开关﹑计数器﹑显示器等组成。如图3.2所示。

图3.2 方框图

图3.2中,由于计数信号必须为方波信号,所以要用史密特触发器对输入波形进行整形,分频器输出的信号必须为1Hz,即脉冲宽度为1秒,这个秒脉冲加到与门上,就能检测到待测信号在1秒内通过与门的个数。脉冲个数由计数器计数,结果由七段显示器显示。二﹑设计任务和要求

设计一个八位的频率计数器逻辑控制线路,具体任务和要求如下:

1. 八位十进制数字显示。

2. 测显范围为1Hz~10MHz。

3. 量程分为四档,分别为*1000﹑*100﹑*10﹑*1。

三﹑可选用器材

1. NET系列数字电子技术实验系统

2. 直流稳压电源

3. 集成电路:频率计数器专用芯片ICM7216B,74LS93,74LS123,74LS390,7555及门电路

4. 晶振:8MHz,10MHz

5. 数显:CL102,CL002,LC5011—11

6. 电阻﹑电容等

四﹑设计方案提示

数字频率计可分为三部分进行考虑:

1. 计数﹑译码﹑显示

这一部分是频率计数器不可少的。即外部整形后的脉冲。通过计数器在单位时间里进行计数﹑译码和显示。计数器选用十进制的中规模(TTL/CMOS)集成计数器均可,译码显示可采用共阴或共阳的配套器件。例如计数器选用74LS161,译码器为74LS248,数显器为LC5011—11。也可选用四合一计数﹑寄存﹑译码﹑显示CL102或专用大规模频率计数器ICM7216芯片等。

中规模组成的计数﹑译码显示和四合一的数显。我们在基本实验和前几个课题中都已使用过,使用时,可参阅有关章节。下面介绍一下专用八位通用频率计数器ICM7216的特点及性能。

ICM7216是用COMS工艺制造的专用数字集成电路,专用于频率﹑周期﹑时间等测量。ICM7216为28管脚,其电源电压为5V。针对不同的使用条件和用途,ICM7216有四种类型产品,其中显示方式为共阴极LED显示器的为ICM7216 B型和D型,而显示方式为共阳极LED显示器的为ICM7216 A型和C型。图3.3为ICM7216B型的外管脚排列图。A﹑

C ﹑D型的管脚排列定义略有区别,但功能一样,使用时参阅有关ICM7216产品手册即可。

图3.3 ICM7216B型的外管脚排列图

在图3.3中,各管脚的功能为:

a~f:为七断数码管的输出端,ICM7216 B接共阴数码管。

fA﹑fB:频率计数输入端。

V+:电源正极,为单电源5V。

GND:电源地端。

HOLD:保持控制输入端,高电平有效。

:复位输入端,低电平有效。

dp:数码管小数点。

OSC0,OSC1:晶振输入端,可以直接选用10MHz或1MHz晶振构成高稳定时钟振荡。

EOI:它是EX-OSC-IN的缩写,即外时钟输入端。若用外时钟,则不需要在OSC0﹑OSC1端接晶振。

D1~D8:显示器段扫描输出位及控制用连线位。用于控制选择CONT,功能选择FUNC,量程选择RANGE,具体功能见表3.1。

表3.1 ICM7216B功能选择

CONT:控制选择输入端。

FUNC:功能选择输入端。

RANGE:量程选择输入端。

在应用过程中,各控制端(CONT﹑FUNC﹑RANGE)应串10kΩ电阻分别接到连接位(D1~D5或D8),以提高其抗干扰能力。

它的具体应用见参考电路3.5所示。

2.整形电路

由于待测信号是各种各样的,有三角波﹑正弦波﹑方波等,所以要使计数器准确计数,必须将输入波形进行整形,通常采用的是史密特集成触发器。史密特触发器也可由555(7555)或其它门电路构成。

3.分频器

分频器一般由计数器实现,例如用十进制计数器去分频。获得1Hz。

十进制计数器用74LS160﹑74LS161﹑74LS90﹑74LS290、74LS390等均可实现。

4.量程选择

由于输入频率有大有小,所以当测低频时,量程开关选择在*1或*10位置,而测高频时,应设置*100或*1000位置,在电路处理上就是将单位时间缩小为1/1000、1/100、1/10等,即在1/1000 秒测得的数值,其量程为数显值*1000;1/100 秒测得的数值,其量程值为数显值*100,余类推。所以我们这里选用1/1000﹑1/100﹑1/10﹑1 秒四档作为脉冲输入的门控时间,完成量程的选择。

五﹑参考电路

根据设计任务的要求,频率计逻辑电路可用大中规模集成电路或专用频率计数器构成,参考电路分别如图3.4和图3.5所示。

图 3.4

图 3.5

六﹑参考电路简要说明

1.图3.4采用八只CMOS电路CL102四合一显示完成计数﹑译码﹑显示功能。

输入待测频率经7555电路进行整形后,输入给CL102进行计数。

由晶振(8MHz)与门电路组成的振荡器经74LS93和74LS390分频后,分别获得1M﹑105﹑104﹑103﹑102﹑101﹑1Hz。图中74LS93为8 分频器,74LS390为双十进制计数器。1Hz控制计数器的计数时间,在计数器清零之前,将计数器的计数值送显示器,其时序电路如图3.6所示。

图3.6清零送数时序波形图

74LS123是单稳态触发器,其主要作用:U1是将1Hz脉冲变成窄脉冲,将CL102计数器数据寄存显示;U2产生的窄脉冲是计数器的清零脉冲,相对于送数脉冲延时了100ns 左右,以保证寄存器的数据正确,其频率由开关K分别置在4﹑3 ﹑2﹑1位置,即可完成*1﹑*10﹑*100﹑*1000等几种不同的量程。如测试量程不用开关,则需增加显示器的数量,从而达到满意的量程。小数点的控制,可根据量程确定,点亮的显示器的dp端接到+5V,其它位的dp接到地上。如不需要显示小数点,可全部接地。

2.在图

3.5中,数显为共阴极八位LED数显,型号为LC5011—11,晶振为10MHz。频率从fA或fB输入。八只数显LC5011—11的a —f﹑dp全部连在一起,分别接至ICM7216B 的a—f﹑dp端,数码管的公共端COM8—COM1分别接ICM7216B的D8—D1端。

S1为量程(自动小数点)选择开关,S2为测量功能选择开关,工作模式选控开关为S3—S7,保持按钮为HOLD,复位开关为。

如果外接1MHz晶体工作,就应把开关S7连通(ON)。其余模式选择方法类推,可参考前述表3.1。在S3—S7上串接隔离二极管,可防止有两只以上开关连通时位输出互为负载而损坏器件。

送入fA﹑fB信号,可以是TTL电平,也可以HCMOS电平,如果是CC4000系列器件送来的信号,则应当把连到V+的3kΩ电阻增大到10kΩ以上或者去掉电阻。通常用单稳电路作为输入波形整形。本电路若将输入型号进行10分频,则测量范围可以提高10倍。

3.图3.4﹑图3.5所示参考电路中,有些IC电路和地未画出,使用时应加上它。

简易数字频率计设计报告 设计内容: 1、测量信号:方波、正弦波、三角波; 2、测量频率范围: 1Hz~9999Hz; 3、显示方式:4位十进制数显示; 4、时基电路由由555构成的多谐振荡器产生(当标准时间的精度要求较高时,应通过晶体振荡器分频获得); 5、当被测信号的频率超出测量范围时,报警。 设计报告书写格式: 1、选题介绍和设计系统实现的功能; 2、系统设计结构框图及原理; 3、采用芯片简介; 4、设计的完整电路以及仿真结果; 5、Protel绘制的电路原理图; 6、制作的PCB; 7、课程设计过程心得体会(负责了哪些内容、学到了什么、遇到的难题及解决方法等)。 电子课程设计过程: 系统设计→在Multisim2001下仿真→应用Protel 99SE绘制电路原理图→制作PCB →撰写设计报告

简易数字频率计课程设计报告 第一章技术指标 1.1整体功能要求 1.2系统结构要求 1.3电气指标 1.4扩展指标 1.5设计条件 第二章整体方案设计 2.1 算法设计 2.2 整体方框图及原理 第三章单元电路设计 3.1 时基电路设计 3.2闸门电路设计 3.3控制电路设计 3.4 小数点显示电路设计 3.5整体电路图 3.6整机原件清单 第四章测试与调整 4.1 时基电路的调测 4.2 显示电路的调测 4-3 计数电路的调测 4.4 控制电路的调测 4.5 整体指标测试 第五章设计小结 5.1 设计任务完成情况 5.2 问题及改进

5.3心得体会附录 参考文献

第一章技术指标 1.整体功能要求 频率计主要用于测量正弦波、矩形波、三角波和尖脉冲等周期信号的频率值。其扩展功能可以测量信号的周期和脉冲宽度。 2.系统结构要求 数字频率计的整体结构要求如图所示。图中被测信号为外部信号,送入测量电路进行处理、测量,档位转换用于选择测试的项目------频率、周期或脉宽,若测量频率则进一步选择档位。 数字频率计整体方案结构方框图 3.电气指标 3.1被测信号波形:正弦波、三角波和矩形波。 3.2 测量频率范围:分三档: 1Hz~999Hz 0.01kHz~9.99kHz 0.1kHz~99.9kHz 3.3 测量周期范围:1ms~1s。 3.4 测量脉宽范围:1ms~1s。 3.5测量精度:显示3位有效数字(要求分析1Hz、1kHz和999kHz的测量误 差)。 3.6当被测信号的频率超出测量范围时,报警. 4.扩展指标 要求测量频率值时,1Hz~99.9kHz的精度均为+1。

长安大学 电子技术课程设计 数字频率计的设计 专业: 班级: 姓名 指导教师: 日期:

目录 引言 第一章系统概述 一、设计方案的选择 1、计数法 2、计时法 二、整体框图及原理 第二章单元电路设计 一、放大电路设计 二、闸门电路设计 三、时基电路设计 四、控制电路设计 五、报警电路设计 六、整体电路图 七、整机元件清单 第三章设计小结 一、设计任务完成情况 二、问题及改进 三、心得体会 鸣谢 附录

引言 题目:数字频率计的设计 初始条件: 本设计可以使用在数模电理论课上学过或没学过的集成器件和必要的门电路构建简易频率计,用数码管显示频率计数值。 要求完成的主要任务: ①设计一个频率计。要求用4位7段数码管显示待测频率,并用发光二极管表示单位。 ②测量频率的范围:100hz—100khz。 ③测量信号类型:正弦波和方波。 ④具有超量程报警功能。 摘要: 本次课程设是基于TTL系列芯片的简易数字频率计,数字频率计应用所学的数字电路和模拟电路的知识进行设计。在设计过程中,所有电路仿真均基于Multisim仿真软件。本课程设计介绍了简易频率计的设计方案及其基本原理,并着重介绍了频率计各单元电路的设计思路,原理及仿真,整体电路的的工作原理,控制器件的工作情况。设计共有三大组成部分:一是原理电路的设计,本部分详细讲解了电路的理论实现,是关键部分;二是性能测试,这部分用于测试设计是否符合任务要求。三是是对本次课程设计的总结。 关键字:频率计、TTL芯片、时基电路、逻辑控制、分频、计数、报警

第一章系统概述 一、设计方案的选择 信号的频率就是信号在单位时间内所产生的脉冲个数,其表达式为f=N/T,其中f为被测信号的频率,N为计数器所累计的脉冲个数,T为产生N个脉冲所需的时间。计数器所记录的结果,就是被测信号的频率。如在1s内记录1000个脉冲,则被测信号的频率为1000HZ。测量频率的基本方法有两种:计数法和计时法,或称测频法和测周期法。 1、计数法 计数法是将被测信号通过一个定时闸门加到计数器进行计数的方法,如果闸门打开的时间为T,计数器得到的计数值为N1,则被测频率为f=N1/T。改变时间T,则可改变测量频率范围。如图(1-1-1) 计数值N1 被测信号 标准闸门 T 图 1-1-1 测频法测量原理 设在T期间,计数器的精确计数值应为N,根据计数器的计数特性可知,N1的绝对误差是N1=N+1,N1的相对误差为δN1=(N1-N)/N=1/N。由N1的相对误差可知,N的数值愈大,相对误差愈小,成反比关系。因此,在f以确定的条件下,为减少N的相对误差,可通过增大T的方法来降低测量误差。当T为某确定值时(通常取1s),则有f1=N1,而f=N,故有f1的相对误差:δf1=(f1-f)/f=1/f 从上式可知f1的相对误差与f成反比关系,即信号频率越高,误差越小;而信号频率越低,则测量误差越大。因此测频法适合用于对高频信号的测量,频率越高,测量精度也越高。

数字逻辑电路设计及应用 C程序设计报告(1) [问题]: 设计一个C程序实现任意十进制数到二进制数的转换,二进制精度为11位。 [思路]: 1.十进制数转二进制数对整数和小数的处理时不一样的。所以设计程序时,也应该对读入 的整数和小数的数据分开处理。(分开的办法可以先直接对浮点数强制类型转换,即可得到整数部分,再用浮点数减整数部分,即可得到小数部分)。 2.对于整数部分,采用的是“除2法”(不知道是不是这个名字……)。即,每次将该数除 以2,得到的余数作为该位的二进制数,商作为下一次的除数,依此类推,直到商为1或0为止。 3.对于小数部分,采用的是“乘2法”(依然不知道是不是这个名字)。即,每次将小数部 分乘2,得到的整数部分即为该位的二进制数,小数部分为下一次的乘数。依此类推,这样做下去是一个无限不循环的小数,所以一般会要求二进制数中小数的精度,本题目要求的是11位。 4.在实际程序设计过程中,我发现了这样一个问题,当小数部分二进制码采用浮点型数据 时,单独输出准确无误,但与整形的整数部分二进制码结合在一起后,最后3位总是不准确的,怀疑是在相加的过程中产生了“大数吃小数”的问题。按照一般思维,此时应提高精度,采用long double型变量,但是我采用的编译器是采用Windows C的运行库(MS C编译器)的MinGW,其对printf函数不支持long double型。无奈之下,我只能把小数部分存为一个11位长的数组,再对其输出。 [流程]: [程序]:

/******************************************************************** /* this is a program to transform decimal nubers to binary nubers. /* Huang Bohao /* 将小数部分用数组形式存储,避免了整数部分与小数部分相加而出现的 /*大数吃小数的情况 ********************************************************************/ #include <> int Integer2Binary(int integer); ,Bina ryInt); for(i = 0; i < 11; i++) printf("%d",BinaryFraction[i]); printf("\n"); } /******************************************************************** /* function name: Integer2Binary /* input parameter: int integer (integer waiting to be transformed) /* output parameter: int output (transformed integer) ********************************************************************/ int Integer2Binary(int integer) { int B,Y,output,flag; //B被除数,Y为余数,output为输出数据,flag为位置标记位

摘要 在电子技术领域中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得更为重要。本文设计的测量频率计由硬件电路和软件设计两部分组成。硬件电路以AT89S52单片机最小系统为核心,实现整个电路的测试信号控制、数据运算等功能,选用74LS160作为分频电路,并通过LCD显示模块显示测量的数据。软件设计包括:单片机定时计数程序、LCD显示程序等。该数字频率计可以对输入信号幅度为5V的正弦波信号、方波信号、三角波信号进行测量,测量的频率范围为1Hz--10MHz。测量的相对误差为 1%。本系统具有结构紧凑、体积小、可靠性高、测频范围宽、使用方便等优点。 关键字:数字频率计;信号;单片机

Abstract In the electronics field, the frequency is one of the most basic parameters, and is very closely related to many electrical parameters measurement program, measurement results, so the measurement of frequency becomes even more important. The measurement of frequency designed in this text consist of two parts: the hardware and software design .the hardware circuitry take AT89S52 microcomputer as the core, to achieve the functions of controlling of the entire circuit of the test signals, data operations and choose 74LS160 as a frequency divider circuits, and through LCD display module shows measured data. Software design includes: MCU timer counting procedures, LCD display procedures and so on. The digital frequency meter can measure amplitude sine wave signal, square wave, triangle wave signals of which input signal is 5v, the frequency measured ranges from 1Hz to10MHz. The relative measurement error is 1%. This system has the advantage of compact structure , small size, high reliability, test frequency range, and easy use. Keyword:Figure frequency meter;Signal;Single-chip 目录

课程设计任务书 学生:专业班级:通信 指导教师:工作单位:信息工程学院 题目: 数字频率计的设计与实现 初始条件: 本设计既可以使用集成脉冲发生器、计数器、译码器、单稳态触发器、锁存器、放大器、整形电路和必要的门电路等,也可以使用单片机系统构建简易频率计。用数码管显示频率计数值。要求完成的主要任务: (包括课程设计工作量及技术要求,以及说明书撰写等具体要求) 1、课程设计工作量:1周。 2、技术要求: 1)设计一个频率计。要求用4位7段数码管显示待测频率,格式为0000Hz。 2)测量频率围:10~9999Hz。 3)测量信号类型:正弦波、方波和三角波。 4)测量信号幅值:0.5~5V。 5)设计的脉冲信号发生器,以此产生闸门信号,闸门信号宽度为1s。 6)确定设计方案,按功能模块的划分选择元、器件和中小规模集成电路,设计分电路,画出总体电路原理图,阐述基本原理。 3、查阅至少5篇参考文献。按《理工大学课程设计工作规》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规。 时间安排: 1、2013年5 月17日,布置课设具体实施计划与课程设计报告格式的要求说明。 2、2013 年 6 月18 日至2013 年6 月22 日,方案选择和电路设计。 3、2013 年6 月22 日至2013 年7 月1 日,电路调试和设计说明书撰写。 4、2013年7月5日,上交课程设计成果及报告,同时进行答辩。 指导教师签名:年月日 系主任(或责任教师)签名:年月日

目录 摘要 (3) 1电路的设计思路与原理 (4) 1.1电路设计方案的选择 (4) 1.1.1方案一:利用单片机制作频率计 (4) 1.1.2方案二:利用锁存器与计数器制作频率计 (5) 1.1.3方案三:利用定时电路与计数器制作频率计 (6) 1.1.4方案确定 (7) 1.2 原理及技术指标 (8) 1.3 单元电路设计及参数计算 (9) 1.3.1时基电路 (9) 1.3.2放大整形电路 (10) 1.3.3逻辑控制电路 (11) 1.3.4计数器 (13) 1.3.5锁存器 (15) 1.3.6译码电路 (16) 2仿真结果及分析 (16) 2.1仿真总图 (16) 2.2单个元电路仿真图 (17) 2.3测试结果 (20) 3测试的数据和理论计算的比较分析 (20) 4制作与调试中出现的故障、原因及排除方法 (20) 4.1故障a (20) 4.2故障b (21) 4.3故障c (21) 4.4故障d (21) 4.5故障e (22) 5 心得体会 (22)

一、填空 1. 数制变换: a) 将十进制数175转换成二进制数为_____ 、十六进制为_____ 、八进制为 __ 。 b) 二进制数(111010010)2对应的十六进制数是_____ 、八进制为—、十进制为 c) ( 16.52)8=( )2 =( )16= ( ) 10 d) ( 17)10=( ) 2 =( )16=( )8 2.编码: a) ( 1000)自然二进制码=( ) 余3码,(110100)2=( )BCD。 b) ( 15.5)10=( )8421BCH( )余3 BCD。 c) ( 38) 10用8421BCD码表示为 ____ 。 d) 二进制数(-100000)的原码为 _、补码为___。 e) [X]反=10111,则[X]补=—,[X]原= ___________ ,[X]真值= 。 g) [X]补=10110,则[X]反=—,[X]原= __ ,[X]真值= _ 。 3. 一种进位计数包含两个基本因素:______ 和____ 。 4. 常见的BCD编码中,有权码有____ 、___ ,无权码有___ 、___ 。 5. 如采用奇偶校验传送的数据部分为0111001,则所加奇校验位应为_____ ,偶校验位 应为_____ 。 6. 逻辑代数的基本运算有:___、___、___。 7. 当决定一事件的条件中,只要具备一个条件,事件就会发生,称这种关系为 逻辑关系,或称为关系。 8. ______________________________________________________ 真值表如下表,写出F1、F2、F3、F4的逻辑关系表达式______________________________ 9. _________________________________________ 逻辑函数F = A + AB以最小项形式表示为__________________________________________ ,可化简为______ 10.逻辑函数F =

实验一原理图输入方式设计数字逻辑电路 一、实验目的: 1、了解基本组合逻辑电路的原理及利用Quartus II 软件进行设计的一般方法。 2、熟悉Quartus II 原理图输入法的设计流程,掌握编辑、编译和仿真的方法。 3、掌握原理图的层次化设计方法。 4、了解Quartus II 软件的编程下载及引脚锁定的方法。 5、了解Quartus II宏功能模块的使用方法。 二、实验的硬件要求: 1、EDA/SOPC实验箱。 2、计算机。 三、实验原理 见附件《Quartus设计的一般步骤》、《元件例化和调用的操作步骤》、《QuartusII基于宏功能模块的设计》 四、实验内容: 1、用原理图方式设计1位二进制半加器半加器。 新建一个工程“HalfAdder”,选择芯片“Cyclone III EP3C16Q240C8”,建立原理图如图1-1,保存为“HalfAdder.BDF”。 图1-1 半加器电路图 编译工程。 建立波形文件,对半加器电路分别进行时序仿真和功能仿真,其波形如下: 图1-2半加器时序仿真波形,注意观察输出延时,以及毛刺的产生原因 图1-3半加器功能仿真波形 2、原理图层次化设计。 新建一工程,取名“FullAdder”;将上面设计的半加器“HalfAdder.BDF”复制到当前工程目录,并生成“符号元件”HalfAdder.BSF。 建立一个原理图文件,取名“FullAdder.BDF”,利用“符号元件”HalfAdder.BSF及其它元件设计全加器电路如下图:

用功能仿真测试全加器的逻辑功能。 图1-5 全加器功能仿真波形 图1-6是输入输出信号与FPGA连接示意图,图中用到了“拨档开关”作为输入,“LED 显示模块”显示输出值。表1-1是本实验连接的FPGA管脚编号。

简易数字频率计电路设计

摘要 请对内容进行简短的陈述,一般不超过300字 关键字:周期;频率;数码管,锁存器,计数器,中规模电路,定时器 在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得更为重要。 数字频率计是用数字显示被测信号频率的仪器,被测信号可以是正弦波、方波或其它周期性变化的信号。如配以适当的传感器,可以对多种物理量进行测试,比如机械振动的频率、转速、声音的频率以及产品的计件等等。因此,数字频率计是一种应用很广泛的仪器。 本章要求设计一个简易的数字频率计,测量给定信号的频率,并用十进制数字显示。数字频率计主要由放大整形电路、闸门电路、计数器电路、锁存器、数码管、时基电路、逻辑控制、译码显示电路几部分组成。

目录 前言 (1) 1.数字频率计的原理 (2) 2.系统框图 (3) 3.系统各功能单元电路设计 (3) 3.1 时基电路设计 (3) 3.2 放大整形电路 (4) 3.3 逻辑控制电路 (5) 3.4 锁存单元 (6) 3.5 分频电路 (7) 3.6 显示器 (7) 3.7 报警电路 (8) 4.系统总电路图 (10) 结束语 (11) 参考文献 (12)

前言 数字频率计是一种专门对被测信号频率进行测量的电子测量仪器。被测信号可以是正弦波、方波或其它周期性变化的信号。数字频率计主要由放大整形电路、闸门电路、计数器电路、锁存器、时基电路、逻辑控制、译码显示电路几部分组成。 在传统的电子测量仪器中,示波器在进行频率测量时测量精度较低,误差较大。频谱仪可以准确的测量频率并显示被测信号的频谱,但测量速度较慢,无法实时快速的跟踪捕捉到被测信号频率的变化。正是由于频率计能够快速准确的捕捉到被测信号频率的变化,因此,频率计拥有非常广泛的应用范围。 在传统的生产制造企业中,频率计被广泛的应用在产线的生产测试中。频率计能够快速的捕捉到晶体振荡器输出频率的变化,用户通过使用频率计能够迅速的发现有故障的晶振产品,确保产品质量。 频率计被用来对各种电子测量设备的本地振荡器进行校准。在无线通讯测试中,频率计既可以被用来对无线通讯基站的主时钟进行校准,还可以被用来对无线电台的跳频信号和频率调制信号进行分析。

目录 1. 引言 (1) 2.设计任务书 (1) 3. 数字频率计基本原理 (1) 3.1 设计思路 (1) 3.2 原理框图 (2) 4. 设计步骤及实现方法 (2) 4.1 信号拾取与整形 (2) 4.2 计数电路 (3) 4.3 锁存电路 (5) 4.4 译码显示电路 (6) 4.5 时钟电路及波形设计 (7) 5 总体电路图及工作原理 (10) 6 元器件的检测与电路调试缺点分析 (12) 7 心得体会 (12) 参考文献 (13)

1. 引言 数字频率计是一种基础测量仪器,在许多情况下,要对信号的频率进行测量,利用示波器可以粗略测量被测信号的频率,精确测量则要用到数字频率计。本设计项目可以进一步加深我们对数字电路应用技术方面的了解与认识,进一步熟悉数字电路系统设计与调试的方法和步骤。

2.设计任务书 1、设计题目:数字频率计 2、设计出一个数字频率计,其技术指标如下: ( 1 )频率测量范围: 10 ~ 9999Hz 。 ( 2 )输入电压幅度 >300mV 。 ( 3 )输入信号波形:任意周期信号。 ( 4 )显示方式:4位十进制数显示。 ( 5 )电源: 220V 、 50Hz 。 3、给定仪器设备及元器件 示波器、音频信号发生器、逻辑笔、万用表、数字集成电路测试仪、直流稳压电源。 4.电路原理要求简单,便于制作调试,元件成本低廉易购。

3. 数字频率计基本原理 3.1 设计思路 (1)利用光电开关管做电机转速的信号拾取元件,在电机的转轴上安装一圆盘,在圆盘上挖一小洞,小洞上下分别对应着光发射和光接受开关,圆盘转动一圈既光电管导通一次,利用此信号做为脉冲计数所需。 (2)计数脉冲通过计数电路进行有效的计数,按照设计要求每一秒种都必须对计数器清零一次,因为电路实行秒更新,所以计数器到译码电路之间有锁存电路,在计数器进行计数的过程中对上一次的数据进行锁存显示,这样做不仅解决了数码显示的逻辑混乱,而且避免了数码显示的闪烁问题。 (3)对于脉冲记数,有测周和测频的方式。测周电路的测量精度主要受电路系统的脉冲产生电路的影响,对于低频率信号,其精度较高。测频电路其对于正负一的信号差比较敏感,对于低频率信号的测量误差较大,但是本电路仍然采用测频方式,原因是本电路对于马达电机转速精度要求较低,本电路还有升级为频率计使用,而测频方式对高频的精度还是很高的。 时钟实现方法很多,本电路采用晶振电路,已求得高精度的时钟需求。3.2 原理框图 图3-1 系统框图

数字逻辑电路课程设计题目及要求 项目一:高精密数控电源的设计和制作: 要求:电源输出电压为:0—9.9V,步进为0.1V,有两位数码管显示,每位有两个按键能加能减的作用。功率大小不做具体的要求,电路设计不能有专业的A/D芯片。项目二:自行车的里程表设计和制作: 要求:设计一个自行车里程表电路,有两位数码管显示,显示数字的单位为百米,自行车轮胎直径为0.99M。 项目三:自行车的速度测定仪表的设计和制作: 要求:设计一个自行车测速电路,有两位数码管显示,显示数字的单位为M/S,采样时间不能超过5S,自行车轮胎直径为0.99M。 项目四:多功能抢答器的设计和制作: 要求:多功能抢答器为八路的,具有数码和指示灯双重指示,电路的附加的电路一个有计时、报警等电路,所用芯片必须为我们所学的。 项目五:数字频率计的设计和制作: 要求:数字频率计的显示为两位数码管,单位为KHZ,具有溢出报警功能,附带震荡电路,频率可调几K到几百KHZ。 项目六:交通灯的设计和制作: 要求:具有真正模拟十字路口的交通灯的能力,红灯5秒,绿灯4秒,黄灯1秒等的时间也可以自己设定。 项目七:数字电子钟逻辑电路的设计和制作: 要求:数字电子钟逻辑电路要具有电子手表的功能,例如时间的设定,整点报时,可以设定闹钟等功能,只需四位数码。 项目八:定时控制器电路的设计和制作: 要求:定时控制器电路能够定时控制家用电器的开关,例如能按时开启、关断电饭煲煮饭等,电器用灯泡代替,时间可以缩短60倍。 项目九:LED广告牌电路设计和制作: 要求:LED广告牌电路能够模拟市面上的LED广告灯箱,能有四个字显示能力(共青学院),可以的话周围有霓虹灯闪烁。 项目十:易拉罐技术电路的设计与制作: 要求:易拉罐在传送带上过时,记录数值,以20灌为一个单位,满二十灌重新 计数并给出提示音,此过程模拟工厂易拉罐装箱过程. 项目十一:数显风扇调速器电路 要求:具有中低高三档,0为停止,1为低档。2为中档,3为高档。调节开关设 置成触摸,遥控等。可以的话加入温度自动控制电路。 项目十二:出租车计价器电路

哈尔滨工业大学 简易频率计的仿真设计

目录 1设计要求 2?总电路图及工作原理 3?电路组成介绍 3.1脉冲形成电路 3.2闸门电路 3.3时基电路 3.4计数译码显示电路 4.电路的测试 5.分析与评价 附录:元器件清单

1 ?设计要求 本次设计任务是要求设计一个简易的数字频率计,即用数字显示被测信号频率的仪

器,数字频率计的设计指标有: 1. 测量信号:正弦信号、方波信号等周期变化的物理信号; 2. 测量频率范围:0Hz~9999Hz 3. 显示方式:4位十进制数显示。 2. 电路工作原理 频率计总电路图如下所示: 2単汙汕驚工 ---------- k

频率计的基本原理:通过将被测周期信号整形为同频率的方波信号后,利用555定时器组成的振荡电路所产生的频率为1Hz的标准方波,作为基准时钟,与被整形后的方波信号一起经过闸门电路处理输入计数电路,再利用74LS90N的十进制计数功能进行级联计数,计数后输入8位数据/地址锁存器74LS273N以实现锁存和清零功能,最后输入到译码显示电路中,用BCD7段译码器显示出来,这样就实现了对被测周期信号的频率测量并显示的功能。 频率计的工作原理流程图如下所示: 3. 电路组成介绍 3.1脉冲形成电路 脉冲形成电路由信号发生器与整形电路组成,输入信号先经过限幅器,再经过施密特 触发器整形,当输入信号幅度较小时,限幅器的二极管均截止,不起限副作用。由555组成的施密特触发器对经过限幅器的信号进行整形得到标准的方波信号。线路图如下所示:

L 1 1 r 1 r 闸门电路 3.2闸门电路 闸门电路的作用是控制计数器的输入脉冲,在电路中用一个与非门来实现(如下图所 标注)。当标准信号(正脉冲)来到时闸门开通,被侧信号的脉冲通过闸门进入计时器计 数;正脉冲结束时闸门关闭,计数器无时钟脉冲输入 72 R2 VA - IS. THZ R 71 C5 lOnF ZFG ■ 丄 D1 X1 N?07 75 D2 jtl NdOOT

《数字电路与数字逻辑》练习题一 一、填空 1.将下列二进制数转为十进制数 (1001011)B = ( )D (11.011)B = ( )D 2.将下列有符号的十进制数转换成相应的二进制数真值、原码、反码和补码 (+122)=( )真值 = ( )原码 =( )反码 = ( )补码 3.把下列4个不同数制的数D 、(110000)B 、(17A)H 、(67)O ( 按从大到小的 次 序 排 列 ( ) > ( )>( )>( ) 。将下列各式变换成最简与或式的形式 =+B AB ( ) =+AB A ( ) =++BC C A AB ( ) 4.将下列二进制数转为十进制数 (101000)B = ( )D (11.0101)B = ( )D 5.将下列十进制数转为二进制数,八进制数和十六进制数 (0.8125)= ( )B = ( )O = ( )H (254.25)= ( )B = ( )O = ( )H 6.将下列有符号的十进制数转换成相应的二进制数真值、原码、反码和补码 (+125)=( )真值 = ( )原码 =( )反码 = ( )补码 (—42)=( )真值 = ( )原码 =( )反码 = ( )补码 7.逻辑函数C A CD AB F ++=的对偶函数F '是__________________________;其反函数F 是_________________________。 8.当j i ≠时,同一逻辑函数的最小项=?j i m m _________;两个最大项

=+j i M M ___________。 9.()10=(_________)2=(_________)16。 10.n 个输入端的二进制译码器,共有_________个输出端,对于每一组输入代码,将有_________个输出端具有有效电平。 11.将下列二进制数转为十进制数 (1010001)B = ( )D (11.101)B = ( )D 12.将下列有符号的十进制数转换成相应的二进制数真值、原码、反码和补码 (+)=( )真值 = ( )原码 =( )反码 = ( )补码 13.把下列4个不同数制的数D 、(27A)H 、(10110)B 、(67)O 按从大到小的次序排列( )>( )>( )>( ) 。 14.对于D 触发器,欲使Qn+1=Qn ,输入D=( ),对于T 触发器,欲使Qn+1=Qn ,输入T=( ) 15.一个512*8位的ROM 芯片,地址线为( )条,数据线为( )条。 16.对32个地址进行译码,需要( )片74138译码器。 17.存储器起始地址为全0,256K*32的存储系统的最高地址为( )。 18.将下列各式变换成最简与或式的形式 ( ) ( ) ( ) 19.五级触发器的进位模数最大为( )进制。 20.十进制数()10转换成十六进制数是( ),转换成二进制数是( ),转换成八进制数是( ),转换成8421BCD 码为( )。 21.将二进制1100110转换成余3码为( ),转换成格雷码为( )。 22.设真值X= —0101,则X 的原码为( ),反码为( ),补码为( )。 23.卡诺图是( )的一种特殊形式。利用卡诺图法花剑逻辑函数比( )法更容易得到简化的逻辑函数表达式。 24.函数L=AC+BC 的对偶式为:( )。 25.一个1024*16位的ROM 芯片,地址线为( )位,数据线为( )位。 26.对于JK 触发器,若J=K ,可完成( )触发器的逻辑功能。 27.组合逻辑电路中部包含存储信号的( )元件,它一般是由各种( )组合而成的。 28.对64个地址进行译码,需要( )片74138译码器。 +AC 化成最小项的形式为( )。 30.将变换成或非的形式为( )。 31.数制转换 10=( )2 2=( )10 32.将下列有符号的十进制数转换成相应的二进制数真值﹑原码﹑反码和补码 (+11/32)=( )真值=( )原码 =( )反码=( )补码

(完整)数字频率计设计与制作 编辑整理: 尊敬的读者朋友们: 这里是精品文档编辑中心,本文档内容是由我和我的同事精心编辑整理后发布的,发布之前我们对文中内容进行仔细校对,但是难免会有疏漏的地方,但是任然希望((完整)数字频率计设计与制作)的内容能够给您的工作和学习带来便利。同时也真诚的希望收到您的建议和反馈,这将是我们进步的源泉,前进的动力。 本文可编辑可修改,如果觉得对您有帮助请收藏以便随时查阅,最后祝您生活愉快业绩进步,以下为(完整)数字频率计设计与制作的全部内容。

数字频率计设计与制作 王峰, 电子工程系 摘要:数字频率计是一种可以用十进制数字显示被测信号频率的测量仪器。被测信号可以是任何周期性变化的信号如正弦波、方波、三角波等等。如果加入放大电路,通过传感器则可以对许多微弱的、规律的物理量进行测量,例如声音、机械振动、转速的频率等等。使用频率计能让我们直观的看到信号的频率,其方便性、简单性、准确性使其具有较高的实用价值。因此数字频率计是一种应用很广泛的仪器,在计算机、通讯设备、自动化等科研生产领域起着重要作用。对于本次课题“数字频率计设计与制作”,我选用了555定时器产生时基信号,单稳态触发器74LS273来控制电路中的锁存,计数器74LS90来计数,74LS48进行译码并通过数码管显示。运用数字集成芯片给设计减少了很多不必要的麻烦。 关键词:数字频率计;锁存;译码;计数 Digital Frequency Meter Design and Fabrication Wangfeng, Electronic Information Engineering Abstract:Digital Frequency Meter is a measuring device, it can using decimal numeral reveal the signal frequency。 The measured signal was variety seasonal signal, such as sinusoidal wave, square wave, triangle wave and so on. If we using amplify circuit, we can also use sensing element measuring so many faint and regular signals, for example voice, inflexible vibrate and rotation rate. Digital Frequency Meter can make us intuitively sight the signal frequency,it’s conveniently, simply and accuracy, so it has enormously worthy in many fields, include computer, communication apparatus, automation equipment and so on。For about this subject study,the Digital Frequency Meter Design and Fabrication,I select 555_timer produce a normal time signal, using Monostable Trigger 74LS273 constitute flip-latch,using counter flip-flop 74LS90 count,using 74LS48 constitute a code translator and usig Mixie light reveal frequency。 Apply digital integrated circuit chip help me save so many time and reduce a number of inconvenience. Key words:Digital Frequency Meter; flip—flop; code translator; counter

数字逻辑电路课程设计 课题:电子密码锁设计 姓名: 班级:13通信 学号: 成绩: 指导教师: 开课时间:

目录 摘要 (1) 一课程设计目的内容及安排 (2) 1.1设计目的 (2) 1.2设计内容 (2) 1.3设计安排 (2) 1.4设计内容 (2) 二电子密码锁设计要求及总框图 (3) 2.1设计要求 (3) 2.2总框图 (4) 三各模块电路设计 (5) 3.1密码输入存储比较模块 (5) 3.2五秒计时电路 (6) 3.3二十秒计时电路 (8) 3.4报警电路 (10) 3.5总电路 (11) 四设计心得 (12) 五参考文献 (13)

电子密码锁 摘要:设计一个密码锁的控制电路,当输入正确代码时,输出开锁信号以推动执行机构工作,用红灯亮、绿灯熄灭表示关锁,用绿灯亮、红灯熄灭表示开锁;在锁的控制电路中储存一个可以修改的4位代码,当开锁按钮开关(可设置成6位至8位,其中实际有效为4位,其余为虚设)的输入代码等于储存代码时,开锁;从第一个按钮触动后的5秒内若未将锁打开,则电路自动复位并进入自锁状态,使之无法再打开,并由扬声器发出持续20秒的报警信号。密码输入存储及比较部分使用芯片74LS194及74LS85。五秒及时部分采用芯片74LS161和数码显示管。二十秒报警电路由74LS160,555定时器组成的多谐振荡器,LED灯和蜂鸣器组成。利用multisim对电路进行仿真可以得到结果。 关键词:电子密码锁,计时电路,报警电路

一课程设计目的内容及安排 1.1设计目的 1 根据设计要求,完成对交通信号灯的设计。 2 加强对Multisim10仿真软件的应用。 3 掌握交通信号灯的主要功能与在仿真软件中的实现方法。 4 掌握74LS160,74LS192等功能。 1.2 设计内容 设计一个密码锁的控制电路,当输入正确代码时,输出开锁信号以推动执行机构工作,用红灯亮、绿灯熄灭表示关锁,用绿灯亮、红灯熄灭表示开锁; 在锁的控制电路中储存一个可以修改的4位代码,当开锁按钮开关(可设置成6位至8位,其中实际有效为4位,其余为虚设)的输入代码等于储存代码时,开锁; 从第一个按钮触动后的5秒内若未将锁打开,则电路自动复位并进入自锁状态,使之无法再打开,并由扬声器发出持续20秒的报警信号。 1.3设计安排

第二章电路的总体设计方案 2.1方案论证与选择 2.1.1方案的提出 方案一 电路整体框架如图一所示。被测信号经过放大,整形电路将其转换成同频率的脉动信号,送入计数器进行计数,闸门的一个输入信号是秒脉冲发出的标准脉冲信号,秒脉冲信号源含有个高稳定的石英振荡器和一个多级分频器共同决定,其时间是相当精确的,计数器显示电路采用七段共阴极LED数码管。 图2-1 方案一框架图 方案二: 本方案采用单片机程序处理输入信号并且将结果直接送往LED显示,为了提高系统的稳定性,输入信号前进行放大整形,在通过A/D转换器输入单片机系统,采用这种方法可大大提高测试频率的精度和灵活性,并且能极大的减少外部干扰,采用VDHL编程设计实现的数字频率计,除被测信号的整形部分、键输入部分和数码显示部分以外,其余全部在一片FPGA芯片上实现,整个系统非常精简,而且具有灵活的现场可更改性。但采用这种方案相对设计复杂度将会大大提高并且采用单片机系统成本也会大大提高。

图2-2 方案二框架图 方案三: 采用频率计专用模块,即大规模集成电路将计数器、锁存器、译码、位和段驱动,量程及小数点选择等电路集成在一块芯片中,该方案在技术上是可行的,可以简化电路的设计,当对于设计要求中的某些指标,采用专用模块来完成比较困难,即扩展极为不便。 图2-3 方案三框架图 2.1.2方案的的比较 方案一:具有设计复杂度小、电路简洁、功能实用且成本低廉等特点,其稳

定性较好基本能满足设计要求。 方案二:采用单片机处理能较高要求,但成本提高且设计复杂,虽然可以达到很高的精度要求,但是,VHDL编程语言是我们在学习过程中没有接触过的,短期内也很难掌握并且熟练运用。 方案三:用专用频率计设计模块固然设计简单且稳定但系统可扩展性能较差。 2.1.3方案的选择 综合三种方案比较:我感觉方案一和我以前学的专业知识更接加近些,电路原理容易理解,所设计的数字频率计稳定性好,基本上能够满足设计要求,所以我采用第一种设计方案。 图2—5 数字频率计组成框图 在我的毕业设计中,数字频率计由信号输入电路、分频电路、放大整形电路、闸门电路、时基电路、逻辑控制电路、计数电路、锁存电路、译码显示电路,小

简易数字频率计的设计与制作 作者:赵玉龙 【摘要】:本设计是基于单片机内部的两个定时器/计数器与外围硬件相结合,并通过一定的软件控制达到测量频率的目的的简易数字频率计,可以直接精确测量1KHZ到65.535KHZ的频率范围。本设计的优点在于直接利用单片机进行频率的测量,更加的方便,实用。 【关键词】:单片机频率测量

前言 单片机即单片微控制器单元,由微处理器,存储器,I/O接口,定时器/计数器等电路集成在一块芯片上构成,现在应用于工业控制,家用民用电器以及智能化仪器仪表,计算机网络,外设,通信技术中,具有体积小、重量轻、性价比高、功耗低等特点, 同时具有较高的抗干扰性与可靠性可供设计开发人员灵活的运用各种逻辑操作,实现实时控制和进行必要的运算.目前单片机更朝着大容量、高性能与小容量、低廉化、外围电路内装化以及I/O接口的增强和能耗降低等方向发展.本设计的意义在于如何利用较少的硬件达到直接测量较高精度频率的目的,更加的方便,快捷,相对于传统的数字频率计实用性更高。

第一章 系统硬件电路的设计 1.1方案的选择: 方案一.采用组合电路和时序电路等大量的硬件电路来构成,利用555多谐振荡产生闸门时间,两个D 触发器来进行门控信号的选择,数码管,以及其他硬件电路组成。 方案二.利用一块AT89C51单片机芯片直接来驱动数码管。 比较方案一与方案二在实现功能一样的情况下,我们可以发现纯粹利用硬件电路来实现不仅产品体积较大,运行速度慢,而且增加了许多的硬件成本,而利用单片机体积小、功能强、性能价格比较高等特点,在实际使用时节约了很多的硬件成本,符合设计的要求,故而本设计选择方案二来实现频率的测量. 1.2系统功能分析 本系统是基于单片机的简易数字频率计,在硬件的基础上通过软件的控制 达到频率测量的目的,整个系统工作由软件程序控制运行。整个系统主要可以分为两个部分,频率测量单元和频率显示单元。频率测量单元主要完成对被测信号的测量,而显示单元主要完成用数码形式将测量结果显示出来。 1.3.系统的方框图: 被测信号通过单片机的内部处理,完成对被测信号的测量,经过转换以数字形式显示出来。 图一 系统方框图 具体情况如下: 将单片机定时/计数器0设置成定时器方式,由它对单片机机器周期信号计数定时,形成时间间隔T,去控制单片机定时/计数器1的启动和停止, 单片机定时计数器1设置成计数器方式,由它对被测信号计数. 这里需要说明能够的是单片机内的两个定时/计数器在同一时刻不能既作为计数器使用又作为定时器使用,如设置成定时器模式就不能作为计数器使用;如设置成计数器模式就不能作为定时器使用. 1.4.各功能部件单元电路设计