实验六帧同步

一、实验目的

1.掌握巴克码识别原理。

2.掌握同步保护原理。

3.掌握假同步保护、漏同步、捕捉态、维持态概念。

二、实验内容

1.观察帧同步码无错误时帧同步器的维持态。

2.观察帧同步码有一位错误时帧同步器的维持态和捕捉态。

3.观察同步器的假同步现象和同步保护作用。

三、基本原理

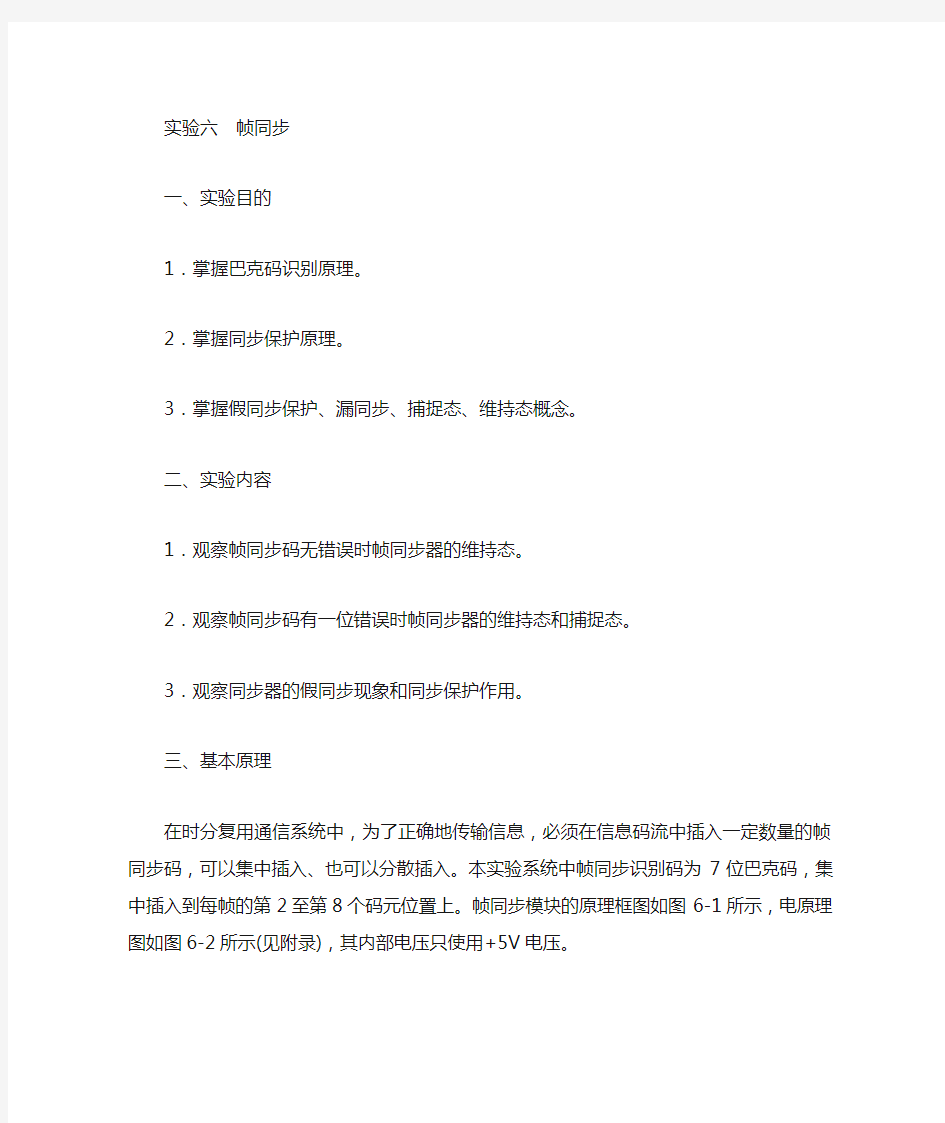

在时分复用通信系统中,为了正确地传输信息,必须在信息码流中插入一定数量的帧同步码,可以集中插入、也可以分散插入。本实验系统中帧同步识别码为7位巴克码,集中插入到每帧的第2至第8个码元位置上。帧同步模块的原理框图如图6-1所示,电原理图如图6-2所示(见附录),其内部电压只使用+5V电压。

图6-1 帧同步模块原理框图

从总体上看,本模块可分为巴克码识别器及同步保护两部分。巴克码识别器包括移位寄存器、相加器和判决器,图6-1中的其余各部分完成同步保护功

能。

移位寄存器由两片74175组成,移位时钟信号是位同步信号。当7位巴克码全部进入移位寄存器时,U50的1Q 、2Q 、3Q 、4Q 及U51的Q 2、Q 3、Q 4都为1,它们输入到相加器U52的数据输入端D 0~D 6,U52的输出端Y 0、Y 1、Y 2都为l ,表示输入端为7个1。若210Y YY =100时,表示输入端有4个1,依此类推,210

Y Y Y 的不同状态表示了U52输入端为1的个数。判决器U53有6个输入端。IN 2、IN 1、IN 0分别与U52的Y 2、Y 1、Y 0相连,L 2、L 1、L 0与判决门限控制电压相连,L 2、L 1已设置为l ,而L 0由同步保护部分控制,可能为1也可能为0。在帧同步模块电路中有三个发光二极管指示灯P1、P2、P3与判决门限控制电压相对应,即从左到右与L 2、L 1、L 0一一对应,灯亮对应1,灯熄对应0。判决电平测试点TH 就是L 0信号,它与最右边的指示灯P3状态相对应。当210L L L =111时门限为7,三个灯全亮,TH 为高电平;当210L L L =110时门限为6,P1和P2亮,而P3熄,TH 为低电平。当U52输入端为1的个数(即U53的IN 2IN 1IN 0)大于或等于判决门限于

210L L L ,识别器就会输出一个脉冲信号。

当基带信号里的帧同步码无错误时(七位全对),把位同步信号和数字基带信号输入给移位寄存器,识别器就会有帧同步识别信号GAL 输出,各种信号波形及时序关系如图6-3所示,GAL 信号的上升沿与最后一位帧同步码的结束时刻对齐。图中还给出了÷24信号及帧同步器最终输出的帧同步信号FS-OUT ,FS-OUT 的上升沿稍迟后于GAL 的上升沿。

图6-3 帧同步器信号波形

÷24信号是将位同步信号进行24分频得到的,其周期与帧同步信号的周期相同(因为一帧24位是确定的),但其相位不定符合要求。当识别器输出一个GAL 脉冲信号时(即捕获到一组正确的帧同步码),在GAL 信号和同步保护器的作用下,÷24电路置零,从而使输出的÷24信号下降沿与GAL 信号的上升沿对齐。÷24信号再送给后级的单稳电路,单稳设置为下降沿触发,其输出信号的上升沿比÷24信号的下降沿稍有延迟。

同步器最终输出的帧同步信号FS 是由同步保护器中的与门3对单稳输出的信号及状态触发器的Q 端输出信号进行“与”运算得到的。

电路中同步保护器的作用是减小假同步和漏同步。

当无基带信号输入(或虽有基带信号输入但相加器输出低于门限值)时,识

别器没有输出(即输出为0),与门1关闭、与门2打开,单稳输出信号通过与门2后输入到÷3电路,÷3电路的输出信号使状态触发器置“0”,从而关闭与门3,同步器无输出信号,此时Q的高电平把判决器的门限置为7(P3灯亮)、且关闭或门、打开与门1,同步器处于捕捉态。只要识别器输出一个GAL信号(因为判决门限比较高,这个GAL信号是正确的帧同步信号的概率根高),与门4就可以输出一个置零脉冲使÷24分频器置零,÷24分频器输出与GAL信号同频同相的周期信号(见图6-3)。识别器输出的GAL脉冲信号通过与门1后使状态触发器置“1”,从而打开与门3,输出帧同步信号FS-OUT,同时使判决器门限降为6(P3灯熄)、打开或门、同步器进入维持状态。在维持状态下,因为判决门限较低,故识别器的漏识别概率减小,假识别概率增加。但假识别信号与单稳输出信号不同步,故与门1、与门4不输出假识别信号,从而使假识别信号不影响÷24电路的工作状态,与门3输出的仍是正确的帧同步信号。实验中可根据判决门限指示灯P3判断同步器处于何种状态,P3亮为捕捉态,P3熄为同步态。

在维持状态下,识别器也可能出现漏识别。但由于漏识别概率比较小,连续几帧出现漏识别的概率更小。只要识别器不连续出现三次漏识别,则÷3电路不输出脉冲信号,维持状态保持不变。若识别器连续出现三次漏识别,则÷3电路输出个脉冲信号,使维持状态变为捕捉状态,重新捕捉帧同步码。

不难看出,若识别器第一次输出的脉冲信号(即首次捕捉到的是信息数据中与帧同步码完全相同的码元序列),则系统将进入错误的同步维持状态,由于本实验系统是连续传输以一帧为周期的周期信号,所以此状态将维持下去,但在实际的信息传输中不会连续传送这种周期信号,因此连续几帧都输出假识别信号的概率极小,所以这种错误的同步维持状态存在的时间是短暂的。

当然,同步保护器中的÷3电路的分频比也可以设置为其它值,此值越大,在维持状态下允许的识别器的漏识别概率也越大。

在维持态下对同步信号的保护措施称为前方保护,在捕捉态下的同步保护措施称为后方保护。本同步器中捕捉态下的高门限属于后方保护措施之一,它可以减少假同步概率,当然还可以采取其它电路措施进行后方保护。低门限及÷3电路属于前方保护,它可以保护已建立起来的帧同步信号,避免识别器偶尔出现的漏识别造成帧同步器丢失帧同步信号即减少漏同步概率。同步器中的其它保护电路用来减少维持态下的假同步概率。

四、实验步骤

本实验使用数字信源单元及帧同步单元。

1、熟悉帧同步单元的工作原理,将信源单元的NRZ-OUT、BS-OUT用信号连线分别与帧同步单元的S-IN、BS-IN对应相连,接通实验箱电源。

2、观察同步器的维持态(同步态)

将数字信源单元的K1(左边的8位微动开关)置于×111 0010状态(1lOO1O 为帧同步码,×是无定义位,可任意置“1”或置“0”),K2置为1000 0000状态、K3则置为全0状态,示波器CH1接信源单元的NRZ-OUT,CH2分别接帧同步单元的GAL、÷24、TH及FS,观察并纪录上述信号波形以及与NRZ-OUT的相位关系(注意:TH为O电平,帧同步模块的P3指示灯熄,P1、P2亮,表示识别门限为6)。

GAL:

÷24:

TH:

使信源的帧同步码(注意是K1的第2位到第8位)中错一位,重新观察上述信号,此时GAL、÷24、TH、FS应不变。

使信源帧同步码再错一位重作上述观察。(此时同步器应转入捕捉态,仅÷24波形不变,请根据原理框图分析思考此过程)。

GAL:

÷24:

FS:

3、观察同步器的捕捉态(失步态)

上步中电路己经由同步态变为捕捉态,示波器仍观察÷24信号,此时断开电源,再接通电源,可看到÷24波形的下降沿已不再对准第一个数据位(相位随机),观察其他信号可见TH为高电平,FS无输出。将信源K1从刚才错两位状态还原为仅错一位状态,观察÷24信号相位是否变化。

再将信源K1还原为正确的帧同步码(×1110010),观察÷24信号相位是否变化。分析÷24信号相位变化原因,从而理解同步器从失步态转为同步态的过程。

4、观察识别器假识别现象及同步保护器的保护作用。

上步中同步器转为同步状态后,使信源单元的K2或K3中出现1110010状态(与1110010状态有一位不同的状态也可),示波器CH1接NRZ-OUT,CH2分别接GAL和FS,观察识别器假识别现象,理解同步保护电路的保护作用。

GAL:

FS:

五、实验报告要求

1.根据实验结果,画出同步器处于同步状态及失步状态时同步器各点波形。

2.本实验中同步器由同步态转为捕捉态时÷24信号相位为什么不变?

答:因为判决器无输入,与门4无输出,故24分频电路无复位脉冲,其输出的24分频信号相位保持不变。

3.同步保护电路是如何使假识别信号不形成假同步信号的?

答:假识别信号与或门输出信号不同步,与门1输出中无假识别信号。因而,假识别信号不能通过与门,所以单稳输出信号仅与负同步码对应的识别信号有关,而与假识别无关,这样假识别信号就不能形成假同步信号。

4.试设计一个后方保护电路,使识别器连续两帧有信号输出且这两个识别脉冲的时间间隔为一帧时,同步器由失步态转为同步态。

中南大学 《通信原理》实验报告 学生姓名 指导教师 学院 专业班级 完成时间

数字基带信号 1、实验名称 数字基带信号 2、实验目的 (1)了解单极性码、双极性码、归零码、不归零码等基带信号波形特点。 (2)掌握AMI、HDB 3 码的编码规则。 (3)掌握从HDB 3 码信号中提取位同步信号的方法。 (4)掌握集中插入帧同步码时分复用信号的帧结构特点。 (5)了解HDB 3 (AMI)编译码集成电路CD22103。 3、实验内容 (1)用示波器观察单极性非归零码(NRZ)、传号交替反转码(AMI)、三阶高密度双极性码 (HDB 3)、整流后的AMI码及整流后的HDB 3 码。 (2)用示波器观察从HDB 3 码中和从AMI码中提取位同步信号的电路中有关波形。 (3)用示波器观察HDB 3 、AMI译码输出波形。 4、基本原理(简写) 本实验使用数字信源模块和HDB 3 编译码模块。 1、数字信源 本模块是整个实验系统的发终端,模块内部只使用+5V电压,其原理方框图如图1-1所示,电原理图如图1-3所示(见附录)。本单元产生NRZ信号,信号码速率约为170.5KB,帧结构如图1-2所示。帧长为24位,其中首位无定义,第2位到第8位是帧同步码(7位巴克码1110010),另外16位为2路数据信号,每路8位。此NRZ信号为集中插入帧同步码时分复用信号,实验电路中数据码用红色发光二极管指示,帧同步码及无定义位用绿色发光二极管指示。发光二极管亮状态表示1码,熄状态表示0码。 本模块有以下测试点及输入输出点: ? CLK 晶振信号测试点 ? BS-OUT 信源位同步信号输出点/测试点(2个) ? FS 信源帧同步信号输出点/测试点 ? NRZ-OUT(AK) NRZ信号(绝对码)输出点/测试点(4个) 图1-1中各单元与电路板上元器件对应关系如下: ?晶振CRY:晶体;U1:反相器7404 ?分频器U2:计数器74161;U3:计数器74193;U4:计数器40160 ?并行码产生器K1、K2、K3:8位手动开关,从左到右依次与帧同步码、数

数据库实验 集团文件版本号:(M928-T898-M248-WU2669-I2896-DQ586-M1988)

数据库原理实验指导 实验前准备: 请设计一个企业销售管理据库,其中需要保存的信息如下: 员工信息,包括:员工编号、员工姓名、性别、所属部门、职称、到职日、生日、薪水、填表日期; 客户信息,包括:客户号,客户名称,客户住址,客户电话、邮政编码; 产品信息,包括:产品编号,产品名称; 员工和客户可以签订订单,每签订一个订单,就要保存订单信息,包括:订单编号、客户号、业务员编号、订单金额、订货日期、出货日期、发票号码。 此外,每个订单可能涉及到多种产品,每种产品可能被多个订单订购。因此需要每个订单中每类产品的销售明细,包括每种产品的销售数量、单价、订单日期; 要求: (1)给出系统的ER图(可以用word或其它画图工具,如Visio画),要求画出所有的实体,联系,属性以及联系的类型; (2)将ER图转换为关系模型; 实验一 实验名称:数据定义(2课时) 一、实验目的

1、理解数据库模式的概念,通过使用SQL SERVER企业管理器或者My Sql建立数据库和基本表。模式为人事表、客户表、销售表、销售明细表、产品表。熟悉SQL SERVER企业管理器的使用,并将得到的表生成脚本,然后保存。 2、理解上述基本表之间的关系,建立关系表。 3、掌握修改表结构的基本方法 4、掌握索引和视图的创建方法 二、实验环境 MS SQL SERVER或者My Sql。 三、实验内容与步骤 1、建立一个数据库和五张表的表结构。 (1)/*员工人事表employee */ Create datebase sale; create table employee( emp_no char(5) Not null primary key, emp_name char(10) Not null, sex char(1) Not null,

目录 系统简介 (2) 实验部分 实验一数字信源及其光纤传输实验 (5) 实验二 HDB3编译码及其光纤传输实验 (11) 实验三 CMI编译码及其光纤传输实验 (20) 实验四光发送模块实验 (28) 实验五光接收模块实验 (35) 实验六数字信号电—光、光—电转换传输实验 (39) 1)方波信号和NRZ码传输; 2)CMI码传输; 3)HDB3码传输; 实验七波分复用(WDM)光纤通信系统实验 (43) EL-GT-IV光纤通信教学实验系统简介 光纤通信教学实验系统是为了配合《光纤通信系统》的理论教学而设计的实验装置,在这套系统上除了完成理论验证实验外,还可实现各种开发性实验,并可配合CPLD进行各模块的二次性开发。此外本实验箱,可扩展实验模块,实现通信原理的实验。 一、结构简介 光纤通信教学实验系统结构框图如下: 1310光纤收发模块1550光纤收发模块

主要由以下功能模块组成: 1.数字信号源单元: 此单元产生码速率为170.5K的单极性不归零码(NRZ),数字信号帧长为24位,其中包括两路数字信息,每路8位,另外8位中的7位为集中插入帧同步码。通过拨码开关,可以很方便地改变要传送的码信息并由发光二极管显示出来。 2.AMI(HDB3)编译码单元: 此单元将数字信号源单元产生的NRZ码进行编码,通过专用芯片转换成HDB3码或AMI码通过切换开关切换,然后将编码后的信号又经过译码单元还原成NRZ码。 3.电话接口单元 此单元有两路独立的电话输入接口、输出接口,通过专用电话接口芯片实现语音的全双工通信。自带馈电电源。 4.PCM&CMI编译码单元; 此单元采用CPLD来实现PCM&CMI编译码电路,可同时完成两路信号的编译码工作。PCM模块可以实现传输两路语音信号,采用TP3057编译器。 5.可调信号源单元: 此单元包括两路频率800HZ—2KHZ可调的方波、正弦波、三角波。 6.串行RS232接口单元: 此单元配有RS232接口及信号端口TX和RX,可实现自发自收通信实验,两台计算机间的全双工光纤通信实验。 7.1310波长光发送单元: PHLC-1310nmFP同轴激光二极管。 8.1550波长光发送单元: PHLC-1310nmFP同轴激光二极管。 9.1310波长光接受单元: 10.1550波长光接受单元: 主要完成光电信号的转换,小信号的检测与信号的恢复放大等功能。它主要有光检测模块、滤波放大模块组成。光检测模块采用PHPC-IS01-PFC,是PHOTRON公司的高性能光检测器件,输出可从DC到1GHZ。 11.数字时分复用光纤传输实验

实验十九滤波法及数字锁相环法位同步提取实验 实验项目三数字锁相环法位同步观测 (1)观测“数字锁相环输入”和“输入跳变指示”,观测当“数字锁相环输入”没有跳变和有跳变时“输入跳变指示”的波形。 从图中可以观察出,若前一位数据有跳变,则判断有效,“输入跳变指示”输出表示1;否则,输出0表示判断无效。 (2)观测“数字锁相环输入”和“鉴相输出”。观测相位超前滞后的情况 数字锁相环的超前—滞后鉴相器需要排除位流数据输入连续几位码值保持不变的不利影响。在有效的相位比较结果中仅给出相位超前或相位滞后两种相位误差极性,而相位误差的绝对大小固定不变。经观察比较,“鉴相输出”比“数字锁相环输入”超前两个码元。

(3)观测“插入指示”和“扣除指示”。 (4)以信号源模块“CLK ”为触发,观测13号模块的“BS2”。 思考题:分析波形有何特点,为什么会出现这种情况。 因为可变分频器的输出信号频率与实验所需频率接近,将其和从信号中提取的相位参考信号同时送入相位比较器,比较的结果若是载波频率高了,就通过补抹门抹掉一个输入分频器的脉冲,相当于本地振荡频率降低;相反,若示出本地频率低了时就在分频器输入端的两个输入脉冲间插入 一个脉冲,相当于本地振荡频率上升,从而了达到同步的目的。 思考题:BS2恢复的时钟是否有抖动的情况,为什么?试分析BS2抖动的区间有多大?如何减小这个抖动的区间? 有抖动的存在,是因为可变分频器的存在使得下一个时钟沿的到来时间不确定,从而引入了相位抖动。而这种引入的误差是无法消除的。减小相位抖动的方法就是将分频器的分频数提高。

实验二十 模拟锁相环实验 实验项目一 VCO 自由振荡观测 (1)示波器CH1接TH8,CH2接TH4输出,对比观测输入及输出波形。 实验项目二 同步带测量 (1) 示波器CH1接13号模块TH8模拟锁相环输入,CH2接TH4输出BS1,观察TH4 输出处于锁定状态。将正弦波频率调小直到输出波形失锁,此时的频率大小f1为 400Hz ;将频率调大,直到TH4输出处于失锁状态,记下此时频率f2为 9.25kHz 。 对比波形可以发现TH8与TH4信号输入与输出错位半个周期 如右图所示,方波抖动,说明处于失锁状态。 记下两次波形失锁的频率,可计 算 出 同 步 带 f=9.25KHz-400Hz=8.85KHz 。

课程设计报告 课题名称帧同步提取 学院 专业 班级 学号 姓名 指导教师 定稿日期: 2014 年 06月13 日

目录 摘要 (1) 一、前言 (2) 1.1 CDMA帧同步背景 (2) 二、帧同步提取基本原理 (3) 2.1 CDMA含义 (3) 2.2基本原理 (3) 2.2.1发端用户数据成帧 (3) 2.2.2 收端帧同步提取 (3) 三、帧同步提取设计 (6) 3.1课程设计分析 (6) 3.2帧同步提取测试设计步骤 (7) 3.2.1实验箱设置 (7) 3.2.2“发端数据成帧”测量步骤 (7) 3.3单片机程序流程图如下 (9) 四、帧同步提取测试结果 (10) 4.1课程设计实物链接图 (10) 4.2“发端数据成帧”实验过程 (10) 4.3实测收端帧同步误码: (11) 五、课设总结 (12) 参考文献 (13) 附录(源程序) (14)

摘要 在当今这个信息高速发展的时代,移动通信已经成为生活中不可或缺的一部分。在移动环境下点对点的传输问题已经得到解决,那么对于给定资源应该采用什么多址技术使得有限的资源能传输更大容量的信息?移动通信系统的发展经历了第一代模拟移动通信系统、第二代数字移动通信系统和第三代移动通信系统(IMT-2000)。第一代移动通信系统包括AMPS、TACS和NMT等体制。第二代数字移动通信系统包括GSM、IS-136(DAMPS)、PDC、IS-95等体制。一个典型的数字蜂窝移动通信系统包括:移动台(MS)、基站分系统(BSS)、移动交换中心(MSC)、原籍(归属)位置寄存器(HLR)、访问位置寄存器(VLR)、设备标识寄存器(EIR)、认证中心(AUC)和操作维护中心(OMC)。而这其中,多址技术便主要解决众多用户如何高效共享给定频谱资源的问题。常规的多址方式有三种:频分多址(FDMA)、时分多址(TDMA)和码分多址(CDMA)。数字通信时,一般总是以一定数目的码元组成一个个的“字”或“句”,即组成一个个的“群”进行传输,因此群同步信号的频率很容易由位同步信号经分频而得出,但是每群的开头和末尾时刻却无法由分频器的输出决定。群同步的任务就是要给出这个“开头”和“末尾”的时刻。群同步有时也称为帧同步。本次课程设计主要研究帧同步的提取及实现方法。 关键词:CDMA 帧同步移动通信

实验一SQL Server使用初步 一、实验目的 1、熟悉SQL Server2000的组成及基本功能。 2、掌握SQL Server2000的登录及注册。 3、掌握SQL Server2000企业管理器的使用方法。 4、熟悉查询分析器的基本使用。 二、实验预习 1、什么是数据库管理系统DBMS?你所知道的DBMS有哪些? 答:DBMS是位于用户和操作系统之间的一层数据管理软件。常见的DBMS主要有:Oracle、db2、SQL Server、MySQL、PostgreSQL、SQLite、Firebird等等。 2、SQL Server 2000(2005)的安装步骤? 答:以企业版安装为例,步骤为: 将企业版安装光盘插入光驱后,出现以下提示框。请选择“安装 SQL Server 2000 组件” 出现下面对话框后,选择 "安装数据库服务器" 。 选择 "下一步",然后选择 "本地计算机" 进行安装。 在 "安装选择" 窗口,选择 "创建新的SQL Server实例..."。对于初次安装的用户,应选用这一安装模式,不需要使用 "高级选项" 进行安装。 "高级选项" 中的内容均可在安装完成后进行调整。 在 "用户信息" 窗口,输入用户信息,并接受软件许可证协议。 在“安装定义”窗口,选择“服务器和客户端工具”选项进行安装。 在“实例名”窗口,选择“默认”的实例名称。 在“安装类型”窗口,选择“典型”安装选项,并指定“目的文件夹”。 在 "服务账号" 窗口,请选择 "对每个服务使用统一账户..." 的选项。 在 "身份验证模式" 窗口,选择 "混合模式..." 选项,并设置管理员"sa"账号的密码。 最后按“下一步”即可完成安装。 检测安装:如果安装成功,应该能成功启动SQL Server,并且能和SQL Server 客户端连接上。 可以通过服务管理器来进行启动。

帧同步识别、保护、提取实验 一、实验目的 1.掌握巴克码识别电路原理; 2.掌握同步保护电路原理; 3.掌握假同步、漏同步、捕捉态、维持态等概念; 4.通过设计性实验,培养学生用EPROM器件写入软件和利用应用手册,完成 该模块中识别、比较器的软、硬件的设计能力。 二、实验内容: 1、观察帧同步码元无误码时帧同步电路的维持态; 2、观察帧同步有一位错码时,帧同步的维持态和捕捉态; 3、观察同步电路的假同步现象和同步保护作用; 4、修改本模块中EPROM的参数即改变比较器的设置,完成相同的电路功能。(选做) 三、基本原理 (一)帧同步模块的原理框图及电原理图分别如图7-1和图7-2所示。 图7-1 帧同步模块原理框图 图7-1中各功能部分在图7-2中所对应元器件关系如下: 1.分频器:U3(74LS161)、U4(4075)、U2(74LS74)、U5(74H04) 2.串/并变换器:U9(74LS164) 3.识别器:U7(2764) 4.判决器:U10(74LS85) 5.人工与门限选择器:U13(74LS157)

6.自动门限:U14(74LS157) 7.人工门限:S1 8.人工门限显示:U16(74247)、U12(LCD) (二)电路基本原理 1.帧同步信号的识别与判决 串/并变换器U9将串行码变成并行码,并完成移位功能,当七位巴克码全部进入U9时,U9的输出端Q6Q5Q4Q3Q2Q1Q0=1110010,并送入U7(2764)帧头识别器。 识别器U7为EPROM器件,在U7中将串/并变换的输出信号与1110010码进行相关运算,使U7的数据输出端的D3D2D1D0有对应的相关输出。如当U7的A6A5A4A3A2A1A0=1110010时,则对应的 D3D2D1D0=0111时(十进制数为7),若A6A5A4A3A2A1A0=1110011(与巴克码错一位)时,则对应的D3D2D1D0=0110(十进制数为6) 比较判决器Ul0(74LS85)有两组输入数据,一组来自帧头识别器,另一组来白人工与白动门限选择器U13。U10的曲组输入数据A3A2A1A0与B3B2B1B0进行比较。只当A3A2A1A0大于或等于B3B2B1B0时U10的输出为“1”,其余输出为:“0”。因此,U10端不仅与来自识别器的数据有关。还与判决门限数据B3B3B1B0有关,还与判决门限数据B3B2B1B0有关。 2.帧同步信号的捕捉与同步保护 本模块是在捕捉态时,Ul0的B3B2B1B0=0111(十进制数为7);另一种是在同步态时,U10的B3B2B1B0=O110(十进制数为6)。在捕捉态时,只有当巴克码到来时(1110010),U10的A3A2A1A0=01111(十进制为7),满足A3A2A1A0A 大于或等于B3B2B1B0的条件,才有判决脉冲输出。 人工门限可以从略0000--0111(0--7)任意置定,可据实验需要,自行选择其门限值。同步保护电路输出的帧同步信号(图7-1)受状态触发器Q端输出的信号所控制。÷32分频信号的周期与比较器输出一个帧同步信号的周期相同,但相位一定相同。但只要比较器输出一个帧同步信号,对÷3 2分频器置零,使÷32分频信号T2的上升沿与判决输出信号Tl的下降沿同相。清零信号由判决器输出信号及÷3 2分频信号共同决定。当无基带信号输入(或虽有基带信号输入但识别器的输出低于门限值)时,判决器输出为0,与门l关闭,与门4打丌。÷32信号经与门4,输入到÷5计数电路。÷5计数电路的输出信号使状态触发器置“0”,从而关闭与门2无帧同步信号输出。此时Q的高电平把判决器门限置为7(门限开关为“自动”),且关闭或门,打开与门1,同步电路进入捕捉态。这时,只要比较器输出一个脉冲信号(认定为帧同步头),与门3就输出一个置“0”脉冲,使÷32电路置“0”,从而输出与帧同步信号同频同相的周期信号。判决器输出的脉冲信号通过与门1后,使状态触发器置“l”,从而打开与门2,输出输出帧同步信号。同时,Q=0,使判决门限降为6,打开或门。同步电路处于维持态。在维持态下,因判决门限低,故与门1,与门3禁止输出假同步信号使,假同步信号小改变÷32的工作状态,与门2的输出仍为正确的同步态。 在维持状态下,识别比较器也可能出现漏同步。但由于漏同步概率比较小,只要识别比较器小连续出现五次漏同步,则÷5电路就小输出信号,使维持状态小变。若识别器连续出现五交漏同步,则÷5电路输出要一个脉冲信号使维持态为捕捉态,重新捕捉帧同步码。(同步指示灯亮,表示同步态;同步指示灯灭表示捕捉态)

滤波法及数字锁相环法位同步提取实验和帧同步提取实验

滤波法及数字锁相环法位同步提取实验和帧同步提取实验 一、实验目的 1、掌握滤波法提取位同步信号的原理及其对信息码的要求; 2、掌握用数字锁相环提取位同步信号的原理及其对信息代码的要求; 3、掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念; 4、掌握巴克码识别原理; 5、掌握同步保护原理; 6、掌握假同步、漏同步、捕捉态、维持态的概念。 二、实验内容 1、熟悉实验箱 2、滤波法位同步带通滤波器幅频特性测量; 3、滤波法位同步恢复观测; 4、数字锁相环位同步观测; 5、帧同步提取实验。 三、实验条件/器材 滤波法及数字锁相环法位同步提取实验: 1、主控&信号源、8号(基带传输编译码)、13号(载波同步及位同步)模块 2、双踪示波器(模拟/数字) 3、连接线若干 帧同步提取实验: 1、主控&信号源、7号模块 2、双踪示波器(模拟/数字) 3、连接线若干 四、实验原理 滤波法及数字锁相环法位同步提取实验原理见通信原理综合实验指导书P129-P134; 帧同步提取实验原理见通信原理综合实验指导书P141。 五、实验过程及结果分析 (一)熟悉实验箱 (二)滤波法位同步带通滤波器幅频特性测量 1、连线及相关设置 (1)关电,连线。 (2)开电,设置主控,选择【信号源】→【输出波形】。设置输出波形为正弦波,调节相应旋钮,使其输出频率为200Khz,峰峰值3V。 (3)此时系统初始状态为:输入信号为频率200KHz、幅度为3V的正弦波。 2、实验操作及波形观测 分别观测13号模块的“滤波法位同步输入”和“BPF-Out”,改变信号源的频率,测量“BPF-Out” 的幅度填入下表,并绘制幅频特性曲线。

通信原理实验指导书思考题答案 实验一思考题P1-4: 1、位同步信号和帧同步信号在整个通信原理系统中起什么作用? 答:位同步和帧同步是数字通信技术中的核心问题,在整个通信系统中,发送端按照确定的时间顺序,逐个传输数码脉冲序列中的每个码元,在接收端必须有准确的抽样判决时刻(位同步信号)才能正确判决所发送的码元。位同步的目的是确定数字通信中的各个码元的抽样时刻,即把每个码元加以区分,使接收端得到一连串的码元序列,这一连串的码元序列代表一定的信息。通常由若干个码元代表一个字母(符号、数字),而由若干个字母组成一个字,若干个字组成一个句。帧同步的任务是把字、句和码组区分出来。尤其在时分多路传输系统中,信号是以帧的方式传送的。克服距离上的障碍,迅速而准确地传递信息,是通信的任务,因此,位同步信号和帧同步信号的稳定性直接影响到整个通信系统的工作性能。 2、自行设计一个码元可变的NRZ码产生电路并分析其工作过程。 答:设计流程图如下。 提示:若设计一个32位的NRZ码,即要求对位同步信号进行32分频,产生一路NRZ码的帧同步信号,码型调节模块对32位码进行设置,可得到可变的任何32位码型,通过帧同步倍锁存设置的NRZ码,通过NRZ码产生器模块把32位并行数据进行并串转换,用位同步信号进行一位一位输出,循环输出32位可变NRZ码即我们的设计完毕。 实验二思考题P2-4: 1、实验时,串/并转换所需的帧同步信号高电平持续时间必须小于一位码元的宽度,为什么? 答:如果学生认真思考,可以提出没有必要一定小于一位码元的宽度。如24位的数据在串行移位时,当同步信号计数到第24位时,输出帧信号,通过帧信号的上升沿马上锁存这一帧24位数据,高电平没有必要作要求。主要检查学生是否认真考虑问题。 2、是否还有更好的方法实现串/并转换?请设计电路,并画出电路原理图及各点理论上的波形图。 答:终端模块采用移位锁存的方法实现串/并转换,此方法目前是最好的方法了。 实验四思考题P4-6: 1、在分析电路的基础上回答,为什么本实验HDB3编、解码电路只能在输入信号是码长为24位的周期性NRZ码时才能 正常工作? 答:因为该电路采用帧同步控制信号,而1帧包含24位,所以当NRZ码输入电路到第24位时,帧同步信号给一个脉冲,使得电路复位。HDB3码再重新对NRZ码进行编译。且HDB3码电路对NRZ进行编译的第一位始终是固定的值。 因此HDB3编译码电路只能在输入信号是码长为24位的周期性NRZ码才能正常工作。但是由于HDB3码很有特点,现在为了使学生更好的观察HDB3如何进行编译码,我们对电路进行了改正,去掉了帧同步控制信号,所以现在对任意位的NRZ码都可以进行编码。 2、自行设计一个HDB3码编码电路,画出电路原理图并分析其工作过程。 答:根据HDB3的编码规则,CPLD电路实现四连“0”的检测电路,并根据检测出来的结果确定破坏点“V”脉冲的加入,再根据取代节选择将“B”脉冲填补进去。原理框图如下: 3

帧同步提取系统实验 一.实验目的 1、了解帧同步的机理 2、熟悉帧同步的性能 3、熟悉帧失步对数据业务的影响 二.实验内容 1、帧同步过程观察; 2、误码环境下的帧同步性能测试; 3、帧失步下对接受帧内的数据信号传输的定性观测。 三.实验仪器 1、JH5001通信原理综合实验系统一台 2、20MHz双踪示波器一台四.原理与电路 在TDM复接系统中,要保证接收端分路系统和发送端一致,必须要有一个同步系统,以实现发送端和接收端同步。帧定位同步系统是复接/解复接设备中最重要的部分。在帧定位系统中要解决的设计问题有:1)同步搜索方法;2)帧定位码型设计;3)帧长度的确定;4)帧定位码的码长选择;5)帧定位保护方法;6)帧定位保护参数的选择;等等。这些设计完成后就确定了复接系统的下列技术性能:1)平均同步搜捕时间;2)平均发现帧时间;3)平均确认同步时间;4)平均发生失帧的时间间隔;5)平均同步持续时间;6)失帧引入的平均误码率,等等。 通常帧定位同步方法有两种:逐码移位同步搜索法和置位同步搜索法。通信原理综合实验系统中的解复接同步搜索方法采用逐码移位同步法。逐码移位同步搜索法的基本工作原理是调整收端本地帧定位码的相位,使之与收到的总码流中的帧定位码对准。同步后用收端各

分路定时脉冲就可以对接收到的码流进行正确的分路。如果本地帧同步码的相位没有对准码流接收信号码流的帧定位码位,则检测电路将输出一个一定宽度的扣脉冲,将接收时钟扣除一个,这等效将数据码流后移一位码元时间,使帧定位检测电路检测下一位信码。如果下一位检测结果仍不一致,则再扣除一位时钟,这过程称“同步搜索”。搜索直至检测到帧定位码为止。因接收码流除有帧定位码型外,随机的数字码流也可能存在与帧定位码完全相同的码型。因此,只有在同一位置,多次连续出现帧定位码型,方可算达到并进入同步。这一部分功能由帧定位检测电路内的校核电路完成。 无论多么可靠的同步电路,由于各种因素(例如强干扰、短促线路故障等),总会破坏同步工作状态,使帧失步。从帧失步到重新获得同步的这段时间(亦称同步时间)将使通信中断。误码也将会造成帧失步。因此,从同步到下一次失步的时间因尽量长一些,否则将不断的中断通信。这一时间的长短表示TDM同步系统的抗干扰能力。抗误码造成的帧失步主要由帧定位检测电路内的保护记数电路完成,只有当在一定的时间内在帧定位码位置多次检测不到帧定位码,才可判定为帧失步,需重新进入同步搜索状态。逐码移位同步搜索法系统组成框图见图1所示。 语音信号的中断时间短于100ms,将不易被人耳分辨出来。但对某些数据终端传输却是不允许的。为能让学生能深入了解在有误码的环境下帧失步、同步和抗误码性能,在复接模块内专门设计了一个错码产生器(3种类型误码),通过错码设置跳线开关SWB02(E_SEL0,E_SEL1)选择不同的信道误码率(分别约为4×10—3、1.6×10—2和1×10—1)。学生能够观测到复接/解复接具有抗误码性能,即在小误码时帧同步锁定状态,加大误码帧帧失步,进入帧同步搜索(扫描)状态;另可测试不同误码和帧失步对话音业务的影响和观测对数据业务的影响。 五.实验步骤 准备工作:首先将解复接模块内的输入信号和时钟选择跳线开关KB01、KB02设置LOOP(自环)位置,使复接模块和解复接模块连接成自环测试方式;将复接模块内的工作状态选择跳线开关SBW02的m序列选择跳线开关M_SEL1、M_SEL2拔下,使m序列发生器产生全0码,将错码选择跳线开关E_SEL0、E_SEL1拔下,不在传输帧中插入误码。

实验项目三 数字锁相环法位同步观测 (1)观测“数字锁相环输入”和“输入跳变指示”,观测当“数字锁相环输入”没有跳变和有跳变时“输入跳变指示”的波形。 (2)观测“数字锁相环输入”和“鉴相输出”。观测相位超前滞后的情况。 (4)以信号源模块“CLK ”为触发,观测13号模块的“ BS2”。 实验二十 实验项目一 VCO 自由振荡观测 (1)示波器CH1接TH8,CH2接TH4 实验项目二 同步带测量

(1)示波器CH1接13号模块TH8模拟锁相环输入,CH2接TH4输出BS1,观察TH4输出处于锁定状态。将正弦波频率调小直到输出波形失锁,此时的频率大小f1为 400Hz ;将频率调大,直到TH4输出处于失锁状态,记下此时频率f2为。 实验二十一载波同步实验 实验项目载波同步 (1)本实验利用科斯塔斯环法提取BPSK调制信号的同步载波,对比观测信号源“256K”和13号模块的“SIN”,调节13号模块的压控偏置调节电位器,观测载波同步情况。

实验二十二帧同步实验 实验项目帧同步提取实验 (1)观测在没有误码的情况下“失步”,“捕获”,“同步”三个灯的变化情况经过多次实验反复观察,“失步”指示灯一直没有亮过,其余两个灯的顺序为捕捉指示灯先亮,之后熄灭,同步指示灯变亮。 (2)关闭7号模块电源。按住“误码插入”不放,打开7号模块电源。再观测“失步”,“捕获”,“同步”三个灯的变化情况。 经过多次实验反复观察,“失步”指示灯一直没有亮过,其余两个灯的顺序为捕捉指示灯先亮,之后熄灭,同步指示灯变亮。 (3)观察同步保护现象:如下图所示。 (4) 现误码时三个LED (5)观察假同步现象: 观察结果知, 分析原因:此时出现假同步状态,即时分复用单元将拨码开关S1的码值做为帧 头码,其他码元和原来的巴克码被当做了数据码元,从而在检查到01110010时 就开始按照8位为一个用户的数据,接着进行下面的数据采集。

实验报告 学院:计信学院专业:网络工程班级:091 姓名学号实验组实验时间2012-6-1 指导教师成绩实验项目名称实验六:数据库系统设计实 验目的 要求掌握数据库设计的基本技术,熟悉数据库设计的每个步骤中的任务和实施方法,并加深对数据库系统概念和特点的理解。 实 验 要 求 本实验属于设计型实验,通过实验,加强对课堂讲授知识的理解。 实验原理 必须按照数据库设计的四个阶段进行:需求分析(分析用户要求)、概念设计(信息分析和定义)、逻辑设计(设计实现)和物理设计(物理数据库设计)。概念模型设计时采用自底向上的方法,即自顶向下的进行需求分析,然后再自底向上地设计概念结构,和自底向上的设计方法;概念模型必须用E-R图进行表示。在逻辑设计阶段,将E-R图转换成关系模式,然后进行关系模式的规范化。在物理设计阶段,将关系模式转化成SQL Server中的具体的数据库表,并建立表间的关系,表的索引,及相关的约束。 实 验仪器(1)硬件条件:个人计算机。 (2)软件条件:Windows 2000NT Server; MS SQL Server 2000。 实验步骤1、完成系统需求分析报告 在系统需求分析报告中包括采用的设计方法、数据流图和数据字典。 2、完成数据库信息要求和关系数据模型设计 使用E-R图表示对数据库中要存储的信息及语义进行详细描述,对数据约束和数据之间的关联进行

详细描述。详细描述系统需要的基本表及属性、视图和索引,对基本表的主码、候选码、外码及被参照表进行说明,对基本表中数据的约束条件进行说明。 3、完成数据库的操作和应用要求报告 在数据库的操作和应用要求报告中,详细描述数据库的数据操作要求、处理方法和处理流程,画出系统功能模块图。 4、在机器上完成整个数据库的设计。 实 验内容 要求根据周围的实际情况,自选一个自己熟悉的小型数据库应用项目,并深入到应用项目的现实世界中,进行系统分析和数据库设计。例如选择学籍管理系统、图书管理系统、材料管理系统或仓库管理系统等。 实验数据我设计的是车站售票管理系统,主要用于车站日常的票务处理。 一、需求分析 车站售票管理系统 员工 管理 模块 汽车 管理 模块 线路 管理 模块 车票 管理 模块 票务 信息 管理 模块 员 工 信 息 添 加 员 工 信 息 删 除 员 工 信 息 修 改 汽 车 信 息 添 加 汽 车 信 息 修 改 汽 车 信 息 删 除 线 路 信 息 添 加 线 路 信 息 修 改 线 路 信 息 删 除 添 加 车 票 删 除 车 票 查 询 车 票 信 息 购 买 / 预 订 车 票员 工 信 息 查 询 汽 车 信 息 查 询 线 路 信 息 查 询 车 票 信 息 查 询 功能模块图 1.员工管理模块: 员工有两种身份,售票员和系统管理员。系统管理员可以进行系统用户的添加,密码的修改操作,汽车,线路,车票信息的更新等,售票员可以查询以上信息和购买车票等。 2.线路信息管理模块:

姓名:学号:班级: 第周星期第大节实验名称:自定义帧结构的帧形成及其传输/自定义帧结构的帧同步系统 一、实验目的 1.加深对PCM30/32系统帧结构的理解。 2.加深对PCM30/32路帧同步系统及其工作过程的理解。 3.加深对PCM30/32系统话路、信令、帧同步的告警复用和分用过程的理解。 二、实验仪器 1.ZH5001A通信原理综合实验系统 2.20MHz双踪示波器 三、实验内容 (一)自定义帧结构的帧形成及其传输 1.发送传输帧结构观测 (1)(2) m序列输入的序列为全0 所找的帧在图上标注了。 (3)调整开关信号。 箭头所指为改变的开关信号。

(4)调整m序列 什么都不接是全0可以看清,接时,可以看清。接M_SEL1和两2.发送帧同步指示的观测 可以观测到已经同步 3.解复接开关信号输出的观测 4.解复接m序列数据输出观测 接M_SEL0 & M_SEL1 接M_SEL0 接M_SEL1 全不接 只要接M_SEL0接收就看不清,全1(M_SEL0)和全0(都不接)都可以

(二)自定义帧结构的帧同步系统 1.帧同步过程观测 (1)输入全0码 可以同步 可以同步 (3)将开关信号设置为帧定位信号,将KB01拔出插入 左边是假同步,右边是真同步。说明开关序列边位帧同步序列以后会影响

2.在误码环境下的帧同步性能测试和数据传输的定性测试(1)通过设置,使信道的误码率为1*10^-1 无法同步,同时观察LED灯,发现LED灯闪烁无规律。 (2)通过设置,使信道的误码率为1.6*10^-2 仍旧不能同步。 (3)通过设置,使信道的误码率为4*10^-3 在误码率较小的情况下,可以同步。

实验八 帧同步信号恢复实验 一、实验目的 1. 掌握巴克码识别原理。 2. 掌握同步保护原理。 3. 掌握假同步、漏同步、捕捉态、维持态概念。 二、实验内容 1. 观察帧同步码无错误时帧同步器的维持态。 2. 观察帧同步码有一位错误时帧同步器的维持态和捕捉态。 3. 观察同步器的假同步现象和同步保护作用。 三、基本原理 (A )原理说明 一、帧同步码插入方式及码型 1.集中插入(连贯插入) 在一帧开始的n 位集中插入n 比特帧同步码,PDH 中的A 律PCM 基群、二次群、三次、四次群,μ律PCM 二次群、三次群、四次群以及SDH 中各个等级的同步传输模块都采用集中插入式。 2.分散插入式(间隔插入式) n 比特帧同步码分散地插入到n 帧内,每帧插入1比持,μ律PCM 基群及△M 系统采用分散插入式。 分散插入式无国际标准,集中插入式有国际标准。 帧同步码出现的周期为帧周期的整数信,即在每N 帧(N≥1)的相同位置插入帧同步码。 3.帧同步码码型选择原则 (1)假同步概率小 (2)有尖锐的自相关特性,以减小漏同步概率 如A 律PCM 基群的帧同步码为001101,设“1”对应正电平1,“0”码对应负电平-1,则此帧同步码的自相关特性如下图所示 0 1 2 3 4 5 6 -6 -5 -4 -3 -2 -1 -1 -1 -1 -1 -5 -5 -5 -5 3 3 3 3 j 7 R(j)

二、帧同步码识别 介绍常用的集中插入帧同步码的识别方法。设帧同码为0011011,当帧同步 码全部进入移位寄存器时它的7个 输出端全为高电平,相加器3个输出端全为高电平,表示u i =1+2+4=7。 门限L 由3个输入电平决定,它们 的权值分别为1,2,4。 比较器的功能为? ??<≥=L u L u u i i o ,0,1据此可得以下波形: 三、识别器性能 设误码率为P e ,n 帧码位,L=n-m ,(即允许帧同步码错m 位),求漏识别概率P 1和假识别概率P 2以及同步识别时间t s 。 1.漏识别概率 正确识别概率为∑=--m n e e n P P C 0 )1(γγγ γ,故 ∑=--- =m n e e p P n P 0 1)1((1γ γ γγ,m=0时e nP P ≈1 门限L 越低,P e 越小,则漏识别概率越小。 2.假识别概率 n 位信码产生一个假识别信号的概率为n m n n P m C P -=-===∑202 20 2时γ γ 门限越高,帧码位数越多,则假识别概率越小。 3.同步识别时间t s P 1=P 2=0时,t s =NT s ,N 为一个同步帧中码元位数,T s 为码元宽度 一个同步帧中产生一个假识别信号概率为22)(NP P n N ≈-,故当P 1≠0、P 2≠0时 s s NT NP P t )1(21++= 分散插入帧同步码的同步识别时间为 s s T N t 2= L u 0 移位寄存器 PCM 码流 u 0

通信原理 实 验 报 告

实验一 数字基带信号实验(AMI/HDB3) 一、 实验目的 1、了解单极性码、双极性码、归零码、不归零码等基带信号波形特点 2、掌握AMI 、HDB 3的编码规则 3、掌握从HDB 3码信号中提取位同步信号的方法 4、掌握集中插入帧同步码时分复用信号的帧结构特点 5、了解HDB 3(AMI )编译码集成电路CD22103 二、 实验内容 1、用示波器观察单极性非归零码(NRZ )、传号交替反转码(AMI )、三阶高密度 双极性码(HDB 3)、整流后的AMI 码及整流后的HDB 3码 2、用示波器观察从HDB 3/AMI 码中提取位同步信号的波形 3、用示波器观察HDB 3、AMI 译码输出波形 三、 基本原理 本实验使用数字信源模块(EL-TS-M6)、AMI/HDB 3编译码模块(EL-TS-M6)。 BS S5S4S3S2S1 BS-OUT NRZ-OUT CLK 并 行 码 产 生 器 八选一 八选一八选一分 频 器 三选一 NRZ 抽 样 晶振 FS 倒相器 图1-1 数字信源方框图 010×0111××××××××× ×××××××数据2 数据1 帧同步码 无定义位 图1-2 帧结构 四、实验步骤 1、 熟悉信源模块和HDB3/AMI 编译码模块的工作原理。 2、 插上模块(EL-TS-M6),打开电源。用示波器观察数字信源模块上的各种信号波形。 用FS 作为示波器的外同步信号,进行下列观察: (1) 示波器的两个通道探头分别接NRZ-OUT 和BS-OUT ,对照发光二极管的发光状态,判断数字信源单元是否已正常工作(1码对应的发光管亮,0码对应的发光管熄);

云南大学软件学院 实验报告 课程:数据库原理与实用技术实验任课教师:刘宇、张璇 姓名:学号:专业:信息安全成绩: 实验6 数据库完整性 实验6-1 完整性约束 1、创建规则(用图形或者语句方法创建) (1)创建入学日期规则“Enter_University_date_rule”,假定该学校于1923年4月30日创建。要求:入学日期必须大于等于学校创建日期,并且小于等于当前日期 测试: (2)创建学生年龄规则“Age_rule”。要求:学生年龄必须在15~30岁之间

测试: (3)创建学生性别规则“Sex_rule”。要求:性别只能为“男”或“女” 测试:

(4)创建学生成绩规则“Score_rule”。要求:学生成绩只能在0~100之间 (5)用图形方法查看学生成绩规则“Score_rule”,截图为: 双击:成绩: (6)用语句方法查看学生成绩规则“Score_rule”,语句为:

2、删除规则Enter_University_date_rule 3、创建默认(用图形或者语句方法创建) (1)创建默认时间“Time_default”为当前系统时间 (2)创建默认入学年龄“Age_default”为18岁 (3)用图形方法查看默认入学年龄“Age_default”,截图为:

(4)用语句方法查看默认入学年龄“Age_default”,语句为: 4、删除默认入学年龄“Age_default” 5、创建声明式默认:在创建表的过程中创建声明式默认 (1)创建表“default_example”,表中包含字段pid、name、sex、age。要求设定sex的默认值为“男”、age的默认值为18。 编号姓名性别年龄 101 苏晴女 201 马拯山20 执行结果为: 输入数据:

实验十八位同步提取实验 一、实验目的 1、掌握用滤波法提取位同步信号的原理及其对信息代码的要求。 2、掌握用数字锁相环提取位同步信号的原理及其对信息代码的要求。 3、掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念。 二、实验内容 1、观察滤波法提取位同步信号各观测点波形。 2、观察数字锁相环的失锁状态和锁定状态。 3、观察数字锁相环锁定状态下位同步信号的相位抖动现象及相位抖动大小与固有频差的 关系。 4、观察数字锁相环位同步器的同步保持时间与固有频差之间的关系。 三、实验器材 1、信号源模块一块 2、⑥号模块一块 3、⑦号模块一块 4、20M双踪示波器一台 5、频率计(选用)一台 四、实验原理 位同步锁相法的基本原理和载波同步的类似。在接收端利用鉴频器比较接收码元和本地产生的位同步信号的相位,若两者相位不一致(超前或滞后),鉴相器就产生误差信号去调整位同步信号的相位,直至获得准确的位同步信号为止。前面讨论的滤波法原理图中,窄带滤波器可以是简单的单调谐回路或晶体滤波器,可以是锁相环路。 我们把采用锁相环来提取位同步信号的方法称为锁相法。下面介绍在数字通信中常采用的数字锁相环法提取位同步信号的原理。 数字锁相环(DPLL)是一种相位反馈控制系统。它根据输入信号与本地估算时钟之间的相位误差对本地估算时钟的相位进行连续不断的反馈调节,从而达到使本地估算时钟相位跟踪输入信号相位的目的。DPLL 通常有三个组成模块:数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)。根据各个模块组态的不同, DPLL 可以被划分出许多不同的类型。根据设计

的要求,本实验系统采用超前滞后型数字锁相环(LL-DPLL)作为解决方案,图18-3是其实现结构。在LL- DPLL中,DLF 用双向计数逻辑和比较逻辑实现,DCO 采用加扣脉冲式数控振荡器。这样设计出来的DPLL具有结构简洁明快,参数调节方便,工作稳定可靠的优点。 六、实验步骤 1、锁相环法位同步提取 (1)将信号源模块上S5拨为“1010”,拨动拨码开关S1、S2、S3,使“NRZ”输出的24位NRZ码设置为01110010 10101010 10101010。模块7上的S2拨为“0110”, 即提取时钟选512K。 (2)在电源关闭的状态下,依照下表完成连线: 源端口目的端口连线说明 信号源:NRZ(32K)模块7:DIN 32KNRZ码输入同步提取 * 检查连线是否正确,检查无误后打开电源 (3)以信号源模块“CLK2”的信号为内触发源,用示波器双踪观察模块7上“BS”波形,并与原始时钟CLK2相比较。 (4)把信号源模块上的S1拨为00000000,S2、S3不变,用示波器双踪同时观察“NRZ” 和模块7上“ABSVAL”两点的波形。(结果可以看到,“NRZ”连零时“ABSVAL”为 0,“NRZ”有跳变时“ABSVAL”为1)

(精编)哈工大通信原理 实验报告

H a r b i n I n s t i t u t e o f T e c h n o l o g y 通信原理 实验报告 课程名称:通信原理 院系:电子与信息工程学院 班级: 姓名: 学号: 指导教师:倪洁 实验时间:2015年12月 哈尔滨工业大学 实验二帧同步信号提取实验 一、实验目的 1.了解帧同步的提取过程。 2.了解同步保护原理。 3.掌握假同步,漏同步,捕捉动态和维持态的概念。

二、实验原理 时分复用通信系统,为了正确的传输信息,必须在信息码流中插入一定数量的帧同步码,帧同步码应具有良好的识别特性。本实验系统帧长为24比特,划分三个时隙,每个时隙长度8比特,在每帧的第一时隙的第2至第8码元插入七位巴克码作为同步吗。第9至24比特传输两路数据脉冲。帧结构为:X11100101010101011001100,首位为无定义位。 本实验模块由信号源,巴克码识别器和帧同步保护电路三部分构成,信号源提供时钟脉冲和数字基带脉冲,巴克码识别器包裹移位寄存器、相加器和判决器。其余部分完成同步保护功能。 三、实验内容 1.观察帧同步码无错误时帧同步器的维持状态。 2.观察帧同步码有一位错误时帧同步器的维持态和捕捉态 3.观察帧同步器假同步现象和同步保护器。 四、实验步骤 1.开关K301接 2.3脚。K302接1.2脚。 2.接通电源,按下按键K1,K2,K300,使电路工作。 3.观察同步器的同步状态 将信号源中的SW001,SW002,SW003设置为11110010,10101010,11001100(其中第2-8位为帧同步码),SW301设置为1110,示波器1通道接TP303,2通道接TP302,TP304,TP305,TP306,观察上述信号波形,使帧同步码(SW001的2-8位)措一位,重新做上述观察,此时除了TP303外,个点波形不变,说明同步状态仍在维持。 4.观察同步器的失步状态。 关闭电源,断开K302,在开电源(三个发光二极管全亮)。使帧同步码措一位后再将