推荐-组合逻辑电路的VHDL设计 精品

- 格式:doc

- 大小:126.50 KB

- 文档页数:5

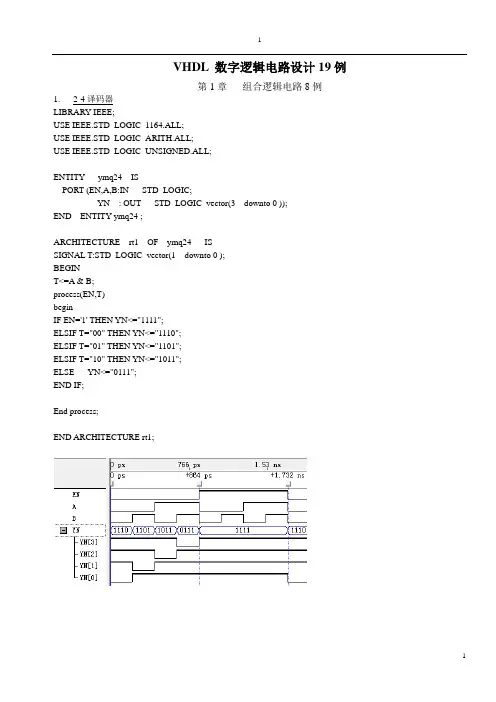

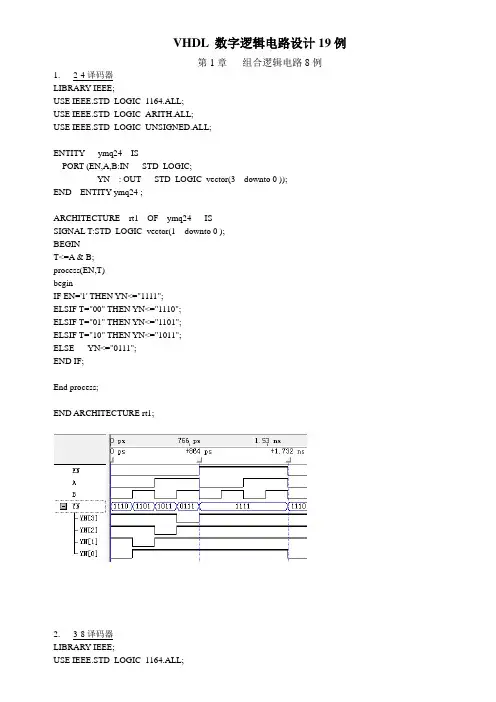

VHDL 数字逻辑电路设计19例第1章组合逻辑电路8例1. 2-4译码器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ymq24 ISPORT (EN,A,B:IN STD_LOGIC;YN : OUT STD_LOGIC_vector(3 downto 0 ));END ENTITY ymq24 ;ARCHITECTURE rt1 OF ymq24 ISSIGNAL T:STD_LOGIC_vector(1 downto 0 );BEGINT<=A & B;process(EN,T)beginIF EN='1' THEN YN<="1111";ELSIF T="00" THEN YN<="1110";ELSIF T="01" THEN YN<="1101";ELSIF T="10" THEN YN<="1011";ELSE YN<="0111";END IF;End process;END ARCHITECTURE rt1;2. 3-8译码器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ymq38 ISPORT (G1,G2N,G3N,A,B,C:IN STD_LOGIC;YN : OUT STD_LOGIC_vector(7 downto 0 )); END ENTITY ymq38 ;ARCHITECTURE rt1 OF ymq38 ISSIGNAL T1,T2:STD_LOGIC_vector(2 downto 0 );BEGINT1<=A & B & C;T2<=G1 & G2N & G3N;process(G1,G2N,G3N,T1,T2)beginIF T2/="100" THEN YN<="11111111";ELSIF T1="000" THEN YN<="11111110";ELSIF T1="001" THEN YN<="11111101";ELSIF T1="010" THEN YN<="11111011";ELSIF T1="011" THEN YN<="11110111";ELSIF T1="100" THEN YN<="11101111";ELSIF T1="101" THEN YN<="11011111";ELSIF T1="110" THEN YN<="10111111";ELSE YN<="01111111";END IF;End process;END ARCHITECTURE rt1;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY xzq41 ISPORT(gn: IN STD_LOGIC;d: IN STD_LOGIC_VECTOR(3 DOWNTO 0);a0,a1: IN STD_LOGIC;y: out STD_LOGIC);END ENTITY xzq41;ARCHITECTURE rt1 OF xzq41 ISsignal s: STD_LOGIC_VECTOR(1 DOWNTO 0); BEGINS<= a1 & a0;Process(S,D,gn)beginif gn='0' thenCASE (S) ISWHEN "00"=> Y<=d(0);WHEN "01"=> Y<=d(1);WHEN "10"=> Y<=d(2);WHEN "11"=> Y<=d(3);WHEN OTHERS =>NULL;END CASE;else y<='0';end if;End process;END ARCHITECTURE rt1;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY xzq81 ISPORT(gn: IN STD_LOGIC;d: IN STD_LOGIC_VECTOR(7 DOWNTO 0);a0,a1,a2: IN STD_LOGIC;y: out STD_LOGIC);END ENTITY xzq81;ARCHITECTURE rt1 OF xzq81 ISsignal s: STD_LOGIC_VECTOR(2 DOWNTO 0); BEGINS<= a2 & a1 & a0;Process(S,D,gn)beginif gn='0' thenCASE (S) ISWHEN "000"=> Y<=d(0);WHEN "001"=> Y<=d(1);WHEN "010"=> Y<=d(2);WHEN "011"=> Y<=d(3);WHEN "100"=> Y<=d(4);WHEN "101"=> Y<=d(5);WHEN "110"=> Y<=d(6);WHEN "111"=> Y<=d(7);WHEN OTHERS =>NULL;END CASE;else y<='0';end if;End process;END ARCHITECTURE rt1;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY l75 ISPORT (A,B,C:IN STD_LOGIC;d,g : OUT STD_LOGIC);END ENTITY l75 ;ARCHITECTURE rt1 OF l75 ISCOMPONENT ymq38PORT (G1, G2N, G3N, A, B, C: IN STD_LOGIC;YN : OUT STD_LOGIC_vector(7 downto 0 )); END COMPONENT ;signal ynt : STD_LOGIC_vector(7 downto 0 );BEGINU1 :ymq38 PORT MAP ('1','0','0',a,b,c,YNt(7 DOWNTO 0));d<=not(ynt(1) and ynt(2) and ynt(4) and ynt(7));g<=not(ynt(1) and ynt(2) and ynt(3) and ynt(7));END ARCHITECTURE rt1;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY l76 ISPORT (A,B,C,D:IN STD_LOGIC;F : OUT STD_LOGIC);END ENTITY l76 ;ARCHITECTURE rt1 OF l76 ISCOMPONENT ymq38PORT (G1,G2N,G3N,A,B,C:IN STD_LOGIC;YN : OUT STD_LOGIC_vector(7 downto 0 ));END COMPONENT ;signal yn1t:STD_LOGIC_vector(7 downto 0 );signal yn2t:STD_LOGIC_vector(7 downto 0 );BEGINU1 :ymq38 PORT MAP ('1',A,'0',B,C,D,YN1t(7 DOWNTO 0));U2 :ymq38 PORT MAP (A,'0','0',B,C,D,YN2t(7 DOWNTO 0));F<=not( yn1t(2) and yn1t(4) and yn1t(6) and yn2t(0) and yn2t(2) and yn2t(4) and yn2t(6)); END ARCHITECTURE rt1;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY l78 ISPORT (A,B,C:IN STD_LOGIC;f : OUT STD_LOGIC);END ENTITY l78 ;ARCHITECTURE rt1 OF l78 ISCOMPONENT xzq81PORT(gn: IN STD_LOGIC;d: IN STD_LOGIC_VECTOR(7 DOWNTO 0);a0,a1,a2: IN STD_LOGIC;y: out STD_LOGIC);END COMPONENT ;BEGINU1 :xzq81 PORT MAP ('0',"01101100",c,b,a,f);END ARCHITECTURE rt1;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY l78 ISPORT (A,B,C:IN STD_LOGIC;f : OUT STD_LOGIC);END ENTITY l78 ;ARCHITECTURE rt1 OF l78 ISCOMPONENT xzq41PORT(gn: IN STD_LOGIC;d: IN STD_LOGIC_VECTOR(3 DOWNTO 0);a0,a1: IN STD_LOGIC;y: out STD_LOGIC);END COMPONENT ;signal t:STD_LOGIC;signal dt:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINt<= not c;dt<=t & c & '1' & '0';U1 :xzq41 PORT MAP ('0',dt,b,a,f);【作业】以下所有题目必须用VHDL代码实现。

![[计算机软件及应用]第4章VHDL设计实例PPT课件](https://uimg.taocdn.com/0dcd63c0a2161479161128c0.webp)

实验二 组合逻辑电路的VHDL 设计一、实验目的与要求 1、目的(1)熟悉VHDL 语言的基本结构(2)掌握用VHDL 语言实现组合逻辑功能器件的逻辑功能的一般方法。

2、要求(1)调试程序要记录调试过程中出现的问题及解决办法; (2)给出每个问题的算法或画出流程图;(3)编写程序要规范、正确,上机调试过程和结果要有记录,并注意调试程序集成环境的掌握及应用,不断积累编程及调试经验; (4)做完实验后给出本实验的实验报告。

二、实验设备、环境PII 以上计算机,装有QuartusII 软件 三、方法与步骤(一)教师简单回顾所需知识并演示较一个简单功能的实现过程。

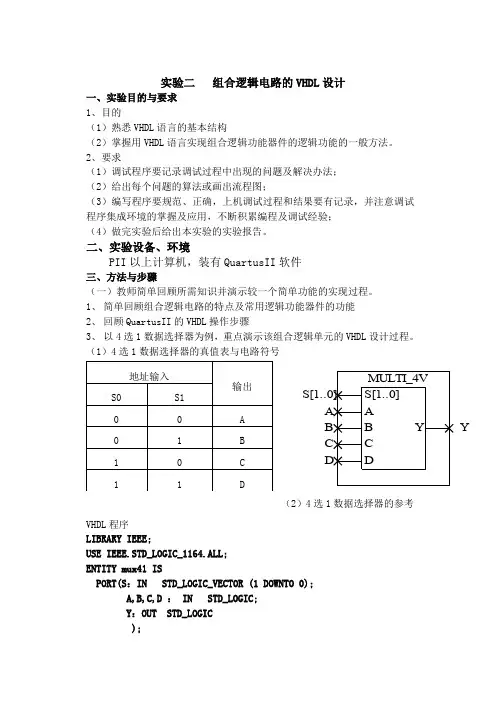

1、 简单回顾组合逻辑电路的特点及常用逻辑功能器件的功能 2、 回顾QuartusII 的VHDL 操作步骤3、 以4选1数据选择器为例,重点演示该组合逻辑单元的VHDL 设计过程。

(1)4选1数据选择器的真值表与电路符号(2)4选1数据选择器的参考VHDL 程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux41 ISPORT(S :IN STD_LOGIC_VECTOR (1 DOWNTO 0); A,B,C,D : IN STD_LOGIC; Y :OUT STD_LOGIC );地址输入输出S0 S1 0 0 A 0 1 B 1 0 C 11DS[1..0]A B C DYMULTI_4VA B C DS[1..0]YEND mux41;ARCHITECTURE a OF mux41 ISBEGINPROCESS (s,A,B,C,D)BEGINIF (S="00") THENY <= A;ELSIF (S="01") THENY <= B;ELSIF (S="10") THENY <= C;ELSIF (S="11") THENY <= D;END IF;END PROCESS;END a;四、实验过程、内容、数据处理及分析按照设计选题编写简单程序1、可供选择进行设计的组合逻辑电路如下,要求规定课时内至少完成3种逻辑电路的设计。

VHDL 数字逻辑电路设计19例第1章组合逻辑电路8例1. 2-4译码器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ymq24 ISPORT (EN,A,B:IN STD_LOGIC;YN : OUT STD_LOGIC_vector(3 downto 0 ));END ENTITY ymq24 ;ARCHITECTURE rt1 OF ymq24 ISSIGNAL T:STD_LOGIC_vector(1 downto 0 );BEGINT<=A & B;process(EN,T)beginIF EN='1' THEN YN<="1111";ELSIF T="00" THEN YN<="1110";ELSIF T="01" THEN YN<="1101";ELSIF T="10" THEN YN<="1011";ELSE YN<="0111";END IF;End process;END ARCHITECTURE rt1;2. 3-8译码器USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ymq38 ISPORT (G1,G2N,G3N,A,B,C:IN STD_LOGIC;YN : OUT STD_LOGIC_vector(7 downto 0 )); END ENTITY ymq38 ;ARCHITECTURE rt1 OF ymq38 ISSIGNAL T1,T2:STD_LOGIC_vector(2 downto 0 );BEGINT1<=A & B & C;T2<=G1 & G2N & G3N;process(G1,G2N,G3N,T1,T2)beginIF T2/="100" THEN YN<="11111111";ELSIF T1="000" THEN YN<="11111110";ELSIF T1="001" THEN YN<="11111101";ELSIF T1="010" THEN YN<="11111011";ELSIF T1="011" THEN YN<="11110111";ELSIF T1="100" THEN YN<="11101111";ELSIF T1="101" THEN YN<="11011111";ELSIF T1="110" THEN YN<="10111111";ELSE YN<="01111111";END IF;End process;END ARCHITECTURE rt1;3. 4选1LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY xzq41 ISPORT(gn: IN STD_LOGIC;d: IN STD_LOGIC_VECTOR(3 DOWNTO 0);a0,a1: IN STD_LOGIC;y: out STD_LOGIC);END ENTITY xzq41;ARCHITECTURE rt1 OF xzq41 ISsignal s: STD_LOGIC_VECTOR(1 DOWNTO 0); BEGINS<= a1 & a0;Process(S,D,gn)beginif gn='0' thenCASE (S) ISWHEN OTHERS =>NULL;END CASE;else y<='0';end if;End process;END ARCHITECTURE rt1;4. 8选1LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY xzq81 ISPORT(gn: IN STD_LOGIC;d: IN STD_LOGIC_VECTOR(7 DOWNTO 0);a0,a1,a2: IN STD_LOGIC;y: out STD_LOGIC);END ENTITY xzq81;ARCHITECTURE rt1 OF xzq81 ISsignal s: STD_LOGIC_VECTOR(2 DOWNTO 0); BEGINS<= a2 & a1 & a0;Process(S,D,gn)beginif gn='0' thenCASE (S) ISWHEN "000"=> Y<=d(0);WHEN "001"=> Y<=d(1);WHEN "110"=> Y<=d(6);WHEN "111"=> Y<=d(7);WHEN OTHERS =>NULL;END CASE;else y<='0';end if;End process;END ARCHITECTURE rt1;5. 例75LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY l75 ISPORT (A,B,C:IN STD_LOGIC;d,g : OUT STD_LOGIC);END ENTITY l75 ;ARCHITECTURE rt1 OF l75 ISCOMPONENT ymq38PORT (G1, G2N, G3N, A, B, C: IN STD_LOGIC;YN : OUT STD_LOGIC_vector(7 downto 0 )); END COMPONENT ;signal ynt : STD_LOGIC_vector(7 downto 0 );BEGINU1 :ymq38 PORT MAP ('1','0','0',a,b,c,YNt(7 DOWNTO 0));d<=not(ynt(1) and ynt(2) and ynt(4) and ynt(7));g<=not(ynt(1) and ynt(2) and ynt(3) and ynt(7));END ARCHITECTURE rt1;6. 例76LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY l76 ISPORT (A,B,C,D:IN STD_LOGIC;F : OUT STD_LOGIC);END ENTITY l76 ;ARCHITECTURE rt1 OF l76 ISCOMPONENT ymq38PORT (G1,G2N,G3N,A,B,C:IN STD_LOGIC;YN : OUT STD_LOGIC_vector(7 downto 0 ));END COMPONENT ;signal yn1t:STD_LOGIC_vector(7 downto 0 );signal yn2t:STD_LOGIC_vector(7 downto 0 );BEGINU1 :ymq38 PORT MAP ('1',A,'0',B,C,D,YN1t(7 DOWNTO 0));U2 :ymq38 PORT MAP (A,'0','0',B,C,D,YN2t(7 DOWNTO 0));F<=not( yn1t(2) and yn1t(4) and yn1t(6) and yn2t(0) and yn2t(2) and yn2t(4) and yn2t(6)); END ARCHITECTURE rt1;7. 例78-1LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY l78 ISPORT (A,B,C:IN STD_LOGIC;f : OUT STD_LOGIC);END ENTITY l78 ;ARCHITECTURE rt1 OF l78 ISCOMPONENT xzq81PORT(gn: IN STD_LOGIC;d: IN STD_LOGIC_VECTOR(7 DOWNTO 0);a0,a1,a2: IN STD_LOGIC;y: out STD_LOGIC);END COMPONENT ;BEGINU1 :xzq81 PORT MAP ('0',"01101100",c,b,a,f);END ARCHITECTURE rt1;8. 例78-2LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY l78 ISPORT (A,B,C:IN STD_LOGIC;f : OUT STD_LOGIC);END ENTITY l78 ;ARCHITECTURE rt1 OF l78 ISCOMPONENT xzq41PORT(gn: IN STD_LOGIC;d: IN STD_LOGIC_VECTOR(3 DOWNTO 0);a0,a1: IN STD_LOGIC;y: out STD_LOGIC);END COMPONENT ;signal t:STD_LOGIC;signal dt:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINt<= not c;dt<=t & c & '1' & '0';U1 :xzq41 PORT MAP ('0',dt,b,a,f);【作业】以下所有题目必须用VHDL代码实现。

实验一组合逻辑电路的VHDL设计实验报告(1) 实验目的:熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

(2) 实验内容1:用VHDL语言设计2选1多路选择器。

提示:参考例3-1。

要求:首先利用QuartusⅡ完成2选1多路选择器的文本编辑输入和编译、仿真测试等步骤,给出时序仿真波形。

选择目标器件EP1C3,建议选实验电路模式5,如附图1所示。

用键1(PIO0,引脚号为1)控制s;a和b分别接clock0(引脚号为93)和clock2(引脚号为17);输出信号y接扬声器speaker(引脚号为129)。

通过短路帽选择clock0接256Hz信号,clock2接8Hz信号。

引脚锁定后进行编译、下载和硬件测试实验,通过键1控制s,可使扬声器输出不同音调。

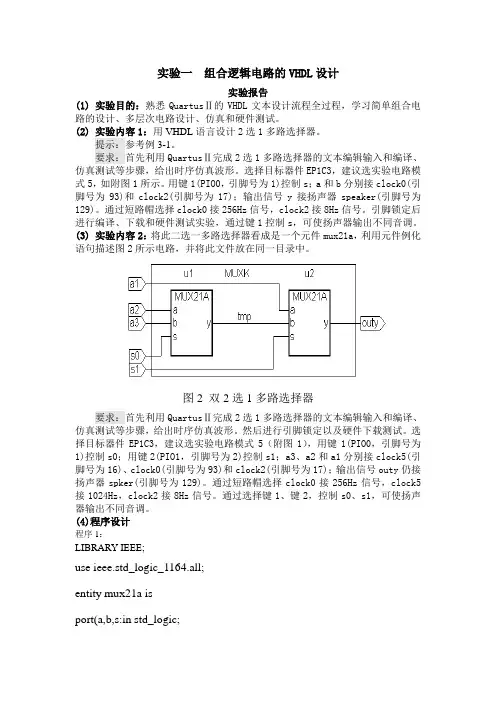

(3) 实验内容2:将此二选一多路选择器看成是一个元件mux21a,利用元件例化语句描述图2所示电路,并将此文件放在同一目录中。

图2 双2选1多路选择器要求:首先利用QuartusⅡ完成2选1多路选择器的文本编辑输入和编译、仿真测试等步骤,给出时序仿真波形。

然后进行引脚锁定以及硬件下载测试。

选择目标器件EP1C3,建议选实验电路模式5(附图1),用键1(PIO0,引脚号为1)控制s0;用键2(PIO1,引脚号为2)控制s1;a3、a2和a1分别接clock5(引脚号为16)、clock0(引脚号为93)和clock2(引脚号为17);输出信号outy仍接扬声器spker(引脚号为129)。

通过短路帽选择clock0接256Hz信号,clock5接1024Hz,clock2接8Hz信号。

通过选择键1、键2,控制s0、s1,可使扬声器输出不同音调。

(4)程序设计程序1:LIBRARY IEEE;use ieee.std_logic_1164.all;entity mux21a isport(a,b,s:in std_logic;y:out std_logic);end entity mux21a;architecture one of mux21a isbeginPROCESS(s,a,b)BEGINCASE S ISWHEN '0' => y <= a;WHEN '1' => y <= b;WHEN OTHERS =>NULL ;END CASE;END PROCESS;end architecture one;程序2:library ieee;use ieee.std_logic_1164.all;entity muxk isport(a1,a2,a3,s0,s1:in std_logic; outy: out std_logic);end entity muxk;architecture one of muxk issignal tmp: std_logic;component mux21aport(a,b,s: in std_logic;y:out std_logic);end component;beginu1: mux21a port map(a=>a2,b=>a3,s=>s0,y=>tmp);u2: mux21a port map(a=>a1,b=>tmp,s=>s1,y=>outy);end architecture one;(5)实验过程打开软件,点击新建建立一个VHDL FILE,将编写好的程序拷进去点击保存根据提示新建一个以实体名为名的工程并选择芯片,程序名也与实体名一致。

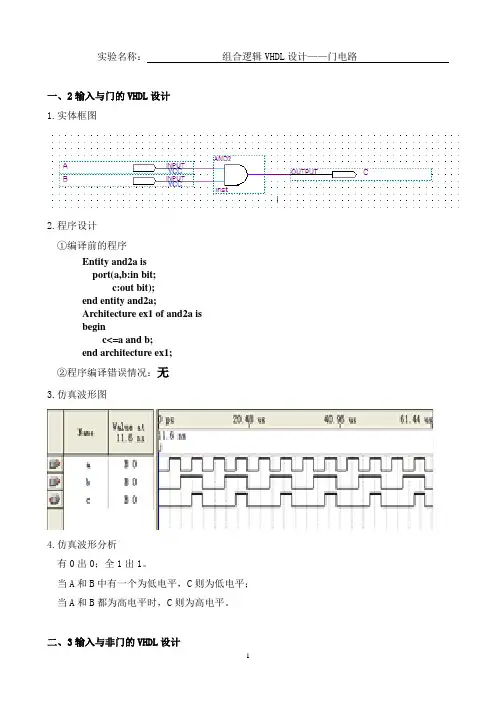

实验名称:组合逻辑VHDL设计——门电路一、2输入与门的VHDL设计1.实体框图2.程序设计①编译前的程序Entity and2a isport(a,b:in bit;c:out bit);end entity and2a;Architecture ex1 of and2a isbeginc<=a and b;end architecture ex1;②程序编译错误情况:无3.仿真波形图4.仿真波形分析有0出0;全1出1。

当A和B中有一个为低电平,C则为低电平;当A和B都为高电平时,C则为高电平。

二、3输入与非门的VHDL设计2.程序设计①编译前的程序Entity nand3a isport(A,B,C:in bit;Y:out bit);end entity nand3a;Architecture ex2 of nand3a isbeginY<=not(A and B and C);end Architecture ex2;②程序编译错误情况:无3.仿真波形图4.仿真波形分析有0出1,全1出0。

当A,B,C中有一个为低电平时,Y则为高电平;当A,B,C三者全为高电平时,Y则为低电平。

三、全加器的VHDL设计2.程序设计①编译前的程序Entity nand3B isport(A,B,CI:in bit;S,CO:out bit);end Entity nand3B;Architecture ex3 of nand3B issignal c,d,e,f :bit;beginc<=A xor B;d<=c and CI;e<=A and B;f<=e nor d;S<=c xor CI;CO<=not f;end architecture ex3;②程序编译错误情况:无3.仿真波形图4.仿真波形分析A B CI CO S0 0 0 0 00 0 1 0 10 1 0 0 10 1 1 1 01 0 0 0 11 0 1 1 01 1 0 1 01 1 1 1 1这是一个全加器,其中A,B为输入,CI为来自低位的进位。

实验一用VHDL语言设计组合逻辑电路一、实验目的:掌握用VHDL语言设计组合逻辑电路的方法。

熟悉QuartusⅡ的操作。

二、实验仪器:PC机一台三、实验内容:1.用VHDL语言设计4选1数据选择器。

2.用文本输入法输入3.建立工程,编译,改错,直至编译通过4.仿真,验证所设计电路的正确性四、操作步骤:1、在所使用的计算机数据盘里建立自己的文件夹2、打开QuartusII3、单击工具栏中的new,在出现的对话框中选择VHDL File,点击OK。

4、输入设计程序。

输入结束后,将程序保存在自己的文件夹中。

注意:存盘的文件名应该跟实体名相同。

5、创建工程。

创建工程有两种方法:第一种方法是在保存文件后出现的对话框中点击‘是’,按提示进行操作;第二种方法是在出现的对话框点击‘否’。

第一种方法的具体过程:点击‘是’,出项下面的框点击‘Next’,出项不需要任何修改,继续点击‘Next’,出项继续点击‘Next’,在后面出现的框图中继续点击‘Next’,直到没有‘Next’选项,点击‘Finish’,这样就完成工程的创建。

第二种方法的具体过程:点击‘否’此时要创建工程,点击菜单File下的“New Preject Wizard”。

出现框图:点击‘Next’,出项点击最上一行右边的,寻找你的文件所在的文件夹,点击要创建工程的文件名,点击打开(或双击要创建工程的文件名),出现项目名称和文件名称相同。

点击‘Next’,出现点击,在出现的对话框点击文件名,点击‘打开’,出现点击右边的‘add’,出现点击‘Next’,在后面出现的框图中继续点击‘Next’,直到没有‘Next’选项,点击‘Finish’,这样就完成工程的创建。

6、观察QUARTUS 界面点击箭头所指图标,观察箭头上方的变化,点击+号,双击出项的文件7、全程编译。

点击箭头所指图标,开始全程编译。

如果有错误,编译会自动停止,出现点击确定,按提示到文件中修改错误,保存文件,继续点击全程编译的图标,如还有错误,继续上面的步骤。

用于逻辑综合的VHDL第三版课程设计引言VHDL (VHSIC Hardware Description Language) 是一种硬件描述语言,广泛应用于数字电路设计和硬件设计领域。

在数字电路设计过程中,逻辑综合是一个非常重要的步骤。

逻辑综合是将高层次的电路设计代码转化为低层次的硬件布局,并且进行优化。

为了学习和掌握VHDL编程和逻辑综合技术,本文档将介绍一篇用于逻辑综合的VHDL第三版课程设计。

设计目标本课程设计的目标是为学生提供一种实践机会,让他们在具体的项目开发中学习和掌握VHDL编程和逻辑综合技术。

本课程设计的具体目标如下:1.学生可以熟练掌握VHDL编程的基本语法,包括entity、architecture、process等。

2.学生可以掌握VHDL模块化设计的基本原则,包括抽象、封装和复用。

3.学生可以了解逻辑综合的基础知识,包括综合基元、综合算法等。

4.学生可以针对给定的电路原理图设计VHDL模块,并进行逻辑综合,得到优化的逻辑电路。

5.学生可以通过仿真验证自己的VHDL设计是否正确,并进行分析和调试。

设计内容本课程设计是一个综合性实践项目,包括VHDL的基本语法和逻辑综合的基本知识。

具体设计内容如下:电路原理图给定一个简单的4位控制器电路原理图,如下所示:+---+reset ----------| |clr ----------| |--+---+| | | |d_in_0[3..0] ----| |--| | +-----+d_in_1[3..0] ----|ALU|--|nc |-----| |d_out_0[3..0] --- | |--| | |reg 0|d_out_1[3..0] --- | |--|nc |-----| || | | | +-----+| | |+---+ || +-----+clk ---------------------| | |----|reg 1|| |+-----+其中,reset, clr和clk均为电路的输入信号,d_in_0[3..0]和d_in_1[3..0]为4位输入数据,ALU为逻辑运算模块,d_out_0[3..0]和d_out_1[3..0]为4位输出数据,reg 0和reg 1为寄存器模块。

实验一组合逻辑电路的设计一、实验目的:1.熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

2.加深FPGA\CPLD设计的过程,并比较原理图输入和文本输入的优劣。

二、实验的硬件要求:1.GW48EDA/SOPC+PK2实验系统。

三、实验内容:1.首先利用QuartusⅡ完成2选1多路选择器(如图S1-1)的文本编辑输入(mux21a.vhd)和仿真测试等步骤。

最后在实验系统上进行硬件测试,验证本项设计的功能。

图S1-12.将此多路选择器看成是一个元件mux21a,利用原理图输出法完成图s1-2,并将此文件放在同一目录中。

图s1-2编译、综合、仿真本例程,并对其仿真波形作出分析说明。

最后在实验系统上进行硬件测试,验证本项设计的功能。

3.以1位二进制全加器为基本元件,用例化语句写出8位并行二进制全加器的顶层文件,编译、综合、仿真本例程,并对其仿真波形作出分析说明。

最后在实验系统上进行硬件测试,验证本项设计的功能。

4.七段数码管译码器(Decoder)七段数码管译码器(Decoder)的输入为4位二进制代码,输出为7个表征七段数码管代码的状态信号。

下面为一个七段数码管译码器的VHDL源代码模型:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY display ISPORT(A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END;ARCHITECTURE ONE OF display ISBEGINPROCESS(A)BEGINCASE A ISWHEN "0000"=>LED7S<="0111111";--X"3F"->0WHEN "0001"=>LED7S<="0000110";--X"06"->1WHEN "0010"=>LED7S<="1011011";--X"5B"->2WHEN "0011"=>LED7S<="1001111";--X"4F"->3WHEN "0100"=>LED7S<="1100110";--X"66"->4WHEN "0101"=>LED7S<="1101101";--X"6D"->5WHEN "0110"=>LED7S<="1111101";--X"7D"->6WHEN "0111"=>LED7S<="0000111";--X"07"->7WHEN "1000"=>LED7S<="1111111";--X"7F"->8WHEN "1001"=>LED7S<="1101111";--X"6F"->9WHEN "1010"=>LED7S<="1110111";--X"77"->10WHEN "1011"=>LED7S<="1111100";--X"7C"->11WHEN "1100"=>LED7S<="0111001";--X"39"->12WHEN "1101"=>LED7S<="1011110";--X"5E"->13WHEN "1110"=>LED7S<="1111001";--X"79"->14WHEN "1111"=>LED7S<="1110001";--X"71"->15WHEN OTHERS=>NULL;END CASE;END PROCESS;END;编译、综合、仿真本例程,并对其仿真波形作出分析说明。

组合逻辑电路的VHDL设计

学院及班级:信工院电子信息工程一班

学号: 20XX550428

姓名:王尧

完成时间: 20XX年10月11日

(1)实验目的:

熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

(2)实验内容1:用VHDL语言设计2选1多路选择器。

提示:参考例3-1。

要求:首先利用QuartusⅡ完成2选1多路选择器的文本编辑输入和编译、仿真测试等步骤,给出时序仿真波形。

选择目标器件EP1C3,建议选实验电路模式5,如附图1所示。

用键1(PIO0,引脚号为1)控制s;a和b分别接clock0(引脚号为93)和clock2(引脚号为17);输出信号y接扬声器speaker(引脚号为129)。

通过短路帽选择clock0接256Hz信号,clock2接8Hz信号。

引脚锁定后进行编译、下载和硬件测试实验,通过键1控制s,可使扬声器输出不同音调。

(3)实验内容2:将此二选一多路选择器看成是一个元件mux21a,利用元件例

化语句描述图2所示电路,并将此文件放在同一目录中。

图2 双2选1多路选择器

要求:首先利用QuartusⅡ完成2选1多路选择器的文本编辑输入和编译、仿真测试等步骤,给出时序仿真波形。

然后进行引脚锁定以及硬件下载测试。

选择目标器件EP1C3,建议选实验电路模式5(附图1),用键1(PIO0,引脚号为1)控制s0;用键2(PIO1,引脚号为2)控制s1;a3、a2和a1分别接clock5(引脚号为16)、clock0(引脚号为93)和clock2(引脚号为17);输出信号outy仍接扬声器spker(引脚号为129)。

通过短路帽选择clock0接256Hz信号,clock5接1024Hz,clock2接8Hz信号。

通过选择键1、键2,控制s0、s1,可使扬声器输出不同音调。

(4)程序设计

程序示例1:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

entity mux21a is

port(a,b,s:in std_logic;

y:out std_logic);

end entity mux21a;

architecture one of mux21a is

begin

PROCESS(s,a,b)

BEGIN

CASE S IS

WHEN '0' => y <= a;

WHEN '1' => y <= b;

WHEN OTHERS =>NULL ;

END CASE;

END PROCESS;

end architecture one;

程序示例2:

library ieee;

use ieee.std_logic_1164.all;

entity muxk is

port(a1,a2,a3,s0,s1:in std_logic;

outy: out std_logic);

end entity muxk;

architecture one of muxk is

signal tmp: std_logic;

ponent mux21a

port(a,b,s: in std_logic;

y:out std_logic);

end ponent;

begin

u1: mux21a port map(a=>a2,b=>a3,s=>s0,y=>tmp);

u2: mux21a port map(a=>a1,b=>tmp,s=>s1,y=>outy);

end architecture one;

(5)实验过程

打开软件,点击新建建立一个VHDL FILE,将编写好的程序拷进去点击保存根据提示新建一个以实体名为名的工程并选择芯片,程序名也与实体名一致。

编译前设置完成后点击START PILATION对程序进行编译检错,然后点击新建建立一个VECTOR WAVEFORM FILE,在EDIT下拉菜单里点END TIME设定仿真结束时间,在VIEW\UTILITY WINDOWS下拉菜单里点击NODE FINDER弹出窗口里点击LIST列出所有端口。

分别将端口移到WAVEFORM1.vwf窗口左边name下,然后分别编辑各输入端口的输入信号。

然后以实体名保存,点击start simulation进行仿真检错。

然后进行引脚锁定和下载:选择ASSIGNMENTS\ASSIGNMENT EDITOR命令,在CATEGORY列表中选择locations;双击To栏的《new》选择电路设计图中的端口,双击location栏的《new》选择外设引脚;储存引脚锁定信息并再编译一次。

选

择Toos\Programmer命令,在Mode下拉列表中选择编程模式,并选中下载文件右侧的第一个小方框,单击左上角的Hardware Setup设置编程器。

向FPGA下载SOF文件前要选择打钩“PROGRAM/CONFIGURE”选项。

然后单击下载标符START 按钮进行下载。

下载完成后按要求进行硬件测试。

(6)仿真波形图

(7)实验分析与总结

1、实验一要注意好内部逻辑与时序,注意端口属性是输入还是输出等,仿真时间

可以适当延长(40-50ns),使观察效果明显,另外,在检验最后的结果是否与要求匹配时,可以按照时序仿真图来观察.

2、实验二的过程中,一度遇到编译报错的问题,后面经检验发现程序的内部架构不完整,顶层文件与子文件的调用关系不明朗,子函数中逻辑缺失,程序不完整,因此在之后的大型程序编写中,要注意先建好程序的内部联系,使逻辑清晰.各种程序调用关系要清楚,不能混淆。