常用组合逻辑电路设计

- 格式:doc

- 大小:768.31 KB

- 文档页数:12

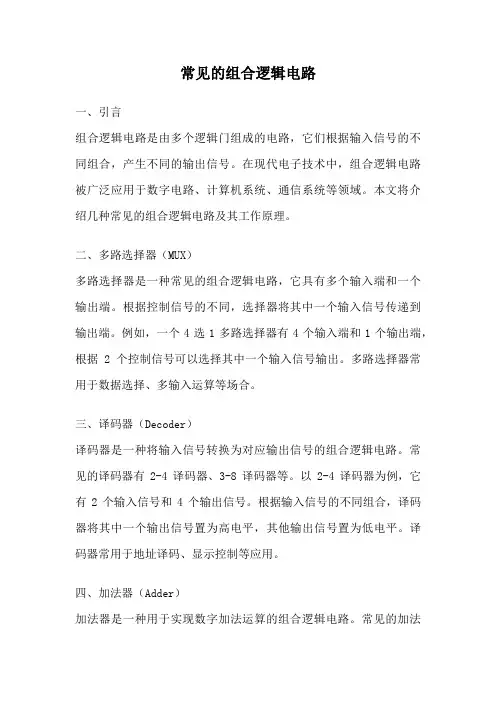

常见的组合逻辑电路一、引言组合逻辑电路是由多个逻辑门组成的电路,它们根据输入信号的不同组合,产生不同的输出信号。

在现代电子技术中,组合逻辑电路被广泛应用于数字电路、计算机系统、通信系统等领域。

本文将介绍几种常见的组合逻辑电路及其工作原理。

二、多路选择器(MUX)多路选择器是一种常见的组合逻辑电路,它具有多个输入端和一个输出端。

根据控制信号的不同,选择器将其中一个输入信号传递到输出端。

例如,一个4选1多路选择器有4个输入端和1个输出端,根据2个控制信号可以选择其中一个输入信号输出。

多路选择器常用于数据选择、多输入运算等场合。

三、译码器(Decoder)译码器是一种将输入信号转换为对应输出信号的组合逻辑电路。

常见的译码器有2-4译码器、3-8译码器等。

以2-4译码器为例,它有2个输入信号和4个输出信号。

根据输入信号的不同组合,译码器将其中一个输出信号置为高电平,其他输出信号置为低电平。

译码器常用于地址译码、显示控制等应用。

四、加法器(Adder)加法器是一种用于实现数字加法运算的组合逻辑电路。

常见的加法器有半加器、全加器等。

半加器用于两个1位二进制数的相加,而全加器用于多位二进制数的相加。

加法器通过多个逻辑门的组合,将两个二进制数进行相加,并输出相应的和与进位。

加法器广泛应用于数字电路、计算机算术单元等领域。

五、比较器(Comparator)比较器是一种用于比较两个数字大小关系的组合逻辑电路。

常见的比较器有2位比较器、4位比较器等。

以2位比较器为例,它有两组输入信号和一个输出信号。

当两组输入信号相等时,输出信号为高电平;当第一组输入信号大于第二组输入信号时,输出信号为低电平。

比较器常用于数字大小判断、优先级编码等应用。

六、编码器(Encoder)编码器是一种将多个输入信号转换为对应输出信号的组合逻辑电路。

常见的编码器有2-4编码器、8-3编码器等。

以2-4编码器为例,它有2个输入信号和4个输出信号。

组合逻辑电路的设计举例例1. 某工厂有A、B、C三个车间和一个自备电站,站内有两台发电机G1和G2。

G1的容量是G2的两倍。

如果一个车间开工,只需G2运行即可满足要求;如果两个车间开工,只需G1运行;如果三个车间同时开工,则G1和 G2均需运行。

试画出控制G1和 G2运行的逻辑图,用与非门实现。

解:(1)根据逻辑要求写出逻辑状态表首先假设逻辑变量取“0”、“1”的含义。

设:A、B、C分别表示三个车间的开工状态:开工为“1”,不开工为“0”;G1和 G2运行为“1”,不运行为“0”。

逻辑状态表ABC G1 G2 0 0 0 00 0 0 1 0 11 0 0 1 0 11 0 1 0 0 01 0 1 1 0 11 0 1 0 1 1 111(2)由逻辑状态表写出逻辑式根据状态表写表达式的一般步骤:①在状态表上找出输出为1的行;②将这一行中所有自变量写成乘积项,当变量的取值为“1”时写为原变量,当变量的取值为“0”时写为原变量的反变量;③将所有乘积项逻辑加,便得到逻辑函数表达式。

这里的乘积项又叫最小项,在最小项里,每个变量都以它的原变量或反变量的形式在乘积项中出现,且仅出现一次。

(3)化简逻辑式(4)用“与非”门构成逻辑电路(5)画出逻辑电路图例2:设计三人表决电路(A、B、C)。

每人一个按键,如果同意则按下,不同意则不按。

结果用指示灯表示,多数同意时指示灯亮,否则不亮。

要求用与非门实现。

解:(1)根据逻辑要求列状态表首先确定逻辑变量取0、1的含义:A、B、C分别表示三人按键的状态,键按下时为“1”,不按时为“0”。

F表示指示灯的亮灭,灯亮为“1”,不亮为“0”。

逻辑要求:两个人(包括两个人)以上同意,指示灯亮。

ABCF 0 0 0 0 0 01 0 0 1 0 01 1 1 1 0 01 0 1 1 1 111111(2)由状态表写出逻辑式并化简、转换(3)实现电路。

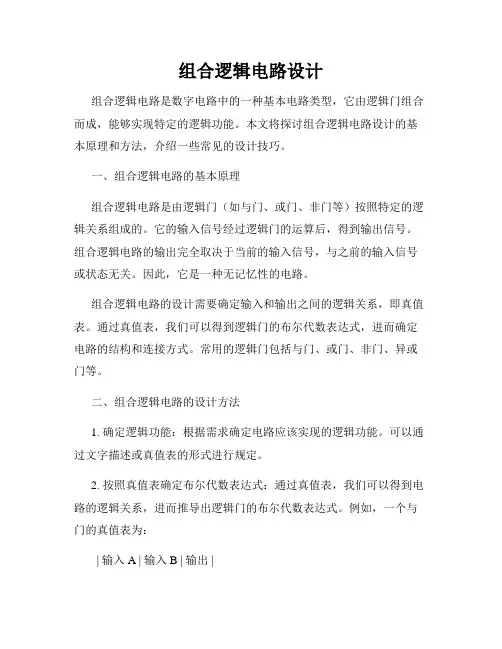

组合逻辑电路设计组合逻辑电路是数字电路中的一种基本电路类型,它由逻辑门组合而成,能够实现特定的逻辑功能。

本文将探讨组合逻辑电路设计的基本原理和方法,介绍一些常见的设计技巧。

一、组合逻辑电路的基本原理组合逻辑电路是由逻辑门(如与门、或门、非门等)按照特定的逻辑关系组成的。

它的输入信号经过逻辑门的运算后,得到输出信号。

组合逻辑电路的输出完全取决于当前的输入信号,与之前的输入信号或状态无关。

因此,它是一种无记忆性的电路。

组合逻辑电路的设计需要确定输入和输出之间的逻辑关系,即真值表。

通过真值表,我们可以得到逻辑门的布尔代数表达式,进而确定电路的结构和连接方式。

常用的逻辑门包括与门、或门、非门、异或门等。

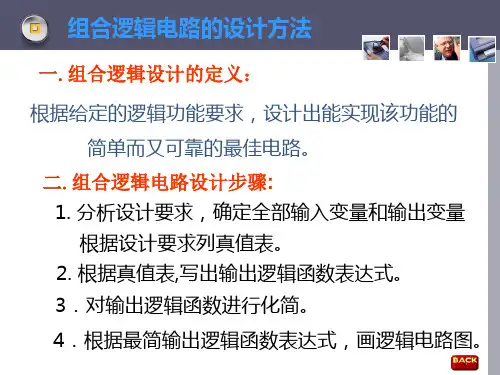

二、组合逻辑电路的设计方法1. 确定逻辑功能:根据需求确定电路应该实现的逻辑功能。

可以通过文字描述或真值表的形式进行规定。

2. 按照真值表确定布尔代数表达式:通过真值表,我们可以得到电路的逻辑关系,进而推导出逻辑门的布尔代数表达式。

例如,一个与门的真值表为:| 输入A | 输入B | 输出 ||------|------|-----|| 0 | 0 | 0 || 0 | 1 | 0 || 1 | 0 | 0 || 1 | 1 | 1 |由此可得与门的布尔代数表达式为:输出 = A·B。

3. 设计逻辑门电路:根据上一步得到的布尔代数表达式,选择适当的逻辑门进行组合设计。

将逻辑门按照表达式和电路的连接关系进行布局。

4. 优化电路结构:对电路进行优化,以减少逻辑门的数量和延迟。

常见的优化技术包括代数化简、费诺定理、卡诺图等。

5. 进行验证和仿真:使用逻辑仿真软件对设计的电路进行验证和调试。

通过输入不同的信号组合,检查输出是否符合预期结果。

三、组合逻辑电路的设计技巧1. 使用多级逻辑门:为了减少电路的延迟和功耗,可以使用多级逻辑门的方式来实现复杂的逻辑功能。

将多个逻辑门级联,形成一个级性结构。

2. 使用寄存器:当需要存储中间结果时,可以使用寄存器来保存数据。

实验一组合逻辑电路的设计组合逻辑电路是一种电子电路,由逻辑门组成,用于执行特定的逻辑功能。

在本实验中,我们将设计一个基本的组合逻辑电路以及一些常见的组合逻辑电路,包括加法器、减法器、比较器等。

首先,我们将设计一个基本的组合逻辑电路,该电路由两个输入和一个输出组成。

输入可以是0或1,输出将依据输入的值进行逻辑运算得出。

在这个基本电路中,我们将使用两个逻辑门:与门和或门。

与门的真值表如下:输入1输入2输出000010100111与门的布尔表达式是:输出=输入1AND输入2或门的真值表如下:输入1输入2输出000011101111或门的布尔表达式是:输出=输入1OR输入2基于以上真值表和布尔表达式,我们可以通过逻辑门的连接来设计一个基本的组合逻辑电路。

具体设计步骤如下:1.首先,将两个输入引线分别连接到与门和或门的输入端。

这将确保输入的值能够传递到逻辑门中。

2.将与门和或门的输出引线连接到一个输出引线上,以便能够输出最终的逻辑结果。

3.最后,将逻辑门的电源连接到电路的电源上,以确保逻辑门能正常工作。

通过以上步骤,我们就完成了一个基本的组合逻辑电路的设计。

这个电路可以根据输入产生不同的输出,实现不同的逻辑功能。

除了基本的组合逻辑电路,我们还可以设计一些常见的组合逻辑电路,如加法器、减法器和比较器。

加法器是用来执行数字加法的组合逻辑电路。

在一个二进制加法器中,输入是两个二进制数和一个进位位,输出是一个和输出和一个进位位。

加法器的设计可以通过级联多个全加器来实现。

减法器是用来执行数字减法的组合逻辑电路。

在一个二进制减法器中,输入是两个二进制数和一个借位位,输出是一个差输出和一个借位位。

减法器的设计可以通过级联多个全减法器来实现。

比较器是用来比较两个数字的大小的组合逻辑电路。

比较器的输出取决于输入的大小关系。

如果两个输入相等,则输出为0。

如果第一个输入大于第二个输入,则输出为1、如果第一个输入小于第二个输入,则输出为-1、比较器的设计可以通过使用逻辑门和触发器来实现。

组合逻辑电路设计之全加器半加器全加器和半加器是组合逻辑电路中常用的两种基本电路。

全加器和半加器可以用于实现二进制数的加法运算。

在本文中,将详细介绍全加器和半加器的设计原理和电路结构。

一、半加器半加器是一个用于实现两个一位二进制数相加求和的电路。

半加器的输入包括两个二进制数A和B,输出包括二进制求和信号S和进位信号C。

```A----,--?--SB----,,--CGND```半加器的输出S等于输入A和B的异或(XOR)结果,输出C等于输入A和B的与(AND)结果。

半加器的真值表如下所示:A,B,S,C---,---,---,---0,0,0,00,1,1,01,0,1,01,1,0,1二、全加器全加器是一个用于实现三个一位二进制数相加求和的电路。

全加器的输入包括两个二进制数A和B,以及一个进位信号Cin(来自上一位的进位或者是初始进位信号),输出包括二进制求和信号S和进位信号Cout (输出给下一位的进位信号)。

```A----,--?---SB ----,,--CoutCin --,--?-------CGND```全加器的输出S等于输入A、B和Cin的异或(XOR)结果,输出Cout等于输入A、B和Cin的任意两个的与(AND)结果和输入A、B和Cin的三个的或(OR)结果的与(AND)结果。

全加器的真值表如下所示:A ,B , Cin , S , Cout---,---,-----,---,------0,0,0,0,00,0,1,1,00,1,0,1,00,1,1,0,11,0,0,1,01,0,1,0,11,1,0,0,11,1,1,1,1三、全加器的电路设计可以通过组合半加器的方式来设计一个全加器。

在全加器中,首先使用两个半加器实现输入A和B的求和结果(S1)和对应的进位(C1);然后再使用一个半加器将输入A和B之间的进位信号(Cin)与求和结果(S1)相加,得到最终的求和结果(S)和进位信号(Cout)。

实验一组合逻辑电路设计一、简介组合逻辑电路是数字电路的一种重要类型,由逻辑门组成,并且没有存储功能。

它的输出只取决于当前的输入状态,与过去的输入状态无关。

本实验旨在设计一组使用逻辑门构成的组合逻辑电路。

二、设计目标本实验的设计目标是实现一个4位2进制加法器电路。

输入为两个4位的二进制数,输出为其和。

为了方便起见,我们假设输入的二进制数已经在输入端以2进制的形式输入。

三、设计思路1.首先,需要设计一个4位的全加器电路,用于对两个位的进位进行处理。

全加器电路由三个输入和两个输出组成。

2.其次,将4个全加器电路组成4位的加法器电路,将各个位的进位进行连接。

3.最后,将输入的两个4位二进制数,以及4个进位信号,分别连接到4个全加器电路的输入端,将各个位的和输出连接到最终的输出端。

四、详细设计1.全加器电路的设计全加器电路有三个输入和两个输出。

其中,三个输入分别为A、B和Cin,分别表示两个相加的输入和进位输入。

两个输出分别为Sum和Cout,分别表示两个输入的和和进位输出。

我们可以使用两个半加器和一个或门来实现全加器电路。

半加器的真值表如下:A B Sum Cout0000011010101101其中,Sum表示两个输入的和,Cout表示两个输入的进位。

将两个半加器按照如下方式连接起来即可构成全加器电路:A --->+------> SumB --->+----------,----> CoutCin --->,--+2.四位加法器电路的设计四位加法器电路由4个全加器电路连接组成。

其中,第一个全加器的输入分别为A0、B0和Cin,输出为S0和C0;第二个全加器的输入分别为A1、B1和C0,输出为S1和C1;依次类推,第三个全加器的输入为A2、B2和C1,输出为S2和C2;第四个全加器的输入为A3、B3和C2,输出为S3和C3将四个全加器按照如下方式连接起来即可构成四位加法器电路:A0--->+---------------->S0B0--->+-------Cin ----,-+-------------------,-------> C0A1---+---->,---------------->S1B1---+---->,-------C0----,--------------,-+---------------,------->C1A2---+------>,---------------->S2B2---+------>,-------C1----,-+---------------->C2A3---+-------+---->,---------------->S3B3---+-----,--------3.输入输出连接将输入的两个4位二进制数依次连接到四位加法器电路的输入端,将四位加法器电路的输出端连接到最终的输出端。

常见的组合逻辑电路组合逻辑电路指的是由多个逻辑门组成的电路,其输出只与输入信号的组合有关,而与输入信号的时间顺序无关。

在现代电子设备中,组合逻辑电路被广泛应用于数字电子系统的设计中。

下面将介绍几种常见的组合逻辑电路及其应用。

一、与门(AND Gate)与门是最基本的逻辑门之一,它只有当所有输入信号都为高电平时,输出才为高电平。

与门在数字电路中扮演着非常重要的角色,可以用于实现多个输入信号的复合判断。

在计算机的算术逻辑单元(ALU)中,与门经常用于进行逻辑运算。

二、或门(OR Gate)或门也是一种常见的逻辑门,它只要任意一个输入信号为高电平,输出就为高电平。

与门和或门可以相互组合使用,实现更复杂的逻辑运算。

或门常用于电子开关和电路选择器等应用中。

三、非门(NOT Gate)非门是最简单的逻辑门,它只有一个输入信号,输出信号是输入信号的反向。

非门常用于信号反转的场合,例如数字信号进行取反操作。

四、与非门(NAND Gate)与非门是由与门和非门组合而成的逻辑门,其输出是与门输出信号取反。

与非门的应用非常广泛,可以用于各种数字电路的设计中,例如计算机内存、固态硬盘等。

五、或非门(NOR Gate)或非门由或门和非门组合而成,其输出是或门输出信号取反。

与与非门类似,或非门也可以用于各种数字电路的设计中,例如译码器、比较器等。

六、异或门(XOR Gate)异或门是一种特殊的逻辑门,只有当输入信号中的奇数个为高电平时,输出为高电平;偶数个为高电平时,输出为低电平。

异或门在编码器、加法器以及数据传输方面有着重要的应用。

七、多路选择器(Multiplexer)多路选择器是一种可以根据选择信号选择不同输入信号的逻辑电路。

它可以将多个输入信号中的一个或多个输出至一个输出线上。

多路选择器可以在数字信号的选择和转换中起到关键作用。

八、译码器(Decoder)译码器是一种将多位输入信号转换为多位输出信号的逻辑电路。

它可以将某个特定的输入编码成高电平,从而实现对多个输入信号的解码和处理。

组合逻辑电路设计实例1. 设计优先编码器设计要求:将Y 0 ~Y 9十个信号编成二进制代码。

其中Y 9的优先级别最高,Y 8次之,依次类推,Y 0优先级别最低。

当有多个信号同时出现在输入端时,要求只对优先级别最高的信号进行编码,且输入、输出都是低电平有效。

(1)分析要求。

Y 0 ~Y 9共十个信号,根据公式2n ≥N =10,取n =4,即取4位二进制码进行编码。

根据设计要求,Y 0 ~Y 9中优先级别高的排斥优先级别低的。

当输入端有多个信号同时存在时,优先级别低的信号无论电平高低,对输出均无影响。

(2)列真值表。

用1表示高电平,用0表示低电平。

由于规定低电平有效,且优先级别高的排斥优先级别低的,被排斥的量用“×”号表示。

输出4位二进制码用DCBA 表示,它们共有16种组合,用来对Y 0 ~Y 9进行编码的方案很多,我们采用其中一种方案。

优先编码器的真值表如表1所示。

表1 优先编码器真值表(3)化简。

因变量太多,用卡诺图化简不方便,可用公式法进行化简。

为便于用与或非门实现该电路,合并使函数值为0的最小项。

先求出反函数的最简与或式,然后再取反求出函数的最简与或非式。

根据真值表写表达式时,因为被排斥的变量对函数值没有影响,所以可以从相应的最小项中去掉,于是可得89899Y Y Y Y Y D +=+= 89Y Y D += 456789567896789789Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y C +++=489589689789Y Y Y Y Y Y Y Y Y Y Y Y +++= 489589689789Y Y Y Y Y Y Y Y Y Y Y Y C +++=2345678934567896789789Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y B +++=2458934589689789Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y +++= 2458934589689789Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y B +++=1234567893456789567897899Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y A ++++=124683468568789Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y A ++++=(4)画逻辑图。

组合逻辑电路设计

组合逻辑电路是一种结构较简单的逻辑电路设计,其组成主要包括逻辑门、寄存器、

比较器、计数器和定时器等功能单元,其基本原理主要是将控制信号和数据信号通过特定

的逻辑关系进行组合,使这两类信号既配合现实应用运算结果正确也可输出想要的结果。

一般来说,组合逻辑电路的设计包括六个基本步骤:要求分析、功能拆解、设计模块、时序分析、组合实现及电路优化。

首先,根据用户的要求或系统的特性分析出电路需求,

以便根据功能分析出系统所要实现的具体功能;其次,划分电路功能模块,然后使用触发器、逻辑门、网络等实现每个功能模块的组合;再次,进行时序分析,以便确定出触发器

的进化规律;再次,将上述步骤中的结果组合起来,使用合适的触发器、逻辑门等将系统

的所有功能实现、组合起来;最后,进行电路优化,以便确定电路的表达能力,减少电路

复杂度,提高组合系统效能。

这样,最终设计出的组合逻辑电路就可以满足用户要求,满足较严格的要求则可以避

免运行失效问题,大大提高电路的可靠性。

此外,组合逻辑还可以按电路特性把功能模块

实现简单化,使系统运行速度更快,也可以更小的电路节省空间达到节能的要求,可谓组

合逻辑电路的优点之一。

实 验 报 告实验日期: 学 号:姓 名:实验名称:常用组合逻辑电路设计 总 分:一、实验目的学习常用组合逻辑电路的可中和代码编写,学习并熟悉VHDL 编程思想与调试方法,掌握LPM 元件实现逻辑设计,从而完成电路设计的仿真验证和硬件验证,记录结果。

二、实验原理VHDL 设计采用层次化的设计方法,自上向下划分系统功能并逐层细化逻辑描述。

层次关系中的没一个模块可以是VHDL 描述的实体,上层VHDL 代码中实例化出各个下层子模块。

利用VHDL 语言和LPM 元件设计这两种方法方法实现两个二位数大小比较的电路,根据A 数是否大于、小于、等于B 数,相应输出端F1、F2、F3为1,设A=A2A1,B=B2B1(A2A1、B2B1表示两位二进制数),当A2A1>B2B1时,F1为1;A2A1<B2B1时,F2为1;A2A1=B2B1时,F3为1。

结构图:Vhdl 实现LPM 元件实现Vhdl 实现LPM 元件实现三、实验设计 ① 利用VHDL 实现 (1)VHDL 代码 library IEEE;use IEEE.std_logic_1164.all; entity bijiao is二位数A2A1 比较运算 二位数B2B1 仿真验证 下载验证port(a2,a1:in STD_LOGIC;b2,b1:in STD_LOGIC;f1,f2:buffer STD_LOGIC;f3:out STD_LOGIC);end bijiao;architecture bijiao_arch of bijiao isbeginf1<=(a2 and(not b2))or(a1 and (not b1)and a2)or(a1 and (not b1)and(not b2));f2<=((not a2)and b2)or((not a2)and(not a1)and b1)or((not a1)and b1 and b2);f3<=not(f1 or f2);end bijiao_arch;(2)波形仿真网格大小 100ns结束时间 2μs功能仿真:时序仿真:输入信号00,01,10,11输入信号00,01,10,11输出信号001,010,100信号均为二进制表达输入信号00,01,10,11(3)仿真分析 周期设置:为得出如图仿真结果,依据题意设置信号输入周期A2为800ns ,A1为400ns ,B2为200ns ,B1为100ns 。

仿真结论:输入 输出A2A1 B2B1 F1F2F3 00 00 001 01 01010 010 11 01001 00 100 01 00110 010 11 01010 00 100 01 10010 001 11 01011 00 100 01 10010 100 11 001由图表结果得出以下结论:I.当A2A1>B2B1时,F1为1; II.当A2A1<B2B1时,F2为1;信号均为二进制表达输入信号00,01,10,11输出信号001,010,100出现延迟III.当A2A1=B2B1时,F3为1; IV.仿真结果正确。

(4)管脚分配(实验板)Input A2 PIN_60Input A1 PIN_59Input B2 PIN_51Input B1 PIN_49Output F1 PIN_88Output F2 PIN_87Output F3 PIN_86(5)下载验证:60、59支配A2A1输入信号,51、49支配B2B1输入信号。

88、87、86分别对应显示F1、F2、F3的结果,又信号输出为1时亮,输出为0时不亮。

结果:I.A2A1>B2B1时,F1为1,88亮灯;II.A2A1<B2B1时,F2为1,87亮灯;III.A2A1=B2B1时,F3为1,86亮灯;结论:下载验证结果与管脚分配保持一致。

(6)RTL viewer调试结果f2~5 b2^b1^a1’ f1~4 b2’^b1’^a1f2~0 b2^a2’ f1~2 a2^(b1’^a1)f2~2 b1^a1’^a2’ f1~5 (b2^b1’^a1)+(b1’^a2)f1~1 b1’^a1f1~0 b2’^a2f2~6 (b2^b1^a1’)+(b2^a2’)+(b1^a1’^a2’)f3~0 (b2^b1^a1’)+(b2^a2’)+(b1^a1’^a2’)+(b2^b1’^a1)+(b1’^a2)②利用LPM元件实现(1)流程利用LPM原件定制实现两个二位数大小比较的电路,包括>、<、=、>=、<=、<>新建工程所在文件夹为lpm_compare2、工程名称为lpm_lpm_compare2、顶层实体名称为lpm_compare2,选择目标器件EPF10K20TI144-4。

选择Tool→Mega Wizard plug-in Manager命令,或在图形编辑窗口中的空白处双击,在弹出的对话框中选择Mega Wizard Plug-in Manager,选择Create a new custom megafunction variation,点击Next。

左侧列表中选择Installed Plug_Ins→Arithmetic→lpm_compare,设置目标器件为Flex10K,元件名为lpm_compare2,文件输出类型为VHDL,单击next。

设置输入数据宽度为2位,选择所需输出端口,单击Next。

设置datab和比较数值符号类型,单击next。

设置流水线,单击Next。

可设置Generate netlist,单击Next。

打开输出路径下地lpm_compare2——waveforms.html。

仿真波形结果如图:输入二进制信号dataa,databA=BA>BA>=BA<BA<=BA≠B结论:与VHDL仿真验证结果保持一致。

(2)管脚分配(实验板)Input dataa[1] PIN_60Input dataa[0] PIN_59Input datab[1] PIN_51Input datab[0] PIN_49Output AeB PIN_95Output AgB PIN_92Output AgeB PIN_91Output AlB PIN_90Output AleB PIN_89Output AneB PIN_88(3)下载验证:60、59支配A2A1输入信号,51、49支配B2B1输入信号。

95、92、91、90、89、88分别对应显示AeB、AgB、AgeB、AlB、AleB、AneB的结果,且信号输出为1时亮,输出为0时不亮。

结果:I.当A=B时,95亮灯;II.当A>B时,92亮灯,III.当A>=B时,91亮灯;IV.当A<B时,90亮灯;V.当A<=B时,89亮灯;VI.当A≠时,88亮灯。

结论:下载验证结果与管脚分配保持一致。

四、思考题1、VHDL中如何调用用户自定义元件、旧式74系列元件、参数化元件?答:调用用户自定义元件:library work;use work.package_name._package_name;调用旧式74系列元件和参数化元件:library altera;use altera.muxplus2.maxplus2;调用参数化原件:library LPM;use LPM.lpm ponents;2、比较VHDL中的signal与variable?答:对信号而言会有延时,而变量则是立即赋值。

变量声明及赋值应在进程中,而信号只需要在整个结构体中声明赋值即可。

在一个进程中,如果对一个信号多次赋值,那么,只有最后一个值才是有效的。

如果对变量多次赋值,那么每次赋值都是有效的,并且,变量的值在再次赋值之前一直保持不变。

3、VHDL中如何设计电路反馈信号?答:将端口声明为Buffer端口,而不是out端口。

4、举例说明常用的VHDL顺序执行和并行执行语句?(1) 顺序执行语句:赋值语句、流程控制语句、等待语句、调用语句、返回语句。

(2) 并行语句:并行信号赋值语句、进程语句、块语句、条件信号赋值语句、元件例化语句、并行过程调用语句、参数传递映射语句、端口说明语句。

5、说明VHDL描述组合逻辑电路是signal的作用是什么?答:在组合逻辑电路中,signal起到电路内部连接传递的作用。

五、实验日志遇到的问题:1、在进行参数设置时,不知道如何设置成仿真图所示。

2、仿真图有细微差别,原因是在LIST选取结点时,未按照信号输入结点的顺序进行点击,即应先点击A2,后点击A1,同理B2B1。

3、在进行LPM宏功能选择对话框的路径必须写明lpm_compare2,未写明是can't find files。

4、在进行LPM的lpm_compare2文件夹中无法找到lpm_compare2_waveforms.html文件,将查找范围定为all.files解决问题。

疑问:lpm_compare2波形中为什么dataa和datab中出现0、1、2、3等信号。

六、实验心得通过本次实验,掌握组合逻辑电路设计的方法,掌握并熟悉VHDL实现、LPM 元件实现以及RTL调试,并进一步熟练了仿真、下载等流程。