文章编号:1671-5314(2003)03-0060-03

作者简介:陈海进(1972-),男,江苏通州人,南通工学院讲师,硕士,主要从事集成电路设计方面的教学与研究。

硬件描述语言与数字集成电路课程教学

陈海进

(南通工学院江苏省专用集成电路设计重点实验室,江苏南通226007)

摘要:以交通灯控制器的设计为例,介绍了Verilo g 硬件描述语言在数字集成电路课程教学中的应用,并探讨了硬件描述语言对数字集成电路设计方法的影响以及现代数字集成电路的教学方法。

关键词:硬件描述语言;电子设计自动化;可编程逻辑器件

中图分类号:T P33文献标识码:A

H ardw are Descri p tion Lan g ua g e and the Teachin g

of Di g ital I nte g rated Circuits

CHEN H ai -j in

(Nanton g Institute of T echnolo gy ,Nanton g 226007,China )

Abstract :T his p a p er took the desi g n of a traffic li g ht controller for exam p le ,introduced the a pp lication of Verilo g H DL in the teachin g of di g ital inte g rated circuits ,and discussed its influence on the desi g n of di g ital inte g rated circuits and the teachin g of m odern di g ital circuits.

K e y w ords :hardw are descri p tion lan g ua g e ;electronic desi g n autom ation ;p ro g ramm able lo g ic dev ice

0引言

电子设计自动化(E DA )的关键技术之一是要求采用形式化的方法来描述数字系统的硬件电路。Verilo g 语言是目前应用最为广泛的硬件描述语言(H DL )之一,并且成为IEEE 的标准。其特点在于能以形式化的抽象表示电路的结构和行为、支持逻辑设计中层次与领域的描述、可借用高级语言的精巧结构来简化电路的描述、具有电路仿真与验证机制以保证设计的正确性、支持电路描述由高层到低层的综合转换、硬件描述

与实现工艺无关(有关工艺参数可通过语言提供的属性包括进去)、

便于文档管理、易于理解和设计使用。本文结合交通灯控制器的设计,介绍Verilo g 语言在数字集成电路设计中的应用及设计方法,并对数字集成电路的教学提出了一些想法。

1传统设计方法的不足与现代数字设计方法的发展

随着电子设计技术的飞速发展,ASIC 和FPG A 的复杂度越来越高。数字通信、工业自动化控制等领域所使用的数字电路及系统的复杂程度也越来越高,特别是需要设计具有实时处理能力的信号处理专用集成电路,并把整个电子系统综合到一个芯片上。设计并验证这样复杂的电路及系统已不再是简单的个人劳动,而需要综合许多专家的经验和知识才能完成。同时,电路制造工艺技术进步非常迅速,电路设计能力跟不上技术的进步。传统的基于电路图的设计方法已日益力不从心,在数字逻辑设计领域,迫切需要一种形式化的设计方法来描述数字电路,这样就能把系统设计工作分解为逻辑设计(前端)和电路实现(后端)两个相互独立而又相关的部分。由于逻辑设计的相对独立性,就可以把专家们设计的各种常用数字逻辑电路第2卷第3期2003年9月南通工学院学报(自然科学版)Journal of Nanton g Institute of T echnolo gy (Natural S cience )V ol.2N o.3S e p .2003

?61?

和系统部件(如FFT 算法、DCT 算法部件)建成宏单元或软核库供设计者引用,以减少重复劳动,提高工作效率。电路的实现则可以借助于逻辑综合工具和布局布线工具(与具体工艺技术有关)来自动完成。

硬件描述语言是一种用形式化的方法来描述数字电路和设计数字逻辑系统的语言。它可以使数字逻辑设计者利用这种语言描述自己的设计思想,然后利用电子设计自动化工具进行仿真,再自动综合到门级电路,最终使用专用集成电路(ASIC )或可编程逻辑器件(P LD )实现其功能。目前,这种称之为高层次设计(H i g h Level Desi g n )的方法已被广泛采用。据统计,在美国硅谷,目前约有90%以上的ASIC 和P LD 采用硬件描述语言进行设计。作为跨世纪的中国大学生,应该尽早掌握这种新的设计方法,使我国在复杂数字电路及系统的设计竞争中逐步缩小与美国等工业发达国家的差距。

2教学中硬件描述语言的选择

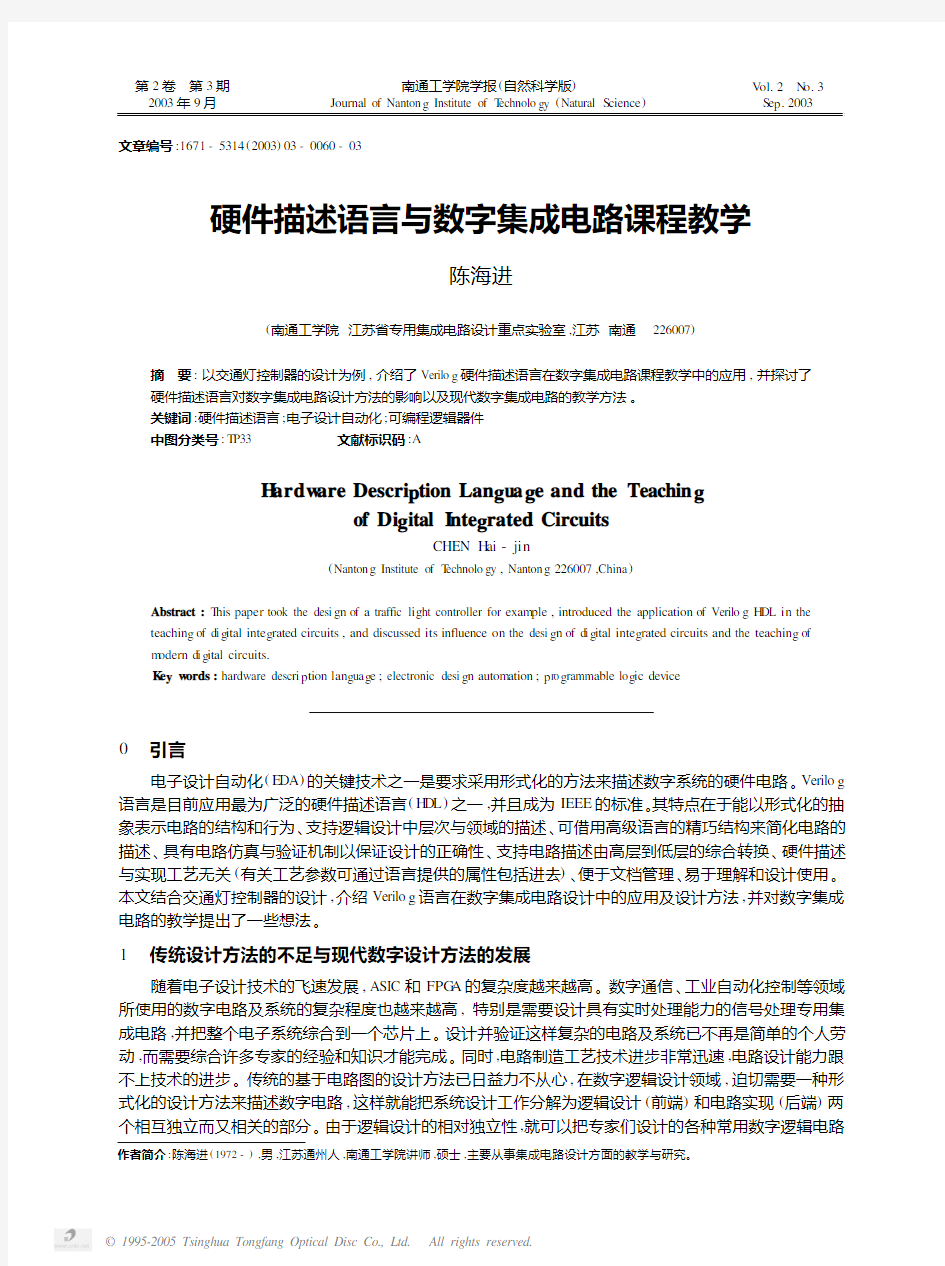

Verilo g 和VH DL 是当前应用最为普遍的两种硬件描述语言,并且都已成为IEEE 的标准。但Verilo g 和VH DL 又各有自己的特点。由于Verilo g H DL 早在1983年就已推出,至今已有19年的应用历史,因而Verilo g H DL 拥有更为广泛的设计群体,成熟的资源也远比VH DL 丰富。与VH DL 相比,Verilo g 最大的优点是:它是

一种非常容易掌握的硬件描述语言,只要有C 语言的

基础,可非常容易地掌握这种设计技术,而掌握VH DL

设计技术就比较困难。这是因为VH DL 不很直观,需

要有Ada 编程基础,一般认为至少需要半年以上的专

业培训,才能掌握VH DL 的基本设计技术。目前版本

的Verilo g H DL 和VH DL 在行为级抽象建模的覆盖范

围也有所不同,图1是两种语言建模能力的比较图。

根据以上分析,考虑到学生学习的方便和日后工作中

的需要,在教学中我们选择了Verilo g 语言。

3Verilo g 语言在交通灯控制器设计中的应用

从课堂教学中学生的反映和批改作业的情况可以看到,仅仅通过课堂教学,学生对Verilo g 语言的掌握仍普遍处于一种似是而非的阶段,这是由Verilo g 语言本身的特点决定的。Verilo g 语言与C 语言在语法上有一定的相似之处,因此,在学生未进行上机编程训练之前普遍的状况是:别人写好的源程序基本都看得懂,自己动手一写就错。分析其中的原因,在于Verilo g 是一门实践性很强的语言,掌握它需要对语言本身和硬件电路知识都十分熟悉,并辅之以一定量的设计实践。

该课程的实践教学环节,我们选择了交通灯控制器作为设计实例。交通灯控制器是一个综合性较强的课程设计项目,包含控制电路、计数器、显示等内容。传统设计方法的步骤分为:系统定义及结构设计、设计原始状态表、状态化简、状态编码、建立输入输出方程,画逻辑图并仿真,编译下载等。学生按此步骤机械地进行,限制了其创造性的发挥,并且对于较大规模的设计,该方法效率低。而使用H DL 语言进行CP LD/FPG A 的设计流程,基本可分为:系统定义及结构设计、H DL 语言设计、仿真、编译下载等步骤。若是进行ASIC 设计,还要针对所选择的工艺对H DL 语言进行自动综合,布局布线,直到最终出G DS 文件到工厂进行流片,其设计灵活,修改容易,不同的源程序设计最终可实现相同的功能,极大地调动了学生的积极性和创造性。实践证明,通过该实践教学环节,加深了学生对Verilo g 语言和数字集成电路的理解,培养了学生运用现代化的设计手段进行数字集成电路设计的能力。

3.1具体设计要求

A 、

B 两道口

1)红、黄、绿灯显示;

2)以倒计时的方式显示时间(红灯,30秒;黄灯,3秒;绿灯,27秒);

3)特殊情况有优先通过的控制权(如消防、警务等)。

3.2设计文档

1)按T o p -Down 设计方法,首先根据设计要求画出图2所示的功能框图,其中选用Altera 可编程器件陈海进:

硬件描述语言与数字集成电路课程教学

南通工学院学报(自然科学版)

?62?2003年

APEX20K来作控制器,指示灯用发光二

极管替代,倒计时用7段数码管。然后确

定接口信号的状态转换及信号定义。

2)控制流程:根据交通灯控制器的

工作原理,将其分为三个状态,如图3

所示。

3)设计说明

(1)a、b两个道口的交通状态分别

各有红、黄、绿三个状态,分别对应红、

黄、绿灯的转换及计时显示,以state a和state b的变化为标志0代表红灯,1代表绿灯,2代表黄灯。

(2)程序中计数器均为二进制计数器,可以节省寄存器资源。

(3)最高优先控制为CONT ROL控制,其次为state a、state b控制。在特殊情况时,可通过改变CONT ROL 的值控制交通灯,CONT ROL=1对应a道口绿灯,CONT ROL=2对应b道口绿灯。

3.3设计实现

使用Verilo g H DL语言,根据上述功能要求进行设计。将设计的源文件进行编译,从仿真波形上可以判断所设计的逻辑电路的正确性,如图4所示。使用q uartus2.1软件,通过管脚配置,优化适配生成熔丝图文件,下载到Altera公司的APEX20K芯片,与外围电路连接调试,结果与设计指标完全一致。在条件许可的情况下,还可借助自动综合工具将上述verilo g设计综合到特定工艺的集成电路标准单元库,并进行自动布局布线,生成可供流片的标准版图数据交换文件,送代工厂进行芯片加工。可以看出整个控制设计简洁,控制转换逻辑关系清楚,便于参数修改和调试。全部设计依据控制关系写出,并不涉及具体电路的连接。

4结束语

通过教学实践,学生普遍反映,利用硬件描述语言进行逻辑设计具有描述方法多、设计快、修改容易、好学好用等优点,在动手进行了一个项目的设计之后,进一步加深了对硬件描述语言和数学集成电路本身以及两者之间相互关系的理解,为今后从事数字集成电路设计工作打下了一定的基础。

数字集成电路设计是一门新的课程,跟踪当前最新的设计方法和手段,适应用人单位对人才的需要并结合本校的实际教学环境是该课程的基本教学指导方向。我们认为,在数字集成电路教学中,应作如下考虑:(1)应重点讲授当前最新的设计方法,讲述清楚数字集成电路与H DL语言两者之间的关系。(2)针对该门课程的特点,强化实践教学环节,让学生在实践中掌握知识。(3)考虑到当前用人单位的实际需要,以CM OS集成电路的设计方法讲解为主,兼顾双极型集成电路设计方法的讲解。

参考文献:

[1]夏宇闻.从算法设计到硬线逻辑的实现———复杂数字逻辑系统的Verilo g H DL设计技术和方法[M].北京:高等教育出版

社,2001.

[2]王志华,邓仰东.数字集成系统的结构化设计与高层次综合[M].北京:清华大学出版社,2000.

[3]杨之廉,申明.超大规模集成电路设计方法学导论(第二版)[M].北京:清华大学出版社,1999.

[4]宋万杰,罗丰,吴顺君.CP LD技术及其应用[M].西安:西安电子科技大学出版社,2000.

组合逻辑电路实验(一)实验报告 一.实验名称:3-8译码器设计 二.实验目的 1.掌握ISE 开发工具的使用,掌握FPGA 开发的基本步骤; 2.掌握组合逻辑电路设计的一般方法; 3.掌握程序下载方法,了解UCF 文件的格式; 4.初步了解开发板资源,掌握开发板使用方法。重点了解滑动开关和LED 显示灯的使用方法。 三.实验内容 1.用VHDL 实现3-8译码器模块 译码器电路如图2-1所示。其功能如表2-1所示。试用VHDL 实现该译码器,并在开发板上进行检验。 表2-1 译码器功能表 EN A B C Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0 1 X X X 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 1 1 1 3-8 译码器 A B C EN Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 图2-1 3-8译码器

0 1 1 0 0 1 0 0 0 0 0 0 0 1 1 1 1 0 0 0 0 0 0 0 2.将程序下载到FPGA并进行检验 (1)资源使用要求:用滑动开关SW3~SW1作为输入A,B,C;滑动开关SW0控制EN;8个LED灯表示8个输出。 (2)检验方法:当SW0处于ON(EN=1)位置时,所有LED灯灭;当SW0处于OFF(EN=0),反映当前输入的译码输出在LED灯上显示,即当输入为000(滑动开关SW3-SW1处于OFF状态),LED0亮,其它灯灭,等等。 四.实验步骤 1.启动ISE,新建工程文件,编写3-8译码器的VHDL模块; 2.新建UCF文件,输入位置约束; 3.完成综合、实现,生成下载文件; 4.连接开发板USB下载线,开启开发板电源; 5.下载到FPGA; 6.拨动开关,验证结果是否正确。 五.主要vhdl代码 architecture Behavioral of coder_38 is --3-8译码器行为级描述signal x:STD_LOGIC_VECTOR (2 downto 0); begin x <= A&B&C;

硬件描述语言HDL的现状与发展 摘要:从数字系统设计的性质出发,结合目前迅速发展的芯片系统,比较、研究各种硬件描述语言;详细阐述各种语言的发展历史、体系结构和设计方法;探讨未来硬件描述语言的发展趋势,同时针对国内EDA基础薄弱的现状,在硬件描述语言方面作了一些有益的思考。 关键词:ASIC 硬件描述语言HDL Verilog HDL VHDL SystemC Superlog 芯片系统SoC 引言 硬件描述语言HDL是一种用形式化方法描述数字电路和系统的语言。利用这种语言,数字电路系统的设计可以从上层到下层(从抽象到具体)逐层描述自己的设计思想,用一系列分层次的模块来表示极其复杂的数字系统。然后,利用电子设计自动化(EDA)工具,逐层进行仿真验证,再把其中需要变为实际电路的模块组合,经过自动综合工具转换到门级电路网表。接下去,再用专用集成电路ASIC或现场可编程门阵列FPGA自动布局布线工具,把网表转换为要实现的具体电路布线结构。 目前,这种高层次(high-level-design)的方法已被广泛采用。据统计,目前在美国硅谷约有90%以上的ASIC和FPGA采用硬件描述语言进行设计。 硬件描述语言HDL的发展至今已有20多年的历史,并成功地应用于设计的各个阶段:建模、仿真、验证和综合等。到20世纪80年代,已出现了上百种硬件描述语言,对设计自动化曾起到了极大的促进和推动作用。但是,这些语言一般各自面向特定的设计领域和层次,而且众多的语言使用户无所适从。因此,急需一种面向设计的多领域、多层次并得到普遍认同的标准硬件描述语言。20世纪80年代后期,VHDL和Verilog HDL语言适应了这种趋势的要求,先后成为IEEE 标准。 现在,随着系统级FPGA以及系统芯片的出现,软硬件协调设计和系统设计变得越来越重要。传统意义上的硬件设计越来越倾向于与系统设计和软件设计结合。硬件描述语言为适应新的情况,迅速发展,出现了很多新的硬件描述语言,像Superlog、SystemC、Cynlib C++等等。究竟选择哪种语言进行设计,整个业界正在进行激烈的讨论。因此,完全有必要在这方面作一些比较研究,为EDA设计做一些有意义的工作,也为发展我们未来的芯片设计技术打好基础。 1 目前HDL发展状况 目前,硬件描述语言可谓是百花齐放,有VHDL、Superlog、Verilog、SystemC、Cynlib C++、C Level等等。虽然各种语言各有所长,但业界对到底使用哪一种语言进行设计,却莫衷一是,难有定论。 而比较一致的意见是,HDL和C/C++语言在设计流程中实现级和系统级都具有各自的用武之地。问题出现在系统级和实现级相连接的地方:什么时候将使用中的一种语言停下来,而开始使用另外一种语言?或者干脆就直接使用一种语言?现在看来得出结论仍为时过早。 在2001年举行的国际HDL会议上,与会者就使用何种设计语言展开了生动、激烈的辩论。最后,与会者投票表决:如果要启动一个芯片设计项目,他们愿意选择哪种方案?结果,仅有2

《硬件描述语言及FPGA设计》复习要点: 一、名词解释 ⑴设计方法:自顶向下和自底向上,以自顶向下为主要设计。 综合:指的是将较高级抽象层次的设计描述自动转化外较低层次的描述过程。 1.EDA :电子设计自动化 2.HDL :硬件描述语言 SoC :系统芯片 4.ASIC :专用集成电路 5.PLD :可编程逻辑器件 6.CPLD :复杂可编程逻辑器件 7.FPGA :现场可编程门阵列 8.LUT :查找表 9.JTAG :联合测试行动组 10.ISP :在系统编程 11.IP核:完成某种功能的设计模块 12.逻辑综合:将设计者在EDA平台上编辑输入的HDL文本、原理图或状态图描述,依据给定的硬件结构和约束控制条件进行编译、优化和转换,最终获得门级电路甚至更底层的电路描述网表文件的过程。 13.设计输入:将设计者所设计的电路以开发软件要求的某种形式表达出来,并输入到相应软件中的过程。 14.下载:把适配后生成的编程文件装入到PLD器件中的过程 15.FSM: 有限状态机 16.UDP:用户自定义 17.NS:次态 18.OL:输出逻辑 二、填空 1.EDA就是以计算机为工作平台,以EDA软件工具为开发环境,以PLD器件或者ASIC专用集成电路为目标器件设计实现电路系统的一种技术。 2.在数字电路设计过程中,综合是将软件转化为硬件电路的关键步骤,是文字描述与硬件实现的一座桥梁。 3.通常,将对CPLD的下载称为编程,对FPGA中的SRAM进行直接下载的方式称配置。 4.仿真时是否考虑硬件延时分类,可分为功能仿真和时序仿真。 5.IP核主要包括硬核、固核和软核。 6.当前最流行的并且成为IEEE标准的硬件描述语言包括Verilog HDL 和VHDL 。7.当前EDA设计中普遍采用的方法是:自顶向下。

摘要:从数字系统设计的性质出发,结合目前迅速发展的芯片系统,比较、研究各种硬件描述语言;详细阐述各种语言的发展历史、体系结构和设计方法;探讨未来硬件描述语言的发展趋势,同时针对国内eda基础薄弱的现状,在硬件描述语言方面作了一些有益的思考。关键词:asic 硬件描述语言hdl verilog hdl vhdl systemc superlog 芯片系统soc引言硬件描述语言hdl是一种用形式化方法描述数字电路和系统的语言。利用这种语言,数字电路系统的设计可以从上层到下层(从抽象到具体)逐层描述自己的设计思想,用一系列分层次的模块来表示极其复杂的数字系统。然后,利用电子设计自动化(eda)工具,逐层进行仿真验证,再把其中需要变为实际电路的模块组合,经过自动综合工具转换到门级电路网表。接下去,再用专用集成电路asic或现场可编程门阵列fpga自动布局布线工具,把网表转换为要实现的具体电路布线结构。目前,这种高层次(high-level-design)的方法已被广泛采用。据统计,目前在美国硅谷约有90%以上的asic和fpga采用硬件描述语言进行设计。硬件描述语言hdl的发展至今已有20多年的历史,并成功地应用于设计的各个阶段:建模、仿真、验证和综合等。到20世纪80年代,已出现了上百种硬件描述语言,对设计自动化曾起到了极大的促进和推动作用。但是,这些语言一般各自面向特定的设计领域和层次,而且众多的语言使用户无所适从。因此,急需一种面向设计的多领域、多层次并得到普遍认同的标准硬件描述语言。20世纪80年代后期,vhdl和verilog hdl语言适应了这种趋势的要求,先后成为ieee标准。现在,随着系统级fpga以及系统芯片的出现,软硬件协调设计和系统设计变得越来越重要。传统意义上的硬件设计越来越倾向于与系统设计和软件设计结合。硬件描述语言为适应新的情况,迅速发展,出现了很多新的硬件描述语言,像superlog、systemc、cynlib c++等等。究竟选择哪种语言进行设计,整个业界正在进行激烈的讨论。因此,完全有必要在这方面作一些比较研究,为eda设计做一些有意义的工作,也为发展我们未来的芯片设计技术打好基础。 1 目前hdl发展状况目前,硬件描述语言可谓是百花齐放,有vhdl、superlog、verilog、systemc、cynlib c++、c level等等。虽然各种语言各有所长,但业界对到底使用哪一种语言进行设计,却莫衷一是,难有定论。而比较一致的意见是,hdl和c/c++语言在设计流程中实现级和系统级都具有各自的用武之地。问题出现在系统级和实现级相连接的地方:什么时候将使用中的一种语言停下来,而开始使用另外一种语言?或者干脆就直接使用一种语言?现在看来得出结论仍为时过早。在2001年举行的国际hdl会议上,与会者就使用何种设计语言展开了生动、激烈的辩论。最后,与会者投票表决:如果要启动一个芯片设计项目,他们愿意选择哪种方案?结果,仅有2票或3票赞成使用systemc、cynlib和c level 设计;而superlog和verilog各自获得了约20票。至于以后会是什么情况,连会议主持人john cooley也明确表示:“5年后,谁也不知道这个星球会发生什么事情。”各方人士各持己见:为verilog辩护者认为,开发一种新的设计语言是一种浪费;为systemc辩护者认为,系统级芯片soc快速增长的复杂性需要新的设计方法;c语言的赞扬者认为,verilog 是硬件设计的汇编语言,而编程的标准很快就会是高级语言,cynlib c++是最佳的选择,它速度快、代码精简;superlog的捍卫者认为,superlog是verilog的扩展,可以在整个设计流程中仅提供一种语言和一个仿真器,与现有的方法兼容,是一种进化,而不是一场革命。当然,以上所有的讨论都没有提及模拟设计。如果想设计带有模拟电路的芯片,硬件描述语言必须有模拟扩展部分,像verilog hdl-a,既要求能够描述门级开关级,又要求具有描述物理特性的能力。 2 几种代表性的hdl语言2.1 vhdl 早在1980年,因为美国军事工业需要描述电子系统的方法,美国国防部开始进行vhdl的开发。1987年,由ieee(institute of electrical and electro- nics engineers)将vhdl制定为标准。参考手册为ieee vhdl 语言参考手册标准草案1076/b版,于1987年批准,称为ieee 1076-1987。应当注意,起初vhdl只是作为系统规范的一个标准,而不是为设计而制定的。第二个版本是在1993年制定

硬件描述语言期末复习整理 1、EDA:Electronic Design Automation 现代电子设计技术的核心是EDA(Electronic Design Automation)技术。 EDA技术就是依靠功能强大的电子计算机,在EDA工具软件平台上完成电子系统的设计工作。 2、20世纪90年代以来,微电子工艺有了惊人的发展,工艺水平已经达到了深亚微米级(通常把0.8-0.35um称为亚微米,0.25um及其以下称为深亚微米) 3、用EDA技术设计电路可以分为不同的技术环节,每一个环节中必须有对应的软件包或专用的EDA工具独立处理。 4、EDA工具大致可以分为设计输入编辑器、仿真器、HDL综合器、适配器(或布局布线器)以及下载器等5个模块。 一般的设计输入编辑器都支持图形输入和HDL文本输入 图形输入通常包括原理图输入、状态图输入和波形图输入三种常用方法。 5、在EDA技术中仿真的地位非常重要,行为模型的表达、电子系统的建模、逻辑电路的验证以及门级系统的测试,每一步都离不开仿真器的模拟检测。 在EDA发展的初期,快速地进行电路逻辑仿真是当时的核心问题,即使在现在,各个环节的仿真仍然是整个EDA设计流程中最重要、最耗时的一个步骤。因此,仿真器的仿真速度、仿真的准确性和易用性成为衡量仿真器的重要指标。 6、硬件描述语言诞生的初衷是用于设计逻辑电路的建模和仿真 HDL综合器是将硬件描述语言转化为硬件电路的重要工具。 7、HDL综合器的输出文件一般是网表文件,是一种用于电路设计数据交换和交流的工业标准化格式的文件,或是直接用硬件描述语言HDL表达的标准格式的网表文件,或是对应FPGA/CPLD器件厂商的网表文件。 8、电路网表(逻辑图)由元件名N、模型M、输入端信号PI、输出端信号PO四部分组成,是唯一确定电路连接关系的数据结构。即:E=(N,M,PI,PO) 9、常用的编程语言 C、Pascal、Fortran、Basic或汇编语言-算法研究 硬件描述语言-设计和制造硬件逻辑专用电路 10、实时系统不能采用通用计算机系统,自行设计非常轻便小巧的高速专用硬件系统来完成该任务。 11、FPGA-用高密度的FPGA(从几万门、几十万门到几百万门)来构成完成算法所需的电路系统是一种较好的办法。 FPGA是一种通用的器件,它的基本结构决定了对某一种特殊应用,性能不如专用的ASIC 电路。 专用集成电路-利用现成的微处理机IP核或根据某一特殊应用设计的微处理机核(也可以没有微处理机核),并结合专门设计的高速ASIC运算电路,能设计出性能价格比最高的理想数字信号处理系统。 12、传统的设计方法:查用器件手册;选用合适的微处理器和电路芯片;设计面包板和线路板;调试;定型;设计复杂的系统(几十万门以上)极其困难。 13、美国和中国台湾地区逻辑电路设计和制造厂家大都以Verilog HDL为主。 1、可编程逻辑器件(PLD)是一种能将数字系统实现在硬件电路上的设备,即能在现场规

中北大学 试题答案及评分标准 硬件描述语言及器件课程 (课程名称须与教学任务书相同) 20xx/20xx 学年第一学期 试题类别 A 拟题日期拟题教师 课程编号教师编号 使用班级 备注:试题答案要求按指定规格计算机打印,并将其文本与电子稿一并上交: ①校级考试课程交评估与考试中心命题科; ②院级考试课程交院教务科。

20xx/20xx 学年第一学期末考试试题答案及评分标准 (A卷) 硬件描述语言及器件 使用班级: xxxx 一、填空题(20分,每空格1分) 1、VHDL语言中标识符通常分为短标识符,扩展标识符两种。 2、VHDL对象包含常量,信号,变量,文件 4个基本数据类型。 3、VHDL语言中,数据类型常量说明的一般格式为: CONSTANT常数名:数据类型:=表达式;。 4、VHDL中位矢量类型表达为 bit ,位向量类型表达为 bit_vector() 。 5、VHDL语言有类型标记法,函数转换法,常数转换法 3种不同类型的数据变换方法。 6、VHDL中,设D0为“1001”, D1为'0', D2为“0110”。D0 & D1的运算结果是“10010”,D0 & D2的运算结果是“10010110”。 7、VHDL语言中包括四种运算操作符,分别是逻辑运算符,算术运算符,关系运算符,和并置运算符。 8、为了启动进程,VHDL语言中必须包含一个显示的敏感信号量表或者包含一个wait语句。

二、判断对错并给出判断依据(20分,每小题5分,判断对错2分,给出正确判断依据3分) 1、进程之间的通信可以通过变量传递来实现。(×) 进程之间的通信需通过信号传递实现。 2、VHDL语言的高速性体现在其进程之内的带入语句都是并行执行的。(×) 进程之内的带入语句是顺序执行的。 3、语句y <= a when s=”00” else b when s=”01” else c when s=”10” else d; 中,s=”00”条件的优先级最高(√) 4、com1:u1 PORT MAP(a => n1,b => n2,c => m);语句中采用了位置映射的信号端口映射方式。(×) 采用的是名称映射方式

上海建桥学院本科课程教学大纲 【硬件设计语言及电路仿真】 【HDL Hardware Description Language and circuit simulation】 一、基本信息 课程代码:【b0822101】 课程学分:【3学分】 面向专业:【微电子学专业】 课程性质:【基础必修课】 开课院系:电子系 使用教材:主教材【《Verilog HDL 与数字系统设计简明教程》吴弋编人民邮电出版社 2009】辅助教材【《数字系统设计与Verilog HDL》(第二版) 王金明编电子工业出版社2005】 参考教材【《Verilog数字系统设计教程》夏宇闻编北京航天航空大学出版社2008】先修课程:【数字逻辑电路 b08214021(4)】 二、课程简介 本课程是微电子、电子、通信专业的一门重要的专业课,是学生学习专业课和从事本专业的科研、生产工作的重要基础。该门课程主要分为两大部分:第一部分主要使学生初步了解EDA技术的现状与发展,以及EDA技术自顶向下的设计方法,要求学生可熟练应用EDA工具平台(QuarutsII、Modelsim等开发软件)对可编程芯片(FPGA或CPLD)进行电路或系统的设计、仿真、下载与调试。第二部分基于硬件描述语言进行数字电路系统的设计与仿真则是该门课程的核心内容。这部分重点介绍目前比较流行的硬件描述语言——Verilog HDL语言,以及它的基本语法、基本结构、建模方法、模块调用以及模块测试等。并且给出不少目前较为常用的数字电路模块的编程实例,如加法器、编码器、译码器、数据选择器等组合逻辑电路,触发器、锁存器、计数器、移位寄存器等时序逻辑电路,以及Mealy状态机、Moore状态机等等。通过本课程的学习,使学生能够比较熟练地使用QuartusII等常用EDA软件对可编程芯片进行一些简单电路系统的设计,如交通灯控制电路,LED点阵显示,自动售货机控制电路,音乐播放器等。三、选课建议 FPGA设计是数字集成电路设计的重要组成部分和实践环节,属于应用部分,是数字集成电路设计的后续课程,应安排在数字电路课程之后。 四、课程基本要求 了解可编程逻辑器件的基本知识,EDA发展历程及EDA设计流程,以及常用的EDA工具。熟悉硬件描述语言的基本结构、建模方式、常用电路模块的设计实例。重点掌握借助于EDA开发工具用硬件描述语言设计可编程芯片电路系统的方法。 五、课程内容 第一部分 EDA技术概述 教学目的及要求:

硬件描述语言[浏览次数:约491次] ?硬件描述语言HDL是一种用形式化方法描述数字电路和系统的语言。 利用这种语言,数字电路系统的设计可以从上层到下层(从抽象到具体)逐层描述自己的设计思想,用一系列分层次的模块来表示极其复杂的数字系统。然后,利用电子设计自动化(EDA)工具,逐层进行仿真验证,再把其中需要变为实际电路的模块组合,经过自动综合工具转换到门级电路网表。接下去,再用专用集成电路ASIC或现场可编程门阵列FPGA自动布局布线工具,把网表转换为要实现的具体电路布线结构。 目录 ?硬件描述语言的概述 ?硬件描述语言的结构 ?硬件描述语言的优点 ?硬件描述语言的用途 ?硬件描述语言开发流程 ?硬件描述语言与原理图输入法的关系 ?硬件描述语言的发展 硬件描述语言的概述 随着EDA技术的发展,使用硬件语言设计PLD/FPGA成为一种趋势。目前最主要的硬件描述语言是VHDL和Verilog H DL。 VHDL发展的较早,语法严格,而Verilog HDL是在C语言的基础上发展起来的一种硬件描述语言,语法较自由。 VHDL和Verilog HDL两者相比,VHDL的书写规则比Verilog烦琐一些,但verilog 自由的语法也容易让少数初学者出错。国外电子专业很多会在本科阶段教授VHDL,在研究生阶段教授verilog。从国内来看,VHDL的参考书很多,便于查找资料,而Verilog HDL的参考书相对较少,这给学习Verilog HDL带来一些困难。 从EDA技术的发展上看,已出现用于CPLD/FPGA设计的硬件C语言编译软件,虽然还不成熟,应用极少,但它有可能会成为继VHDL和Verilog之后,设计大规模CPLD/FPGA的又一种手段。 硬件描述语言[浏览次数:约491次]

2007/2008 学年第一学期末考试试题(A卷) 硬件描述语言及器件 使用班级:05182401/2/3 一、填空题(20分,每空格1分) 1、VHDL是否区分大小写?。 2、digital_ _8标识符合法吗?。12_bit标识符合法吗?。 signal标识符合法吗?。 3、结构体有三种描述方式,分别是、、和。 4、请分别列举一个常用的库和程序包、。 5、一个信号处于高阻(三态)时的值在VHDL中描述为。 6、将一个信号width定义为一个4位标准逻辑向量的语句为 。 7、/=是操作符,功能是。 8、设D0为'0', D1为'1', D2为'1', D3为'0', D3 & D2 & D1 & D0的运算结果是 ,(D3 or D2)and(D1 and not D0)的运算结果是:。 9、赋值语句是(并行/串行)执行的,if语句是(并行/串行)执行的。 10、请列举三种可编程逻辑器件:、、。

二、简答(20分,每小题5分) 1、简述VHDL程序的基本结构。 2、简述信号与变量的区别。 3、简述可编程逻辑器件的优点。 4、试比较moore状态机与mealy状态机的异同。

三、判断题(10分) library ieee; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; 以上库和程序包语句有无错误?,有的话请在原程序相应位置改正。 entity rom is port( addr: in std_logic_vector(0 to 3); ce: in std_logic; data:out std_logic_vector(7 downto 0); ) end rom; 以上port语句有无错误?,有的话请在原程序相应位置改正。 architecture behave of rom is begin process begin if ce='0' then case addr is when "0000"=> data<="10001001"; when "0001"=> data<="10001010"; when "0010"=> data<="10001011"; when "0011"=> data<="10001100"; when "0100"=> data<="10001101";

20XX/20XX学年第一学期末考试试题(A卷) 硬件描述语言及器件 使用班级: XXXXXX 一、填空题(20分,每空格1分) 1、VHDL语言中标识符通常分为,两种。 2、VHDL对象包含,,, 4个基本数据类型。 3、VHDL语言中,数据类型常量说明的一般格式为:。 4、VHDL中位矢量类型表达为,位向量类型表达为。 5、VHDL语言有,, 3种不同类型的数据变换方法。 6、VHDL中,设D0为“1001”, D1为'0', D2为“0110”。D0 & D1的运算结果是,D0 & D2的运算结果是。 7、VHDL语言中包括四种运算操作符,分别是,, ,和。 8、为了启动进程,VHDL语言中必须包含一个或者。

二、判断对错并给出判断依据(20分,每小题5分,判断对错2分,给出正确判断依据3分) 1、进程之间的通信可以通过变量传递来实现。() 2、VHDL语言的高速性体现在其进程之内的带入语句都是并行执行的。() 3、语句y <= a when s=”00” else b when s=”01” else c when s=”10” else d; 中,s=”00”条件的优先级最高() 4、com1:u1 PORT MAP(a => n1,b => n2,c => m);语句中采用了位置映射的信号端口映射方式。()

三、判断题(10分) use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; 以上库和程序包声明是否完整?,如果不完整请添加 entity rom is port( addr: in std_logic; ce: in std_logic; data:out std_logic_vector(7 to 0) ); end rom; 以上实体定义有无错误?,有的话请改正原语句 architecture behave of entity is begin process(ce,addr) begin if ce='0' case addr is when ‘0’=> data<="10001001"; when others=> data<="10011000"; elseif data<="00000000"; end if end behave; 以上architecture中划线各行有无错误?请在相应行划线位置判断并改正。

竭诚为您提供优质的服务,优质的文档,谢谢阅读/双击去除 【什么是硬件描述语言】硬件描述语言 有多少种 什么是硬件描述语言,你知道吗?今天就让小编来教下大家吧,快来看看吧,希望能让大家有所收获! 什么是硬件描述语言 硬件描述语言hDL是一种用形式化方法描述数字电路和系统的语言。利用这种语言,数字电路系统的设计可以从上层到下层(从抽象到具体)逐层描述自己的设计思想,用一系列分层次的模块来表示极其复杂的数字系统。然后,利用电子设计自动化(eDA)工具,逐层进行仿真验证,再把其中需要变为实际电路的模块组合,经过自动综合工具转换到门级电路网表。接下去,再用专用集成电路AsIc或现场可编程

门阵列FpgA自动布局布线工具,把网表转换为要实现的具体电路布线结构。 硬件描述语言的概述 随着eDA技术的发展,使用硬件语言设计pLD/FpgA成为一种趋势。目前最主要的硬件描述语言是VhDL和VeriloghDL。VhDL发展的较早,语法严格,而VeriloghDL 是在c语言的基础上发展起来的一种硬件描述语言,语法较自由。VhDL和VeriloghDL两者相比,VhDL的书写规则比Verilog烦琐一些,但verilog自由的语法也容易让少数初学者出错。国外电子专业很多会在本科阶段教授VhDL,在研究生阶段教授verilog。从国内来看,VhDL的参考书很多,便于查找资料,而VeriloghDL的参考书相对较少,这给学习VeriloghDL带来一些困难。从eDA技术的发展上看,已出现用于cpLD/FpgA设计的硬件c语言编译软件,虽然还不成熟,应用极少,但它有可能会成为继VhDL和Verilog之后,设计大规模cpLD/FpgA的又一种手段。硬件描述语言的结构

硬件描述语言实验题目:四位加法器实验 学院计算机科学与技术 学科门类xxxxxxxxxx 专业xxxxxxxxxx 学号xxxxxxxxxx 姓名宁剑 指导教师xxxx 20xx年x月x 日

硬件描述语言 一、实验题目:四位加法器 二、实验目的和要求 实验目的:进一步练习VHDL 语言设计工程的建立与仿真的步骤和方法、熟悉VHDL 语言三种描述方法。 实验要求:设计一个四位加法器,实体名称为“adder4_3”,其引脚及其功能如下表。 要求应用一位全加器(实验二中所实现的)按如下电路图通过结构描述方式构造四位加法器。 本实验用实验二“full_adder ”的实体作为元件,用port map 语句描述出来将下图的电路,实现四位加法器,并与实验三、实验四的加法器进行比较。 三、实验内容

1、打开altera 软件,建立一个名为adder4_3的vhdl 工程。 2、要求调用实验二中的一位加法器,按照如下电路图通过结构描述方式构造一个四位加法器。 3、编译及修改错误。 4、建立波形并仿真。 5、根据仿真结果分析设计是否正确。 附录:实验二中一位加法器的引脚及功能如下图: 设计一个一位加法器,实体名称为“full_adder ”,其引脚与功能如下表。 附录:实验三中四位加法器的引脚及功能如下图: 设计一个四位加法器,实体名称为“adder4”,其引脚与功能如下表。

附录:实验四中四位加法器的引脚及功能如下图: 设计一个四位加法器,实体名称为“adder4_2”,其引脚与功能如下表。 四、实验结果 部分代码截图: 通过此图我们得知编写的代码全部通过编译。

专科《硬件描述语言和数字系统设计》_试 卷_答案

专科《硬件描述语言和数字系统设计》 一、(共36题,共150分) 1. reg类型的数组通常用于描述存储器,reg [15: 0] MEM [0:1023];定义存储器字的位数为(2分) A.1024 B.16 C.16384 D.1040 .标准答案:B 2. 下列关于同步有限状态机的描述错误的是()(2分) A.状态变化只能发生在同一个时钟跳变沿; B.状态是否变化要根据输入信号,只要输入条件满足,就会立刻转入到下一个状态。 C.在时钟上升沿,根据输入信号的变化,确定电路状态 D.利用同步状态机可以设计出极其复杂灵活的数字逻辑电路系统 .标准答案:B 3. 关于如下描述,正确的说法是( ) (2分) A.这种描述是错误的 B.该电路不可综合 C.该电路不可综合,但生成的不是纯组合逻辑 D.以上说法都不对 .标准答案:D 4. 下列关于流水线的描述错误的是( ) (2分) A.流水线设计就是将组合逻辑系统地分割,并在各个部分(分级)之间插入寄存器,并暂存中间数据的方法; B.设计流水线目的是提高数据吞吐率 C.流水线缩短了在一个时钟周期内给的那个信号必须通过的通路长度,从而可以提高时钟频率 D.增加流水线长度可以节省更多延迟,流水线越长,首次延迟越大,系统频率就会降低。 .标准答案:D 5. 以下关于Top-Down的设计方法不正确的描述是( ) (2分)A.Top-Down的设计方法首先从系统设计入手; B.Top-Down设计中的系统总体仿真与所选工艺有关 C.Top-Down的设计方法从顶层进行功能划分和结构设计 D.自顶向下的设计方法可以早期发现结构上的错误 .标准答案:B 6. 在verilog中,下列哪些操作一定是单bit?()(2分) A.== B.^ C.> D.&& .标准答案:A,B,C,D 7. 下面哪些是verilog的关键字()(2分) A.input B.assign C.write D.module .标准答案:A,B,D 8. 全球主要的FPGA厂家有()(2分) A.Xilinx B.Altera C.Broadcom https://www.doczj.com/doc/a96598920.html,ttice .标准答案:A,B,D 9. 大规模数字逻辑设计原则,正确的说法有()(2分) A.异步设计原则 B.组合时序电路分开原则 C.面向RTL的原则 D.先电路后代码的原则 .标准答案:B,C 10. 下面有关SRAM,DRAM的叙述,正确的有()(2分) A.DRAM存储单元的结构比SRAM简单 B.DRAM比SRAM成本高 C.DRAM比SRAM速度快 D.DRAM要刷新,SRAM不刷新 .标准答案:A,D 11. 阻塞赋值与非阻塞赋值的差别及其各自的使用环境。(10分)标准答案:非阻塞(non-blocking)赋值语句(b