第三章 门 电 路

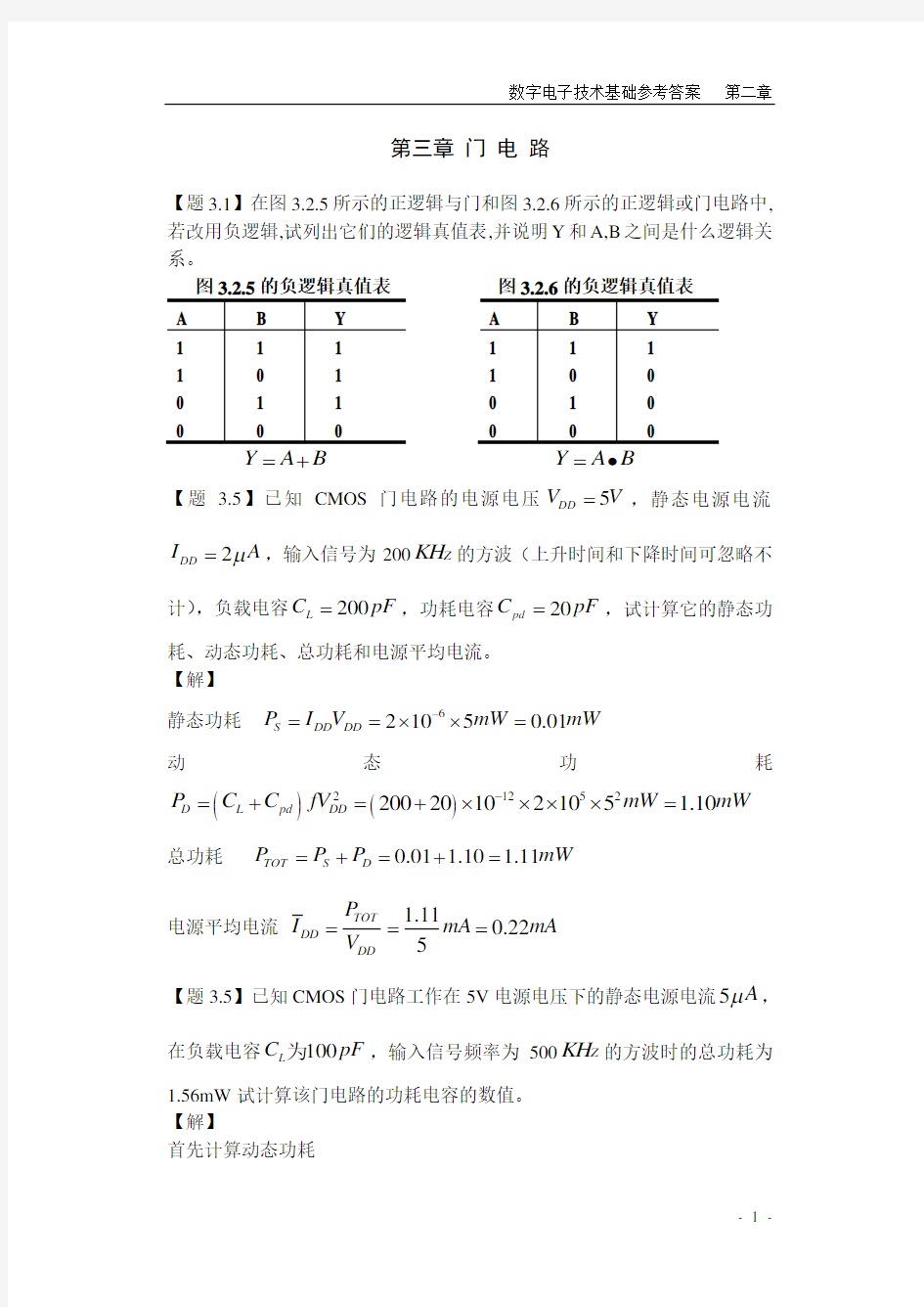

【题3.1】 在图3.2.5所示的正逻辑与门和图3.2.6所示的正逻辑或门电路中,若改用负逻辑,试列出它们的逻辑真值表,并说明Y 和A,B 之间是什么逻辑关系。

图3.2.5的负逻辑真值表

图3.2.6的负逻辑真值表

【题 3.5】已知CMOS 门电路的电源电压5DD V V =,静态电源电流

2DD I A μ=,输入信号为200Z KH 的方波(上升时间和下降时间可忽略不

计),负载电容200L C pF =,功耗电容20pd C pF =,试计算它的静态功耗、动态功耗、总功耗和电源平均电流。 【解】

静态功耗 6

21050.01S DD DD P I V mW mW -==??=

动态功耗

()()2

125220********* 1.10D L pd DD P C C fV mW mW -=+=+????=

总功耗 0.01 1.10 1.11TOT S D P P P mW =+=+= 电源平均电流 1.11

0.225

TOT DD DD

P I mA mA V =

=

= 【题3.5】已知CMOS 门电路工作在5V 电源电压下的静态电源电流5A μ,在负载电容100L C pF 为,输入信号频率为500Z KH 的方波时的总功耗为1.56mW 试计算该门电路的功耗电容的数值。 【解】

首先计算动态功耗

()31.565510 1.54D TOT S

TOT DD DD

P P P P I V mW mW

-=-=-=-??≈

根据()

2D L pd DD P C C fV =+得

312252

1.541010010135105D

pd L DD P C C F pF fV --???=

-=-?≈ ?????

【题3.7】 试分析图P3.7 中各电路的逻辑功能,写出输出逻辑函数式。

A

B C

DD Y

V DD

Y

(b)

A

A B

D

C INH

V DD

Y

图P3.7

【解】

(a )Y A B C =++ (b )Y A B C =?? (c )Y AB CD INH =+?

【题3.11】 在图P3.11的三极管开关电路中,若输入信号I v 的高、低电平分别为50IH IL V V V V ==、,试计算在图中标注的参数下能否保证I IH v V =时三极管饱和导通、I IL v V =时三极管可靠地截止?三极管的饱和导通压降

()0.1CE sat V V =,饱和导通内阻()20CE sat R =Ω。如果参数配合不当,则在电

源电压和C R 不变的情况下,应如何修改电路参数?

-10V +10V

图P3.11

o

v I

v

【解】利用戴维宁定理接至基极与发射极间的外电路化简为由等效电压E

v 和等效电阻E R 串联的回路,如图A3.11(a)所示。其中

10 5.118 5.1I E I v v v +=-

?+,18 5.1

3.9718 5.1

E R K K ?=Ω=Ω+

若10,v V =则 2.2,E v V =-故三极管处于截止状态,010v V =。 若15v V =,则 1.690.7

1.69,0.25,3.97

E BE E B E v V v V i mA mA R --==

==而临界饱和基极电流()

()

()

()

100.1

0.323010.02CC CE sat BS C CE sat V v I mA R R β--=

=

=?++。

可见,,B BS i I <三极管不饱和,为了使三极管在5I v V =时能饱和导通,可以减小1R 的阻值或用β值更大的三极管。

图A3.11(a)

b

e

V E

b

e

5.1K Ω

I

v E

R

【题3.12】 在图P3.12两个电路中,试计算当输入分别接0V ,5V 和悬空时输出电压0v 的数值,并指出三极管工作在什么状态。假定三极管导通以后

0.7BE v ≈V ,电路参数如图中所注。三极管的饱和导通压降()0.1CE sat V V =,

饱和导通内阻()20CE sat R =Ω。

-8V 图

P3.12

v O

v

【解】当输入断悬空时,用戴维宁定理可将接至与发射极间的外电路等效地化为由E V 和E R 串联的单回路,如图A3.12(b)所示。 其中

5818(3 4.7)

5(3 4.7) 1.1, 5.43 4.71818 4.73

E E V V V R K K +?+=-

?+==Ω=Ω

++++。所以 1.10.70.0745.4

B i mA mA -==。而

()()()

()50.10.0495020.02CC CE sat BS C CE sat V v I mA R R β--===?++ 故 ,B BS i I ?三极管

处于饱和导通状态,00.1CES V V V =≈。

图A3.12(a)

b

e

V E

b

e

E

R 3K

当输入端接有1V 时,仍将接至基极与发射极间的外电路简化为E V 与E R 串联的形式,如图A3.1(c)所示。其中

8 4.718

4.7, 3.74.718 4.718

I E I E v V v R K K +?=-

?=Ω=Ω++。

若10,V V =则 1.66,E V V =-三极管截止,05V V =。 若15V V =,则 2.30.7

2.3,0.43

3.7

E B V V i mA mA -

==

=。可见 ,B BS i I ? 三极管饱和导通,00.1CES V V V =≈。

图A3.12(c)

b

e

V E

b

e

E

R v

【题3.13】试分析图P3.13中各电路的逻辑功能,写出输出逻辑函数式。

CC

A

B

(a)

Y

(b)

A

B

Y

V CC

(c)

第三章集成逻辑门电路 一、选择题 1。三态门输出高阻状态时,()是正确的说法。 A.用电压表测量指针不动B.相当于悬空 C.电压不高不低 D.测量电阻指针不动 2. 以下电路中可以实现“线与”功能的有( ). A。与非门B.三态输出门 C.集电极开路门D。漏极开路门 3。以下电路中常用于总线应用的有( )。 A.TSL门 B。OC门 C.漏极开路门D.CMOS与非门 4。逻辑表达式Y=AB可以用()实现。 A.正或门 B.正非门 C。正与门D。负或门 5.TTL电路在正逻辑系统中,以下各种输入中( )相当于输入逻辑“1”。 A.悬空 B。通过电阻2.7kΩ接电源 C.通过电阻2.7kΩ接地D.通过电阻510Ω接地 6.对于TTL与非门闲置输入端的处理,可以( )。 A。接电源 B.通过电阻3kΩ接电源 C.接地 D.与有用输入端并联 7.要使TTL与非门工作在转折区,可使输入端对地外接电阻RI( ). A.>RON B。<ROFF C。ROFF<RI 3 逻辑门电路 3.1 MOS 逻辑门电路 3.1.2 求下列情况下TTL 逻辑门的扇出数:(1)74LS 门驱动同类门;(2)74LS 门驱动74ALS 系列TTL 门。 解:首先分别求出拉电流工作时的扇出数N OH 和灌电流工作时的扇出数N OL ,两者中的最小值即为扇出数。 从附录A 可查得74LS 系列电流参数的数值为I OH =0.4mA ,I OL =8mA ,I IH =0.02mA,I IL =0.4mA ;74ALS 系列输入电流参数的数值为I IH =0.02mA ,I IL =0.1mA ,其实省略了表示电流流向的符号。 (1) 根据(3.1.4)和式(3.1.5)计算扇出数 74LS 系列驱动同类门时,输出为高电平的扇出数 0.4200.02OH OH IH I mA N I mA === 输出为低电平的扇出数 8200.4OL OL IL I mA N I mA = == 所以,74LS 系列驱动同类门时的扇出数N O 为20。 (2) 同理可计算出74LS 系列驱动74ALS 系列时,有 0.4200.02OH OH IH I mA N I mA === 8800.1OL OL IL I mA N I mA = == 所以,74LS 系列驱动74ALS 系列时的扇出数N O 为20。 3.1.4 已知图题3.1.4所示各MOSFET 管的 T V =2V ,忽略电阻上的压降,试确定其工作状态(导通或截止)。 解:图题3.1.4(a )和(c )的N 沟道增强型MOS ,图题3.1.4(b )和(d )为P 沟道增强型MOS 。N 沟道增强型MOS 管得开启电压V T 为正。当GS V <V T 时,MOS 管处于截止状态;当GS V ≥V T ,且DS v ≥(GS V —V T )时,MOS 管处于饱和导通状态。 对于图题3.1.4(a ),GS V =5V ,DS v =5V ,可以判断该MOS 管处于饱和导通状态。对于图题 第三章逻辑门电路 u逻辑门电路的一般特性 u半导体二极管及其基本电路(模拟第三章) u半导体三极管BJT(模拟4.1) u MOS管(模拟5.1) u 基本逻辑门电路 u MOS逻辑门电路 u TTL逻辑门电路 u正负逻辑的概念 u逻辑门电路使用中的几个实际问题 本章的重点:一般特性;各种器件及门电路的外部特性。 内部工作原理作为了解内容。 条输入信号满足一定条件时,门开启, 开门状态:一、什么是门电路?——用来实现基本逻辑运算和复合逻辑运算的单元电路。(门电路是数字电路最为基本的逻辑单元) §3.1逻辑门电路的一般特性 件开关 允许信号通过。 关门状态:输入信号条件不满足,门关闭, 信号通不过。 与门、或门、非门、与非门、或非门、与或非门、异或门等。 门 因此门电路的输出和输入之间存在着一定的逻辑关系。不同的门电路,输出与输入之间的逻辑关系也不同,如: 二、数字集成电路的分类 1.按工艺结构区分: ?54/74系列?54H/74H 系列?54LS/74LS 系列TTL 电路逻辑门电路的一般特性 ?54AS/74AS 系列?54ALS/74ALS 系列IIL 电路ECL 电路HTL 电路CMOS 电路NMOS 电路PMOS 电路 BiMOS 型 MOS 型双极型 ?54HC/74HC 系列?54HCT/74HCT 系列?4000系列 ?54LVC/74LVC 系列 ?54VHC/74VHC 系列 各种系列逻辑门: 1)74TTL / 54TTL 标准TTL 2)74HTTL / 54HTTL 高速TTL 3)74STTL / 54STTL 肖特基TTL 4)74LSTTL / 54LSTTL 低功耗肖特基 TTL 10mW/ 10ns 22mW/ 6ns 19mW/ 3ns 2mW/ 9.5ns 5)74ALSTTL / 54ALSTTL 先进低功耗肖特基TTL 6)74ASTTL / 54ASTTL 先进肖特基TTL 7)74FTTL / 54FTTL 快速TTL 1mW/ 3.5ns 8mW/ 3ns 4mW/ 3.4ns 8)CC4×××× 标准CMOS 9)74HC / 54HC 高速CMOS 10)74HCT / 54HCT 与TTL 逻辑电平兼容的HC 第3章-门电路-课后答案 - 2 - 第三章 门 电 路 【题3.1】 在图3.2.5所示的正逻辑与门和图3.2.6所示的正逻辑或门电路中,若改用负逻辑,试列出它们的逻辑真值表,并说明Y 和A,B 之间是什么逻辑关系。 图3.2.5的负逻辑真值表 图3.2.6的负逻辑真值表 【题3.5】已知CMOS 门电路的电源电压5DD V V =,静态电源电流2DD I A μ=,输入信 号为200Z KH 的方波(上升时间和下降时间可忽略不计),负载电容200L C pF =,功 耗电容20pd C pF =,试计算它的静态功耗、 - 3 - 动态功耗、总功耗和电源平均电流。 【解】 静态功耗 621050.01S DD DD P I V mW mW -==??= 动态 功 耗 ()()2 12 5 2 20020102105 1.10D L pd DD P C C fV mW mW -=+=+????= 总功耗 0.01 1.10 1.11TOT S D P P P mW =+=+= 电源平均电流 1.11 0.225 TOT DD DD P I mA mA V = = = 【题3.5】已知CMOS 门电路工作在5V 电源电压下的静态电源电流5A μ,在负载电容100L C pF 为,输入信号频率为500Z KH 的 方波时的总功耗为1.56mW 试计算该门电路的功耗电容的数值。 【解】 首先计算动态功耗 ()31.565510 1.54D TOT S TOT DD DD P P P P I V mW mW -=-=-=-??≈ 根据()2 D L pd DD P C C fV =+得 312252 1.541010010135105D pd L DD P C C F pF fV --???= -=-?≈ ????? 第三章组合逻辑电路 第一节重点与难点 一、重点: 1.组合电路的基本概念 组合电路的信号特点、电路结构特点以及逻辑功能特点。 2.组合电路的分析与设计 组合电路分析是根据已知逻辑图说明电路实现的逻辑功能。 组合电路设计是根据给定设计要求及选用的器件进行设计,画出逻辑图。如果选用小规模集成电路SSI,设计方法比较规范且容易理解,用SSI设计是读者应掌握的最基本设计方法。由于设计电路由门电路组成,所以使用门的数量较多,集成度低。 若用中规模集成电路MSI进行设计,没有固定的规则,方法较灵活。 无论是用SSI或MSI设计电路,关键是将实际的设计要求转换为一个逻辑问题,即将文字描述的要求变成一个逻辑函数表达式。 3.常用中规模集成电路的应用 常用中规模集成电路有加法器、比较器、编码器、译码器、数据选择器和数据分配器等,重要的是理解外部引脚功能,能在电路设计时灵活应用。 4.竞争冒险现象 竞争冒险现象的产生原因、判断是否存在竞争冒险现象以及如何消除。 二、难点: 无论是用SSI还是用MSI设计电路,首先碰到的是如何将设计要求转换为逻辑问题,得到明确的真值表,这一步既是重点又是难点。总结解决这一难点的方法如下: (1)分析设计问题的因果关系,分别确定输入变量、输出变量的个数及其名称。 (2)定义逻辑变量0、1信号的含义。无论输入变量、输出变量均有两个状态0、1,这两个状态代表的含义由设计者自己定义。 (3)再根据设计问题的因果关系以及变量定义,列出真值表。 2.常用组合电路模块的灵活应用 同样的设计要求,用MSI设计完成后,所得的逻辑电路不仅与所选芯片有关,而且还与设计者对芯片的理解及灵活应用能力有关。读者可在下面的例题和习题中体会。 3.硬件描述语言VHDL的应用 VHDL的应用非常灵活,同一个电路问题可以有不同的描述方法,初学者可以先仔细阅读已有的程序实例,再自行设计。 三、考核题型与考核重点 1.概念与简答 题型1为填空、判断和选择; 题型2为叙述基本概念与特点。 建议分配的分数为3~6分。 2.综合分析与设计 题型1为根据已知电路分析逻辑功能; 题型2为根据给定的逻辑问题,设计出满足要求的逻辑电路。 建议分配的分数为6~12分。 第二节思考题题解 第三章 门 电 路 【题3.1】 在图3.2.5所示的正逻辑与门和图3.2.6所示的正逻辑或门电路中,若改用负逻辑,试列出它们的逻辑真值表,并说明Y 和A,B 之间是什么逻辑关系。 图3.2.5的负逻辑真值表 图3.2.6的负逻辑真值表 【题 3.5】已知CMOS 门电路的电源电压5DD V V =,静态电源电流 2DD I A μ=,输入信号为200Z KH 的方波(上升时间和下降时间可忽略不 计),负载电容200L C pF =,功耗电容20pd C pF =,试计算它的静态功耗、动态功耗、总功耗和电源平均电流。 【解】 静态功耗 6 21050.01S D D D D P I V m W m W -==??= 动态功耗 ()()2125220020102105 1.10D L pd DD P C C fV mW mW -=+=+????= 总功耗 0.01 1.10 1.11T O T S D P P P m W =+=+= 电源平均电流 1.11 0.225 TOT DD DD P I mA mA V = = = 【题3.5】已知CMOS 门电路工作在5V 电源电压下的静态电源电流5A μ,在负载电容100L C pF 为,输入信号频率为500Z KH 的方波时的总功耗为1.56mW 试计算该门电路的功耗电容的数值。 【解】 首先计算动态功耗 ()31.565510 1.54D TOT S TOT DD DD P P P P I V mW mW -=-=-=-??≈ 根据() 2 D L pd DD P C C fV =+得 312252 1.541010010135105D pd L DD P C C F pF fV --???= -=-?≈ ????? 【题3.7】 试分析图P3.7 中各电路的逻辑功能,写出输出逻辑函数式。 A B C DD Y V DD Y (b) A 第2章 逻辑门电路 2.1解题指导 【例2-1】 试用74LS 系列逻辑门,驱动一只V D =1.5V ,I D =6mA 的发光二极管。 解:74LS 系列与之对应的是T4000系列。与非门74LS00的I OL 为4mA ,不能驱动I D =6mA 的发光二极管。集电极开路与非门74LS01的I OL 为6mA ,故可选用74LS01来驱动发光二极管,其电路如图所示。限流电阻R 为 Ω =--=--=k V V V R OL D CC 5.065.05.156 【例2-2】 试分析图2-2所示电路的逻辑功能。 解:由模拟开关的功能知:当A =1时,开关接通。传输门导通时,其导通电阻小于1k Ω,1k Ω与200k Ω电阻分压,输出电平近似为0V 。 而A =0时,开关断开,呈高阻态。109Ω以上的电阻与200k Ω电阻分压,输出电平近似为V DD 。 故电路实现了非逻辑功能。 【例2-3】 试写出由TTL 门构成的逻辑图如图2-3所示的输出F 。 & ≥1 F ≥1 A B 图2-3 例2-3门电路 解:由TTL 门输入端悬空逻辑上认为是1可写出 【例2-4】 试分别写出由TTL 门和CMOS 门构成的如图2-4所示逻辑图的表达式或逻 辑值。 B F 图2-4 例2-4门电路 解:由TTL 门组成上面逻辑门由于10k Ω大于开门电阻R ON ,所以,无论 A 、B 为何值 。 由CMOS 门组成上面逻辑门由于CMOS 无开门电阻和关门电阻之说,所以, 。 2.2 例题补充 2-1 一个电路如图2-5所示,其三极管为硅管,β=20,试求:ν1小于何值时,三极管T 截止,ν1大于何值时,三极管T 饱和。 解:设v BE =0V 时,三极管T 截止。T 截止时,I B =0。此时 10) 10(020I --= -v v I =2V T 临界饱和时,v CE =0.7V 。此时 V CC v I v O +10V -V BB V V V 0200 11 DD F ≈+=DD DD 44 DD 599F 210101021010V V V V ≈+≈?+=A B A F =++?=110≡F AB F = 第三章门电路 第三章门电路 3.1 概述 TTL电路问世几十年来,经过电路结构的不断改进和集成工艺的逐步完善,至今仍广泛应用,几乎占据着数字集成电路领域的半壁江山。 把若干个有源器件和无源器件及其连线,按照一定的功能要求,制做在同一块半导体基片上,这样的产品叫集成电路。若它完成的功能是逻辑功能或数字功能,则称为逻辑集成电路或数字集成电路。最简单的数字集成电路是集成逻辑门。 集成逻辑门,按照其组成的有源器件的不同可分为两大类:一类是双极性晶体管逻辑门;另一类是单极性绝缘栅场效应管逻辑门,简称MOS门。 双极性晶体管逻辑门主要有TTL门(晶体管-晶体管逻辑门)、ECL门(射极耦合逻辑门)和I2L门(集成注入逻辑门)等。 单极性MOS门主要有PMOS门(P沟道增强型MOS 管构成的逻辑门)、NMOS门(N沟道增强型MOS管构成的逻辑门)和CMOS门(利用PMOS管和NMOS管构成的互补电路构成的门电路,故又叫做互补MOS门 门电路:实现基本运算、复合运算的单元电路,如与门、与非门、或门…… 门电路中以高/低电平表示逻辑状态的1/0 获得高、低电平的基本原理如图1所示。 图1 高/低电平都允许有一定的变化范围如图2所示。 正逻辑:高电平表示1,低电平表示0 负逻辑:高电平表示0,低电平表示1 图 2 3.2 半导体二极管门电路 二极管的结构如图3所示: PN结+ 引线+ 封装构成 图3 3.2.1二极管的开关特性 如图4,高电平:V IH=V CC,低电平:V IL=0 图4 3.2.2二极管与门 最简单的与门可以用二极管和电阻组成,图5是有两个输入端的与门电路。图中A,B为两个输入变量,Y为输出变量。 图5 二极管与门电路及图形符号 设VCC=5V,A,B输入端的高、低电平分别为VIH=3V,VIL=0V,二极管D1,D2的正向导通压降VDF=0.7V。由图可见,A,B当中只要有一个是低电平0V,则必有一个二极管导通,使Y=0.7V。只有A,B同时为高电平3V时,Y才为3.7V。将输出与输入逻辑电平的关系列表,即得如表1 电路的逻辑电平表电路的真值表 如果规定3V以上为高电平,用逻辑1表示,0.7V 第三章集成逻辑门 一、选择题 1. 三态门输出高阻状态时,是正确的说法。 A.用电压表测量指针不动 B.相当于悬空 C.电压不高不低 D.测量电阻指针不动 2. 以下电路中可以实现“线与”功能的有。 A.与非门 B.三态输出门 C.集电极开路门 D.漏极开路门 3.以下电路中常用于总线应用的有。 A.T S L门 B.O C门 C.漏极开路门 D.C M O S与非门 4.逻辑表达式Y=A B可以用实现。 A.正或门 B.正非门 C.正与门 D.负或门 5.T T L电路在正逻辑系统中,以下各种输入中相当于输入逻辑“1”。 A.悬空 B.通过电阻 2.7kΩ接电源 C.通过电阻 2.7kΩ接地 D.通过电阻510Ω接地 6.对于T T L与非门闲置输入端的处理,可以。 A.接电源 B.通过电阻3kΩ接电源 C.接地 D.与有用输入端并联7.要使T T L与非门工作在转折区,可使输入端对地外接电阻R I。 A.>R O N B.<R O F F C.R O F F<R I<R O N D.>R O F F 8.三极管作为开关使用时,要提高开关速度,可。 A.降低饱和深度 B.增加饱和深度 C.采用有源泄放回路 D.采用抗饱和三极管 9.C M O S数字集成电路与T T L数字集成电路相比突出的优点是。 A.微功耗 B.高速度 C.高抗干扰能力 D.电源范围宽 10.与C T4000系列相对应的国际通用标准型号为。 A.C T74S肖特基系列 B.C T74L S低功耗肖特基系列 C.C T74L低功耗系列 D.C T74H高速系列 二、判断题(正确打√,错误的打×) 1.TTL与非门的多余输入端可以接固定高电平。() 2.当TTL与非门的输入端悬空时相当于输入为逻辑1。() 3.普通的逻辑门电路的输出端不可以并联在一起,否则可能会损坏器件。() 4.两输入端四与非门器件74LS00与7400的逻辑功能完全相同。() 5.CMOS或非门与TTL或非门的逻辑功能完全相同。() 6.三态门的三种状态分别为:高电平、低电平、不高不低的电压。() 7.TTL集电极开路门输出为1时由外接电源和电阻提供输出电流。() 8.一般TTL门电路的输出端可以直接相连,实现线与。() 第三章(组合逻辑电路)作业及答案 1、写出图3-1所示组合逻辑电路中输入输出的逻辑关系式和真值表。 图3-1:组合逻辑电路逻辑图 解:(1)C A A AC B A Y +=++=1 (2)D B C B A CD B A CD B A D BD CD A B A Y ++=++=+=++=)(2 2、试分析图3-2所示组合逻辑电路,写出其逻辑函数表达式。若设S 1﹑S 0为功能控制信号,A ﹑B 为输入信号,L 为输出,说明当S 1﹑S 0取不同信号值时,电路所实现的逻辑功能。 图3-2:组合逻辑电路逻辑图 3、试用与门、或门和非门,或者与门、或门和非门的组合来实现如下各逻辑函数关系,画出相应的逻辑电路图。 (1)1 Y AB BC =+ 1 (2)2Y A C B =+() (3)3 Y ABC B EF G =++() A B C . Y2 A B C . E F G .. . 4、试用门电路设计4线-2线优先编码器,输入、输出信号都是高电平有效,要求任一按键按下时,G S 为1,否则G S =0;还要求没有按键按下时,E O 信号为1,否则为0。 为S,输出信号为Y,要求写出真值表、逻辑函数表达式和画出逻辑电路图。 6、某公司3条装配线各需要100kW电力,采用两台发电动机供电,一台100kW,另外一台是200kW,3条装配线不同时开工,试设计一个发电动机控制电路, 可以按照需求启动发电动机以达到节电的目的。 7、图3-3是由3线/8线译码器74LS138和与非门构成的组合逻辑电路,试写出P1和P2的逻辑表达式,并列出真值表,说明其逻辑功能。 BIN/OCT 0 1 20 1 2 3 4 5 6 7 B A C 1 0 074LS138 P1 P2 第3章逻辑门电路 3.1 概述 逻辑门电路:用以实现基本和常用逻辑运算的电子电路。简称门电路。用逻辑 1和o 分别来 表示电子电路中的高、低电平的逻辑赋值方式,称为正逻辑,目前在数字技术中,大都采用正逻 辑工作;若用低、高电平来表示,则称为负逻辑。本课程采用正逻辑。 获得高、低电平的基本方法:利用半导体开关元件的导通、截止(即开、关)两种工作状态。 在数字集成电路的发展过程中,同时存在着两种类型器件的发展。一种是由三极管组成的双极 型集成电路,例如晶体管-晶体管逻辑电路(简称 TTL 电路)及射极耦合逻辑电路(简称 ECL 电 路)。另一种是由MOS 管组成的单极型集成电路, 例如N-MOS 逻辑电路和互补 MOS (简称COMS ) 逻辑电路。 3.2 分立元件门电路 3.3.1二极管的开关特性 性NPN 型三极管截止、放大、饱和 3种工作状态的特点 工作状态 截 止 放 大 饱 和 条 件 i B = 0 0 v i B < I BS i B > I BS 工 作 吐 偏置情况 特 占 发射结反偏 集电结反偏 U BE <0, U BC <0 发射结正偏 集电结反偏 U BE >0, U BC <0 发射结正偏 集电结正偏 U BE >0, U BC >0 A ID (mA) 4- - / UD (V) 0 5 0.7 伏安特性二极管导通。 气W )V 时的等效电路 U]-0V 时,二极管截止, 如同开关断开,W 0 = OV S 屮弋时的等奴电路 a 3 = ?二极管导通,如 ^|0.7V 的电压源.% = 二极管的反向恢复时间限制了二极管的开关速度, 3.2.2 三极管的开关特 3组合逻辑电路习题解答 1 自我检测题 [T3.1]组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与电路以前的输入信号 无关 。 [T3.2]在组合逻辑电路中,当输入信号改变状态时,输出端可能出现虚假过渡干扰脉冲的现象称为 竞争冒险 。 [T3.3]8线—3线优先编码器74LS148的优先编码顺序是7I 、6I 、5I 、…、0I ,输出2Y 1Y 0Y 。输入输出均为低电平有效。当输入7I 6I 5I …0I 为11010101时,输出2Y 1Y 0Y 为 010 。 [T3.4]3线—8线译码器74LS138处于译码状态时,当输入A 2A 1A 0=001时,输出07Y ~Y = 11111101 。 [T3.5]能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。 [T3.6]实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫 数据分配器 。 [T3.7]根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。 [T3.8]一位数值比较器,输入信号为两个要比较的一位二进制数,用A 、B 表示,输出信号为比较结果:Y (A >B ) 、Y (A =B )和Y (A <B ),则Y (A >B )的逻辑表达式为B A 。 [T3.9]下列电路中,不属于组合逻辑电路的是 。 (A )译码器 (B )全加器 (D )编码器 [T3.10]译码器74LS138的使321为 时,处于允许状态。 (A )011 (B )100 (C )101 (D )010 [T3.11]在二进制译码器中,若输入有4位代码,则输出有 个信号。 (A )2 (B )4 (C )8 (D )16 [T3.12]组合逻辑电路中的险象是由于 引起的。 (A )电路未达到最简 (B )电路有多个输出 (C )电路中的时延 (D )逻辑门类型不同 [T3.13]用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的? (A )在输出级加正取样脉冲 (B )在输入级加正取样脉冲 (C )在输出级加负取样脉冲 (D )在输入级加负取样脉冲 [T3.14]比较两位二进制数A=A 1A 0和B=B 1B 0,当A >B 时输出F =1,则F 表达式是 。 (A )B A F = (B )0101B B A A F ++= (D )0011B A B A F ++= 数字电子技术基础第三章习题答案 3-1如图3-63a~d所示4个TTL门电路,A、B端输入的波形如图e所示,试分别画出F1、F2、F3和F4的波形图。 略 3-2电路如图3-64a所示,输入A、B的电压波形如图3-64b所示,试画出各个门电路输出端的电压波形。 略 3-3 答: F与 (2)图 A B F 000 010 100 111 F与A、B之间相当于正逻辑的“与”操作。 3-4试说明能否将与非门、或非门、异或门当做反相器使用?如果可以,各输入端应如何连接? 答:三种门经过处理以后均可以实现反相器功能。(1)与非门:将多余输入端接至高电平或与另一端并联;(2)或非门:将多余输入端接至低电平或与另一端并联;(3)异或门:将另一个输入端接高电平。 3-5为了实现图3-65所示的各TTL 门电路输出端所示的逻辑关系,请合理地将多余的输入端进行处理。 答:a )多余输入端可以悬空,但建议接高电平或与另两个输入端的一端相连; b)多余输入端接低电平或与另两个输入端的一端相连; c)未用与门的两个输入端至少一端接低电平,另一端可以悬空、接高电平或接低电平; d )未用或门的两个输入端悬空或都接高电平。 3-6如要实现图3-66所示各TTL 门电路输出端所示的逻辑关系,请分析电路输入端的连接是否正确?若不正确,请予以改正。 答:a )不正确。输入电阻过小,相当于接低电平,因此将?50提高到至少2K ?。b)不正确。第三脚V CC 应该接低电平。 c )不正确。万用表一般内阻大于2K ?,从而使输出结果0。因此多余输入端应接低电平,万用表只能测量A 或B 的输入电压。 3-7(修改原题,图中横向电阻改为6k ?,纵向电阻改为3.5k ?,β=30改为β=80)为了提高TTL 与非门的带负载能力,可在其输出端接一个NPN 晶体管,组成如图3-67所示的开关电路。当与非门输出高电平V OH =3.6V 时,晶体管能为负载提供的最大电流是多少? 答:如果输出高电平,则其输出电流为(3.6-0.7)/6=483u A ,而与非门输出高电平时最大负载电流是400u A ,因此最大电流L I (4000.7/3.5)8016mA =?×=。 [题3.1] 分析P3.1电路的逻辑功能,写出Y 1、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。 答案: 12()Y ABC A B C AB AC BC ABC ABC Y AB BC AC =+++?++=++=++ 由真值表可见,这是一个全加器电路。A 、B 、C 为加数、被加数和来自低位的进位, Y 1是和,Y 2是进位输出。 [题3.3] 用或非门设计四变量的多数表决电路。当输入变量A 、B 、C 、D 有3个或3个以上为1时输出为1,输入为其它状态时输出为0。 答案: Y ABCD ABCD ABCD ABCD ABCD ABC ABD ACD BCD ABC ABD ACD BCD =++++=+++=+++ [题3.7] 某医院有一、二、三、四号病室4间,每室设有呼叫按钮,同时在护士值班室内对应地装有一号、二号、三号、四号4个指示灯。 现要求当一号病室的按钮按下时,无论其它病室的按钮是否按下,只有一号灯亮。当一号病室的按钮没有按下而二号病室的按钮按下时,无论三号、四号病室的按钮是否按下,只有二号灯亮。当一号、二号病室的按钮没有按下而三号病室的按钮按下时,无论四号病室的按钮是否按下,只有三号灯亮。只有在一号、二号、三号病室的按钮均未按下而四号病室的按钮按下时,四号灯才亮。试用优先编码器74LS148和门电路设计满足以上控制要求的逻辑电路,给出控制四个指示灯状态的高、低电平信号。 答案: 以1234A A A A 、 、、分别表示按下一、二、三、四号病室按钮给出的低电平信号,以1234Y Y Y Y 、、、表示一、二、 三、四号灯亮的信号。电路如图A3.7。 [题3.8] 写出图P3.8中Z 1、Z 2、Z 3的逻辑函数式,并化简为最简的与-或表达式。译码器74LS42的逻辑图见图3.3.10。 答案: 1147Z Y Y Y M N PQ M N PQ M NPQ ==++ 2258Z Y Y Y M NPQ M N PQ M N PQ ==++ 3369Z Y Y Y M NPQ M NPQ M N PQ ==++ [题3.10] 试画出用3线-8线译码器74LS138(见图3.3.8)和门电路产生如下多输出 第三章 门 电 路 【题3.1】 在图3.2.5所示的正逻辑与门和图3.2.6所示的正逻辑或门电路中,若改用负逻辑,试列出它们的逻辑真值表,并说明Y 和A,B 之间是什么逻辑关系。 图3.2.5的负逻辑真值表 图3.2.6的负逻辑真值表 【题 3.5】已知CMOS 门电路的电源电压5DD V V =,静态电源电流 2DD I A μ=,输入信号为200Z KH 的方波(上升时间和下降时间可忽略不 计),负载电容200L C pF =,功耗电容20pd C pF =,试计算它的静态功耗、动态功耗、总功耗和电源平均电流。 【解】 静态功耗 6 21050.01S DD DD P I V mW mW -==??= 动态功耗 ()()2 125220********* 1.10D L pd DD P C C fV mW mW -=+=+????= 总功耗 0.01 1.10 1.11TOT S D P P P mW =+=+= 电源平均电流 1.11 0.225 TOT DD DD P I mA mA V = = = 【题3.5】已知CMOS 门电路工作在5V 电源电压下的静态电源电流5A μ,在负载电容100L C pF 为,输入信号频率为500Z KH 的方波时的总功耗为1.56mW 试计算该门电路的功耗电容的数值。 【解】 首先计算动态功耗 ()31.565510 1.54D TOT S TOT DD DD P P P P I V mW mW -=-=-=-??≈ 根据() 2D L pd DD P C C fV =+得 312252 1.541010010135105D pd L DD P C C F pF fV --???= -=-?≈ ????? 【题3.7】 试分析图P3.7 中各电路的逻辑功能,写出输出逻辑函数式。 A B C DD Y V DD Y (b) A 3 逻辑门电路 MOS 逻辑门电路 3.1.2 求下列情况下TTL 逻辑门的扇出数:(1)74LS 门驱动同类门;(2)74LS 门驱动74ALS 系列TTL 门。 解:首先分别求出拉电流工作时的扇出数N OH 和灌电流工作时的扇出数N OL ,两者中的最小值即为扇出数。 从附录A 可查得74LS 系列电流参数的数值为I OH =,I OL =8mA ,I IH =,I IL =;74ALS 系列输入电流参数的数值为I IH =,I IL =,其实省略了表示电流流向的符号。 (1) 根据(3.1.4)和式()计算扇出数 74LS 系列驱动同类门时,输出为高电平的扇出数 0.4200.02OH OH IH I mA N I mA === 输出为低电平的扇出数 8200.4OL OL IL I mA N I mA = == 所以,74LS 系列驱动同类门时的扇出数N O 为20。 (2) 同理可计算出74LS 系列驱动74ALS 系列时,有 0.4200.02OH OH IH I mA N I mA === 8800.1OL OL IL I mA N I mA = == 所以,74LS 系列驱动74ALS 系列时的扇出数N O 为20。 3.1.4 已知图题所示各MOSFET 管的 T V =2V ,忽略电阻上的压降,试确定其工作状态(导 通或截止)。 解:图题3.1.4(a )和(c )的N 沟道增强型MOS ,图题(b )和(d )为P 沟道增强型MOS 。N 沟道增强型MOS 管得开启电压V T 为正。当GS V <V T 时,MOS 管处于截止状态;当GS V ≥V T ,且DS v ≥(GS V —V T )时,MOS 管处于饱和导通状态。 一、选择题 1. 三态门输出高阻状态时,()是正确的说法。 A.用电压表测量指针不动 B.相当于悬空 C.电压不高不低 D.测量电阻指针不动 2. 以下电路中可以实现“线与”功能的有()。 A.与非门 B.三态输出门 C.集电极开路门 D.漏极开路门 3.以下电路中常用于总线应用的有()。 门门 C. 漏极开路门与非门 4.逻辑表达式Y=AB可以用()实现。 A.正或门 B.正非门 C.正与门 D.负或门 5.TTL电路在正逻辑系统中,以下各种输入中()相当于输入逻辑“1”。 A.悬空 B.通过电阻Ω接电源 C.通过电阻Ω接地 D.通过电阻510Ω接地 6.对于TTL与非门闲置输入端的处理,可以()。 A.接电源 B.通过电阻3kΩ接电源 C.接地 D.与有用输入端并联 7.要使TTL与非门工作在转折区,可使输入端对地外接电阻RI()。 A.>RON B.<ROFF <RI<RON D.>ROFF 。( ).三极管作为开关使用时,要提高开关速度,可8. A.降低饱和深度 B.增加饱和深度 C.采用有源泄放回路 D.采用抗饱和三极管 9.CMOS数字集成电路与TTL数字集成电路相比突出的优点是()。 A.微功耗 B.高速度 C.高抗干扰能力 D.电源范围宽 10.与CT4000系列相对应的国际通用标准型号为()。 肖特基系列 B. CT74LS低功耗肖特基系列 74L低功耗系列 D. CT74H高速系列 11.电路如图(a),(b)所示,设开关闭合为1、断开为0;灯亮为1、灯灭为0。 F 对开关A、B、C的逻辑函数表达式()。 A. B. C. 12.某TTL反相器的主要参数为IIH=20μA;IIL=mA;IOH=400μA;水IOL =14mA,带同样的门数()。 A.20 B.200 C.10 D.100 13.在TTL门电路的一个输入端与地之间开路,则相当于在该输入端输入()。 A.高阻态 B.高电平 C.低电平第3章-逻辑门电路

第三章 逻辑门电路的一般特性(1)2015 [兼容模式] (1)

第3章-门电路-课后答案

数字电子技术基本第三版第三章答案解析

第3章_门电路 课后答案

第三章集成逻辑门电路例题补充

第三章 门电路

数字电路与逻辑设计习题-3第三章集成逻辑门

数字电子技术第三章(组合逻辑电路)作业及答案

数字电路教案-阎石第三章逻辑门电路

数字电路_第三章答案

课后习题答案 第3章 门电路

《数字电子技术基础》第三章习题(阎石主编,第四版)

第3章门电路课后答案

第3章-逻辑门电路

数字电路第三章习题与答案