数字逻辑第六章

- 格式:pdf

- 大小:884.99 KB

- 文档页数:25

数字逻辑知到章节测试答案智慧树2023年最新江西理工大学第一章测试1.四位二进制数的最大数是()。

参考答案:11112.将数1101.11B转换为十六进制数为()。

参考答案:D.CH3.十数制数2006.375转换为二进制数是()。

参考答案:11111010110.0114.将十进制数130转换为对应的八进制数()。

参考答案:2025.四位二进制数0111加上0011等于1010。

()参考答案:对6.16进制数2B等于10进制数()。

参考答案:437.16进制数3.2等于2进制数()。

参考答案:11.0018.十进制数9比十六进制数9小。

()参考答案:错9.与八进制数(47.3)8等值的数为()参考答案:(100111.011)2;(27.6)1610.有符号数10100101的补码是()。

参考答案:1101101111.[X]补+[Y]补=()。

参考答案:[X+Y]补12.十进制数7的余3码是()。

参考答案:101013.以下代码中为无权码的为()。

参考答案:余三码;格雷码14.格雷码具有任何相邻码只有一位码元不同的特性。

()参考答案:对第二章测试1.逻辑函数的表示方法中具有唯一性的是()。

参考答案:卡诺图;真值表2.在何种输入情况下,“与非”运算的结果是逻辑0。

()参考答案:全部输入是13.逻辑变量的取值1和0可以表示()。

参考答案:电位的高、低;真与假;开关的闭合、断开;电流的有、无4.A’+B’等于()。

参考答案:(AB)’5.以下表达式中符合逻辑运算法则的是()。

参考答案:A+1=16.逻辑函数两次求反则还原,逻辑函数的对偶式再作对偶变换也还原为它本身。

()参考答案:对7.求Y=A(B+C)+CD的对偶式是()。

参考答案:(A+BC)(C+D)8.已知逻辑函数Y的波形图如下图,该逻辑函数式是Y=()。

参考答案:A’BC+AB’C+ABC’9.任意函数的全体最大项之积为1。

()参考答案:错10.下列哪些项属于函数Y(A、B、C、D)=(A’B+C)’D+AB’C’的最小项()。

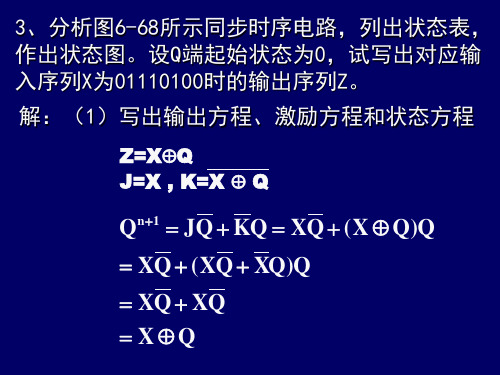

《数字逻辑教案》word版第一章:数字逻辑基础1.1 数字逻辑概述介绍数字逻辑的基本概念和特点解释数字逻辑在计算机科学中的应用1.2 逻辑门介绍逻辑门的定义和功能详细介绍与门、或门、非门、异或门等基本逻辑门1.3 逻辑函数解释逻辑函数的概念和作用介绍逻辑函数的表示方法,如真值表和逻辑表达式第二章:数字逻辑电路2.1 逻辑电路概述介绍逻辑电路的基本概念和组成解释逻辑电路的功能和工作原理2.2 逻辑电路的组合介绍逻辑电路的组合方式和连接方法解释组合逻辑电路的输出特点2.3 逻辑电路的时序介绍逻辑电路的时序概念和重要性详细介绍触发器、计数器等时序逻辑电路第三章:数字逻辑设计3.1 数字逻辑设计概述介绍数字逻辑设计的目标和方法解释数字逻辑设计的重要性和应用3.2 组合逻辑设计介绍组合逻辑设计的基本方法和步骤举例说明组合逻辑电路的设计实例3.3 时序逻辑设计介绍时序逻辑设计的基本方法和步骤举例说明时序逻辑电路的设计实例第四章:数字逻辑仿真4.1 数字逻辑仿真概述介绍数字逻辑仿真的概念和作用解释数字逻辑仿真的方法和工具4.2 组合逻辑仿真介绍组合逻辑仿真的方法和步骤使用仿真工具进行组合逻辑电路的仿真实验4.3 时序逻辑仿真介绍时序逻辑仿真的方法和步骤使用仿真工具进行时序逻辑电路的仿真实验第五章:数字逻辑应用5.1 数字逻辑应用概述介绍数字逻辑应用的领域和实例解释数字逻辑在计算机硬件、通信系统等领域的应用5.2 数字逻辑在计算机硬件中的应用介绍数字逻辑在中央处理器、存储器等计算机硬件部件中的应用解释数字逻辑在计算机指令执行、数据处理等方面的作用5.3 数字逻辑在通信系统中的应用介绍数字逻辑在通信系统中的应用实例,如编码器、解码器、调制器等解释数字逻辑在信号处理、数据传输等方面的作用第六章:数字逻辑与计算机基础6.1 计算机基础概述介绍计算机的基本组成和原理解释计算机硬件和软件的关系6.2 计算机的数字逻辑核心讲解CPU内部的数字逻辑结构详细介绍寄存器、运算器、控制单元等关键部件6.3 计算机的指令系统解释指令系统的作用和组成介绍机器指令和汇编指令的概念第七章:数字逻辑与数字电路设计7.1 数字电路设计基础介绍数字电路设计的基本流程解释数字电路设计中的关键概念,如时钟频率、功耗等7.2 数字电路设计实例分析简单的数字电路设计案例讲解设计过程中的逻辑判断和优化7.3 数字电路设计工具与软件介绍常见的数字电路设计工具和软件解释这些工具和软件在设计过程中的作用第八章:数字逻辑与数字系统测试8.1 数字系统测试概述讲解数字系统测试的目的和方法解释测试在保证数字系统可靠性中的重要性8.2 数字逻辑测试技术介绍逻辑测试的基本方法和策略讲解测试向量和测试结果分析的过程8.3 故障诊断与容错设计解释数字系统中的故障类型和影响介绍故障诊断方法和容错设计策略第九章:数字逻辑在现代技术中的应用9.1 数字逻辑与现代通信技术讲解数字逻辑在现代通信技术中的应用介绍数字调制、信息编码等通信技术9.2 数字逻辑在物联网技术中的应用解释数字逻辑在物联网中的关键作用分析物联网设备中的数字逻辑结构和功能9.3 数字逻辑在领域的应用讲述数字逻辑在领域的应用实例介绍逻辑推理、神经网络等技术中的数字逻辑基础第十章:数字逻辑的未来发展10.1 数字逻辑技术的发展趋势分析数字逻辑技术的未来发展方向讲解新型数字逻辑器件和系统的特点10.2 量子逻辑与量子计算介绍量子逻辑与传统数字逻辑的区别讲解量子计算中的逻辑结构和运算规则10.3 数字逻辑教育的挑战与机遇分析数字逻辑教育面临的挑战讲述数字逻辑教育对培养计算机科学人才的重要性重点和难点解析重点环节一:逻辑门的概念和功能逻辑门是数字逻辑电路的基本构建块,包括与门、或门、非门、异或门等。

第六章数字系统6.1 数字系统的基本概念6.2 数据通路6.3 由顶向下的设计方法6.4 小型控制器的设计6.5 微程序控制器的设计6.6 数字系统设计实例返回目录6.1 数字系统的基本概念6.1.1 一个数字系统实例6.1.2 数字系统的基本模型6.1.3 数字系统与逻辑功能部件的区别6.1.1 一个数字系统实例数字系统是由许多基本的逻辑功能部件有机连接起来完成某种任务的数字电子系统,其规模有大有小,复杂性有简有繁。

图6.1表示生产线上药片计数和装瓶控制显示系统的组成框图,它是一个典型的数字系统应用模型。

图6.1 药片装瓶计数显示系统框图6.1.2 数字系统的基本模型图6.2数字系统基本模型6.1.3 数字系统与逻辑功能部件的区别6.2 数据通路6.2.1 总线结构6.2.2 数据通路实例6.2.1 总线结构1.总线的概念图6.3 总线原理示意图2.总线的逻辑结构图6.4多路选择器构成的数据总线图6.5(a)三态门构成的数据总线图6.5(b)三态门构成的数据总线6.2.2 数据通路实例图6.6数据通路6.3 由顶向下的设计方法6.3.1 数字系统的设计任务6.3.2 算法状态机和算法流程图6.3.1 数字系统的设计任务•数字系统的设计任务主要包括下列几部分:(1)对设计任务进行分析,根据课题任务,把所要设计的系统合理地划分成若干子系统,使其分别完成较小的任务。

(2)设计系统控制器,以控制和协调各子系统的工作。

(3)对各子系统功能部件进行逻辑设计。

•【例2】设计一个简单的8位二进制无符号数并行加法运算器,使之能完成两数相加并存放累加和的要求。

图6.7 累加运算器基本框图6.3.2 算法状态机和算法流程图图6.8 状态及其时间关系•(2)分支框。

•(3)条件输出框。

•(4)状态单元。

图6.9 算法流程图的基本图形•【例3】将图6.10(a )所示的米里机状态图转换成ASM 流程图。

•【例4】将图6.11(a )所示的四状态机转换成ASM 流程图。

习题六6.1 可编程逻辑器件有哪些主要特点?PLD作为一种通用型可编程逻辑器件,而它的逻辑功能又是由用户通过对器件编程来自行设定的。

它可以把一个数字系统集成在一片PLD上,而不必由芯片制造厂商去设计和制作专用集成芯片。

采用PLD设计数字系统和中小规模相比具有如下特点:(1) 减小系统体积:单片PLD有很高的密度,可容纳中小规模集成电路的几片到十几片。

(低密度PLD小于700门/片,高密度PLD每片达数万门,最高达25万门)。

(2) 增强逻辑设计的灵活性:使用PLD器件设计的系统,可以不受标准系列器件在逻辑功能上的限制;用户可随时修改。

(3) 缩短设计周期:由于可完全由用户编程,用PLD设计一个系统所需时间比传统方式大为缩短;(4) 用PLD与或两级结构实现任何逻辑功能,比用中小规模器件所需的逻辑级数少。

这不仅简化了系统设计,而且减少了级间延迟,提高了系统的处理速度;(5) 由于PLD集成度高,测试与装配的量大大减少。

PLD可多次编程,这就使多次改变逻辑设计简单易行,从而有效地降低了成本;(6) 提高系统的可靠性:用PLD器件设计的系统减少了芯片数量和印制板面积,减少相互间的连线,增加了平均寿命, 提高抗干扰能力,从而增加了系统的可靠性;(7) 系统具有加密功能:多数PLD器件,如GAL或高密度可编程逻辑器件,本身具有加密功能。

设计者在设计时选中加密项,可编程逻辑器件就被加密。

器件的逻辑功能无法被读出,有效地防止电路被抄袭。

6.2 常见PLD器件有哪些主要类型?常见PLD器件根据可编程逻辑器件问世的时间,我们把PLA、PAL和GAL称为早期的可编程逻辑器件,把CPLD及FPGA称为近代的可编程逻辑器件。

也有人把它们分别称为低密度PLD和高密度PLD。

6.3 简述PAL和PLA在结构上的主要区别。

PAL是由可编程的与阵列、固定的或阵列和输出电路三部分组成。

有些PAL器件中,输出电路包含触发器和从触发器输出端到与阵列的反馈线,便于实现时序逻辑电路。

第六章 习题答案1现有D触发器组成的三个n位寄存器,需要连接起来传送数据。

当控制信号S时,执行(Ra)→Rc的操作;当控制信号S b有效时,执行(R b)→R C的操作。

试写连接电路的逻辑表达式,并画出逻辑电路图。

解:ImageRc = Ra·Sa·LDC + Rb·Sb·LDC2 现有D触发器组成的四个8位寄存器,要求它们之间实现数据传送,试设计连接电路解:Image3 ALU的输出端一般带有一个移位器,其功能为:①ALU输出正常传送;②ALU输左移1位(ALU i+1)传送;③ALU输出右移一位(ALU i-1)传送。

试设计移位器的逻电路。

解:4 一个系统有A,B两条总线,为了接收来自任何一条总线上的数据并驱动任何一条总要一个总线缓冲寄存器。

请用D触发器和三态门设计一个总线缓冲寄存器。

解:Image5 试构造能完成下列程序操作的ASM图:(a) if X = N, then … 。

(b) if X≠N, then …, else …。

解:(c) for X from A to B, step C, do… 。

解:(d) while X = Y, do …。

解:Image(e) if X > N OR X < O, then …, else …。

解:6 有一个数字比较系统,它能对两个8位二进制进行比较。

其操作过程如下:先将二进制数存入寄存器A和B, 然后进行比较,最后将大数移入寄存器A中。

要求:⑴画出此系统方框图,并构造ASM流程图。

⑵设计一个计数器型控制器。

解:(1)②状态转移真值表Image1 电路图Image2 控制信号表达式:ImageImage1. 根据题6的条件,设计一个MUX型控制器。

① ASM流程图Image②状态转移表Image③电路图Image④控制信号表达式为:LDRB=(状态a+状态c)·T2=(+B)·T2LDR A=状态b·T2=A·T2CAP=状态d=BA2. 根据题6的条件,设计一个定序型控制器。

① ASM流程图②状态转移表(3)写出激励方程 NS=Σ PS·C控制信号表达式(4)逻辑电路图1. 根据题6的条件,设计一个微程序控制器。

①微程序流程图Image②微指令格式Image③ 定时信号Image T1-----打入微指令寄存器定时 T2-----执行部件控制信号定时T3-----修改微地址并读出控存定时 ④ 微程序控制器电路Image ⑤微程序代码Image2. 某控制器的状态表如下表所示,其中X和Y为输入变量,试设计一个计数器型控制器。

Image ① ASM流程图与编码(Q1,Q2为两个触发器)令状态A=00, B=01, C=10, D=11Image②状态转移表Image③ 激励方程表达式 利用NS=∑PS·C公式,使用D触发器。

Q2(D)=·X+ ·XY + Q1·X+ Q1·XY + Q2·XY + Q2 Q1·X+ Q2 Q1·XY= ·X + ·XY + Q1·XQ1(D) = ·Y + Q1·XY + Q2(X+Y) + Q2Q1·Y = ·Y + Q2·X + Q2·Y④电路图Image⑤ 控制信号表达式(假设为电位控制信号) F=状态A·+ 状态B·Y + 状态C·X+ 状态D=·+ Q1·Y + Q2·X+ Q2Q1Image11. .根据题10的条件,设计一个MUX型控制器解答:1) ASM流程图与编码同计数器型控制器(见第10题答案)2)按MUX方式列出状态转移真值表3)画出电路图12.根据题10的条件,设计一个定序型控制器解答:1) ASM流程图与计数器法相同2) 使用Qa、Qb、Qc、Qd四个触发器,编码分别为Qa=1000,Qb=0100,Qc=0010,Qd=00013) 状态转移真值表4)写出激励方程 NS=Σ PS·C 5)画出电路图13.设计一个累加运算系统定序型控制器解答:1)算法流程图2)状态转移真值表及激励函数表达式NS=∑PS·C(C=1,无条件转移)3)控制信号表达式4)电路图14.设计一个累加运算系统MUX型控制器解答:1) ASM流程图2)状态转移真值表及激励表达式NS=∑PS·C3)电路图4)控制信号表达式15. 图P6.1所示ASM流程图,设计计数器型控制器解:(1)ASM流程图与编码(Q1,Q2为两个触发器)令状态a=00, b=01, c=11, d=10②状态转移表Image (3)次态方程Image(4)控制信号16.根据图P6.1所示ASM 流程图,设计一个MUX 型控制器解:(1)ASM 流程图、编码、状态转移真值表同计数器型控制器(见第15题答案)(1) MUXA 的输出接触发器D 2,MUXB 的输出接触发器D1,则ImageImage(3)控制信号17. 根据图P6.1所示ASM 流程图,设计一个定序型控制器解: 1)使用Qa 、Qb 、Qc 、Qd 四个触发器对应四个状态a ,b ,c ,d2)状态转移真值表及激励方程表达式Image(3)控制信号18. 根据图P6.1所示ASM流程图,设计一个微程序控制器。

解:步骤如下将ASM流程图转化为微程序流程图确定微指令地址确定微命令确定微指令格式和字长确定控制存储器容量写出微地址转移逻辑表达式将微指令编译成二进制代码。

19. 根据教材图P6.7所示通路,设计一个微程序控制器。

略20. 设计十字路口交通灯控制器解:交通灯控制系统结构框图控制系统ASM图如下Image21.设计一个彩灯控制器。

解:彩灯电路框图如下Imagelibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity light isport(clk1: in std_logic; ---时钟信号light: buffer std_logic_vector(11 downto 0)); --输出end light;architecture behv of light isconstant len: integer:=11;signal banner: std_logic:='0'; ----定义信号banner为两种节拍转换信号;signal clk,clk2: std_logic; ----信号CLK,CLK2作为辅助时钟beginclk<=(clk1 and banner) or (clk2 and not banner);process(clk1)beginif clk1'event and clk1='1' then ---CLK1二分频得CLK2 clk2<=not clk2;end if;end process;process(clk) ----variable flag: bit_vector(3 downto 0):="0000";beginif clk'event and clk='1' thenif flag="0000" thenlight<='1' & light(len downto 1); ----顺序向右循环移位if light(1)='1' then ----依次点亮flag:="0001";end if;elsif flag="0001" then ———依次熄灭light<=light(len-1 downto 0) & '0';if light(10)='0' thenflag:="0010";end if;elsif flag="0010" thenlight<= light(len-1 downto 0) & '1'; ----顺序向左循环移位if light(10)='1' then ----依次点亮flag:="0011";end if;elsif flag="0011" then ———依次熄灭light<= '0' & light(len downto 1);if light(1)='0' thenflag:="0100";end if;elsif flag="0100" thenlight(len downto 6)<=light(len-1 downto 6)&'1'; ---从中间向两边点light(len-6 downto 0)<='1'&light(len-6 downto 1);if light(1)='1' thenflag:="0101";end if;elsif flag="0101" thenlight(len downto 6)<='0'&light(len downto 7); ----从两边向中间熄light(len-6 downto 0)<=light(len-7 downto 0)&'0';if light(2)='0' thenflag:="0110";end if;elsif flag="0110" thenlight(len downto 6)<='1'&light(len downto 7); ----奇偶位循环点亮light(len-6 downto 0)<='1'&light(len-6 downto 1);if light(1)='1' thenflag:="0111";end if;elsif flag="0111" thenlight<="000000000000";flag:="1000";elsif flag="1000" then ----从新开始banner<=not banner; ---banner信号转换,实现第二种节拍flag:="0000";end if;end if;end process;end behv;。