华南理工大学学报(自然科学版)第38卷第10期Journa l o f South C hina U niversity o f Techno l o g y

V o.l 38 N o .102010年10月

(N atura l Science Editi o n)

O ctober 2010

文章编号:1000 565X (2010)10 0024 06

收稿日期:2009 11 23

*基金项目:广东省教育部产学研结合项目(2008A 090400011)

作者简介:黄君凯(1963 ),男,在职博士生,暨南大学教授,主要从事多晶硅薄膜晶体管物理特性和建模研究.E m a i:l h j k196310@https://www.doczj.com/doc/9b9852174.html,

多晶硅薄膜晶体管的泄漏电流和噪声模型

*

黄君凯1

郑学仁1

邓婉玲

2

(1.华南理工大学电子与信息学院,广东广州510640;2.暨南大学信息科学技术学院,广东广州510630)

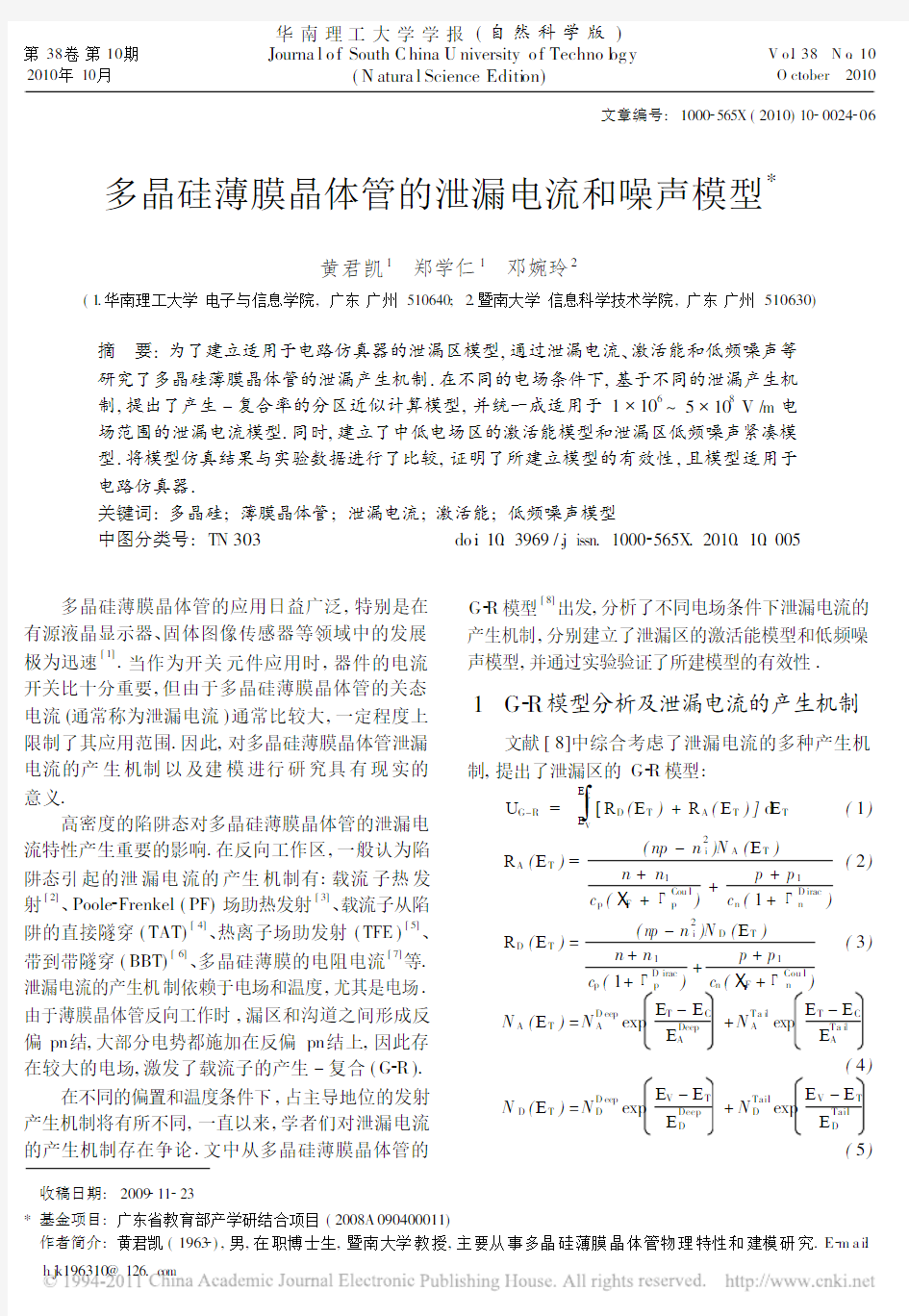

摘 要:为了建立适用于电路仿真器的泄漏区模型,通过泄漏电流、激活能和低频噪声等研究了多晶硅薄膜晶体管的泄漏产生机制.在不同的电场条件下,基于不同的泄漏产生机

制,提出了产生-复合率的分区近似计算模型,并统一成适用于1 106~5 108

V /m 电场范围的泄漏电流模型.同时,建立了中低电场区的激活能模型和泄漏区低频噪声紧凑模型.将模型仿真结果与实验数据进行了比较,证明了所建立模型的有效性,且模型适用于电路仿真器.

关键词:多晶硅;薄膜晶体管;泄漏电流;激活能;低频噪声模型中图分类号:TN 303 do :i 10.3969/.j issn.1000 565X .2010.10.005

多晶硅薄膜晶体管的应用日益广泛,特别是在

有源液晶显示器、固体图像传感器等领域中的发展极为迅速[1]

.当作为开关元件应用时,器件的电流开关比十分重要,但由于多晶硅薄膜晶体管的关态电流(通常称为泄漏电流)通常比较大,一定程度上限制了其应用范围.因此,对多晶硅薄膜晶体管泄漏电流的产生机制以及建模进行研究具有现实的意义.

高密度的陷阱态对多晶硅薄膜晶体管的泄漏电流特性产生重要的影响.在反向工作区,一般认为陷阱态引起的泄漏电流的产生机制有:载流子热发射[2]、Poole Frenkel (PF)场助热发射[3]、载流子从陷阱的直接隧穿(TAT)

[4]

、热离子场助发射(TFE )

[5]

、

带到带隧穿(BBT)[6]

、多晶硅薄膜的电阻电流[7]

等.

泄漏电流的产生机制依赖于电场和温度,尤其是电场.由于薄膜晶体管反向工作时,漏区和沟道之间形成反偏pn 结,大部分电势都施加在反偏pn 结上,因此存在较大的电场,激发了载流子的产生-复合(G R ).在不同的偏置和温度条件下,占主导地位的发射产生机制将有所不同,一直以来,学者们对泄漏电流的产生机制存在争论.文中从多晶硅薄膜晶体管的

G R 模型[8]

出发,分析了不同电场条件下泄漏电流的

产生机制,分别建立了泄漏区的激活能模型和低频噪

声模型,并通过实验验证了所建模型的有效性.

1 G R 模型分析及泄漏电流的产生机制

文献[8]中综合考虑了泄漏电流的多种产生机制,提出了泄漏区的G R 模型:

U G-R =

E C

E V [R D

(E T )+R A (E T )]d E T

(1)

R A (E T )=(np -n 2

i )N A (E T )

n +n 1c p ( F + Cou l p )+p +p 1

c n (1+ D irac

n )(2)

R D (E T )=

(np -n 2

i )N D (E T )

n +n 1c p (1+ D irac p )+p +p 1

c n ( F + Cou l

n )(3)

N A (E T )=N D eep

A

exp

E T -E C E Deep A +N Ta il

A exp E T -E C E Ta il

A

(4)

N D (E T )=N D eep

D

exp E V -E T E Deep

D

+N Tail

D exp

E V -E T E Tail

D

(5)

式中: F 是PF 效应增强因子; Cou l

n ,p 和 D irac

n ,p 分别是Cou lo mb ic 陷阱和D irac 陷阱在电场作用下的发射率比;N A 和N D 分别代表双指数形式的类受主和类施主陷阱态密度分布;U G R 是总的G R 率;E C 是导带底能级;E V 是价带顶能级;E T 是陷阱能级;n 是导带电子浓度;p 是价带空穴浓度;n i 是本征载流子浓度,其值与温度有关[9]

;n 1和p 1分别是陷阱能级上的电子浓度和空穴浓度;c n 和c p 分别是电子和空穴的俘获系数;N D eep

A

和N Ta il

A 分别是类受主的深能级和

带尾态的陷阱态密度;N D eep

D 和N Tail

D 分别是类施主的

深能级和带尾态的陷阱态密度;E D eep

A

和E Ta il

A 分别是

类受主的深能级和带尾态的特征能量宽度;E D eep

D 和

E Tail

D 分别是类施主的深能级和带尾态的特征能量宽度.

式(1)所描述的G R 率在电场(F,单位为V /m )

为1 106~8 108

V /m 时的数值计算结果如图1所

示,其中m *e 和m *

h 分别是电子和空穴的隧穿有效质量.由于 Cou l

n ,p 和 D irac

n ,p 包含对隧穿几率的积分,因此式(1)的G R 率是一个双积分表达式.双积分的计算不仅需要消耗大量的计算资源,而且无法清晰地表征陷阱态的发射产生机制对泄漏电流的影响.为了进一步揭示泄漏电流产生的主要机制,文中将电场划分成3个区间进行分析,即低电场区(1 0 106

V /m !F <

1 0 107V /m )、中电场区(1 0 107

V /m !F <1 2 108V /m )和高电场区(F ?1 2 108

V /m

).

图1 U G R 与F 的关系F i g .1 U G R as a f unction o f F

1.1 低电场区

如图2所示,在低电场区,l g U G R 与电场的开方近似呈线性关系,与文献[9]中结果一致,且 F =

exp q 3

F /(p S i )k T

,其中q 是电子电量, S i 是硅的

介电常数,k 是Bo ltz m ann 常数,T 是热力学温度.可

见,在低电场区,PF 效应增强下的热发射是泄漏电

流产生的主要机制.因此,可以导出低电场区U G R 的渐进方程为

U L G-R

=a 1exp a 2

q 3

F /(p S i )k T

(6)式中:a 1和a 2是拟合系数.

从图2中可知,在低场区,式(6)能较好地拟合式(1)的数值仿真结果.同时,如图2所示,采用不同的陷阱参数,式(6)仍有较好的拟合结果.进一步

的计算表明,仿真结果的相对误差(U G R -U L

G R U G R )平均值为0 0315,满足器件应用的要求.存在该误差的主要原因是式(6)中只考虑了 F 因子,而式(1)中则综合考虑了影响泄漏电流的各种因素.图2仿真结果的相对误差最大值约为0 0900,且出现在电场值较大处,这是由于此时电场已接近中电场区范围,热离子场助发射逐渐替代热发射成为主要的泄漏产生机制.另外,在较低的V dg (V dg =V d -V g ,单位为V ,其中V d 是漏电压,V g 是栅电压)下,lg I leak 与

V dg 也近似呈线性关系.这进一步验证了在低电场区泄漏电流的主要产生机制是PF 效应增强下的热发射.

图2 低电场区U G R 与F 、I leak 与

V dg 的关系F i g .2 R e lati onships bet w een U G R and F ,

and bet ween I leak

and

V dg i n l ow i ntensit y electric field

V d =1V;陷阱曲线1参数:a 1=7 4 1018c m -3/s 、a 2=0 7,其它参数与图1相同;陷阱曲线2参数:a 1=2 0

1018c m -3/s 、a 2=0 7、N De ep A =N D eep D =2 1018c m -3#e V -1、N Ta il A =N T ail D =1 1021c m -3#e V -1、E Deep A =E De ep D =0 1610e V 、E T a il A =E Ta il D =0 0166e

V,其它参数与图1相同 另外,G R 率受温度T 的影响较大,特别是在热

发射主导下.当电场固定时,激活能E a 就是曲线ln I leak -1/(k T )的斜率.当E a 减小时,陷阱态的载流子产生率将增加,从而引起泄漏电流的增加,因此E a 反映了U G R 或I leak 随温度的变化情况.考虑式(1)

25

第10期黄君凯等:多晶硅薄膜晶体管的泄漏电流和噪声模型

中的n i 随温度T 的变化情况[10]

,利用式(6)可以得到低电场区E a 的近似表达式为

E L a

=E g 2-a 2

q 3

F p S i

(7)

其中E g 是多晶硅材料的禁带宽度.

1.2 中电场区

在中电场区,lg U G R 与电场F 近似呈线性关系,如图3所示,其中W 和L 分别为薄膜晶体管的沟宽和沟长.图3反映了在中电场条件下,PF 效应影响下的热离子场助发射是泄漏电流的主要产生机制,此时陷阱中的载流子首先热激发到一个虚能级[5,11],然后从那里直接隧穿到导带或价带.为了保证低、中电场区的U G R 表达式连续,可推导出中电场区U G R 的渐进方程为

U

M G R

=a 1exp a 2

k T

q 3

F low p S i

# exp a 02k T q 3

p Si F low

(F -F low )(8)式中:F low 是低电场和中电场交界处的电场值;a 0是拟合参数.

图3 中电场区U G R 与F 、I leak 与V dg 的关系

F ig .3 R elati onship bet w een U

G R and F,and bet ween I leak and

V dg i n m odera te i ntens i ty electr i c fi e l d

W =50 m,L =6 m,V d =5 1V ,a 0=0 745,其它参数值与图2相同

从图3中可知,在中电场区,式(8)是一个适用

于不同陷阱密度参数的近似表达式.图3仿真结果的相对误差平均值为0 0865,可满足应用要求.存在该误差的主要原因是式(8)中只考虑了D irac 陷阱的

TFE 效应,而忽略了其它因素.此外,实验结果[5]

也验证了在中电场范围的V dg 下,lg I leak 与V dg 呈正比关系.

如前所述,TFE 机制包括热激发过程,因此温度既影响了热发射,也影响了TFE 的几率.利用式(8),

可推导出中电场区E a 的近似方程:

E M a

=E g

2

-q 3

p S i F low

a 02F !+a 2-a 0

2

F low (9)

其中拟合因子!考虑了在中电场区的电场较高值

处,U G R 逐渐受到TAT 机制的影响.由于直接隧穿机制不受温度的影响,因此E a 在高电场区快速下降.

1.3 高电场区

在高电场区,隧穿几率大大增加,而PF 效应影

响的热发射可忽略,因而载流子从陷阱直接隧穿机

制占主导地位.如图4所示,当F ?1 2 108

V /m 时,lg (U G R /F )与1/F 近似呈线性关系,这表明此时直接隧穿占优.在高电场条件下,U G R 只考虑了载流子从陷阱的直接隧穿,没有考虑载流子的BBT 机

制.事实上,当F ?1 0 108

V /m 时,BBT 的作用相

当重要[12]

.注意到BBT 对净G R 率的贡献也存在lg (U G R /F )?1/F 的关系.因此,综合考虑TAT 和BBT 机制,高电场区G R 率的渐进方程可以表示为

U H

G R =a 3F exp (-a 4/F ), F ?F h igh a 3F h igh exp (-a 4/F h igh ), F (10) 式中:a 3和a 4是拟合系数;F high 是中电场与高电场交界处的电场强度. 从图4中可知,在V dg 取高值时,ln (I leak /V dg )与1/V dg 呈线性关系,表明此时隧穿机制(包括TAT 和BBT )已经成为泄漏电流的主要产生机制;当F >F h igh 时,式(10)的函数值逼近了式(1)的数值积分结果.图4仿真结果的相对误差平均值为0 1700,产生该误差的主要原因是式(10)中只考虑了直接隧穿机制,而忽略了其它产生机制. 图4 高电场区U G R /F 与1/F 、I le ak /V dg 与1/V dg 的关系F i g .4 R elati onship be t w een U G R /F and 1/F, and bet ween I leak /V dg and 1/V dg i n h i gh intensity e lectr i c fi e l d V d =10V ;陷阱曲线1参数:a 3=1023c m -2#s -1#V -1,a 4=1 3 109V /m;陷阱曲线2参数:a 4=1 3 109V /m;a 3=2 9 1022c m -2#s -1#V -1;其它参数值与图2相同 26 华南理工大学学报(自然科学版) 第38卷 由于纯隧穿机制受温度的影响可忽略,隧穿几率主要受高电场的影响.在泄漏区,随着负栅压和漏压的增大,漏耗尽区的高电场降低了载流子需要克服的势垒.此时,增加的电场使激活能快速下降,E a 可低于0 1e V. 综上所述,结合在低、中和高电场中起主导作用的U L G R、U M G R和U H G R,可得到总的G R率: U L M G R=U L G R 1+l1e xp F-F low l2 + U M G R 1+l1exp -(F-F low) l2 (11) U G R= 1 1/U L M G R+11U H G R (12) 式中:l1和l2反映了U G R在不同电场区过渡的突变程度;F high为[13]: F h igh=22m*e E C c1k T/(qh)(13)式中:c1是拟合系数,取0 5 基于式(12),泄漏电流可近似描述为[11]: I leak=qV ol U G R(14)式中:V ol是耗尽的栅漏交叠区的体积,栅漏交叠区是泄漏电流产生机制的主要发生区域.因此,运用式(14)可以快速地计算电场F为106~5 108V/m的泄漏电流值. 2 泄漏区的低频噪声模型 为了进一步确定泄漏电流的产生机制,可以将低频噪声测量及模型应用到泄漏电流的分析中[14].在n沟薄膜晶体管中泄漏电流的噪声主要是由漏结耗尽区的载流子数目涨落造成的.因此,测量得到的低频泄漏电流噪声S L基本满足1/f(f是工作频率)规律. 在泄漏工作区,正常的偏压V d和V g下,漏结附近的最大电场值通常处于中电场区或高电场区,因此文中讨论的低频噪声模型只考虑这两种电场范围.由于电流的涨落是由电场F的起伏引起的,因此在高电场区,泄漏电流的噪声频谱密度可以表示为[14]: S L= 4 2S i ?I leak ?F 2S Q WL (15)其中S Q为界面电荷的频谱密度.对于单一陷阱能级而言,S Q是Lorentzian频谱,因此有[15]: S Q?4t 1+4p2f2t2 (16)其中t是时间常数. 考虑到多晶硅材料中陷阱态的分布是连续的,时间常数的分布g(t)?1/t,因此1/f的频谱为[15]: % 1 t 4t 1+4p2f2t2 d t= 1 f (17)所以,考虑陷阱态的连续分布,应有 S Q? 1 f (18) 另外,在高电场区,利用式(10)和(14),有 ?I leak ?F=qV ol a31+ a4 F exp- a4 F =I leak 1+a4/F F (19) 将式(18)和(19)代入式(15),S L可简写成 S h igh L=A1 1+a4/F F 2I2 leak f (20)其中A1是高电场区噪声频谱密度的幅值拟合系数.式(20)就是高电场区泄漏电流噪声频谱密度的紧凑模型. 基于类似的分析,可推导得到中电场区泄漏电流噪声频谱密度的紧凑模型: S m id L=A2 I2leak f (21)其中A2是中电场区噪声频谱密度的幅值拟合系数. 以上分析表明,泄漏电流和噪声都与电场有关,最大的电场主要发生在栅漏覆盖区[16],此时电场的大小可近似表示为[17]: F= V dg-V fb t OX( S i/ O X) + V d w (22)式中:t OX是栅氧化层厚度; OX是栅氧化层的介电常数;V fb是平带电压;w为拟合参数. 3 实验结果与讨论 式(7)和(9)可分别用于近似计算低电场区和中电场区的E a,而在高电场区E a快速下降到0 1e V 以下.图5分别给出了由式(7)和(9)计算得到的E a 与由数值仿真式(1)得到的激活能.从图5中可见,文中提出的E a计算方法在低电场区和中场电区是有效的;E a随电场的增加而下降,因为受温度影响 27 第10期黄君凯等:多晶硅薄膜晶体管的泄漏电流和噪声模型 较大的热发射和TFE 主要发生在这两个电场区 . 图5 低、中电场区E a -F 特性的模型仿真结果与式(1)的 数值仿真结果比较 F ig .5 Co m parison of E a -F cha racter istics bet ween si m ulati on results of the propsed m ode ls and nu m erical si m ulati on results o f Equ .(1)f o r lo w and moderate i ntensity elec tr ic fi e l ds 图6给出了器件在不同漏压下泄漏区的转移特性曲线.从图6中可见,模型(式(14))计算结果与实验结果 [7] 相吻合,其中模型计算所用参数值如下: t O X =100n m ,w =5 10-5 c m ,qV ol =1 28 10 -34C #c m 3 ,a 1=3 75 1020 c m -3 /s ,a 2=1,a 3=1023 c m -2 /(s #V ), a 0=0 92,a 4=6 108 V /c m ,V fb =0V ,l 1=1 1,l 2= 4 103 V /c m . 图7(a )给出了n 沟多晶硅薄膜晶体管在高电场区的低频噪声频谱密度与泄漏电流的关系.根据式(20)可知,lg (S high L [F /(1+a 4/F )]2 )与l g I leak 应 呈线性关系,且斜率为2.如图7(a )所示,对实验结果 [14] 进行整理,并画出这两者之间的关系曲线,发 现它们的确呈线性关系且斜率约为2,从而验证了式(20)的高电场区泄漏电流噪声频谱密度紧凑模 型是有效的. 图6 泄漏区转移特性的模型计算结果与实验结果[7]比较F i g .6 Co m parison o f transfer character istics i n leakage reg i on bet w een ca l culati on resu lts by m ode l s and exper i m enta l results i n R eference [7] 图7 两种薄膜晶体管的S h i g h L [F /(1+a 4/F )]2与I leak 的关系F i g .7 R e l a ti onsh i p be t w een S high L [F /(1+a 4/F )]2and I leak f o r t w o types o f thin fil m transist o rs 注意到纳米晶硅薄膜晶体管的物理特性与多晶硅薄膜晶体管存在相似性,但纳米晶硅薄膜晶体管的陷阱态密度更高,因此也可以采用多晶硅薄膜晶体管的建模理论对其建立模型.图7(b )给出了纳米晶硅薄膜晶体管在高电场条件下,泄漏区中 28华南理工大学学报(自然科学版)第38卷 S h igh L[F/(1+a4/F)]2与I leak的关系曲线,其中F利用式(22)计算得到.从图7(b)中可见,l g(S h igh L[F/ (1+a4/F)]2)与l g I leak同样呈线性关系且斜率也约为2.因此式(20)对纳米晶硅薄膜晶体管同样有效. 4 结语 基于低电场区的PF增强热发射、中电场区的热离子场助发射、高电场区的隧穿这3类泄漏电流的产生机制,分别在不同电场条件下和满足器件应用的误差范围内,提出了双积分G R率的近似计算模型.由于泄漏电流除了依赖于电场外,还与温度有关,因此提出了相应的激活能模型.为了进一步确定泄漏电流的产生机制,提出了泄漏区的低频噪声模型.泄漏电流、激活能和噪声频谱密度的计算结果与实验数据的比较,证明了文中模型的有效性.由于该模型无需进行积分计算,从而提高了运算速度,因此所建立的模型适用于电路仿真器中. 参考文献: [1] 郑学仁,邓婉玲,陈荣盛.多晶硅薄膜晶体管的电流和 电容分析模型[J].华南理工大学学报:自然科学版, 2007,35(10):221 226. Zheng X ue ren,D eng W an li ng,Chen Rong sheng.A na lytical current and capac itance m ode ls o f po l ys ilicon t h i n fil m transist o rs[J].Journal o f South Ch i na U n i versity o f T echno l ogy:N a t ura l Sc i ence Editi on,2007,35(10):221 226. [2] Brotherton S D,A y res J R,Y oung N D.Character i sati on o f low temperature poly Si t h i n fil m transi stors[J].Soli d Sta te E lectron i cs,1991,34(7):671 679. [3] Seki S,K ogure O,T suji ya m a B.L eakag e current charac ter i sti cs o f offset ga te structure polycrysta lli ne silicon M O SFET s[J].I EEE E lectron D ev ice L etters,1987,8 (9):434 436. [4] K i m C H,Sohn K S.T emperature dependen t l eakage cur rents i n po lycry sta lli ne sili con thi n fil m transi stors[J]. Jou rnal of A pp lied Phy si cs,1997,81(12):8084 8089. [5] JacunskiM D,ShurM S,Owusu A A,et a.l A short chan ne l DC SP ICE mode l for po l ysilicon th i n fil m transistors inc l udi ng temperat u re effects[J].I EEE T ransac ti ons on E l ec tron D ev ices,1999,46(6):1146 1157. [6] D i m itr i adis C A,Fa r m ak i s F V,B ri n i J,et a.l D ependence o f the leakage current on the fil m qua lity i n polycrysta lli ne sili con th i n fil m transistors[J].Journa l o f A pp lied Phy sics,2000,88(5):2648 2651. [7] O no K,A oya m a T,K onish i N,et a.l Ana l ys i s o f current vo ltage character istics of low te m pera t ure processed po l y silicon thin fil m transisto rs[J].I EEE T ransacti ons on E lectron Dev ices,1992,39(4):792 802. [8] L ui O K B,M ig li o ra to P.A ne w gene ration reco m b i na ti on model for dev ice si m ulation inc l udi ng the Poo le F renke l effect and phonon assisted t unneli ng[J].So lid State E lectronics,1997,41(4):575 583. [9] W u W J,Y ao R H,L i S H,e t a.l A compact model f o r po lysili con TFT s l eakage current i ncl uding the Poo le F renke l effect[J].I EEE T ransactions on E lectron D e v i ces,2007,54(11):2975 2983. [10] A rora N D.M OSFET m ode ls for VLS I circu it si m u l a ti on [M].N e w Y ork:Spri nger V erlag,1993. [11] Bha ttacharya S S,Bane rjee S K,N guyen B Y,et a.l T e m perat u re dependence o f the anom alous leakage curren t in po l ysilicon on insu l a tor M OSFET s[J].IEEE T ransac ti ons on E l ectron D ev ices,1994,41(2):221 227. [12] Hurkx G A M,K l aassen D B M,K nuversM P G.A new reco m b i nati on m ode l for dev i ce si m ulati on i ncl uding tun neli ng[J].IEEE T ransacti ons on E lectron D ev ices, 1992,39(2):331 338. [13] V incentG,Chan tre A,Bo is D.E lectr ic fi e l d eff ec t on the therma l e m issi on o f traps in sem i conductor j unctions [J].Journa l of A ppli ed Physics,1979,50(8):5484 5487. [14] A ng eli s C T,D i m itriadis C A,Sa m aras I,et a.l St udy of leakage current in n channe l and p channe l po l y crysta l li ne silicon t h i n fil m transistors by conduc ti on and l ow frequency no i se measure m ent[J].Journa l o f A ppli ed Physi cs,1997,82(8):4095 4101. [15] H oog e F N.O n t he additiv i ty o f gene ration reco m b i na ti on spectra Part1:Conduction band w ith t wo cen tres[J]. Physi ca B:Condensed M atter,2002,311(3/4):238 249. [16] K ang I S,Yu S H,San S W,et a.l Low leakage current struc t ures w ith subgate i n me tal i nduced unil ate ra lly crys tallized sili con th i n fil m transist o rs[J].Journa l of the Electroche m i ca l So ciety,2008,155(7):H536 H539. [17] H atzopou l os A T,A rpatzan is N,T ass i s D H,et a.l St udy o f the dra i n l eakage current i n bo tto m ga ted nano crysta l li ne sili con t h i n fil m trans i stors by conduction and l ow frequency no ise m easurem ents[J].I EEE T ransactions on E lectron D ev i ces,2007,54(5):1076 1081. (下转第35页) 29 第10期黄君凯等:多晶硅薄膜晶体管的泄漏电流和噪声模型 Quantified Feedback Preprocessi ng ofM IMO OFD M Syste m s Zhou D ong y ue Hu B in jie (Schoo l o f E lectron ic and Infor m a ti on Eng i neering ,South Ch i na U nivers it y of T echno logy ,G uang zhou 510640,G uangdong ,China) Abst ract :I n order to reduce the feedback b its o fM I M O OFDM preprocessi n g syste m s ,a ne w li m ited feedback pre processi n g sche m e ,w hich incl u des do w nlink quantified power distribution coefficients and quantified diversity w e i g ht vectors ,is proposed based on the spatial d i v ersity ofM I M O OFD M syste m s .I n this sche m e ,the po w er dis tri b ution o f sub carriers is un ifor m l y quantified by the receiverw ith a lo w co mp lex ity and the preprocessing diversity vectors are quantified v ia j o int interpo lati o n opti m ization .Then ,the li m ited b its o f quantified po w er distribution and vector infor m ati o n are fed back to the trans m itter ,and the quan titati v e infor m ati o n obta i n ed fro m the feedback is used by t h e trans m itter to restore the preprocessed po w er allocati o n and vector through i n ter polati o n .Si m ulated re su lts sho w that t h e proposed sche m e considerably i m proves the BER (B it Error Rate)perfor m ance of the syste m .K ey w ords :orthogona l frequency division m ultiplex i n g ;prepr ocessing ;li m ited feedback ;quantification ;space di versity 责任编辑:许花桃 (上接第29页) Leakage Curre nt and Noise M odel of Pol ysilicon Thin Fil m Transistors H uang Jun kai 1 Zheng X ue ren 1 D eng Wan ling 2 (1.Schoo l of Electron ic and In f o r ma tion Eng ineer i ng ,South Chi na Un i versity of T echno l ogy ,G uangzhou 510640,G uangdong ,Chi na ; 2.Co ll ege o f Info r m ati on Sc i ence and T echnology ,Ji nan U n i v ers it y ,G uang z hou 510630,G uangdong ,China) Abst ract :In order to estab lish a su itab le m odel to descri b e the leakage reg ion of circuit si m ulato rs ,t h e leakage generati o n m echanis m of po lysilicon thin fil m transistors is i n vestigated i n ter m s of curren,t activati o n energy and lo w frequency no ise ,etc .Then,based on different leakage m echan is m s ,so m e approx i m ations o f the genera ti o n re co m b i n ati o n m odel are proposed,and a unified leakage curren tm ode l su itable for the e lectric fi e l d of 1 106 ~5 108 V /m is deduced .M oreover ,the acti v ation energy m ode ls fo r lo w and m oderate electric fields are derived ,and a co m pactm odel for lo w frequency leakage curren t no ise is put for w ard .Co m parisons bet w een the si m ulated and the experi m ental resu lts sho w t h at the proposed m odels are a ll effective and su itab le for circu it si m u l a tors .K ey w ords :po l y silicon ;th i n fil m transistors ;leakage curren;t acti v ation energy ;lo w frequency noise m odel 责任编辑:许花桃 35 第10期周冬跃等:量化反馈的M I M O OFD M 预处理方法 第五代低温多晶硅薄膜晶体管液晶显示器件 (L TPS TFT-LCD)项目 环境影响报告书 (简本) 评价单位:深圳市环境科学研究院 二O一一年十月·深圳 目录 第一章总论 (3) 1.1任务来源 (3) 1.2区域环境功能属性 (4) 1.3评价标准 (4) 1.4评价等级 (8) 1.5评价工作范围 (9) 1.6环境敏感点及环境保护目标 (9) 第二章现有工程回顾性影响评价 (12) 2.1现有工程的基本情况 (12) 2.2现有工程建设内容 (13) 2.3现有工程污染物排放及治理措施回顾性评价 (16) 第三章技改项目工程概况、工程分析 (22) 3.1技改项目基本情况 (22) 3.2技改项目建设内容 (22) 3.3工程分析 (24) 3.4“三本帐”核算 (38) 第四章环境现状调查与评价 (39) 4.1环境空气质量现状 (39) 4.2水环境质量现状 (39) 4.3声环境现状 (39) 4.4评价区域的环境问题 (39) 第五章环境影响预测与评价 (40) 5.1水环境影响评价结论 (40) 5.2大气环境影响评价结论 (40) 5.3声环境影响评价结论 (40) 5.4固(液)体废物环境影响评价结论 (40) 5.5环境风险评价结论 (41) 第六章污染防治措施 (42) 6.1废水治理措施 (42) 6.2废气处理措施 (45) 6.3噪声治理措施可行性分析 (50) 6.4固体废物治理措施可行性分析 (50) 6.5地下水污染防治措施 (51) 6.6项目二期工程达产后进行技改的环保措施要求 (51) 第七章项目与规划符合性分析 (52) 第八章结论 (53) 场效应管(FET)是利用控制输入回路的电场效应来控制输出回路电流的一种半导体器件,并以此命名。由于它仅靠半导体中的多数载流子导电,又称单极型晶体管。 工作原理场效应管工作原理用一句话说,就是“漏极-源极间流经沟道的漏极电流,用以栅极与沟道间的pn结形成的反偏的栅极电压控制漏极电流ID”。更正确地说,漏极电流ID流经通路的宽度,即沟道截面积,它是由pn结反偏的变化,产生耗尽层扩展变化控制的缘故。在VGS=0的非饱和区域,表示的过渡层的扩展因为不很大,根据漏极-源极间所加VDS的电场,源极区域的某些电子被漏极拉去,即从漏极向源极有电流漏极电流ID流动。从门极向漏极扩展的过度层将沟道的一部分构成堵塞型,漏极电流ID饱和。将这种状态称为夹断。这意味着过渡层将沟道的一部分阻挡,并不是电流被切断。 在过渡层由于没有电子、空穴的自由移动,在理想状态下几乎具有绝缘特性,通常电流也难流动。但是此时漏极-源极间的电场,实际上是两个过渡层接触漏极与门极下部附近,由于漂移电场拉去的高速电子通过过渡层。因漂移电场的强度几乎不变产生ID的饱和现象。其次,VGS向负的方向变化,让VGS=VGS(off),此时过渡层大致成为覆盖全区域的状态。而且VDS的电场大部分加到过渡层上,将电子拉向漂移方向的电场,只有靠近源极的很短部分,这更使电流不能流通。 分类场效应管分为结型场效应管(JFET)和绝缘栅场效应管(MOS管)两大类。 按沟道材料型和绝缘栅型各分N沟道和P沟道两种;按导电方式:耗尽型与增强型,结型场效应管均为耗尽型,绝缘栅型场效应管既有耗尽型的,也有增强型的。 场效应晶体管可分为结场效应晶体管和MOS场效应晶体管,而MOS场效应晶体管又分为N沟耗尽型和增强型;P沟耗尽型和增强型四大类。 场效应管与双极性晶体管的比较,场效应管具有如下特点。 1. 场效应管是电压控制器件,栅极基本不取电流,它通过VGS(栅源电压)来控制ID(漏 极电流);而晶体管是电流控制器件,基极必须取一定的电流。因此,在信号源额定电流极小的情况,应选用场效应管。 2. 场效应管是多子导电,而晶体管的两种载流子均参与导电。由于少子的浓度对温度、 辐射等外界条件很敏感,因此,它的温度稳定性较好;对于环境变化较大的场合,采用场效应管比较合适。 3. 场效应管的源极和漏极在结构上是对称的,可以互换使用,耗尽型MOS 管的栅——源电压可正可负。因此,使用场效应管比晶体管灵活。 4 . 场效应管除了和晶体管一样可作为放大器件及可控开关外,还可作压控可变线性电阻使用 特点与双极型晶体管相比,(1)场效应管的控制输入端电流极小,因此它的输入电阻很大。 (2)场效应管的抗辐射能力强; (3)由于不存在杂乱运动的电子扩散引起的散粒噪声,所以噪声低。 晶体管的特性曲线 晶体管特性曲线即管子各电极电压与电流的关系曲线,是管子内部载流子运动的外部表现,反映了晶体管的性能,是分析放大电路的依据。为什么要研究特性曲线: (1) 直观地分析管子的工作状态 (2) 合理地选择偏置电路的参数,设计性能良好的电路重点讨论应用最广泛的共发射极接法的特性曲线 1.测量晶体管特性的实验线路 图1 共发射极电路 共发射极电路:发射极是输入回路、输出回路的公共端。如图1所示。 2.输入特性曲线 输入特性曲线是指当集-射极电压U CE为常数时,输入电路( 基极电路)中基极电流I B与基-射极电压U BE之间的关系曲线I B = f (U BE),如图2所示。 图2 3DG100晶体管的输入特性曲线 U CE=0V时,B、E间加正向电压,这时发射结和集电结均为正偏,相当于两个二极管正向并联的特性。 U CE≥1V时,这时集电结反偏,从发射区注入基区的电子绝大部分都漂移到 集电极,只有小部分与空穴复合形成I B。U CE>1V以后,I C增加很少,因此I B 的变化量也很少,可以忽略U CE对I B的影响,即输入特性曲线都重合。 由输入特性曲线可知,和二极管的伏安特性一样,晶体管的输入特性也有一段死区。只有在发射结外接电压大于死区电压时,晶体管才会导通,有电流I B。 晶体管死区电压:硅管0.5V,锗管0.1V。晶体管正常工作时发射结电压:NPN型硅管U BE0.6 ~ 0.7) V PNP型锗管U BE0.2 ~ 0.3) V 3.输出特性曲线 输出特性曲线是指当基极电流I B为常数时,输出电路(集电极电路)中集电极电流I C与集-射极电压U CE之间的关系曲线I C = f (U CE),如图3所示。 变化曲线,所以晶体管的输出特性曲在不同的I B下,可得出不同的I C随U CE 线是一族曲线。下面结合图4共发射极电路来进行分析。 图3 3DG100晶体管的输出特性曲线图4 共发射极电路 晶体管有三种工作状态,因而输出特性曲线分为三个工作区 (1) 放大区 在放大区I C=βI B,也称为线性区,具有恒流特性。在放大区,发射结处于正向偏置、集电结处于反向偏置,晶体管工作于放大状态。 对NPN 型管而言, 应使U BE> 0, U BC< 0,此时,U CE> U BE。 (2) 截止区I B = 0 的曲线以下的区域称为截止区。 I B = 0 时, I C = I CEO(很小)。(I CEO<0.001mA)。对NPN型硅管,当U BE<0.5V 时, 即已开始截止, 为使晶体管可靠截止, 常使U BE≤0。截止时, 集电结也处于反向偏置(U BC≤ 0),此时, I C≈0, U CE≈U CC。 (3) 饱和区当U CE< U BE时,集电结处于正向偏置(U BC> 0),晶体管工作于饱和状态。 龙源期刊网 https://www.doczj.com/doc/9b9852174.html, 激光晶化能量对多晶硅薄膜晶体管特性影响的研究 作者:江朝庆 来源:《电子技术与软件工程》2016年第13期 摘要本文利用准分子激光晶化技术制备了低温多晶硅薄膜晶体管,研究了不同激光晶化能量密度对多晶硅薄膜晶粒尺寸以及器件电学特性的影响。为了进一步阐释激光晶化能量密度对多晶硅薄膜晶体管特性产生影响的原因,通过二维器件仿真拟合了多晶硅薄膜晶体管特性并提取了缺陷态密度等参数。通过比较得到态密度随着能量密度变化规律,最终得到最优工艺条件。 【关键词】激光晶化能量密度多晶硅薄膜晶体管缺陷态器件仿真 在经过了阴极射线显像管,液晶屏显示技术以后,发展到了有机发光二极管(OLED)显示器又称为有机电激光显示技术阶段。OLED显示器极大提升了画面的细腻程度和彩色饱和度及对比度,使人们对于视觉的享受追求到达了一个新的境界。有源矩阵有机发光二极管(AMOLED)产业在国内外都得到迅速的发展,其中代表性的企业有三星,台积电等。多晶硅薄膜晶体管在AMOLED做驱动电路,起着重要的作用,对于其迁移率,阈值电压,亚阈值摆幅,均一性等参数都有很高的要求。 利用二维器件仿真工具对多晶硅薄膜晶体管进行器件仿真,通过模型的选取以及参数的调整,能够让我们对于多晶硅薄膜晶体管的复杂物理机制进行研究讨论。例如多晶硅材料的晶粒结构特性,以及漏电模型我们都可以通过仿真工具建模来分析。而且在对更为复杂的应用中,还可以利用它来建新的器件,并预测相关的电学特性。在半导体行业及集成电路产业中都有深远的意义。 1 ELA多晶硅薄膜晶体管制备与分析 1.1 工艺流程 本论文中用到了P型准分子激光晶化(ELA)多晶硅薄膜晶体管器件,其制备工艺流程如下: 利用等离子体增强化学气相沉积法(PECVD)方法在玻璃衬底上沉淀厚度为100nm的 Si02缓冲层。450℃下采用PECVD,淀积厚度为50nm非晶硅。利用准分子激光法制备多晶硅薄膜,为了研究比较不同晶化能量密度的激光对器件特性,分别采用能量密度为390、410、430、450、470、490、510、530 mJ/cm2激光光照来制备多晶硅薄膜晶体管,定义有源区,并在有源区上利用PECVD法淀积厚度为120 nm的栅氧层。之后利用金属溅射法将MoW作为栅 根据三极管的原理开发出的新一代放大元件,有3个极性,栅极,漏极,源极,它的特点是栅极的内阻极高,采用二氧化硅材料的可以达到几百兆欧,属于电压控制型器件 -------------------------------------------------------------- 1.概念: 场效应晶体管(Field Effect Transistor缩写(FET))简称场效应管.由多数载流子参与导电,也称为单极型晶体管.它属于电压控制型半导体器件. 特点: 具有输入电阻高(100000000~1000000000Ω)、噪声小、功耗低、动态范围大、易于集成、没有二次击穿现象、安全工作区域宽等优点,现已成为双极型晶体管和功率晶体管的强大竞争者. 作用: 场效应管可应用于放大.由于场效应管放大器的输入阻抗很高,因此耦合电容可以容量较小,不必使用电解电容器. 场效应管可以用作电子开关. 场效应管很高的输入阻抗非常适合作阻抗变换.常用于多级放大器的输入级作阻抗变换.场效应管可以用作可变电阻.场效应管可以方便地用作恒流源. 2.场效应管的分类: 场效应管分结型、绝缘栅型(MOS)两大类 按沟道材料:结型和绝缘栅型各分N沟道和P沟道两种. 按导电方式:耗尽型与增强型,结型场效应管均为耗尽型,绝缘栅型场效应管既有耗尽型的,也有增强型的。 场效应晶体管可分为结场效应晶体管和MOS场效应晶体管,而MOS场效应晶体管又分为N沟耗尽型和增强型;P沟耗尽型和增强型四大类.见下图: 3.场效应管的主要参数: Idss —饱和漏源电流.是指结型或耗尽型绝缘栅场效应管中,栅极电压UGS=0时的漏源电流. Up —夹断电压.是指结型或耗尽型绝缘栅场效应管中,使漏源间刚截止时的栅极电压. Ut —开启电压.是指增强型绝缘栅场效管中,使漏源间刚导通时的栅极电压. gM —跨导.是表示栅源电压UGS —对漏极电流ID的控制能力,即漏极电流ID变化量与栅源电压UGS变化量的比值.gM 是衡量场效应管放大能力的重要参数. BVDS —漏源击穿电压.是指栅源电压UGS一定时,场效应管正常工作所能承受的最大漏源电压.这是一项极限参数,加在场效应管上的工作电压必须小于BVDS. PDSM —最大耗散功率,也是一项极限参数,是指场效应管性能不变坏时所允许的最大漏源耗散功率.使用时,场效应管实际功耗应小于PDSM并留有一定余量. IDSM —最大漏源电流.是一项极限参数,是指场效应管正常工作时,漏源间所允许通过的最大电流.场效应管的工作电流不应超过IDSM Cds---漏-源电容 Cdu---漏-衬底电容 Cgd---栅-源电容 Cgs---漏-源电容 Ciss---栅短路共源输入电容 Coss---栅短路共源输出电容 Crss---栅短路共源反向传输电容 D---占空比(占空系数,外电路参数) di/dt---电流上升率(外电路参数) dv/dt---电压上升率(外电路参数) ID---漏极电流(直流) IDM---漏极脉冲电流 ID(on)---通态漏极电流 IDQ---静态漏极电流(射频功率管) 第20卷第6期 半 导 体 学 报 V o l.20,N o.6 1999年6月 CH I N ESE JOU RNAL O F SE M I CONDU CTOR S June,1999 多晶硅薄膜应力特性研究 张国炳 郝一龙 田大宇 刘诗美 王铁松 武国英 (北京大学微电子学研究所 北京 100871) 摘要 本文报道了低压化学气相淀积(L PCVD)制备的多晶硅薄膜内应力与制备条件、退火 ,用XRD、R ED等技术测量分析了多晶硅膜的微结构组成.结果表明,L PCVD制备的多晶硅薄膜具有本征压应力,其内应力受淀积条件、微结 构组成等因素的影响.采用快速退火(R TA)可以使其压应力松弛,减小其内应力,并可使其转 变成为本征张应力,以满足在微机电系统(M E M S)制备中的要求. PACC:6220,7360F,6860 1 引言 多晶硅薄膜由于其特有的导电特性和易于实现自对准工艺的优点,在大规模集成电路(VL S I)的制备中有着广泛的应用.对多晶硅薄膜的导电特性已进行了深入的研究[1].近年来,随着集成电路的发展,特别是微机电系统(M E M S)的兴起,多晶硅膜作为M E M S中的基本结构材料,其机械特性直接影响着器件的性能和稳定性、可靠性. 在M E M S应用中要求多晶硅膜本身具有较小的张应力且膜内有小的应力梯度,如果多晶硅膜内应力过大,会使M E M S结构层形变甚至断裂,造成器件失效.所以,控制制备工艺条件,使其具有较小的张应力,成为M E M S制造工艺中的一个很关键的问题[2,3].本文对L PCVD多晶硅薄膜的应力特性进行了实验研究,主要包括:制备工艺条件、退火温度和时间、掺杂浓度和微结构组成对其应力特性的影响.实验中采用薄膜全场应力测试系统测量薄膜的应力,用X光衍射(XRD)及反射电子衍射(R ED)等技术测量分析了多晶硅膜的微结构组成. 2 实验 2.1 实验样品制备 实验样品采用在N型(100)单晶硅衬底热生长300~500nm厚的Si O2膜;再用低压化学气相淀积生长多晶硅薄膜,工艺条件为:淀积温度分别为575℃和610℃,压力30Pa,硅烷 张国炳 男,1937年出生,教授,从事半导体器件物理及VL S I和M E M S中薄膜结构特性及应用研究 郝一龙 男,1963年出生,副研究员,从事VL S I多层互连技术及M E M S器件和制备工艺研究 1998202213收到,1998208225定稿 多晶硅薄膜材料同时具有单晶硅材料的高迁移率及非晶硅材料的可大面积、低成本制备的优点。因此,对于多晶硅薄膜材料的研究越来越引起人们的关注,多晶硅薄膜的制备工艺可分为两大类:一类是高温工艺,制备过程中温度高于600℃,衬底使用昂贵的石英,但制备工艺较简单。另一类是低温工艺,整个加工工艺温度低于600℃,可用廉价玻璃作衬底,因此可以大面积制作,但是制备工艺较复杂。 目前制备多晶硅薄膜的方法主要有如下几种: 低压化学气相沉积(LPCVD)这是一种直接生成多晶硅的方法。LPCVD是集成电路中所用多晶硅薄膜的制备中普遍采用的标准方法,具有生长速度快,成膜致密、均匀、装片容量大等特点。多晶硅薄膜可采用硅烷气体通过LPCVD法直接沉积在衬底上,典型的沉积参数是:硅烷压力为13.3~26.6Pa,沉积温度Td=580~630℃,生长速率5~10nm/min。由于沉积温度较高,如普通玻璃的软化温度处于500~600℃,则不能采用廉价的普通玻璃而必须使用昂贵的石英作衬底。LPCVD法生长的多晶硅薄膜,晶粒具有择优取向,形貌呈“V”字形,内含高密度的微挛晶缺陷,且晶粒尺寸小,载流子迁移率不够大而使其在器件应用方面受到一定限制。虽然减少硅烷压力有助于增大晶粒尺寸,但往往伴随着表面粗糙度的增加,对载流子的迁移率与器件的电学稳定性产生不利影响。 固相晶化(SPC)所谓固相晶化,是指非晶固体发生晶化的温度低于其熔融后结晶的温度。这是一种间接生成多晶硅的方法,先以硅烷气体作为原材料,用LPCVD方法在550℃左右沉积a-Si:H薄膜,然后将薄膜在600℃以上的高温下使其熔化,再在温度稍低的时候出现晶核,随着温度的降低熔融的硅在晶核上继续晶化而使晶粒增大转化为多晶硅薄膜。使用这种方法,多晶硅薄膜的晶粒大小依赖于薄膜的厚度和结晶温度。退火温度是影响晶化效果的重要因素,在700℃以下的退火温度范围内,温度越低,成核速率越低,退火时间相等时所能得到的晶粒尺寸越大;而在700℃以上,由于此时晶界移动引起了晶粒的相互吞并,使得在此温度范围内,晶粒尺寸随温度的升高而增大。经大量研究表明,利用该方法制得的多晶硅晶粒尺寸还与初始薄膜样品的无序程度密切相关,T.Aoyama等人对初始材料的沉积条件对固相晶化的影响进行了研究,发现初始材料越无序,固相晶化过程中成核速率越低,晶粒尺寸越大。由于在结晶过程中晶核的形成是自发的,因此,SPC多晶硅薄膜晶粒的晶面取向是随机的。相邻晶粒晶面取向不同将形成较高的势垒,需要进行氢化处理来提高SPC多晶硅的性能。这种技术的优点是能制备大面积的薄膜,晶粒尺寸大于直接沉积的多晶硅。可进行原位掺杂,成本低,工艺简单,易于形成生产线。由于SPC是在非晶硅熔融温度下结晶,属于高温晶化过程,温度高于600℃,通常需要1100℃左右,退火时间长达10个小时以上,不适用于玻璃基底,基底材料采用石英或单晶硅,用于制作小尺寸器件,如液晶光阀、摄像机取景器等。准分子激光晶化(ELA)激光晶化相对于固相晶化制备多晶硅来说更为理想,其利用瞬间激光脉冲产生的高能量入射到非晶硅薄膜表面,仅在薄膜表层100nm厚的深度产生热能效应,使a-Si薄膜在瞬间达到1000℃左右,从而实现a-Si向p-Si的转变。在此过程中,激光脉冲的瞬间(15~50ns)能量被a-Si薄膜吸收并转化为相变能,因此,不会有过多的热能传导到薄膜衬底,合理选择激光的波长和功率,使用激光加热就能够使a-Si薄膜达到熔化的温度且保证基片的温度低于450℃,可以采用玻璃基板作为衬底,既实现了p-Si薄膜的制备,又能满足LCD及OEL对透明衬底的要求。其主要优点为脉冲宽度短(15~50ns),衬底发热小。通过选择还可获得混合晶化,即多晶硅和非晶硅的混合体。准分子激光退火晶化的机理:激光辐射到a-Si的表面,使其表面在温度到达熔点时即达到了晶化域值能量密度Ec。a-Si在激光辐射下吸收能量,激发了不平衡的电子-空穴对,增加了自由电子的导电能量,热电子-空穴对在热化时间内用无辐射复合的途径将自己的能量传给晶格,导致近表层极其迅速的升温,由于非晶硅材料具有大量的隙态和深能级,无辐射跃迁是主要的复合过程,因而具有较高的光热转换效率,若激光的能量密度达到域值能量密度Ec 时,即半导体加热至熔点温度,薄膜的表面会熔化,熔化的前沿会以约10m/s的速度深入材料内部, 多晶硅薄膜的制备方法 2010年01月21日作者:胡志鹏来源:中国电源博览总第106期编辑:杨宇 摘要:本文介绍了太阳能多晶硅薄膜的主要制备方法。其中化学气相沉积法(CVD)是制备多晶硅薄膜最广泛使用的方法,其中主要有等离子体增强化学气相沉积(PECVD)法、甚高频等离子体增强化学气相沉积系统(VHF-PECVD)、低压化学气相沉积LPCVD和快速热化学气相沉积(RTCVD)。固相晶化技术(SPC)是指通过使固态下的非晶硅薄膜的硅原子被激活,重组,从而使非晶硅薄膜转化为多晶硅薄膜的晶化技术,其中主要包括常规高温炉退火、金属诱导晶化(MIC)。另外还有金属诱导非晶硅晶化。 关键词:太阳能多晶硅薄膜制备方法 为了减少材料浪费,降低成本,单晶硅和多晶硅太阳能电池都在朝薄型化发展。目前晶体硅薄膜电池的晶粒大小从纳晶直到毫米级都有,为了方便,光伏界将它们统称为多晶硅薄膜太阳能电池。由于多晶硅薄膜生产成本低、效率稳定性好、光电转换效率高,近年来随着人们在陷光技术、钝化技术以及载流子束缚等技术方面不断取得进展,多晶硅薄膜电池的研究日益受到人们的重视,未来将成为太阳能电池的主要竞争者。在研究怎样把硅片切薄的同时,人们加大了对多晶硅薄膜电池的研究。 制备多晶硅薄膜的方法有很多种,其中化学气相沉积法(CVD)是制备多晶硅薄膜最广泛使用的方法。在这种方法中,气源,例如硅烷(SiH4),可以在等离子体(PECVD)、催化作用(Hot-Wire CVD)等方法中有几种不同的可行性的分解过程。分解后的物质在经过一系列的气相反应后抵达衬底并沉积生长。在多数情况下,用氢气稀释后的气源来制备多晶硅薄膜,而用纯硅烷来制备非晶硅薄膜。然而,电子束蒸发法(EBE)也有着它独特的优点:相比气相沉积法使用气源,以固体硅材料作为原料的EBE可以有更高的原料利用率。此外,为了获得更高质量的多晶硅薄膜,还可以通过两步法(Two Steps Process)来制备多晶硅薄膜,即:先用CVD或者电子束蒸发(EBE)法制得非晶硅薄膜,再经固相晶化法(SPC)或者快速热处理法(RTP)等进一步制得多晶硅薄膜。 一、化学气相沉积法 1.等离子体增强化学气相沉积(PECVD)法 等离子体增强化学气相沉积法(PEcvD)l61是化学气相沉积方法的一种,是在低压化学气相沉积的同时,利用辉光放电等离子体对过程施加影响,利用PECVD技术可以在非硅衬底上制备晶粒较小的多晶硅薄膜。 在用等离子体增强化学气相沉积方法来制备多晶硅薄膜的过程中,目前都是通入SiH4和H2两者的混合气体作为气源,如若仅仅引入纯SiH4气体,PECVD在衬底上面沉积而得的 多晶硅薄膜的制备方法 多晶硅薄膜材料同时具有单晶硅材料的高迁移率及非晶硅材料的可大面积、低成本制备的优点。因此,对于多晶硅薄膜材料的研究越来越引起人们的关注,多晶硅薄膜的制备工艺可分为两大类:一类是高温工艺,制备过程中温度高于600C ,衬底使用昂贵的石英,但制备工艺较简单。另一 类是低温工艺,整个加工工艺温度低于600C,可用廉价玻璃作衬底,因此可以大面积制作,但 是制备工艺较复杂。目前制备多晶硅薄膜的方法主要有如下几种: 低压化学气相沉积( LPCVD) 这是一种直接生成多晶硅的方法。LPCVD是集成电路中所用多晶硅薄膜的制备中普遍采 用的标准方法,具有生长速度快,成膜致密、均匀、装片容量大等特点。多晶硅薄膜可采用硅烷气体通过LPCVD法直接沉积在衬底上,典型的沉积参数是:硅烷压力为13.3?26.6Pa,沉积温 度Td=580?630C,生长速率5?10nm/min。由于沉积温度较高,如普通玻璃的软化温度处于 500? 600C,则不能采用廉价的普通玻璃而必须使用昂贵的石英作衬底。 LPCVD法生长的多晶硅薄膜,晶粒具有择优取向,形貌呈“ V'字形,内含高密度的微挛晶缺陷,且晶粒尺寸小,载流子迁移率不够大而使其在器件应用方面受到一定限制。虽然减少硅 烷压力有助于增大晶粒尺寸,但往往伴随着表面粗糙度的增加,对载流子的迁移率与器件的电学稳定性产生不利影响。 固相晶化 (SPC) 所谓固相晶化,是指非晶固体发生晶化的温度低于其熔融后结晶的温度。这是一种间接 生成多晶硅的方法,先以硅烷气体作为原材料,用LPCVD方法在550C左右沉积a-Si:H 薄膜, 然后将薄膜在600C以上的高温下使其熔化,再在温度稍低的时候岀现晶核,随着温度的降低熔融的硅在晶核上继续晶化而使晶粒增大转化为多晶硅薄膜。使用这种方法,多晶硅薄膜的晶粒大 小依赖于薄膜的厚度和结晶温度。退火温度是影响晶化效果的重要因素,在700C以下的退火温 度范围内,温度越低,成核速率越低,退火时间相等时所能得到的晶粒尺寸越大;而在700C以上,由于此时晶界移动引起了晶粒的相互吞并,使得在此温度范围内,晶粒尺寸随温度的升高而增大。经大量研究表明,利用该方法制得的多晶硅晶粒尺寸还与初始薄膜样品的无序程度密切相关, T.Aoyama 等人对初始材料的沉积条件对固相晶化的影响进行了研究,发现初始材料越无序,固相晶化过程中成核速率越低,晶粒尺寸越大。由于在结晶过程中晶核的形成是自发的,因此, SPC多晶硅薄膜晶粒的晶面取向是随机的。相邻晶粒晶面取向不同将形成较高的势垒,需要进行氢化处理来提高 SPC多晶硅的性能。这种技术的优点是能制备大面积的薄膜,晶粒尺寸大于直接 沉积的多晶硅。可进行原位掺杂,成本低,工艺简单,易于形成生产线。由于SPC是在非 晶硅熔融温度下结晶,属于高温晶化过程,温度高于600C,通常需要1100C左右,退火时 间长达10 个小时以上,不适用于玻璃基底,基底材料采用石英或单晶硅,用于制作小尺寸器件,如液晶光阀、摄像机取景器等。 准分子激光晶化 (ELA) 激光晶化相对于固相晶化制备多晶硅来说更为理想,其利用瞬间激光脉冲产生的高能量入射到非晶硅薄膜表面,仅在薄膜表层100nm厚的深度产生热能效应,使 a-Si薄膜在瞬间达到 晶体管的输入输出特性曲线详解 届别 系别 专业 班级 姓名 指导老师 二零一二年十月 晶体管的输入输出特性曲线详解 学生姓名:指导老师: 摘要:晶体三极管,是半导体基本元器件之一,具有电流放大作用,是电子电路的核心元件。 根据晶体管的结构进行分类,晶体管可以分为:NPN型晶体管和PNP 型晶体管。依据晶体管两个PN结的偏置情况,晶体管的工作状态有放大、饱和、截止和倒置四种。晶体管的性能可以有三个电极之间的电压和电流关系来反映,通常称为伏安特性。 生产厂家还给出了各种管子型号的参数也能表示晶体管的性能。利用晶体管制成的放大电路的可以是把微弱的信号放大到负载所需的数值 晶体管是一种半导体器件,放大器或电控开关常用。晶体管是规范操作电脑,手机,和所有其他现代电子电路的基本构建块。由于其响应速度快,准确性,晶体管可用于各种各样的数字和模拟功能,包括放大,开关,稳压,信号调制和振荡器。晶体管可独立包装或在一个非常小的的区域,可容纳一亿或更多的晶体管集成电路的一部分。 关键字:晶体管、输入输出曲线、放大电路的静态分析和动态分析。 【Keywords】The transistor, the input/output curve, amplifying circuit static analysis and dynamic analysis. 一、晶体管的基本结构 晶体三极管,是半导体基本元器件之一,具有电流放大作用,是电子电路的核心元件。三极管是在一块半导体基片上制作两个相距很近的PN结,两个PN结把正块半导体分成三部分,中间部分是基区,两侧部分是发射区和集电区,排列方式有PNP和NPN两种,如图 1-1(a)、(b)所示。从三个区引出相应的电极,发射极,基极,集电极,各用“E”(或“e”)、“B”(或“b”)、“C”(或“c”)表示。 发射区和基区之间的PN结叫发射结,集电区和基区之间的PN结叫集电极。基区很薄,而发射区较厚,杂质浓度大,PNP型三极管发射区"发射"的是空穴,其移动方向与电流方向一致,故发射极箭头向里;NPN型三极管发射区"发射"的是自由电子,其移动方向与电流方向相反,故发射极箭头向外。发射极箭头向外。发射极箭头指向也是PN结在正向电压下的导通方向。硅晶体三极管和锗晶体三极管都有PNP型和NPN型两种类型。当前国内生产的锗管多为PNP型(3A 系列),硅管多为NPN型(3D系列)。 华南理工大学学报(自然科学版)第38卷第10期Journa l o f South C hina U niversity o f Techno l o g y V o.l 38 N o .102010年10月 (N atura l Science Editi o n) O ctober 2010 文章编号:1000 565X (2010)10 0024 06 收稿日期:2009 11 23 *基金项目:广东省教育部产学研结合项目(2008A 090400011) 作者简介:黄君凯(1963 ),男,在职博士生,暨南大学教授,主要从事多晶硅薄膜晶体管物理特性和建模研究.E m a i:l h j k196310@https://www.doczj.com/doc/9b9852174.html, 多晶硅薄膜晶体管的泄漏电流和噪声模型 * 黄君凯1 郑学仁1 邓婉玲 2 (1.华南理工大学电子与信息学院,广东广州510640;2.暨南大学信息科学技术学院,广东广州510630) 摘 要:为了建立适用于电路仿真器的泄漏区模型,通过泄漏电流、激活能和低频噪声等研究了多晶硅薄膜晶体管的泄漏产生机制.在不同的电场条件下,基于不同的泄漏产生机 制,提出了产生-复合率的分区近似计算模型,并统一成适用于1 106~5 108 V /m 电场范围的泄漏电流模型.同时,建立了中低电场区的激活能模型和泄漏区低频噪声紧凑模型.将模型仿真结果与实验数据进行了比较,证明了所建立模型的有效性,且模型适用于电路仿真器. 关键词:多晶硅;薄膜晶体管;泄漏电流;激活能;低频噪声模型中图分类号:TN 303 do :i 10.3969/.j issn.1000 565X .2010.10.005 多晶硅薄膜晶体管的应用日益广泛,特别是在 有源液晶显示器、固体图像传感器等领域中的发展极为迅速[1] .当作为开关元件应用时,器件的电流开关比十分重要,但由于多晶硅薄膜晶体管的关态电流(通常称为泄漏电流)通常比较大,一定程度上限制了其应用范围.因此,对多晶硅薄膜晶体管泄漏电流的产生机制以及建模进行研究具有现实的意义. 高密度的陷阱态对多晶硅薄膜晶体管的泄漏电流特性产生重要的影响.在反向工作区,一般认为陷阱态引起的泄漏电流的产生机制有:载流子热发射[2]、Poole Frenkel (PF)场助热发射[3]、载流子从陷阱的直接隧穿(TAT) [4] 、热离子场助发射(TFE ) [5] 、 带到带隧穿(BBT)[6] 、多晶硅薄膜的电阻电流[7] 等. 泄漏电流的产生机制依赖于电场和温度,尤其是电场.由于薄膜晶体管反向工作时,漏区和沟道之间形成反偏pn 结,大部分电势都施加在反偏pn 结上,因此存在较大的电场,激发了载流子的产生-复合(G R ).在不同的偏置和温度条件下,占主导地位的发射产生机制将有所不同,一直以来,学者们对泄漏电流的产生机制存在争论.文中从多晶硅薄膜晶体管的 G R 模型[8] 出发,分析了不同电场条件下泄漏电流的 产生机制,分别建立了泄漏区的激活能模型和低频噪 声模型,并通过实验验证了所建模型的有效性. 1 G R 模型分析及泄漏电流的产生机制 文献[8]中综合考虑了泄漏电流的多种产生机制,提出了泄漏区的G R 模型: U G-R = E C E V [R D (E T )+R A (E T )]d E T (1) R A (E T )=(np -n 2 i )N A (E T ) n +n 1c p ( F + Cou l p )+p +p 1 c n (1+ D irac n )(2) R D (E T )= (np -n 2 i )N D (E T ) n +n 1c p (1+ D irac p )+p +p 1 c n ( F + Cou l n )(3) N A (E T )=N D eep A exp E T -E C E Deep A +N Ta il A exp E T -E C E Ta il A (4) N D (E T )=N D eep D exp E V -E T E Deep D +N Tail D exp E V -E T E Tail D (5) 目录 一、三极管特性曲线分析 (1) 1.1三极管结构 (1) 1.2 三极管输入特性曲线 (2) 1.3 三极管输出特性曲线 (2) 二、三极管应用举例 (3) 2.1 三极管在放大状态下的应用 (3) 2.2 三极管在开关状态下的应用 (3) 三、线性电路和非线性电路 (4) 3.1线性电路理论 (4) 3.2 非线性电路理论 (5) 3.3 线性电路的分析应用举例 (6) 3.4 非线性电路的分析应用举例 (7) 四、数字电路和模拟电路 (8) 4.1 数字电路 (8) 4.2 模拟电路 (8) 4.3数字电路和模拟电路区别与联系 (9) 五、总结与体会 (9) 六、参考文献 (10) 三极管输入输出曲线分析 ——谈线性电路与非线性电路 摘要:三极管是电路分析中非常重要的一个元器件。本文主要分析了三极管输入输出特性曲线,介绍了线性电路和非线性电路的理论在分析工具的不同之处。同时,线性电路和非线性电路在分析电路时各有着不同的用处。最后,介绍了数字电路及模拟电路区别与联系。 关键词:三极管;数字电子技术;模拟电子技术 一、三极管特性曲线分析 1.1三极管结构 双极结型三极管是由两个PN结背靠背构成。三极管按结构不同一般可分为PNP和NPN 两种。 图1-1 三极管示意图及符号 PNP型三极管和NPN型三极管具有几乎等同的电流放大特性,以下讨论主要介绍NPN 型三极管工作原理。NPN型三极管其两边各位一块N型半导体,中间为一块很薄的P型半导体。这三个区域分别为发射区、集电区和基区,从三极管的三个区各引出一个电极,相应的称为发射极(E)、集电极(C)和基极(B)。虽然发射区和集电区都是N型半导体,但是发射区的掺杂浓度比集电区的掺杂浓度要高得多。另外在几何尺寸上,集电区的面积比发射区的面积要大。由此可见,发射区和集电区是不对称的。 双极型三极管有三个电极:发射极(E)、集电极(C)、基极(B),其中两个可以作为输入,两个可以作为输出,这样就有一个电极是公共电极。三种接法就有三种组态:共发射极接法(CE)、共基极接法(CC)、共集电极接法(CB)。这里只以共射接法为例分析其输入 多晶硅薄膜的制备方法 Document serial number【UU89WT-UU98YT-UU8CB-UUUT-UUT108】 多晶硅薄膜的制备方法免费!!免费获得在我站的广告 2008-12-26 20:43:46 作者:leilei 来源:希萌光伏商务网 多晶硅薄膜材料同时具有单晶硅材料的高迁移率及非晶硅材料的可大面积、低成本制备的优点。因此,对于多晶硅薄膜材料的研究越来越引起人们的关注,多晶硅薄膜... 多晶硅薄膜材料同时具有单晶硅材料的高迁移率及非晶硅材料的可大面积、低成本制备的优点。因此,对于多晶硅薄膜材料的研究越来越引起人们的关注,多晶硅薄膜的制备工艺可分为两大类:一类是高温工艺,制备过程中温度高于600℃,衬底使用昂贵的石英,但制备工艺较简单。另一类是低温工艺,整个加工工艺温度低于600℃,可用廉价玻璃作衬底,因此可以大面积制作,但是制备工艺较复杂。目前制备多晶硅薄膜的方法主要有如下几种: 低压化学气相沉积(LPCVD) 这是一种直接生成多晶硅的方法。LPCVD是集成电路中所用多晶硅薄膜的制备中普遍采用的标准方法,具有生长速度快,成膜致密、均匀、装片容量大等特点。多晶硅薄膜可采用硅烷气体通过LPCVD法直接沉积在衬底上,典型的沉积参数是:硅烷压力为~,沉积温度Td=580~630℃,生长速率5~10nm/min。由于沉积温度较高,如普通玻璃的软化温度处于 500~600℃,则不能采用廉价的普通玻璃而必须使用昂贵的石英作衬底。 LPCVD法生长的多晶硅薄膜,晶粒具有择优取向,形貌呈“V”字形,内含高密度的微挛晶缺陷,且晶粒尺寸小,载流子迁移率不够大而使其在器件应用方面受 多晶硅薄膜晶体管特性研究 摘要 多晶硅薄膜晶体管(polysilicon thin film transiston)因其高迁移率、高速高集成化、p 型和n型导电模式、自对准结构以及耗电小、分辨率高等优点,近年来被广泛的应用于液晶显示器。随着器件尺寸减小至深亚微米,热载流子退化效应所致器件以及电路系统的可靠性是器件的长期失效问题。 本文主要研究热载流子效应。首先,研究热载流子退化与栅极应力电压,漏极应力电压及应力时间的依赖关系。其次,漏极轻掺杂(Light Doped Drain,LDD)结构是提高多晶硅薄膜晶体管抗热载流子特性的一种有效方法,研究了LDD结构多晶硅薄膜晶体管的结构参数对器件可靠性的影响。 关键词:多晶硅薄膜晶体管热载流子效应可靠性 Study on Characteristics of polysilicon thin film transistor Abstract Today, p-Si TFTs are used broadly in display devices because of its high field effect mobility,high integration and high speed,high definition display,n channel and p channel capability,low power consumption and self-aligned structures. With the device scaling down to deep-submicrometer, the reliability of the device circuit system induced by hot carrier effect is long-term failure. Hot carrier effects is studied. Firstly,we mainly study the dependence between hot carrier degradation and gate-stress voltage,drain-stress voltage and stress time.Secondly,the structure of Light Doped Drain is an effective means to resist hot carrier effect ,the influence of parameters of LDD structures on reliability of p-Si TFT was investigated. Keywords:p-Si TFT;hot carrier effect;reliability 绝缘栅场效应晶体管工作原理及特性 场效应管(MOSFET)是一种外形与普通晶体管相似,但控制特性不同的半导体器件。它的输入电阻可高达1015W,而且制造工艺简单,适用于制造大规模及超大规模集成电路。场效应管也称为MOS管,按其结构不同,分为结型场效应晶体管和绝缘栅场效应晶体管两种类型。在本文只简单介绍后一种场效应晶体管。 绝缘栅场效应晶体管按其结构不同,分为N沟道和P沟道两种。每种又有增强型和耗尽型两类。下面简单介绍它们的工作原理。 1、增强型绝缘栅场效应管 2、图6-38是N沟道增强型绝缘栅场效应管示意图。 在一块掺杂浓度较低的P型硅衬底上,用光刻、扩散工艺制作两个高掺杂浓度的N+区,并用金属铝引出两个电极,称为漏极D和源极S如图6-38(a)所示。然后在半导体表面覆盖一层很薄的二氧化硅(SiO2)绝缘层,在漏-源极间的绝缘层上再装一个铝电极,称为栅极G。另外在衬底上也引出一个电极B,这就构成了一个N沟道增强型MOS管。它的栅极与其他电极间是绝缘的。图6-38(b)所示是它的符号。其箭头方向表示由P(衬底)指向N(沟道)。 图6-38 N沟道增强型场效应管 场效应管的源极和衬底通常是接在一起的(大多数场效应管在出厂前已联结好)。从图 6-39(a)可以看出,漏极D和源极S之间被P型存底隔开,则漏极D和源极S之间是两个背靠背的PN结。当栅-源电压UGS=0时,即使加上漏-源电压UDS,而且不论UDS的极性如何,总有一个PN结处于反偏状态,漏-源极间没有导电沟道,所以这时漏极电流ID≈0。 若在栅-源极间加上正向电压,即UGS>0,则栅极和衬底之间的SiO2绝缘层中便产生一个垂直于半导体表面的由栅极指向衬底的电场,这个电场能排斥空穴而吸引电子,因而使栅极附近的P型衬底中的空穴被排斥,剩下不能移动的受主离子(负离子),形成耗尽层,同时P衬底中的电子(少子)被吸引到衬底表面。当UGS数值较小,吸引电子的能力不强时,漏-源极之间仍无导电沟道出现,如图6-39(b)所示。UGS增加时,吸引到P衬底表面层的电子就增多,当UGS达到某一数值时,这些电子在栅极附近的P衬底表面便形成一个N型薄层,且与两个N+区相连通,在漏-源极间形成N型导电沟道,其导电类型与P衬底相反,故又称为反型层,如图6-39(c)所示。UGS越大,作用于半导体表面的电场就越强,吸引到P衬底 多晶硅薄膜的制备方法 快速热退火(RTA)一般而言,快速退火处理过程包含三个阶段:升温阶段、稳定阶段和冷却阶段。当退火炉的电源一打开,温度就随着时间而上升,这一 阶段称为升温阶段。单位时间内温度的变化量是很容易控制的。在升温过程结 束后,温度就处于一个稳定阶段。最后,当退火炉的电源关掉后,温度就随着 时间而降低,这一阶段称为冷却阶段。用含氢非晶硅作为初始材料,进行退火 处理。平衡温度控制在600℃以上,纳米硅晶粒能在非晶硅薄膜中形成,而且 所形成的纳米硅晶粒的大小随着退火过程中的升温快慢而变化。在升温过程中,若单位时间内温度变化量较大时(如100℃/s),则所形成纳米硅晶粒较小 (1.6~15nm);若单位时间内温度变化量较小(如1℃/s),则纳米硅粒较大 (23~46nm)。进一步的实验表明:延长退火时间和提高退火温度并不能改变所形成的纳米硅晶粒的大小;而在退火时,温度上升快慢直接影响着所形成的纳米 硅晶粒大小。为了弄清楚升温量变化快慢对所形成的纳米硅大小晶粒的影响, 采用晶体生长中成核理论。在晶体生长中需要两步:第一步是成核,第二步是 生长。也就是说,在第一步中需要足够量的生长仔晶。结果显示:升温快慢影 响所形成的仔晶密度。若单位时间内温度变化量大,则产生的仔晶密度大;反之,若单位时间内温度变化量小,则产生的仔晶密度小。RTA退火时升高退火温度 或延长退火时间并不能消除薄膜中的非晶部分,薛清等人提出一种从非晶硅中 分形生长出纳米硅的生长机理:分形生长。从下到上,只要温度不太高以致相 邻的纳米硅岛不熔化,那么即使提高退火温度或延长退火时间都不能完全消除 其中的非晶部分。RTA退火法制备的多晶硅晶粒尺寸小,晶体内部晶界密度大,材料缺陷密度高,而且属于高温退火方法,不适合于以玻璃为衬底制备多晶硅。等离子体增强化学反应气相沉积(PECVD)等离子体增强化学反应气相沉积(PECVD)法是利用辉光放电的电子来激活化学气相沉积反应的。起初,气体由于受到紫 外线等高能宇宙射线的辐射,总不可避免的有轻微的电离,存在着少量的电子。在充有稀薄气体的反应容器中引进激发源(例如,直流高压、射频、脉冲电源等),电子在电场的加速作用下获得能量,当它和气体中的中性粒子发生非弹性碰撞时,就有可能使之产生二次电子,如此反复的进行碰撞及电离,结果将产 生大量的离子和电子。由于其中正负粒子数目相等。故称为等离子体,并以发 光的形式释放出多余的能量,即形成"辉光"。在等离子体中,由于电子和离子第五代低温多晶硅薄膜晶体管液晶显示器件(ltpstftlcd

场效应晶体管特性

晶体管的特性曲线

激光晶化能量对多晶硅薄膜晶体管特性影响的研究

场效应管特性

多晶硅薄膜应力特性研究(1)

多晶硅薄膜材料同时具有单晶硅材料的高迁移率及非晶硅材料的可大面积

多晶硅薄膜的制备方法

多晶硅薄膜的制备方法

晶体管的输入输出特性曲线详解.

多晶硅薄膜晶体管的泄漏电流和噪声模型

三极管特性曲线分析

多晶硅薄膜的制备方法

多晶硅薄膜晶体管特性研究

绝缘栅场效应晶体管工作原理及特性

多晶硅薄膜的制备方法