青岛理工大学

实验报告

实验课程:计算机组成原理I Array实验日期:2014年10月15日,交报告日期:2014年11月日,成绩:

实验地点:现代教育技术中心305(计算机实验室)

计算机工程学院,计算机科学与技术专业,班级:计算122班

实验指导教师:龚玉玺批阅教师:龚玉玺

一、实验课题

一、主要元件设计

1.16位寄存器

功能要求:同步并行置数,异步复位(清零),三态输出,片选信号,读/写控制。

2.地址译码器

功能要求:3-8译码器

二、顶层设计

用层次结构设计的方法设计一个通用寄存器组。包括8个16位寄存器,1个地址译码器等元件。

功能要求:每个寄存器能够同步并行置数,异步复位(清零),三态输出。每个都可以(用地址)独立访问

三、仿真

设计仿真波形数据,要考虑到所有可能的情况。在实验报告中必须清楚说明仿真波形数据是怎样设计的。

四、深入的课题

①上面设计的通用寄存器组,每次只能访问一个寄存器。如果想同时访问两个寄存器,

应该怎样设计?

②16位的寄存器每次读/写都是一个16位字,如果需要写入的是8位的字,即将8

位的字写到16位寄存器的高8位或低8位(例如,16位寄存器A由AH和AL两个8位的寄存器组成),读出时,可一次读16位。应该怎样设计

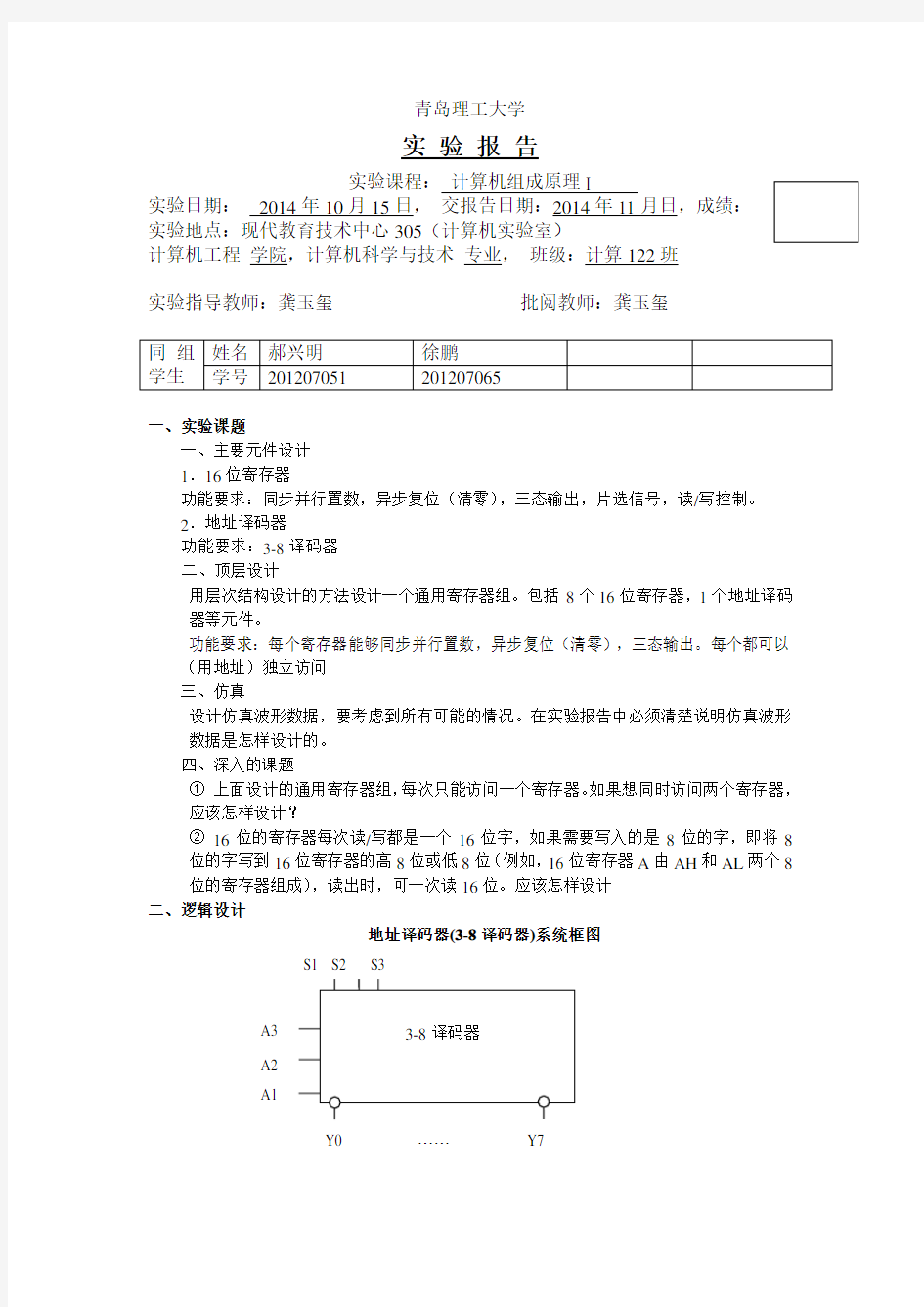

二、逻辑设计

端口说明:A(1-3):输入信号 S(1-3):使能端 Y(0-7):输出端口

功能表:

321逻辑函数:S A A A Y ???=)(0120,

S A A A Y ???=)(0121,S A A A Y ???=)(0122 S A A A Y ???=)(0123,S A A A Y ???=)(0124,S A A A Y ???=)(0125 S A A A Y ???=)(0126,S A A A Y ???=)(0127

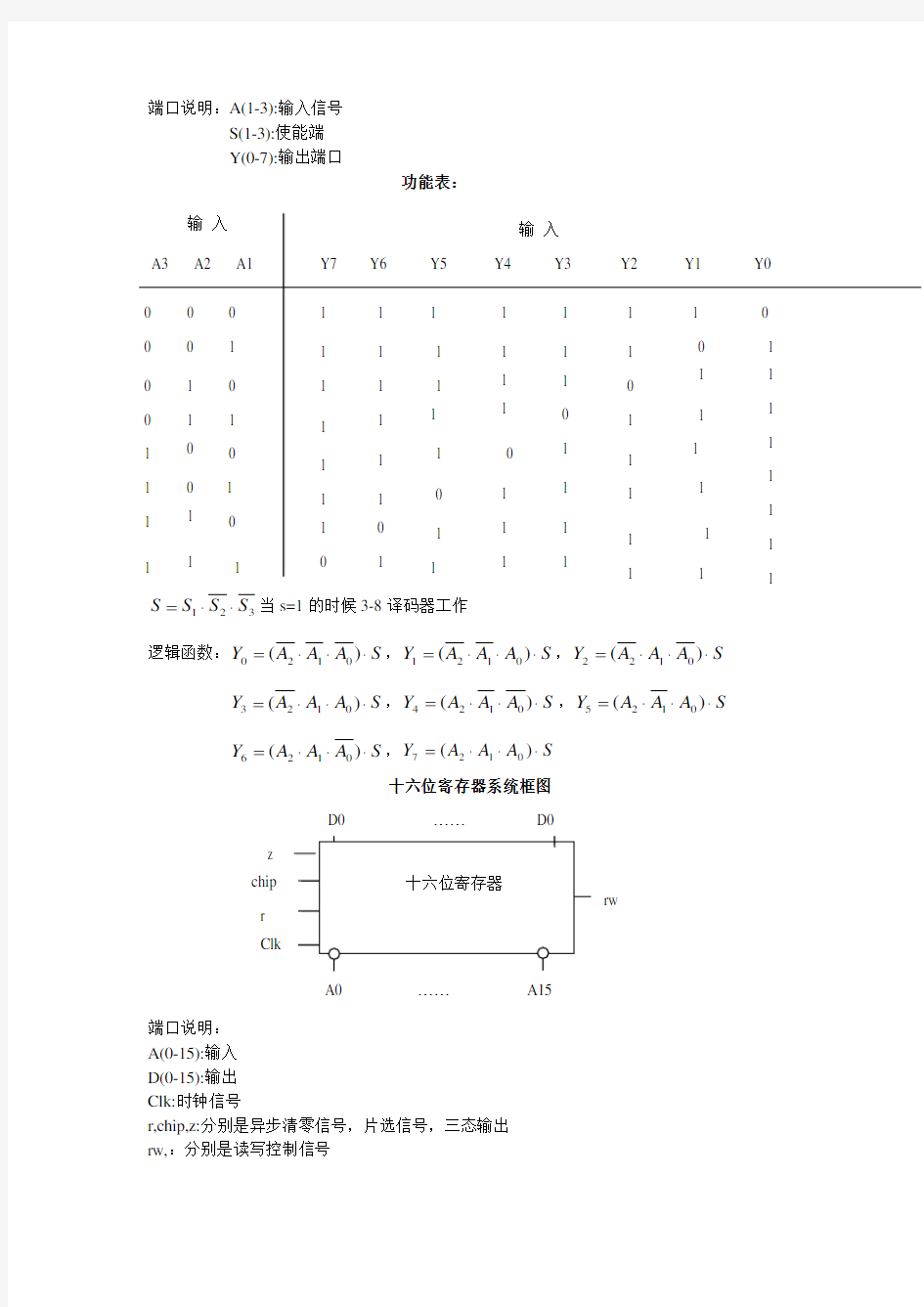

十六位寄存器系统框图

端口说明: A(0-15):输入 D(0-15):输出 Clk:时钟信号

r,chip,z:分别是异步清零信号,片选信号,三态输出 rw,:分别是读写控制信号

功能表:

十六位寄存器组系统框图

端口说明: AI(0-3):给译码器的输入

z,r,clk,rw:分别是三态输出,异步置零,时钟,读写控制 A(0-15):数据输入 D(0-15):数据输出

十六位寄存器逻辑图

1、3-8译码器:

--Decode

library ieee;

use ieee.std_logic_1164.all;

entity decode is

port

(

s1,s2,s3: in std_logic;--使能端

A : in std_logic_vector(2 downto 0);--输入

Y : out std_logic_vector(7 downto 0)--输出

);

end decode;

architecture de_behave of decode is

signal s: std_logic;

begin

s<=s1 and (not s2) and (not s3);

Y(0)<=not( ((not A(2)) and (not A(1)) and (not A(0))) and s );

Y(1)<=not( ((not A(2)) and (not A(1)) and A(0)) and s);

Y(2)<=not( ((not A(2)) and A(1) and (not A(0))) and s );

Y(3)<=not( (not A(2) and A(1) and A(0)) and s);

Y(4)<=not( (A(2) and (not A(1)) and (not A(0))) and s);

Y(5)<=not( (A(2) and (not A(1)) and A(0)) and s);

Y(6)<=not( (A(2) and A(1) and (not A(0))) and s);

Y(7)<=not( (A(2) and A(1) and A(0)) and s);

end de_behave;

2、十六位寄存器:

--十六位寄存器

library ieee;

use ieee.std_logic_1164.all;

entity Sixteen_Register is

port

( --clk:时钟信号(上升沿有效)

--r:异步清零信号(高电平有效)

--chip:片选信号(低电平有效)

--z:三态门(z=1三态门打开)

--load:同步置数信号

--rw:读写控制信号rw = 1 is Read ,or is Write

clk,r,chip,z,rw : in std_logic ;

a : in std_logic_vector(15 downto 0);

d : out std_logic_vector(15 downto 0)

);

end Sixteen_Register;

architecture behave of Sixteen_Register is

signal sign : std_logic_vector(15 downto 0);--中间信号begin

process(clk,r,chip,z,rw)

begin

if chip = '0' then --片选信号有效时候

if r = '1' then --异步置零

sign <= (others=>'0');

elsif rising_edge(clk) then --clk上升沿

if rw = '1' then

d <= sign;

else --时钟上升沿,写

sign<=a;

end if;

if z = '0' then

d<=(others=>'Z');

end if;

end if;

else

d<=(others=>'Z');

end if;

end process;

end behave;3、十六位寄存器组

--通用寄存器组

library ieee;

use ieee.std_logic_1164.all;

entity Sixteen_Register_group is

port(

--A是选择信号,端口和3-8译码器相连

--clk是时钟信号

--load是同步置数控制端

--rw是读写控制

--r异步清零

--load:同步置数信号

--z三态门

--a输入

--d输出

s1,s2,s3 : in std_logic;

AI : in std_logic_vector(2 downto 0);

clk,rw,r,z: in std_logic;

a : in std_logic_vector(15 downto 0);

d : out std_logic_vector(15 downto 0)

);

end Sixteen_Register_Group;

architecture struct of Sixteen_Register_Group is

signal Y : std_logic_vector(7 downto 0);--暂时存储3-8译码器产生的信号

component Sixteen_Register --十六位寄存器元件说明

port

( --clk:时钟信号(上升沿有效)

--r:异步清零信号(高电平有效)

--chip:片选信号(低电平有效)

--z:三态门(z=1三态门打开)

--load:同步置数信号

--rw:读写控制信号rw = 1 is Read ,or is Write

clk,r,chip,z,rw : in std_logic ;

a : in std_logic_vector(15 downto 0);

d : out std_logic_vector(15 downto 0)

);

end component;

component decode --3-8译码器元件说明

port

(

s1,s2,s3: in std_logic;--使能端

A : in std_logic_vector(2 downto 0);--输入

Y : out std_logic_vector(7 downto 0)--输出

);

end component;

begin

--3-8译码器的一次例化

TEdecode: decode port map

(A=>AI , Y=>Y,s1=>s1,s2=>s2,s3=>s3);

--十六位寄存器的例化

G0:Sixteen_Register port map

(clk=>clk,r=>r,z=>z,rw=>rw,chip=>Y(0),a=>a,d=>d);

G1:Sixteen_Register port map

(clk=>clk,r=>r,z=>z,rw=>rw,chip=>Y(1),a=>a,d=>d);

G2:Sixteen_Register port map

(clk=>clk,r=>r,z=>z,rw=>rw,chip=>Y(2),a=>a,d=>d);

G3:Sixteen_Register port map

(clk=>clk,r=>r,z=>z,rw=>rw,chip=>Y(3),a=>a,d=>d);

G4:Sixteen_Register port map

(clk=>clk,r=>r,z=>z,rw=>rw,chip=>Y(4),a=>a,d=>d);

G5:Sixteen_Register port map

(clk=>clk,r=>r,z=>z,rw=>rw,chip=>Y(5),a=>a,d=>d);

G6:Sixteen_Register port map

(clk=>clk,r=>r,z=>z,rw=>rw,chip=>Y(6),a=>a,d=>d);

G7:Sixteen_Register port map

(clk=>clk,r=>r,z=>z,rw=>rw,chip=>Y(7),a=>a,d=>d);

end struct;

四、仿真设计

3-8译码器仿真设计:

从它的功能表可以知道输入的数据是有限的且只有八组。故可以按照功能表对全部数据进行仿真。故仿真数据,大可以参考前边列出的功能表。

十六位寄存器仿真设计:

验证无工作状态功能:令chip=‘1’,若输出为Z则说明其没有工作。

验证异步清零功能:使chip=‘0’且r=‘1’,接着使chip=‘0’,clk处于上升沿,r=0,z=1,rw=‘1’。

若仿真结果是16个0则表明异步清零功能有效,且简洁验证了,读功

能是正确的。

验证写入寄存器的功能:使chip=‘0’且clk处于上升沿,r=‘0’,rw=0。接着读出数据,若读出的数据是这之前写入寄存器的数据则表明写功能正确。

验证读功能:使chip=‘0’且clk处于上升沿,r=‘0’,rw=‘1’。若仿真的结果是之前写入寄存器的数据,则辨明读功能是正确的。

仿真数据:(一个句号分割一组数据,不全的数据,则用仿真中的默认数据代替)

令chip=1。

令r=1。(异步清零)

令chip=‘0’,clk处于上升沿,r=0,z=1,rw=‘1’。(读出数据)

令chip=0, clk处于上升沿,r=0,z=1,rw=‘0。(写入数据)这里有一点奇怪的地方是,写入数据时z=1,即三态门打开了。其实读或者写入数据是由rw控制的,

此处设置此数据的目的在于验证程序的正确性。即:三态的数据是由z

控制的而不是其他信号。

令chip=‘0’,clk处于上升沿,r=0,z=1,rw=‘1’。(读出数据,用来验证写入功能的正确性)。

令chip=0,r=1,z=1。验证清零功能,它应该是不受三态输出的影响的。

令chip=‘0’,clk处于上升沿,r=0,z=1,rw=‘1’。(读出数据,读出的数据应该为全零) 令chip=0,r=0,z=0,rw=0,验证三态门,和写入寄存器的功能。输出应该是高祖态。

令chip=‘0’,clk处于上升沿,r=0,z=1,rw=‘1’。(读出数据)读出的数据应该和之前写入的数据一致。

对于以上仿真,每种情况可多输入几组数据,以尽可能避免偶然误差。

注意:对于chip不工作状态,我是用Z来代替的,它有可能使你和三态输出混淆,但是我实在不知道,该用什么样的数据来表示寄存器的不工作状态。

十六位寄存器组仿真设计:

对十六位寄存器组,共有8个寄存器。每一个寄存器都要进行功能验证,一、为了验证译码器的正确性;二、为了验证每个寄存器的功能是否都正确。(实际上这些寄存器都是由一

个模板复制而来,之所以每个都进行验证是为了查看每个组件之间的连接是否正确)。按

照十六位寄存器的仿真设计,对每一种片选信号都进行十六位寄存器的仿真。

五、结果分析讨论

1、3-8译码器功能仿真结果:

结果讨论:从仿真图可以看出对于每种输入,都可以得到和功能表一致的结果。故3-8译码器设计是正确的。

2、十六位寄存器仿真结果:

电子通信与软件工程 系2013-2014学年第2学期 《数字电路与逻辑设计实验》实验报告 --------------------------------------------------------------------------------------------------------------------- 班级: 姓名: 学号: 成绩: 同组成员: 姓名: 学号: --------------------------------------------------------------------------------------------------------------------- 一、 实验名称:集成计数器及寄存器的运用 二、实验目的: 1、熟悉集成计数器逻辑功能与各控制端作用。 2、掌握计数器使用方法。 三、 实验内容及步骤: 1、集成计数器74LS90功能测试。74LS90就是二一五一十进制异步计数器。逻辑简图为图8、1所示。 四、 五、 图8、1 六、 74LS90具有下述功能: ·直接置0(1)0(2)0(.1)R R ,直接置9(S9(1,·S,.:,=1) ·二进制计数(CP 、输入QA 输出) ·五进制计数(CP 2输入Q D Q C Q B 箱出) ·十进制计数(两种接法如图8.2A 、B 所示) ·按芯片引脚图分别测试上述功能,并填入表 8、1、表8、2、表8、3中。

图8、2 十进制计数器 2、计数器级连 分别用2片74LS90计数器级连成二一五混合进制、十进制计数器。 3、任意进制计数器设计方法 采用脉冲反馈法(称复位法或置位法)。可用74LS90组成任意模(M)计数器。图8、3就是用74LS90实现模7计数器的两种方案,图(A)采用复位法。即计数计到M异步清0。图(B)采用置位法,即计数计到M一1异步置0。 图8、3 74LS90 实现七进进制计数方法 (1)按图8、3接线,进行验证。 (2)设计一个九进制计数器并接线验证。 (3)记录上述实验的同步波形图。 四、实验结果:

寄存器组的设计与实现 第______ _________组 成员___ ____ ____ 实验日期___ _____ _____ 实验报告完成日期___________ 1、实验目的 1、学习掌握Quartus软件的基本操作; 2、理解寄存器组的工作原理和过程; 3、设计出寄存机组并对设计的正确性进行验证; 二、实验内容

1、设计出功能完善的寄存器组,并对设计的正确性进行验证。要求如下: (1)用图形方式设计出寄存器组的电路原理图 (2)测试波形时用时序仿真实现,先将不同的数据连续写入 4个寄存器后,再分别读出 (3)将设计文档封装成器件符号。 (4)数据的宽度最好是16位 2、能移位的暂存器实验,具体要求如下: (1)用图形方式设计出能移位的暂存器电路原理图,分别实 现左移、逻辑右移和算术右移。 (2)测试波形时要用时序仿真实现,测试数据不要全为0也 不要全为1,算术右移的测试数据要求为负数(即符号位为 1) (3)将设计文档封装成器件符号。 (4)数据的宽度最好是16位 三、能完善的寄存器组设计思想 1、对于寄存器组设计思路 利用具有三态功能的寄存器堆74670芯片进行设计,根据实验要求,需要设计16位的存储器组,则需要74670芯片4片,在寄存器组工作时,同时对4片74670芯片进行读写操作控制,封装后即可作为包含有4个寄存器的16位寄存器组在主机系统中调用。 2、对74670器件的学习 74670(三态输出4×4寄存器堆)提供4个4位的寄存器,在功能上可对4个寄存器去分别进行写操作和读操作。在寄存器进行写操作时,通过WB、WA两个寄存器选择端的组合和00、01、10、11、来选择寄存器,公国GWN写操作端控制进行三态控制,在GWN为低电平时将数据写入端数据D4D3D2D1写入该寄存器;在寄存

《计算机组成》实验报告 实验名称:运算器组成实验任课教师:李永华 学号:090342104 姓名:程立雪完成日期:2011-11-10 一实验目的 1、掌握算术逻辑运算加、减、乘、与的工作原理。 2、熟悉简单运算的数据传送通路。 3、验证实验台运算的8位加、减、与、直通功能。 4、验证实验台的4位乘4位功能。 5、按给定数据,完成几种指定的算术和逻辑运算。 二实验内容 (1)按图6所示,正确连接运算器模块与实验台上的电平开关K0-K15。由于运算C指示灯,8位数据开关SWO-SW7,T2,T4的连线已由印制电路板连好,故接线任务仅仅是完成有关控制信号与电平开关K0-K15的连线。正确设置开关DZ,DB,DP。用数据开关SWO-SW7向DR1和DR2寄存器置数。 1)置ALU-BUS=0,关闭ALU向数据总线DBUS的输出,置SW-BUS#=0,开启数据开关SWO-SW7向数据总线DBUS的输出。注意,对于数据总线DBUS(或者其他任何总线),在任一时刻,只能有一个数据向它输出。置IR/DBUS开关于DBUS位置,在数据开关SWO-SW7上设置各种数据,观察数据指示灯状态是否与数据开关状态一致。 2)置M1=1,选择DBUS作为DR1的数据源,置LDDR1=1,按QD按钮,则将DBUS的数据打入DR1。置M2=1。选择DBUS作为DR2的数据源,置LDDR2=1,按QD按钮,则将DBUS 的数据打入DR2。向DR1存入01010101,向DR2存入10101010。 3)置SW-BUS#=1,关闭数据长关SWO-SW7对数据总线的DBUS的输出;置ALU-BUS=1,开启ALU对DBUS的输出。选择S2=0,S1=0,S0=1,使运算器进行直通运算,通过DBUS指示灯验证DR2中的内容是否为第2步设置的值。令S2=0,S1=1,S0=0,使运算器进行加运算,通过DBUS指示灯验证DR1中的内容是否为第2步设置的值。在表4中填入控制信号状态与DBUS显示状态。 (2)验证运算器的算术运算和逻辑运算功能。 1)令DR1=01100011B,DR2=10110100B,正确选择S2,S1,S0,依次进行加、减、与、直通、乘实验,记下实验结果(数据和进位)并对结果进行分析。 2)令DR1=10110100B,DR2=01100011B,正确选择S2,S1,S0,依次进行加、减、与、直通、乘实验,记下实验结果(数据和进位)并对结果进行分析。 3)令DR1=01100011B,DR2=01100011B,正确选择S2,S1,S0,依次进行加、减、与、直通、乘实验,记下实验结果(数据和进位)并对结果进行分析。 4)令DR1=01001100,DR2=10110011,正确选择S2,S1,S0,依次进行加、减、与、直通、乘

寄存器实验报告

一、实验目的 1. 了解寄存器的分类方法,掌握各种寄存器的工作原理; 2. 学习使用V erilog HDL 语言设计两种类型的寄存器。 二、实验设备 PC 微机一台,TD-EDA 实验箱一台,SOPC 开发板一块。 三、实验内容 寄存器中二进制数的位可以用两种方式移入或移出寄存器。第一种方法是以串行的方式将数据每次移动一位,这种方法称之为串行移位(Serial Shifting),线路较少,但耗费时间较多。第二种方法是以并行的方式将数据同时移动,这种方法称之为并行移位(Parallel Shifting),线路较为复杂,但是数据传送的速度较快。因此,按照数据进出移位寄存器的方式,可以将移位寄存器分为四种类型:串行输入串行输出移位寄存器(Serial In- Serial Out)、串行输入并行输出移位寄存器(Serial In- Parallel Out)、并行输入串行输出移位寄存器(Parallel In- Serial Out)、并行输入并行输出移位寄存器(Parallel In-Parallel Out)。 本实验使用V erilog HDL 语言设计一个八位并行输入串行输出右移移位寄存器(Parallel In- Serial Out)和一个八位串行输入并行输出寄存器(Serial In- Parallel Out),分别进行仿真、引脚分配并下载到电路板进行功能验证。 四、实验步骤 1.并行输入串行输出移位寄存器实验步骤 1). 运行Quartus II 软件,选择File New Project Wizard 菜单,工程名称及顶层文件名称为SHIFT8R,器件设置对话框中选择Cyclone 系列EP1C6Q240C8 芯片,建立新工程。 2.) 选择File New 菜单,创建V erilog HDL 描述语言设计文件,打开文本编辑器界面。 3.) 在文本编辑器界面中编写V erilog HDL 程序,源程序如下: module SHFIT8R(din,r_st,clk,load,dout); input [7:0]din; input clk,r_st,load; output dout; reg dout; reg [7:0]tmp; always @(posedge clk) if(!r_st) begin dout<=0; end else begin if(load) begin tmp=din; end else

计算机组成原理课程设计报告 班级:06计算机 6 班姓名:李凯学号:20063007 完成时间:2009年1月3日 一、课程设计目的 1.在实验机上设计实现机器指令及对应的微指令(微程序)并验证,从而进一步掌握微程序设计控制器的基本方法并了解指令系统与硬件结构的对应关系; 2.通过控制器的微程序设计,综合理解计算机组成原理课程的核心知识并进一步建立整机系统的概念; 3.培养综合实践及独立分析、解决问题的能力。 二、课程设计的任务 针对COP2000实验仪,从详细了解该模型机的指令/微指令系统入手,以实现乘法和除法运算功能为应用目标,在COP2000的集成开发环境下,设计全新的指令系统并编写对应的微程序;之后编写实现乘法和除法的程序进行设计的验证。 三、课程设计使用的设备(环境) 1.硬件 ●COP2000实验仪 ●PC机 2.软件 ●COP2000仿真软件 四、课程设计的具体内容(步骤) 1.详细了解并掌握COP 2000模型机的微程序控制器原理,通过综合实验来实现该模型机指令系统的特点: COP2000模型机包括了一个标准CPU所具备所有部件,这些部件包括:运算器ALU、

累加器A、工作寄存器W、左移门L、直通门D、右移门R、寄存器组R0-R3、程序计数器PC、地址寄存器MAR、堆栈寄存器ST、中断向量寄存器IA、输入端口IN、输出端口寄存器OUT、程序存储器EM、指令寄存器IR、微程序计数器uPC、微程序存储器uM,以及中断控制电路、跳转控制电路。其中运算器和中断控制电路以及跳转控制电路用CPLD来实现,其它电路都是用离散的数字电路组成。微程序控制部分也可以用组合逻辑控制来代替。 模型机为8位机,数据总线、地址总线都为8位,但其工作原理与16位机相同。相比而言8位机实验减少了烦琐的连线,但其原理却更容易被学生理解、吸收。 模型机的指令码为8位,根据指令类型的不同,可以有0到2个操作数。指令码的最低两位用来选择R0-R3寄存器,在微程序控制方式中,用指令码做为微地址来寻址微程序存储器,找到执行该指令的微程序。而在组合逻辑控制方式中,按时序用指令码产生相应的控制位。在本模型机中,一条指令最多分四个状态周期,一个状态周期为一个时钟脉冲,每个状态周期产生不同的控制逻辑,实现模型机的各种功能。模型机有24位控制位以控制寄存器的输入、输出,选择运算器的运算功能,存储器的读写。24位控制位分别介绍如下: XRD :外部设备读信号,当给出了外设的地址后,输出此信号,从指定外设读数据。 EMWR:程序存储器EM写信号。 EMRD:程序存储器EM读信号。 PCOE:将程序计数器PC的值送到地址总线ABUS上。 EMEN:将程序存储器EM与数据总线DBUS接通,由EMWR和EMRD决定是将DBUS数据写到EM中,还是从EM读出数据送到DBUS。 IREN:将程序存储器EM读出的数据打入指令寄存器IR和微指令计数器uPC。 EINT:中断返回时清除中断响应和中断请求标志,便于下次中断。 ELP: PC打入允许,与指令寄存器的IR3、IR2位结合,控制程序跳转。 MAREN:将数据总线DBUS上数据打入地址寄存器MAR。 MAROE:将地址寄存器MAR的值送到地址总线ABUS上。 OUTEN:将数据总线DBUS上数据送到输出端口寄存器OUT里。 STEN:将数据总线DBUS上数据存入堆栈寄存器ST中。 RRD:读寄存器组R0-R3,寄存器R?的选择由指令的最低两位决定。 RWR:写寄存器组R0-R3,寄存器R?的选择由指令的最低两位决定。

华南理工大学实验报告集团文件版本号:(M928-T898-M248-WU2669-I2896-DQ586-M1988)

实验报告课程名称:计算机组成与体系结构 学生姓名:张璐鹏 学生学号: 学生专业:网络工程 开课学期: 2017年10月

实验一运算器组成实验 地点:楼 房; 实验台号: 实验日期与时 间: 评分: 预习检查纪录:实验教师: 一、实验目的 1.熟悉双端口通用寄存器堆的读写操作。 2.熟悉简单运算器的数据传送通路。 3.验证运算器74LS181的算术逻辑功能。 4.按给定数据,完成指定的算术、逻辑运算。 二、实验电路 图3.1示出了本实验所用的运算器数据通路图。参与运算的数据首先通过实验台操作板上的八个二进制数据开关SW7-SW0来设置,然后输入到双端口通用寄存器堆RF中。 RF(U54)由一个ispLSI1016实现,功能上相当于四个8位通用寄存器,用于保存参与运算的数据,运算后的结果也要送到RF中保存。双端口寄存器堆模块的控制信号中,RS1、RS0用于选择从B端口(右端口)读出的通用寄存器,RD1、RD0用于选择从A端口(左端口)读出的通用寄存器。而WR1、WR0用于选择写入的通用寄存器。LDRi是写入控制信号,当LDRi=1时,数据总线DBUS上的数据在T3写入由WR1、WR0指定的通用寄存器。RF的A、B端口分别与操作数暂存器DR1、DR2相连;另

外,RF的B端口通过一个三态门连接到数据总线DBUS上,因而RF中的 数据可以直接通过B端口送到DBUS上。 DR1(U47)和DR2(U48)各由1片74LS273构成,用于暂存参与运算的数据。DR1接ALU的A输入端口,DR2接ALU的B输入端口。ALU(U31、U35)由两片74LS181构成,ALU的输出通过一个三态门(74LS244)发送到数 据总线DBUS上。 实验台上的八个发光二极管DBUS7-DBUS0显示灯接在DBUS上,可以 显示输入数据或运算结果。另有一个指示灯C显示运算器进位标志信号 状态。 图中尾巴上带粗短线标记的信号都是控制信号,其中S3、S2、S1、 S0、M、Cn#、LDDR1、LDDR2、ALU_BUS#、SW_BUS#、LDRi、RS1、RS0、 RD1、RD0、WR1、WR0都是电位信号,在本次实验中用拨动开关K0—K15 来模拟;T2、T3为时序脉冲信号,印制板上已连接到实验台的时序电 路。实验中进行单拍操作,每次只产生一组T1、T2、T3、T4时序脉冲,需将实验台上的DP、DB开关进行正确设置。将DP开关置1,DB开关置0,每按一次QD按钮,则顺序产生T1、T2、T3、T4一组单脉冲。 三、实验设备 1.TEC-5计算机组成实验系统1台 2.逻辑测试笔一支(在TEC-5实验台上) 3.双踪示波器一台(公用) 4.万用表一只(公用) 四、实验任务

成绩:实验报告 课程名称:计算机组成原理 实验项目:寄存器的原理及操作 姓名: 专业:计算机科学与技术 班级: 学号:

计算机科学与技术学院 实验教学中心 20 16年6月20日

实验项目名称:寄存器的原理及操作 一、实验目的 1.了解模型机中 A, W 寄存器结构、工作原理及其控制方法。 2.了解模型机中寄存器组 R0..R3 结构、工作原理及其控制方法。 3.了解模型机中地址寄存器 MAR,堆栈寄存器 ST,输出寄存器 OUT寄存器结构、工作原理及其控 制方法。 二、实验内容 1、A、W寄存器:利用 COP2000实验仪上的K16..K23 开关做为DBUS的数据,其它开关做为控制信号, 将数据写入寄存器A, W。 2、R0、R1、R2、R3 寄存器实验:利用COP2000实验仪上的K16..K23 开关做为DBUS的数据,其它开 关做为控制信号,对数据寄存器组R0..R3 进行读写。 3、MAR、ST、OUT寄存器:利用COP2000实验仪上的K16..K23 开关做为DBUS的数据,其它开关做为 控制信号,将数据写入地址寄存器MAR,堆栈寄存器ST,输出寄存器OUT。 三、实验用设备仪器及材料 伟福 COP2000 系列计算机组成原理实验系统 四、实验原理及接线 实验 1:A,W 寄存器实验

实验 2 :R0,R1, R2,R3寄存器实验

MAR为存储器地址寄存器,其功能是存储操作数在内存中的地址,信号MAREN的功能是将数据总线DBUS上数据 MAR,信号 MAROE的功能是将MAR的值送到地址总线ABUS上 ST 堆栈寄存器的作用,是出现中断或子程序调用时,保存断点处PC 的值,以便中断或子程序结束时, 能继续执行原程序。图中,信号STEN的作用是将数据总线DBUS上数据存入堆栈寄存器ST 中

计 算 机 组 成 原 理 论 文 姓名:某某 班级:计科一班 学号:

8位CPU的设计与实现论文CPU 的主要功能是执行指令,控制完成计算机的各项操作,包括运算操作、传送操作、输入/输出操作等。作为模型计算机设计,将重点放在寄存器组,采取较简单的组成模式,以尽量简洁的设计帮助读者掌握CPU 的基本原理。 此次设计CPU就是为了了解CPU运行的原理,从而完成从指令系统到CPU 的设计,并且通过仿真对CPU设计进行正确性评定。 关键词:CPU,设计指标,电路原理图,运算部件,寄存器组,模型机 指令系统,微命令序列,数据通路 1. 设计的任务与要求 1.1设计指标 1. 能实现IN(输入)、ADD(二进制加法)、STA(存数)、OUT(输出)、JMP (无条件转移)这五种指令; 2. 整个系统能正常稳定工作。 1.2 设计要求 1. 画出电路原理图; 2.写出设计的全过程,附上有关资料和图纸(也可直接写在相关章节中),有 心得体会。 2. 方案论证与选择 2.1 CPU的系统方案

CPU 主要由算术逻辑单元ALU,数据暂存寄存器DR1、DR2,数据寄存器R0~R2,程序计数器PC,地址寄存器AR,程序/数据存储器MEMORAY,指令寄存器IR,微控制器uC,输入单元INPUT 和输出单元OUTPUT 所组成。图中虚线框内部分包括运算器、控制器、程序存储器、数据存储器和微程序存储器等,实测时,它们都可以在单片FPGA 中实现。虚线框外部分主要是输入/输出装置,包括键盘、数码管、LCD 显示器等,用于向CPU 输入数据,或CPU 向外输出数据,以及观察CPU 内部工作情况及运算结果。 1.运算部件 运算部件的任务是对操作数进行加工处理。主要由三部分组成: (1)输入逻辑。(2)算术/逻辑运算部件ALU。(3)输出逻辑 2.寄存器组 计算机工作时,CPU 需要处理大量的控制信息和数据信息。例如对指令信息进行译码,以便产生相应控制命令对操作数进行算术或逻辑运算加工,并且根据运算结果决定后续操作等。因此,在CPU 中需要设置若干寄存器,暂时存放这些信息。在模型CPU中,寄存器组由R0、R1、R2 所组成。 3.指令寄存器指令寄存器(IR) 指令寄存器指令寄存器(IR)用来存放当前正在执行的指令,它的输出包括操作码信息、地址信息等,是产生微命令的主要逻辑依据。 4.程序计数器程序计数器(PC) 程序计数器程序计数器也称指令指针,用来指示指令在存储器中的存放位置。当程序顺序执行时,每次从主存取出一条指令,PC 内容就增量计数,指向下一条指令的地址。增量值取决于现行指令所占的存储单元数。如果现行指令只占一个存储单元,则PC 内容加1;若现行指令占了两个存储单元,那么PC 内容就要加2。当程序需要转移时,将转移地址送入PC,使PC 指向新的指令地址。因此,当现行指令执行完,PC 中存放的总是后续指令的地址;将该地址送往主存的地址寄存器AR,便可从存储器读取下一条指令。 5.地址寄存器 CPU 访问存储器,首先要找到需要访问的存储单元,因此设置地址寄存器(AR)来存放被访单元的地址。当需要读取指令时,CPU 先将PC 的内容送入AR,再由AR将指令地址送往存储器。当需要读取或存放数据时,也要先将该数据的有效地址送入AR,再对存储器进行读写操作。 6.标志寄存器 标志寄存器F是用来记录现行程序的运行状态和指示程序的工作方式的,标志位则用来反映当前程序的执行状态。一条指令执行后,CPU 根据执行结果设置相应特征位,作为决定程序流向的判断依据。例如,当特征位的状态与转移条件符合时,程序就进行转移;如果不符合,则顺序执行。在后面将要介绍的较复杂模型计算机设计中设置了两个标志位:进位Fc、零位Fz。 7.微指令产生部件 实现信息传送要靠微命令的控制,因此在CPU 中设置微命令产生部件, 根据控制信息产生微命令序列,对指令功能所要求的数据传送进行控制, 同时在数据传送至运算部件时控制完成运算处理。 微命令产生部件可由若干组合逻辑电路组成,也可以由专门的存储逻辑组成。产生微命令的方式可分为组合逻辑控制方式和微程序控制方式两种。在本章所介绍的8 位模型CPU 设计中,采用微程序控制方式通过微程序控制器和微指令存储器

杭州电子科技大学计算机学院 实验报告 实验项目: 课程名称:计算机组成原理与系统结构设计 姓名: 学号: 同组姓名: 学号 : 实 验 位 置 ( 机 号 ) : 实验日期: 指 导 教 师: 实验 内容 (算 法、 程 序、 步骤 和 方 法) 一、 实验目的 (1 )学会使用Verilog HDL 进行时序电路的设计方法。 (2)掌握灵活应用Verilog HDL 进行各种描述与建模的技巧和方法。 (3 )学习寄存器堆的数据传送与读 /写工作原理,掌握寄存器堆得设计方法。 二、 实验仪器 ISE 工具软件 三、 步骤、方法 (1) 启动Xilinx ISE 软件,选择File->New Project,输入工程名shiyan2,默认选择后,点 击Next 按钮,确认工程信息后点击 Finish 按钮,创建一个完整的工程。 (2) 在工程管理区的任意位置右击,选择 New Source 命令。弹出 New Source Wizard 对 话框, 选择Verilog Module,并输入Verilog 文件名,点击Next 按钮进入下一步, 点击Finish 完成创建。 (3) 编辑程序源代码,然后编译,综合;选择 Synthesize--XST 项中的Check Syntax 右击 选择 Run 命令,并查看RTL 视图;如果编译出错,则需要修改程序代码,直至正确。 (4) 在工程管理区将 View 类型设置成 Simulation ,在任意位置右击,选择 New Source 命 令,选择Verilog Test Fixture 选项。点击Next ,点击Finish ,完成。编写激励代码,观察仿 真波形,如果验证逻辑有误,则修改代码,重新编译,仿真,直至正确。 (5) 由于实验四并未链接实验板,所以后面的链接实验板的步骤此处没有。

计算机组成原理课程实验报告 9.3 运算器组成实验 姓名:曾国江 学号: 系别:计算机工程学院 班级:网络工程1班 指导老师: 完成时间: 评语: 得分:

9.3运算器组成实验 一、实验目的 1.熟悉双端口通用寄存器堆的读写操作。 2.熟悉简单运算器的数据传送通路。 3.验证运算器74LS181的算术逻辑功能。 4.按给定数据,完成指定的算术、逻辑运算。 二、实验电路 ALU-BUS# DBUS7 DBUS0 Cn# C 三态门(244) 三态门(244)ALU(181) ALU(181) S3S2S1S0M A7A6A5A4F7F6F5F4 F3F2F1F0B3B2B1B0 Cn+4 Cn Cn Cn+4 LDDR2T2 T2 LDDR1LDRi T3 SW-BUS# DR1(273) DR2(273) 双端口通用寄存器堆RF (ispLSI1016) RD1RD0RS1RS0WR1WR0 数据开关(SW7-SW0)数据显示灯 A3A2A1A0B7B6B5B4 图3.1 运算器实验电路 LDRi T3A B 三态门 R S -B U S # 图3.1示出了本实验所用的运算器数据通路图。参与运算的数据首先通过实验台操作板上的八个二进制数据开关SW7-SW0来设置,然后输入到双端口通用寄存器堆RF 中。

RF(U30)由一个ispLSI1016实现,功能上相当于四个8位通用寄存器,用于保存参与运算的数据,运算后的结果也要送到RF中保存。双端口寄存器堆模块的控制信号中,RS1、RS0用于选择从B端口(右端口)读出的通用寄存器,RD1、RD0用于选择从A端口(左端口)读出的通用寄存器。而WR1、WR0用于选择写入的通用寄存器。LDRi是写入控制信号,当LDRi=1时,数据总线DBUS上的数据在T3写入由WR1、WR0指定的通用寄存器。RF的A、B端口分别与操作数暂存器DR1、DR2相连;另外,RF的B端口通过一个三态门连接到数据总线DBUS上,因而RF中的数据可以直接通过B端口送到DBUS 上。 DR1和DR2各由1片74LS273构成,用于暂存参与运算的数据。DR1接ALU的A输入端口,DR2接ALU的B输入端口。ALU由两片74LS181构成,ALU的输出通过一个三态门(74LS244)发送到数据总线DBUS上。 实验台上的八个发光二极管DBUS7-DBUS0显示灯接在DBUS上,可以显示输入数据或运算结果。另有一个指示灯C显示运算器进位标志信号状态。 图中尾巴上带粗短线标记的信号都是控制信号,其中S3、S2、S1、S0、M、Cn#、LDDR1、LDDR2、ALU_BUS#、SW_BUS#、LDRi、RS1、RS0、RD1、RD0、WR1、WR0都是电位信号,在本次实验中用拨动开关K0—K15来模拟;T2、T3为时序脉冲信号,印制板上已连接到实验台的时序电路。实验中进行单拍操作,每次只产生一组T1、T2、T3、T4时序脉冲,需将实验台上的DP、DB开关进行正确设置。将DP开关置1,DB开关置0,每按一次QD 按钮,则顺序产生T1、T2、T3、T4一组单脉冲。 三、实验设备 1.TEC-5计算机组成实验系统1台 2.逻辑测试笔一支(在TEC-5实验台上) 3.双踪示波器一台(公用) 4.万用表一只(公用) 四、实验任务 1、按图3.1所示,将运算器模块与实验台操作板上的线路进行连接。由于运 算器模块内部的连线已由印制板连好,故接线任务仅仅是完成数据开关、控制信号

8位移位寄存器的电路设计与版图实现 摘要 电子设计自动化,缩写为EDA,主要是以计算机为主要工具,而Tanner EDA则是一种在计算机windows平台上完成集成电路设计的一种软件,基本包括S-Edit,T-Spice,W-Edit,L-Edit与LVS等子软件,其S-Edit以及L-Edit为常用软件,前者主要实现电路设计,后者主要针对的是已知电路的版图绘制,而T-Spice主要可实现电路图及版图的仿真,可以用Tanner EDA实现电路的设计布局以及版图实现等一系列完整过程。本文用Tanner EDA工具主要设计的是8位移位寄存器,移位寄存器主要是用来实现数据的并行和串行之间的转换以及对数据进行运算或专业处理的工具,主要结构构成是触发器,触发器是具有储存功能的,可以用来储存多进制代码,一般N 位寄存器就是由N个触发器构成,移位寄存器工作原理主要是数据在其脉冲的作用下实现左移或者右移的效果,输入输出的方式表现为串行及并行自由组合,本设计就是在Tanner EDA的软件平台上进行对8位移位寄存器的电路设计仿真,再根据电路图在专门的L-Edit 平台上完成此电路的版图实现,直至完成的结果和预期结果保持一致。 关键词:Tanner EDA;L-Edit;移位寄存器,S-Edit

8 bits shift register circuit design and layout Abstract Electronic design automation,referred to as EDA,it is based on computers as the main tool,and Tanner EDA is a kind of software that complete the integrated circuit design on Windows platforms.Its Sub-Softwares include S-Edit,T-Spice,W-Edit,L-Edit and LVS and so on.S-Edit and L-Edit are commonly used software,S-Edit is primarily designed to achieve circuit,the latter is aimed primarily known circuit layout drawing,T-Spice can achieve schematic and layout simulation.We can achieve layout of the circuit design and a series of complete process layout used Tanner EDA tools.In this paper, Tanner EDA tools are mainly designed an 8-bit shift register.The shift register is mainly used for data conversion between parallel and serial, and the data processing tool operation or professional,its main structure is the trigger composition,flip-flop is a storage function,it can be used to store more hexadecimal code,In general N-bits register is composed of N trigger.Working principle of the shift register data under the action of the pulse, mainly the effect of the shift to the left or right,input and output of the way of serial and parallel free combination.This design is in Tanner on the EDA software platform to 8 bits shift register circuit design and simulation,then according to the circuit diagram on special L - Edit platform to complete the circuit layout implementation,until the finish is consistent with the results and expected results. Keywords:Tanner EDA;L-Edit;Shift register,S-Edit

实验六移位寄存器的设计 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。 二、实验预习要求 1、复习有关寄存器及串行、并行转换器有关内容。 2、查阅CC40194、CC4011及CC4068 逻辑线路。熟悉其逻辑功能及引脚排列。 3、在对CC40194进行送数后,若要使输出端改成另外的数码,是否一定要使寄存器清零? 4、使寄存器清零,除采用R C输入低电平外,可否采用右移或左移的方法?可否使用并行送数法?若可行,如何进行操作? 5、若进行循环左移,图6-4接线应如何改接? 6、画出用两片CC40194构成的七位左移串 /并行转换器线路。 7、画出用两片CC40194构成的七位左移并 /串行转换器线路。 三、实验设备及器件 1、+5V直流电源 2、单次脉冲源 3、逻辑电平开关 4、逻辑电平显示器 5、CC40194×2(74LS194)CC4011(74LS00) CC4068(74LS30) 四、设计方法与参考资料 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图6-1所示。 其中D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串行输 C为直接无条件清零端; 入端,S L为左移串行输入端;S1、S0为操作模式控制端;R

课程设计(大作业)报告课程名称:计算机组成原理 设计题目:基本模型机设计与实现 院系:信息技术学院 班级:计算机科学与技术3班 设计者: 学号: 指导教师: 设计时间: 昆明学院 信息技术学院 课程设计(大作业)任务书

目录 课程设计(大作业)报告 一、课程设计的教学目的 1. 在“微程序控制器的组成与微程序设计实验”的基础上,进一步将其中各单元组成系统构造一台模型计算机。 2. 本实验定义五条机器指令,编写相应的微程序,并上机调试运行,形成整机概念。 课程设计内容设计一台基本模型机,并实现相关的指令。 二、课程设计任务和基本要求 本课程设计以TDN-CM++计算机组成原理教学实验系统为平台设计完成。 1.按给定的数据格式和指令系统,设计一个微程序控制器。 2.设计给定机器指令系统以及微程序流程图,按微指令格式写出微 程序的为指令代码。

3.连接逻辑电路完成启动,测试,编程,测试,效验和运行,并观测运 行过程及结果。 4.将微程序控制器模块与运算器模块,存储器模块联机,组成一台 模型计算机。 5.用微程序控制器控制模型机的数据通路。 6.通过在模型机上运行由机器指令组成的简单程序,掌握机器指令 与微指令的关系,建立计算机整机的概念,掌握计算机的控制机制。 7.按指定的应用项目进行汇编指令格式及功能设计,并设计相应的 机器指令代码,按照模型机数据通路设计实现机器指令功能的微程序.在 PC机上编辑机器指令和微程序,装载代码到TDN-CM++实验系统并运行,实现应用要求。 三、设计任务及分析 (1)设计任务: 从输入设备读取数据X并将其存入以A为间接地址的 内存单元,将X与R 0. 寄存器中的内容Y执行X ⊕,结果送到以B为直接地址的内存单元保存。 (2)分析: A:给R 寄存器直接置入01H. B:从数据开关给间接地址为0CH的内存单元置数,(03H). C:给R 0中的内容取反,结果存在R 中. D:将间接地址0CH中直接地址0EH中的内容(03H)放入DR1中, R 中的内容 放入DR2中,将DR1和DR2种的数进行异或运算,结果放在R 中. E:将R 中的内容存在直接地址为0DH的内存单元中. 四、设计原理 模型机在微程序控制下自动产生各部件单元控制信号,实现特定指令的功能。这里,计算机数据通路的控制将由微程序控制器来完成,CPU 从内存中取出一条机器指令到指令执行结束的一个指令周期全部由微指令组成的序列来完成,即一条机器指令对应一段微程序。 本实验采用五条机器指令: IN(输入)、ADD(二进制加法)、STA(存数)、OUT(输出)、JMP(无条件转移),其指令格式如下(前4位为操作码):

序号: 学号: C H A N G Z H O U U N I V E R S I T Y 计算机组成原理 课程设计报告 题 目: 8位机微程序控制器模型计算机的设计与实现 学 生 姓 名: 学 号: 学 院(系): 专 业 班 级: 校内指导教师: 专业技术职务: 实 习 时 间: 年 月 日 年 月 日

计算机组成原理课程设计任务书

计算机科学与技术系指导教师

目录 1、课程设计的目的 (1) 2、课程设计的环境 (1) 3、课程设计的内容 (1) 3.1课程设计的原理 (1) 3.2课程设计机器指令 (3) 3.3微指令格式 (4) 3.4数据通路图 (6) 4、设计方案 (7) 4.1设计指令 (9) 4.2微程序流程图 (10) 4.3微指令二进制微代码表 (10) 5、验证与结果分析 (13) 5.1课设过程中所遇问题 (23) 5.2对应问题的解决 (23) 6、课程设计总结 (24) 6.1任务分工 (24) 6.2心得体会 (24) 参考文献 (26)

1、课程设计的目的 深入了解计算机各种指令的执行过程,以及控制器的组成,指令系统微程序设计的具体知识,进一步理解和掌握动态微程序设计的概念;完成微程序控制的特定功能计算机的指令系统设计和调试。 总体概括而言,分为两点:1、在掌握部件单元电路实验的基础上,进一步将其组成系统,构造一台基本模型计算机。2、为其定义两条以上的机器指令,并编写相应的微程序,上机调试,掌握整机概念。 2、课程设计的环境 硬件环境:TEC-9实验系统一台,排线若干,连接有关联的开关,使信号同步。 软件环境:HQFC-B1计算机组成原理软件,进行微程序的写入。 3、课程设计的内容 1、通过知识的综合运用,设计一台新的微程序控制器模型计算机。 2、选择合适的寻址方式,进行数据的提取。 3、确定你需要做的两条指令,并画出对应指令的流程图。 4、根据流程图,设计控制器代码。 5、根据控制器代码,在TEC-9实验系统上进行连线、调试,修改控制器代码。 6、最后,得出正确的控制器代码并完成实验报告、答辩,课程设计完成3.1课程设计的原理 TEC-9实验系统的组成:控制台、数据通路、控制器、时序电路、数字逻辑实验区、电源模块 时序发生器 时序发生器产生计算机模型所需的时序和数字逻辑实验所需的时钟。时序电路由一个500KHz晶振、2片GAL22V10组成。根据本机的设计,执行一条微程序指令需要4个节拍脉冲T1、T2、T3、T4,执行一条机器指令需要三个节拍电位W1、W2、W3,因此本机的基本时序如下:

成绩: 计算机原理实验室实验报告 本说明打印前删除!!proteus 实验报告格式必须保持原样,蓝色部分按照实验内容自行填写;全班统一使用A4大小纸张,部分困难学生可以使用等大小纸张,自绘实验报告格式;全部实验完成后,学委按照实验顺序把每个学生的实验报告(含首页)装订成册,按照学号顺序排列,提交给实验指导老师(询问代课老师,学校将实验工作指派给了哪位老师)。 学委提交报告时,需要同时提交(附录)实验成绩登记表一份。其中表头部分课程,班级,班级总人数照实填写,项目填写本学期本课程的实验数量;学号姓名栏按照顺序填写,报告一栏填写该同学交报告的份数(每项目每人一份报告);出勤和成绩栏留空,由实验室填写;特殊情况填写在备注处,若空间不够请写于背面并在备注处标明;若有学号超过58号的情况,请在背后按照格式登记所有项目;空学号可以不留空位置,顺序递进。 课程:计算机组成原理 姓名:刘翔翔 专业:软件工程 学号:1420561 21 日期:2016年6月 太原工业学院 计算机工程系

实验二:输寄存器实验 实验环境PC机+Win 7+proteus仿真器实验日期2016.06.01 一.实验内容 基本要求 1.理解CPU运算器中寄存器的作用 2.设计并验证寄存器组(至少四个寄存器) 扩展要求 3.实现更多的寄存器(至少8个) 思考题: 思考随着寄存器的增多,电路设计的复杂度是什么比例增大? 二.理论分析或算法分析 1.基本要求 使用74LS373充当寄存器,74LS139做地址译码,74LS245用作输入,数码管显示寄存器内的数据。74LS139为二-四译码器,用两根线作为地址线接到74LS139的输入端,输出端分别接到每个74LS373的OE上,再用一个74LS139配合反相器产生控制每个74LS373的LE的信号。74LS245的输出端分别对应接到373输入端的每个管脚上的。74LS373的输出端对应接到数码管的对应管教上,以实现数据的显示。先在各个寄存器中输入不同的数据,然后关闭74ls248(输入),选择不同的373(寄存器),在数码管上显示不同的数据。 2.扩展要求 与基本要求相比大体不变,地址译码部分选择74LS138来做地址译码器。原理图连接方式原理不变,验证方式不变。

河南科技大学 课程设计说明书 课程名称 EDA技术与应用 题目移位寄存器的设计与实现 学院 班级 学生姓名 指导教师 日期

EDA技术课程设计任务书 班级:姓名:学号: 设计题目:移位寄存器的设计与实现 一、设计目的 进一步巩固理论知识,培养所学理论知识在实际中的应用能力;掌握EDA设计的一般方法;熟悉一种EDA软件,掌握一般EDA系统的调试方法;利用EDA软件设计一个电子技术综合问题,培养VHDL编程、书写技术报告的能力。为以后进行工程实际问题的研究打下设计基础。 二、设计任务 根据计算机组成原理中移位寄存器的相关知识,利用VHDL语言设计了三种不同的寄存器:双向移位寄存器、串入串出(SISO)移位寄存器、串入并出(SIPO)移位寄存器。 三、设计要求 (1)通过对相应文献的收集、分析以及总结,给出相应课题的背景、意义及现状研究分析。 (2)通过课题设计,掌握计算机组成原理的分析方法和设计方法。 (3)学习按要求编写课程设计报告书,能正确阐述设计和实验结果。 (4)学生应抱着严谨认真的态度积极投入到课程设计过程中,认真查阅相应文献以及实现,给出个人分析、设计以及实现。 四、设计时间安排 查找相关资料(1天)、设计并绘制系统原理图(2天)、编写VHDL程序(2天)、调试(2天)、编写设计报告(2天)和答辩(1天)。 五、主要参考文献 [1] 江国强编著. EDA技术与实用(第三版). 北京:电子工业出版社,2011. [2] 曹昕燕,周凤臣.EDA技术实验与课程设计.北京:清华大学出版社,2006.5 [3] 阎石主编.数字电子技术基础.北京:高等教育出版社,2003. [4] Mark Zwolinski. Digital System Design with VHDL.北京:电子工业出版社,2008 [5] Alan B. Marcovitz Introduction to logic Design.北京:电子工业出版社,2003 指导教师签字:年月日