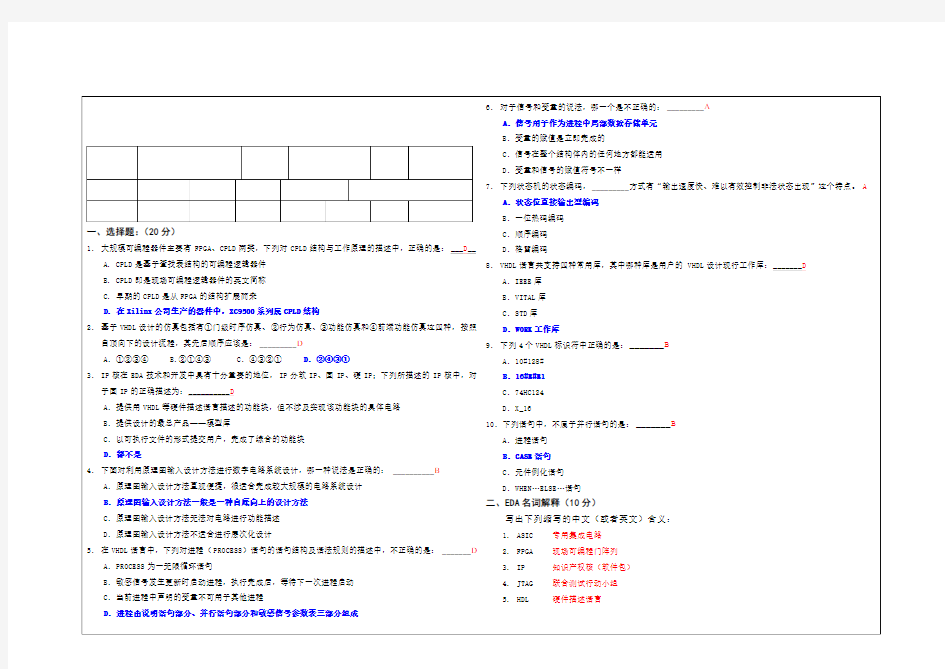

AD574工作时序

位转换模式,K12_8、A0在control中如何设置?

《EDA技术与项目训练》选择题

1. 一个项目的输入输出端口是定义在 A 。

A. 实体中

B. 结构体中

C. 任何位置

D. 进程体

2. 描述项目具有逻辑功能的是 B 。

A. 实体

B. 结构体

C. 配置

D. 进程

3. 关键字ARCHITECTURE定义的是 A 。

A. 结构体

B. 进程

C. 实体

D. 配置

4. MAXPLUSII中编译VHDL源程序时要求 C 。

A.文件名和实体可不同名

B.文件名和实体名无关

C. 文件名和实体名要相同

D. 不确定

5. 1987标准的VHDL语言对大小写是 D 。

A. 敏感的

B. 只能用小写

C. 只能用大写

D. 不敏感

6. 关于1987标准的VHDL语言中,标识符描述正确的是 A 。

A. 必须以英文字母开头

B.可以使用汉字开头

C.可以使用数字开头

D.任何字符都可以

7. 关于1987标准的VHDL语言中,标识符描述正确的是 B 。

A. 下划线可以连用

B. 下划线不能连用

C. 不能使用下划线

D. 可以使用任何字符

8. 符合1987VHDL标准的标识符是 A 。

A. A_2

B. A+2

C. 2A

D. 22

9. 符合1987VHDL标准的标识符是 A 。

A. a_2_3

B. a_____2

C. 2_2_a

D. 2a

10. 不符合1987VHDL标准的标识符是 C 。

A. a_1_in

B. a_in_2

C. 2_a

D. asd_1

11. 不符合1987VHDL标准的标识符是 D 。

A. a2b2

B. a1b1

C. ad12

D. %50

12. VHDL语言中变量定义的位置是 D 。

A. 实体中中任何位置

B. 实体中特定位置

C. 结构体中任何位置

D. 结构体中特定位置

13. VHDL语言中信号定义的位置是 D 。

A. 实体中任何位置

B. 实体中特定位置

C. 结构体中任何位置

D. 结构体中特定位置

14. 变量是局部量可以写在 B 。

A. 实体中

B. 进程中

C. 线粒体

D. 种子体中

15. 变量和信号的描述正确的是 A 。

A. 变量赋值号是:=

B. 信号赋值号是:=

C. 变量赋值号是<=

D. 二者没有区别

16. 变量和信号的描述正确的是 B 。

A. 变量可以带出进程

B. 信号可以带出进程

C. 信号不能带出进程

D. 二者没有区别

17. 关于VHDL数据类型,正确的是 D 。

A. 数据类型不同不能进行运算

B. 数据类型相同才能进行运算

C. 数据类型相同或相符就可以运算

D. 运算与数据类型无关

18. 下面数据中属于实数的是 A 。

A. 4.2

B. 3

C. ‘1’

D. “11011”

19. 下面数据中属于位矢量的是 D 。

A. 4.2

B. 3

C. ‘1’

D. “11011”

20. 关于VHDL数据类型,正确的是。

A. 用户不能定义子类型

B. 用户可以定义子类型

C. 用户可以定义任何类型的数据

D. 前面三个答案都是错误的

A. STD_LOGIC

B. STD_LOGIC_VECTOR

C. BIT

D. 前面三个答案都是错误的

22. STD_LOGIG_1164中定义的高阻是字符 D 。

A. X

B. x

C. z

D. Z

23. STD_LOGIG_1164中字符H定义的是 A 。

A. 弱信号1

B. 弱信号0

C. 没有这个定义

D. 初始值

24. 使用STD_LOGIG_1164使用的数据类型时 B 。

A.可以直接调用

B.必须在库和包集合中声明

C.必须在实体中声明

D. 必须在结构体中声明

25. 关于转化函数正确的说法是。

A. 任何数据类型都可以通过转化函数相互转化

B. 只有特定类型的数据类型可以转化

C. 任何数据类型都不能转化

D. 前面说法都是错误的

26. VHDL运算符优先级的说法正确的是 C 。

A. 逻辑运算的优先级最高

B. 关系运算的优先级最高

C. 逻辑运算的优先级最低

D. 关系运算的优先级最低

27. VHDL运算符优先级的说法正确的是 A 。

A. NOT的优先级最高

B. AND和NOT属于同一个优先级

C. NOT的优先级最低

D. 前面的说法都是错误的

28. VHDL运算符优先级的说法正确的是 D 。

A. 括号不能改变优先级

B. 不能使用括号

C. 括号的优先级最低

D. 括号可以改变优先级

29. 如果a=1,b=0,则逻辑表达式(a AND b) OR( NOT b AND a)的值是 B 。

A. 0

B. 1

C. 2

D. 不确定

30. 关于关系运算符的说法正确的是。

A. 不能进行关系运算

B. 关系运算和数据类型无关

C. 关系运算数据类型要相同

D. 前面的说法都错误

31. 转换函数TO_BITVECTOR(A)的功能是。

A. 将STDLOGIC_VECTOR转换为BIT_VECTOR

B. 将REAL转换为BIT_VECTOR

C. 将TIME转换为BIT_VECTOR

D. 前面的说法都错误

32. VHDL中顺序语句放置位置说法正确的是。

A.可以放在进程语句中

B. 可以放在子程序中

C. 不能放在任意位置

D. 前面的说法都正确

33. 不属于顺序语句的是 B 。

A. IF语句

B. LOOP语句

C. PROCESS语句

D. CASE语句

34. 正确给变量X赋值的语句是 B 。

A. X<=A+B;

B. X:=A+b;

C. X=A+B;

D. 前面的都不正确

35. EDA的中文含义是 A 。

A. 电子设计自动化

B. 计算机辅助计算

C. 计算机辅助教学

D. 计算机辅助制造

36. 可编程逻辑器件的英文简称是。 A. FPGA B. PLA C. PAL D. PLD

37. 现场可编程门阵列的英文简称是。 A. FPGA B. PLA C. PAL D. PLD

38. 基于下面技术的PLD器件中允许编程次数最多的是。

A. FLASH

B. EEROM

C. SRAM

D. PROM

39. 在EDA中,ISP的中文含义是。

A. 网络供应商

B. 在系统编程

C. 没有特定意义

D. 使用编程器烧写PLD芯片

40. 在EDA中,IP的中文含义是。

A. 网络供应商

B. 在系统编程

C. 没有特定意义

D. 知识产权核

41. EPF10K20TC144-4具有多少个管脚 A 。

42. EPF10K20TC144-X器件,如果X的值越小表示。

A. 器件的工作频率越小

B. 器件的管脚越少

C. 器件的延时越小

D. 器件的功耗越小

43. 如果a=1,b=1,则逻辑表达式(a XOR b) OR( NOT b AND a)的值是 A 。

A. 0

B. 1

C. 2

D. 不确定

44. 执行下列语句后Q的值等于 B 。

……

SIGNAL E: STD_LOGIC_VECTOR (2 TO 5);

SIGNAL Q: STD_LOGIC_VECTOR (9 DOWNTO 2);

……

E<=(2=>’1’, 4=>’0’, OTHERS=>’1’);

Q<=(2=>E (2), 4=>E (3), 5=>’1’, 7=>E (5), OTHERS=>E (4));

……

A.“11011011” B. “00101101” C. “11011001” D. “00101100”

45. VHDL文本编辑中编译时出现如下的报错信息

Error: VHDL syntax error: signal declaration must have ‘;’,but found begin instead. 其错误原因是 A 。

A. 信号声明缺少分号。

B. 错将设计文件存入了根目录,并将其设定成工程。

C. 设计文件的文件名与实体名不一致。

D. 程序中缺少关键词。

46. VHDL文本编辑中编译时出现如下的报错信息

Error: VHDL syntax error: choice value length must match selector expression value length 其错误原因是 A 。

A. 表达式宽度不匹配。

B. 错将设计文件存入了根目录,并将其设定成工程。

C. 设计文件的文件名与实体名不一致。

D. 程序中缺少关键词。

47. MAX+PLUSII的设计文件不能直接保存在 B 。

A.硬盘 B. 根目录 C. 文件夹 D. 工程目录

48. MAXPLUSII是哪个公司的软件 A 。

A. ALTERA

B. ATMEL

C. LATTICE

D. XILINX

49. MAXPLUSII不支持的输入方式是 D 。

A. 文本输入

B. 原理图输入

C. 波形输入

D. 矢量输入

50. MAXPLUSII中原理图的后缀是 B 。

A. DOC

B. GDF

C. BMP

D. JIF

51. 在一个VHDL设计中Idata是一个信号,数据类型为std_logic_vector,试指出下面那个赋值语句是错误的。 D 。

A.idata <= “00001111”;

B.idata <= b”0000_1111”;

C.idata <= X”AB”

D. idata <= B”21”;

52. 在VHDL语言中,下列对时钟边沿检测描述中,错误的是 D 。

A.if clk’event and clk = ‘1’ then

B.if falling_edge(clk) then

C.if clk’event and clk = ‘0’ then

D.if clk’stable and not clk = ‘1’ then

53. 下面对利用原理图输入设计方法进行数字电路系统设计的描述中,那一种说法是不正确的。。

A.原理图输入设计方法直观便捷,但不适合完成较大规模的电路系统设计;

B.原理图输入设计方法一般是一种自底向上的设计方法;

C.原理图输入设计方法无法对电路进行功能描述;

D.原理图输入设计方法也可进行层次化设计。

54. 在一个VHDL设计中idata是一个信号,数据类型为integer,数据范围0 to 127,下面哪个赋值语句是正确的。 C 。

A.idata := 32;

B.idata <= 16#A0#;

C.idata <= 16#7#E1;

D.idata := B#1010#;

55. 下列那个流程是正确的基于EDA软件的FPGA / CPLD设计流程: A 。

B.原理图/HDL文本输入→适配→综合→功能仿真→编程下载→硬件测试;

C.原理图/HDL文本输入→功能仿真→综合→编程下载→→适配硬件测试;

D.原理图/HDL文本输入→功能仿真→适配→编程下载→综合→硬件测试

56. 在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,正确的是。

A.PROCESS为一无限循环语句;敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动。

B.敏感信号参数表中,应列出进程中使用的所有输入信号;

C.进程由说明部分、结构体部分、和敏感信号参数表三部分组成;

D.当前进程中声明的信号也可用于其他进程。

57. 对于信号和变量的说法,哪一个是不正确的: A 。

A.信号用于作为进程中局部数据存储单元

B.变量的赋值是立即完成的

C.信号在整个结构体内的任何地方都能适用

D.变量和信号的赋值符号不一样

58. VHDL语言共支持四种常用库,其中哪种库是用户的VHDL设计现行工作库:。

A.IEEE库

B.VITAL库

C.STD库

D.WORK工作库

59. 下列语句中,不属于并行语句的是: B 。

A.进程语句

B.CASE语句

C.元件例化语句

D.WHEN…ELSE…语句

60. 下面哪一条命令是MAX+PLUSII在时序仿真时执行加载节点的命令? C 。

A. file—>set project to current file

B. assign—>pin/location chip

C. node—>enter node from SNF

D. file—>create default symbol

61. 在EDA工具中,能将硬件描述语言转换为硬件电路的重要工具软件称为 D 。 A.仿真器 B.综合器 C.适配器 D.下载器

62. VHDL文本编辑中编译时出现如下的报错信息

Error: Can’t open VHDL“WORK”其错误原因是 B 。

A. 错将设计文件的后缀写成.tdf,而非.vhd 。

B. 错将设计文件存入了根目录,并将其设定成工程。

C. 设计文件的文件名与实体名不一致。

D. 程序中缺少关键词。

63. 在VHDL的CASE语句中,条件句中的“=>”不是操作符号,它只相当与 B 作用。

A. IF

B. THEN

C. AND

D. OR

64. 下面哪一条命令是MAXPLUSII软件中引脚锁定的命令 C 。

A. file—>set project to current file B.node—>enter node from SNF

C. assign—>pin/location chip D. file—>create default symbol]

65. 下列关于信号的说法不正确的是 C 。A . 信号相当于器件内部的一个数据暂存节点。

B. 信号的端口模式不必定义,它的数据既可以流进,也可以流出。

C. 在同一进程中,对一个信号多次赋值,其结果只有第一次赋值起作用。

D. 信号在整个结构体内的任何地方都能适用。

66. 下面哪一个可以用作VHDL中的合法的实体名 D 。

A. OR

B. VARIABLE

C. SIGNAL

D. OUT1

67. VHDL文本编辑中编译时出现如下的报错信息

Error:Line1,File e:\muxfile\mux21.tdf: TDF syntax error…其错误原因是 A 。

A. 错将设计文件的后缀写成.tdf 而非.vhd 。

B. 错将设计文件存入了根目录,并将其设定成工程。

C. 设计文件的文件名与实体名不一致。

D. 程序中缺少关键词。

68. 下列关于变量的说法正确的是 A 。

A. 变量是一个局部量,它只能在进程和子程序中使用。

C. 在进程的敏感信号表中,既可以使用信号,也可以使用变量。

D. 变量赋值的一般表达式为:目标变量名<= 表达式。

69. 下列关于CASE语句的说法不正确的是 B 。

A. 条件句中的选择值或标识符所代表的值必须在表达式的取值范围内。

B. CASE语句中必须要有WHEN OTHERS=>NULL;语句。

C. CASE语句中的选择值只能出现一次,且不允许有相同的选择值的条件语句出现。

D. CASE语句执行必须选中,且只能选中所列条件语句中的一条。

70. VHDL中,为目标变量赋值符号是 D 。

A. =:

B. =

C. <=

D.:=

71. 在VHDL中,可以用语句 D 表示检测clock下降沿。

A. clock’ event

B. clock’ event and clock=’1’

C. clock=’0’

D. clock’ event and clock=’0’

72.在VHDL的FOR_LOOP语句中的循环变量是一个临时变量,属于LOOP语句的局部量, B 事先声明。 A. 必须 B. 不必 C. 其类型要 D.其属性要

73. 在VHDL中,语句”FOR I IN 0 TO 7 LOOP ”定义循环次数为 A 次。

A. 8

B. 7

C. 0

D.1

74. 在VHDL中,PROCESS结构内部是由 B 语句组成的。

A. 顺序

B. 顺序和并行

C. 并行

D.任何

75. 执行MAX+PLUSII的 C 命令,可以对设计的电路进行仿真。

A.Creat Default Symbol

https://www.doczj.com/doc/8816259634.html,piler

C.Simulator

D.Programmer

76. 在VHDL中,PROCESS本身是 C 语句。

A. 顺序

B.顺序和并行

C.并行

D.任何

77. 下面哪一个是VHDL中的波形编辑文件的后缀名 B 。

A. gdf

B. scf

C. sys

D. tdf

78. 在元件例化语句中,用 D 符号实现名称映射,将例化元件端口声明语句中的信号与PORT MAP()中的信号名关联起来。

A. =

B. :=

C. <=

D.=>

79.在VHDL中,含WAIT语句的进程PROCESS的括弧中 B再加敏感信号,否则则是非法的。

A. 可以

B.不能

C. 必须

D. 有时可以

80.在MAX+PLUSII集成环境下为图形文件产生一个元件符号的主要作用是 D 。

A. 综合

B. 编译

C. 仿真

D.被高层次电路设计调用

81.在MAX+PLUSII工具软件中,完成网表提取、数据库建立、逻辑综合、逻辑分割、适配、延时网表提取和编程文件汇编等操作,并检查设计文件是否正确的过程称为。

A. 编辑

B. 编译

C. 综合

D. 编程

82. VHDL文本编辑中编译时出现如下的报错信息

Error: VHDL Design File “mux21” must contain an entity of the same name

其错误原因是 C 。

A. 错将设计文件的后缀写成.tdf 而非.vhd 。

B. 错将设计文件存入了根目录,并将其设定成工程。

C. 设计文件的文件名与实体名不一致。

D. 程序中缺少关键词。

83. 执行下列语句后Q的值等于 D 。

……

SIGNAL E: STD_LOGIC_VECTOR (2 TO 5);

SIGNAL Q: STD_LOGIC_VECTOR (9 DOWNTO 2);

……

E<=(2=>’0’, 4=>’0’, OTHERS=>’1’);

Q<=(2=>E (2), 4=>E (3), 5=>’1’, 7=>E (5), OTHERS=>E (4));

……

A.“11011011” B. “00110100” C. “11011001” D. “00101100”

A. 综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;

B. 为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;

C. 综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系不是唯一的。

D. 综合是纯软件的转换过程,与器件硬件结构无关;

85. 关于VHDL中的数字,请找出以下数字中数值最小的一个:

A. 2#1111_1110#

B. 8#276#

C. 10#170#

D. 16#E#E1

86. 以下对于进程PROCESS的说法,正确的是: C 。

A. 进程之间可以通过变量进行通信

B. 进程内部由一组并行语句来描述进程功能

C. 进程语句本身是并行语句

D.一个进程可以同时描述多个时钟信号的同步时序逻辑

87. 进程中的信号赋值语句,其信号更新是。

A.按顺序完成;

B.比变量更快完成;

C.在进程的最后完成;

D.以上都不对。

88.关于VHDL中的数字,请找出以下数字中最大的一个:。

A.2#1111_1110# B.8#276# C. 0#170# D.6#E#E1

89.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述。A.器件外部特性; B.器件的内部功能;C.器件的综合约束;

C.器件外部特性与内部功能。

90.下列标识符中, B 是不合法的标识符。

A. State0

B. 9moon

C. Not_Ack_0

D. signal

91.在VHDL中,IF语句中至少应有1个条件句,条件句必须由表达式构成。

A. BIT

B. STD_LOGIC

C. BOOLEAN

D. INTEGER

92. 在VHDL中 D 不能将信息带出对它定义的当前设计单元。

A. 信号

B. 常量

C. 数据

D. 变量

93.在VHDL中,为定义的信号赋初值,应该使用__D___ 符号。

A. =:

B. =

C. :=

D. <=

94.在VHDL中,一个设计实体可以拥有一个或多个 D

A. 设计实体

B. 结构体

C. 输入

D. 输出

95. 执行下列语句后Q的值等于 A 。

……

SIGNAL E: STD_LOGIC_VECTOR (2 TO 5);

SIGNAL Q: STD_LOGIC_VECTOR (9 DOWNTO 2);

E<=(2=>’1’, 4=>’1’, OTHERS=>’0’);

Q<=(2=>E (2), 4=>E (3), 5=>’1’, 7=>E (5), OTHERS=>E (4)); ……

A.“11011011” B. “00110100” C. “11011001” D. “00101100”

96. 在VHDL的IEEE标准库中,预定义的标准逻辑位STD_LOGIC的数据类型中是用表示的。 A.小写字母和数字 B. 大写字母数字 C.大或小写字母和数字 D. 全部是数字

97. 执行MAX+PLUSII的 A 命令,可以为设计电路建立一个元件符号。

A. create default symbol B. simulator C. compiler D. timing analyzer

98. 在VHDL中,条件信号赋值语句WHEN_ELSE属于语句。

A.并行和顺序 B. 顺序 C. 并行 D. 不存在的

99. 在VHDL的IEEE标准库中,预定义的标准逻辑数据STD_LOGIC有 C 种逻辑值。

A. 2 B. 3 C. 9 D. 8

100.一个能为VHDL综合器接受,并能作为一个独立的设计单元的完整的VHDL程序成为。

A.设计输入 B. 设计输出 C. 设计实体 D. 设计结构

一、填空题(本大题共10小题,每空1分,共20 分)

1.一般把EDA技术的发展分为MOS时代、MOS时代和ASIC三个阶段。

2.EDA设计流程包括设计输入、设计实现、实际设计检验和下载编程四个步骤。

4.时序仿真是在设计输入完成之后,选择具体器件并完成布局、布线之后进行的时序关系仿真,因此又称为功能仿真。5.VHDL的数据对象包括变量、常量和信号,它们是用来存放各种类型数据的容器。

6.图形文件设计结束后一定要通过仿真,检查设计文件是否正确。

7.以EDA方式设计实现的电路设计文件,最终可以编程下到FPGA和CPLD芯片中,完成硬件设计和验证。

8.MAX+PLUS的文本文件类型是(后缀名).VHD。

9.在PC上利用VHDL进行项目设计,不允许在根目录下进行,必须在根目录为设计建立一个工程目录。

10.VHDL源程序的文件名应与实体名相同,否则无法通过编译。

二、选择题:(本大题共5小题,每小题3分,共15 分)。

11.在EDA工具中,能完成在目标系统器件上布局布线软件称为(C )

A.仿真器

B.综合器

C.适配器

D.下载器

12.在执行MAX+PLUSⅡ的(d )命令,可以精确分析设计电路输入与输出波形间的延时量。

A .Create default symbol B. Simulator

C. Compiler

D.Timing Analyzer

13.VHDL常用的库是(A )

A. IEEE

B.STD

C. WORK

D. PACKAGE

14.下面既是并行语句又是串行语句的是( C )

A.变量赋值

B.信号赋值

C.PROCESS语句

D.WHEN…ELSE语句

15.在VHDL中,用语句(D )表示clock的下降沿。

A. clock’EVENT

B. clock’EVENT AND clock=’1’

C. clock=’0’

D. clock’EVENT AND clock=’0’

三、名词解释题:(本大题共3题,每小题3分,共计9分)

16. EDA: 电子设计自动化

17.VHDL和FPGA: 超高速硬件描述语言现场可编程门阵列

1.一个项目的输入输出端口是定义在()1-5 ACDCD 6-10 CCACA

A. 实体中;.

B. 结构体中;

C. 任何位置;

D. 进程中。

2. MAXPLUS2中编译VHDL源程序时要求( )

A. 文件名和实体可以不同名;

B. 文件名和实体名无关;

C. 文件名和实体名要相同;

D. 不确定。

3. VHDL语言中变量定义的位置是( )

A. 实体中中任何位置;

B. 实体中特定位置;

C. 结构体中任何位置;

D. 结构体中特定位置。

4.可以不必声明而直接引用的数据类型是( )

A. STD_LOGIC ;

B. STD_LOGIC_VECTOR;

C. BIT;

D. ARRAY。

5. MAXPLUS2不支持的输入方式是( )

A 文本输入;.B. 原理图输入;C. 波形输入;D. 矢量输入。

6.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是( )

A. FPGA全称为复杂可编程逻辑器件;

B. FPGA是基于乘积项结构的可编程逻辑器件;

C. 基于SRAM的FPGA器件,在每次上电后必须进行一次配置;

D. 在Altera公司生产的器件中,MAX7000系列属FPGA结构。

7.下面不属于顺序语句的是( )

A. IF语句;

B. LOOP语句;

C. PROCESS语句;

D. CASE语句。

8. VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,实体体描述的是( )

A. 器件外部特性;

B. 器件的内部功能;

C. 器件的综合约束;

D. 器件外部特性与内部功能。

9. 进程中的信号赋值语句,其信号更新是( )

10. 嵌套使用IF语句,其综合结果可实现:( )

A. 带优先级且条件相与的逻辑电路;

B. 条件相或的逻辑电路;

C. 三态控制电路;

D. 双向控制电路。

一、选择题:(20分)

1.下列是EDA技术应用时涉及的步骤:

A. 原理图/HDL文本输入;

B. 适配;

C. 时序仿真;

D. 编程下载;

E. 硬件测试;

F. 综合

请选择合适的项构成基于EDA软件的FPGA / CPLD设计流程:

A → ___F___ → ___B__ → ____C___ → D → ___E____

2.PLD的可编程主要基于A. LUT结构或者 B. 乘积项结构:

请指出下列两种可编程逻辑基于的可编程结构:

FPGA 基于 ____A_____ CPLD 基于 ____B_____

3.在状态机的具体实现时,往往需要针对具体的器件类型来选择合适的状态机编码。

对于A. FPGA B. CPLD 两类器件:

一位热码状态机编码方式适合于 ____A____ 器件;

顺序编码状态机编码方式适合于 ____B____ 器件;

4.下列优化方法中那两种是速度优化方法:____B__、__D__

A. 资源共享

B. 流水线

C. 串行化

D. 关键路径优化

单项选择题:

5.综合是EDA设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;在下面对综合的描述中,___D___是错误的。

A. 综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;

B. 为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;

C. 综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系不是唯一的。

D. 综合是纯软件的转换过程,与器件硬件结构无关;

6.嵌套的IF语句,其综合结果可实现___D___。

A. 条件相与的逻辑

B. 条件相或的逻辑

C. 条件相异或的逻辑

D. 三态控制电路

7.在一个VHDL设计中Idata是一个信号,数据类型为std_logic_vector,试指出下面那个赋值语句是错误的。D

A. idata <= “00001111”

B. idata <= b”0000_1111”;

C. idata <= X”AB”;

D. idata <= B”21”;

8.在VHDL语言中,下列对时钟边沿检测描述中,错误的是__D___。

A. if clk’event and clk = ‘1’ then

B. if falling_edge(clk) then

C. if clk’event and clk = ‘0’ then

D.if clk’stable and not clk = ‘1’ then

9.请指出Altera Cyclone系列中的EP1C6Q240C8这个器件是属于__C___

A. ROM

B. CPLD

C. FPGA

D.GAL

二、EDA名词解释,(10分)

写出下列缩写的中文(或者英文)含义:

1.ASIC 专用集成电路

2.FPGA 现场可编程门阵列

3.CPLD 复杂可编程逻辑器件

4.EDA 电子设计自动化

5.IP 知识产权核

6.SOC 单芯片系统

1、2. 基于EDA软件的FPGA/CPLD设计流程为:原理图/HDL文本输入→__A__→综合→适配→____B____→编程下载→硬件测试。P14

A. 功能仿真

B. 时序仿真

C. 逻辑综合

D. 配置

3. IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为__A___。P25

A. 软IP

B. 固IP

C. 硬IP

D. 全对

4. 综合是EDA设计流程的关键步骤,在下面对综合的描述中,_____D____是错误的。P15

A. 综合就是把抽象设计层次中的一种表示转化成另一种表示的过程。

B. 综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件。

C. 为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束。

D. 综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的(即综合结果是唯一的)。

5. 大规模可编程器件主要有FPGA、CPLD两类,其中CPLD通过___A__实现其逻辑功能。P42

A. 可编程乘积项逻辑

B. 查找表(LUT)

C. 输入缓冲

D. 输出缓冲

6. VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述_____B___。P274

A. 器件外部特性

B. 器件的内部功能

C. 器件外部特性与内部功能

D. 器件的综合约束

7. 电子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);下列方法中___A___不属于面积优化。P238

A. 流水线设计

B. 资源共享

C. 逻辑优化

D. 串行化

8. 进程中的信号赋值语句,其信号更新是___B____。P134

A. 立即完成

B. 在进程的最后完成

C. 按顺序完成

D. 都不对

9. 不完整的IF语句,其综合结果可实现__A__。P147

A. 时序逻辑电路

B. 组合逻辑电路

C. 双向电路

D. 三态控制电路

10. 状态机编码方式中,其中__A__占用触发器较多,但其简单的编码方式可减少状态译码组合逻辑资源,且易于控制非法状态。P221

A. 一位热码编码

B. 顺序编码

C. 状态位直接输出型编码

D. 格雷码编码

二、VHDL程序填空

1. 下面程序是1位十进制计数器的VHDL描述,试补充完整。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT10 IS

PORT ( CLK : IN STD_LOGIC ;

Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)) ;

END CNT10;

ARCHITECTURE bhv OF CNT10 IS

SIGNAL Q1 : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS (CLK)

BEGIN

IF Q1 > 10 THEN

Q1 <= (OTHERS => '0'); -- 置零

ELSE

Q1 <= Q1 + 1 ; -- 加1

END IF;

END IF;

END PROCESS ;

Q <= Q1;

END bhv;

2. 下面是一个多路选择器的VHDL描述,试补充完整。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY bmux IS

PORT ( sel : IN STD_LOGIC;

A, B : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

Y : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)) ;

END bmux;

ARCHITECTURE bhv OF bmux IS

BEGIN

y <= A when sel = '1' ELSE

B;

END bhv;

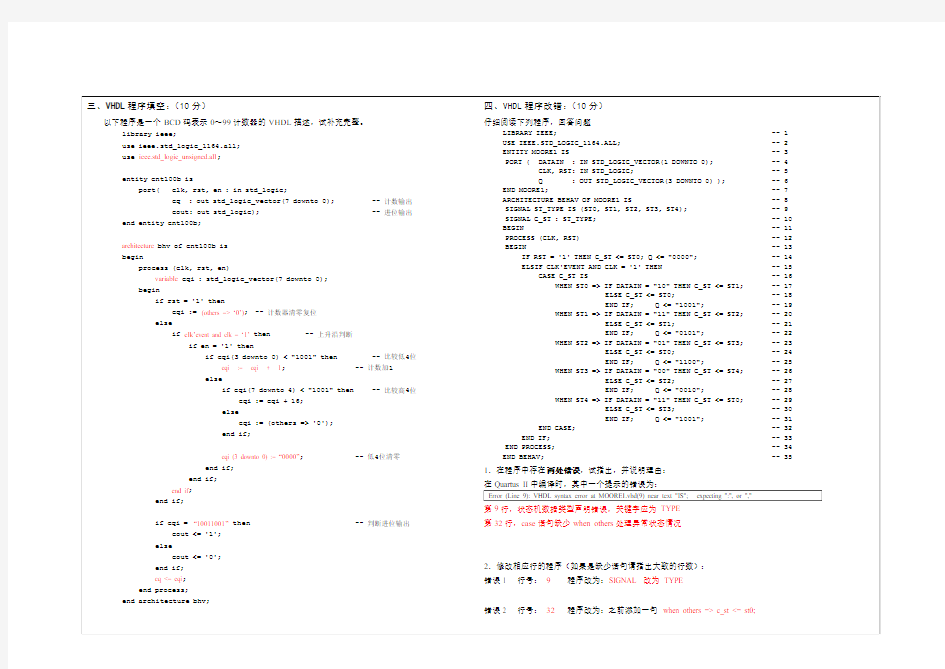

三、VHDL程序改错

仔细阅读下列程序,回答问题

LIBRARY IEEE; -- 1 USE IEEE.STD_LOGIC_1164.ALL; -- 2 ENTITY LED7SEG IS -- 3 PORT ( A : IN STD_LOGIC_VECTOR(3 DOWNTO 0); -- 4

CLK : IN STD_LOGIC; -- 5 LED7S : OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); -- 6 END LED7SEG; -- 7 ARCHITECTURE one OF LED7SEG IS -- 8 SIGNAL TMP : STD_LOGIC; -- 9 BEGIN -- 10 SYNC : PROCESS(CLK, A) -- 11

BEGIN -- 12 IF CLK'EVENT AND CLK = '1' THEN -- 13 TMP <= A; -- 14 END IF; -- 15 END PROCESS; -- 16

OUTLED : PROCESS(TMP) -- 17

BEGIN -- 18 CASE TMP IS -- 19

WHEN "0001" => LED7S <= "0000110"; -- 21

WHEN "0010" => LED7S <= "1011011"; -- 22

WHEN "0011" => LED7S <= "1001111"; -- 23

WHEN "0100" => LED7S <= "1100110"; -- 24

WHEN "0101" => LED7S <= "1101101"; -- 25

WHEN "0110" => LED7S <= "1111101"; -- 26

WHEN "0111" => LED7S <= "0000111"; -- 27

WHEN "1000" => LED7S <= "1111111"; -- 28

WHEN "1001" => LED7S <= "1101111"; -- 29

END CASE; -- 30 END PROCESS; -- 31 END one; -- 32 1.在程序中存在两处错误,试指出,并说明理由:

第14行 TMP附值错误

第29与30行之间,缺少WHEN OTHERS语句

2.修改相应行的程序:

错误1 行号:9程序改为:

TMP : STD_LOGIC_VECTOR(3 DOWNTO 0);

错误2 行号: 29 程序改为:

该语句后添加 WHEN OTHERS => LED7S <= "0000000";

四、阅读下列VHDL程序,画出原理图(RTL级)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY HAD IS

PORT ( a : IN STD_LOGIC;

b : IN STD_LOGIC;

c : OUT STD_LOGIC;

d : OUT STD_LOGIC);

END ENTITY HAD;

ARCHITECTURE fh1 OF HAD IS

BEGIN

c <= NOT(a NAND b);

d <= (a OR b)AND(a NAND b);

END ARCHITECTURE fh1;

五、请按题中要求写出相应VHDL程序

输入端口: clk 时钟信号

rst 异步复位信号 en 计数使能 load 同步装载

data (装载)数据输入,位宽为10

输出端口: q 计数输出,位宽为10 LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY CNT1024 IS

PORT ( CLK, RST, EN, LOAD : IN STD_LOGIC;

DATA : IN STD_LOGIC_VECTOR (9 DOWNTO 0); Q : OUT STD_LOGIC_VECTOR (9 DOWNTO 0) ); END CNT1024;

ARCHITECTURE ONE OF CNT1024 IS BEGIN

PROCESS (CLK, RST, EN, LOAD, DATA)

VARIABLE Q1 : STD_LOGIC_VECTOR (9 DOWNTO 0); BEGIN

IF RST = '1' THEN

Q1 := (OTHERS => '0');

ELSIF CLK = '1' AND CLK'EVENT THEN IF LOAD = '1' THEN Q1 := DATA; ELSE

IF EN = '1' THEN Q1 := Q1 + 1; END IF; END IF; END IF; Q <= Q1; END PROCESS; END ONE;

2. 看下面原理图,写出相应VHDL 描述

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; ENTITY TRI_STATE IS

e

a b y

Y : INOUT STD_LOGIC;

B : OUT STD_LOGIC);

END TRI_STATE;

ARCHITECTURE BEHAV OF TRI_STATE IS

BEGIN

PROCESS (E, A, Y)

BEGIN

IF E = '0' THEN

B <= Y;

Y <= 'Z';

ELSE

B <= 'Z';

Y <= A;

END IF;

END PROCESS;

END BEHAV;

六、综合题

下图是一个A/D采集系统的部分,要求设计其中的FPGA采集控制模块,该模块由三个部分构成:控制器(Control)、地址计数器(addrcnt)、内嵌双口RAM(adram)。控制器(control)是一个状态机,完成AD574的控制,和adram的写入操作。Adram是一个LPM_RAM_DP单元,在wren为’1’时允许写入数据。试分别回答问题

FPGA采集控制

下面列出了AD574的控制方式和控制时序图

AD574逻辑控制真值表(X表示任意)

AD574工作时序:

1.要求AD574工作在12位转换模式,K12_8、A0在control中如何设置

K12_8为‘1’,A0为‘0’

类似书上图8-4

3.对地址计数器模块进行VHDL描述

输入端口:clkinc 计数脉冲

cntclr 计数器清零

输出端口:rdaddr RAM读出地址,位宽10位

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity addr_cnt is

port ( clkinc, cntclr : in std_logic;

wraddr : out std_logic_vector (9 downto 0) ); end addr_cnt;

architecture one of addr_cnt is

signal tmp : std_logic_vector (9 downto 0);

begin

process (clkinc, cntclr)

begin

if clkinc'event and clkinc = '1' then

if cntclr = '1' then

tmp <= (others => '0');

else

tmp <= tmp + 1;

end if;

end if;

end process;

wraddr <= tmp;

end one;

4.根据状态图,试对control进行VHDL描述

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity control is

port ( addata : in std_logic_vector (11 downto 0);

status, clk : in std_logic;

cs, ce, a0, rc, k12_8, clkinc : out std_logic;

rddata : out std_logic_vector (11 downto 0) ); end control;

architecture behav of control is

type con_st is (s0, s1, s2, s3, s4);

signal cst, nst : con_st;

signal lock : std_logic;

signal reg12 : std_logic_vector (11 downto 0);

a0 <= '0';

k12_8 <= '1';

ce <= '1';

cs <= '0';

REGP : process (clk)

begin

if clk'event and clk = '1' then

cst <= nst;

end if;

end process;

COMP : process (cst, status, addata)

begin

case (cst) is

when s0 => rc <= '1'; lock <= '0'; nst <= s1;

when s1 => rc <= '0'; lock <= '0'; nst <= s2;

when s2 => if status = '1' then nst <= s3; end if;

rc <= '1'; lock <= '0';

when s3 => rc <= '1'; lock <= '1'; nst <= s4;

when s4 => rc <= '1'; lock <= '0'; nst <= s0;

when others => nst <= s0;

end case;

end process;

LOCKP : process (lock)

begin

if lock = '1' and lock'event then

reg12 <= addata;

end if;

end process;

rddata <= reg12;

clkinc <= lock; --(或者为NOT LOCK,延后半个时钟)

end behav;

5.已知adram的端口描述如下

ENTITY adram IS

PORT

(

data : IN STD_LOGIC_VECTOR (11 DOWNTO 0); -- 写入数据

wraddress: IN STD_LOGIC_VECTOR (9 DOWNTO 0); -- 写入地址

rdaddress: IN STD_LOGIC_VECTOR (9 DOWNTO 0); -- 读地址

wren : IN STD_LOGIC := '1'; -- 写使能

q : OUT STD_LOGIC_VECTOR (11 DOWNTO 0) -- 读出数据

);

END adram;

姓名: ______________ 工号: 日期:____________ 得分:________________ 焊锡岗位培训考试试题 填空题:(每空2分) 1?电烙铁由哪几部分组成:_______________ 、 _______________ 、________________ 。 2?海绵必须保持潮湿,每隔_________ 小时必须清洗一次。 3?当天工作结束后,不焊接时将烙铁头__________________后重新沾上_____________ 于尖端部分,并将之存放在烙铁架 上并将 _______________ 关闭。 4?烙铁在使用过程中,严禁__________ 否则会造成_________ 断或 _________ 脱落,烙铁头有锡渣时应用_________ 擦拭,严禁 _________ 或___________ ,以免烫伤人或将锡渣抛到产品中。 5?焊锡的目的是将_______ 或_______ 可靠的连接在PCB焊盘或导体上,达到_____________ 和___________ 的作用。 6?我们公司有规定恒温烙铁的温度,一般焊接玻纤板温度设置_____________ C,焊接铝基板设置___________ C。 7?常见焊锡不良项目主要包括__________ 、__________ 、___________ 、__________ 等。 8.烙铁的电源线必须安装___________ 来消除静电,而人体通常带有1000V以上静电,所以在接触半导体电子产品的 作业过程中必须戴____________ 。(3分) 二.判断题:(5*2分共10分) 1焊锡时产生的烟雾对人体有害,所以在焊接时要使用抽风装置,抽走焊锡产生的烟雾,避免烟吸入鼻孔。()2?烙铁头使用时间过久,会出现尖端弯曲,空洞等,焊接时会感觉到熔锡困难、划板等现象,此时应及时更换新的,否则将影响焊接质量和效率。()3?不同元件,耐热程度不同,所以烙铁头的温度高低,直接影响到元件的使用寿命和焊接质量,因此,焊接时,必 须根据工艺要求设置烙铁温度,且校正好后严禁随意调节。()4?烙铁不使用時应将烙铁头清洗干净,在烙铁头上加锡,冷却保存,防止烙铁头氧化。()5?焊锡过程当中需离岗时,应将烙铁放回烙铁架中,不可直接摆放于工作台面,以免引起火灾等。() 三、简答题(4*10分共40分) 1.焊接前注意事项。 2?焊锡步骤。 3?简述撤开电烙铁的步骤及注意事项。

第一章 1-1 EDA技术与ASIC设计和FPGA开发有什么关系?FPGA/CPLD在ASIC设计中有什么用途? 答:利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现;FPGA和CPLD是实现这一途径的主流器件。FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。FPGA和CPLD的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。FPGA/CPLD在ASIC设计中,属于可编程ASIC的逻辑器件;使设计效率大为提高,上市的时间大为缩短。 1-2与软件描述语言相比,VHDL有什么特点? P6 答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。综合器将VHDL程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。 l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么? P5 什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。 有哪些类型?答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。(3)从RTL级表示转换到逻辑门(包括触发器)的表示,即逻辑综合。(4)从逻辑门表示转换到版图表示(ASIC设计),或转换到FPGA的配置网表文件,可称为版图综合或结构综合。 综合在电子设计自动化中的地位是什么?答:是核心地位(见图1-3)。综合器具有更复杂的工作环境,综合器在接受VHDL程序并准备对其综合前,必须获得与最终实现设计电路硬件特征相关的工艺库信息,以及获得优化综合的诸多约束条件信息;根据工艺库和约束条件信息,将VHDL程序转化成电路实现的相关信息。 1-4在EDA技术中,自顶向下的设计方法的重要意义是什么? P7~10 答:在EDA技术应用中,自顶向下的设计方法,就是在整个设计流程中各设计环节逐步求精的过程。 1-5 IP在EDA技术的应用和发展中的意义是什么? P11~12 答:IP核具有规范的接口协议,良好的可移植与可测试性,为系统开发提供了可靠的保证。 1-6 叙述EDA的FPGA/CPLD设计流程。P13~16 答:1.设计输入(原理图/HDL文本编辑);2.综合;3.适配;4.时序仿真与功能仿真;5.编程下载;6.硬件测试。

(A卷) 赣南师范学院 2010—2011学年第一学期期末考试试卷(A卷)(闭卷)年级 2008 专业电子科学与技术(本)课程名称 EDA技术基础 2、学生答题前将密封线外的内容填写清楚,答题不得超出密封线; 3、答题请用蓝、黑钢笔或圆珠笔。 一、单项选择题(30分,每题2分) 1.以下关于适配描述错误的是 B A.适配器的功能是将综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件 B.适配所选定的目标器件可以不属于原综合器指定的目标器件系列 C.适配完成后可以利用适配所产生的仿真文件作精确的时序仿真 D.通常,EDAL软件中的综合器可由专业的第三方EDA公司提供,而适配器则需由FPGA/CPLD供应商提供 2.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 D 。 A.器件外部特性B.器件的综合约束 C.器件外部特性与内部功能D.器件的内部功能 3.下列标识符中, B 是不合法的标识符。 A.State0 B.9moon C.Not_Ack_0 D.signall 4.以下工具中属于FPGA/CPLD集成化开发工具的是 D A.ModelSim B.Synplify Pro C.MATLAB D.QuartusII 5.进程中的变量赋值语句,其变量更新是 A 。 A.立即完成B.按顺序完成 C.在进程的最后完成D.都不对 6.以下关于CASE语句描述中错误的是 A A.CASE语句执行中可以不必选中所列条件名的一条 B.除非所有条件句的选择值能完整覆盖CASE语句中表达式的取值,否则最末一个条件句的选择必须加上最后一句“WHEN OTHERS=><顺序语句>” C.CASE语句中的选择值只能出现一次 D.WHEN条件句中的选择值或标识符所代表的值必须在表达式的取值范围 7.以下哪个程序包是数字系统设计中最重要最常用的程序包 B A.STD_LOGIC_ARITH B.STD_LOGIC_1164 C.STD_LOGIC_UNSIGNED D.STD_LOGIC_SIGNED 8.基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→A →综合→适配→时序仿真→编程下载→硬件测试。 A.功能仿真B.逻辑综合C.配置D.引脚锁定 9.不完整的IF语句,其综合结果可实现 D A.三态控制电路B.条件相或的逻辑电路 C.双向控制电路D.时序逻辑电路 10.下列语句中,属于并行语句的是A A.进程语句B.IF语句C.CASE语句D.FOR语句11.综合是EDA设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;在下面对综合的描述中, C 是错误的。 A.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件 B.综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系不是唯一的 C.综合是纯软件的转换过程,与器件硬件结构无关 D.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束 12.CPLD的可编程是主要基于什么结构 D 。 A.查找表(LUT)B.ROM可编程 C.PAL可编程D.与或阵列可编程 13.以下器件中属于Altera 公司生产的是 B A.ispLSI系列器件B.MAX系列器件 C.XC9500系列器件D.Virtex系列器件 14.在VHDL语言中,下列对时钟边沿检测描述中,错误的是 D A.if clk'event and clk = '1' then B.if clk'stable and not clk = '1' then C.if rising_edge(clk) then D.if not clk'stable and clk = '1' then 15.以下关于状态机的描述中正确的是 B A.Moore型状态机其输出是当前状态和所有输入的函数 B.与Moore型状态机相比,Mealy型的输出变化要领先一个时钟周期C.Mealy型状态机其输出是当前状态的函数

信号发生器的设计 要求: (1) 产生方波、三角波、锯齿波、正弦波 (2)产生波形的模式可选 (3)频率为10KHz 设计方案: 1.总体设计思路 1.1 设计步骤 此设计将按模块式实现,据设计要求,设计总共分四大步份完成:(1)产生波形(四种波形:方波、三角波、矩形波和锯齿波)信号;(3)频率为10KHZ 幅度固定; 1.2设计思想 利用VHDL编程,依据基本数字电路模块原理进行整合。系统各部分所需工作时钟信号由输入系统时钟信号得到。总体设计框图如下图1所示: 波形输出

2. 方案论证 2.1方案 采用VHDL语言来编程,然后下载文件到FPGA来实现。VHDL语言是电子设计领域的主流硬件描述语言,具有很强的电路描述和建模能力,能从多个层次对数字系统进行建模和描述,从而大大降低了硬件设计任务,提高了设计效率和可靠性,要比模拟电路快得多。该方案是利用FPGA具有的静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改,极大地提高了电子系统设计的灵活性和通用性,设计图如图2。 图2 FPGA总体设计图 (需要修改) 通过FPGA软件扫描方式将波形数据读出传输给DAC0832(为8分辨率的D/A 转换集成芯片㈠ )产生波形输出。这种方法在软、硬件电路设计上都简单,且与 我们的设计思路紧密结合。 3硬件选择 4软件设计 4.1.1波形产生模块 本设计用VHDL语言根据傅立叶函数采集点进行扫描,分别产生正弦波、三角波和矩形波。以下介绍各种常用周期信号的傅立叶函数展开式。 4.1.3正弦波 (1)设计思想 正弦波发生分为两个步骤,即正弦波幅值采样存储和正弦波波形的还原输出。幅值采样是将一个周期正弦波进行64等分,如图3所示,将64个采样点

新上岗人员培训试题 1.通常认为,医疗机构最佳的干手方法为(B ) A.感应式烘干机 B.一次性干手纸 C.个人专用小毛巾 D.自然干燥 2.下列关于外科口罩的描述错误的是(C )? A.能阻挡血液、体液和飞溅物 B.标准的外科口罩分3层,分别为阻水层、过滤层、吸湿层。 C.为开放性肺结核患者进行气管镜检查时,应佩戴双层医用外科口罩 D.牙科医生诊疗时应佩戴医用外科口罩 3.下列哪种情况无需穿隔离衣(C ) A.为HIV患者清理呕吐物时 B.为多重耐药菌感染患者吸痰时 C.为糖尿病携带HBV的患者进行晨间护理时 D.护理大面积烧伤患者时 4.经空气传播疾病的主要预防策略,说法错误的是(B) A.将患者安置在负压病房 B.接触疑似患者时,必须佩戴医用外科口罩 C.严格病房空气消毒 D.如病情允许,患者应佩戴医用外科口罩 5.对于重症监护病房的门把手、床头柜等高频接触环境表面,通常宜采用哪种清洁消毒管理策略(C )? A.清水擦拭 B.清水擦拭+清洁剂辅助清洁 C.清水擦拭+250mg/L含氯消毒剂消毒或使用消毒湿巾擦拭 D.清水擦拭+1000mg/L含氯消毒剂消毒 6.以下哪些情况,可初步判定发生了医院感染( C) A.患者留置导尿管期间,尿液培养发现产ESBLs大肠埃希菌 B.气管插管病人,痰标本培养出白色念珠菌 C.术后高热病人,经留置的中央导管抽血培养10小时报告有革兰阳性球菌生长,而同时经外周静脉抽血36小时后报告革兰阳性球菌生长 D.胆囊癌术后2周,经引流管的胆汁培养分离到粪肠球菌

7.目前认为引起抗生素相关腹泻最常见的病原体是(D) A.白色念珠菌 B.金黄色葡萄球菌 C.铜绿假单胞菌 D.艰难梭菌 8.某内科病区进行手卫生依从性监测,其中医护人员手卫生观察时机为25次,实际执行手卫生20人次,正确执行手卫生18人次。请问,该内科病区的手卫生依从性和正确率分别是(A ) A.80%,90% B.90%,80% C.72%,80% D.80%,72% 9.某患者,女,58岁,拟在全麻下行二尖瓣置换术,术前鼻拭子筛查为MRSA阳性,下列预防手术部位感染的措施中,不推荐哪一项?( C ) A.术前使用莫匹罗星软膏去定植至手术日 B.术前晚使用洗必泰沐浴 C.手术切口涂抹莫匹罗星软膏 D.切皮前2小时静滴万古霉素,术后48小时停药 10.下列哪项措施不是预防导管相关血流感染(CLABSI)的核心措施(A )? A.加强室内的空气净化 B.落实最大无菌屏障 C.首选2%氯己定-乙醇消毒剂进行穿刺部位皮肤消毒 D.每日评估留置中央静脉导管(CVC)的必要性,尽早拔除导管 11.为了有效预防呼吸机相关肺炎(VAP)的发生,对于长期使用呼吸机的患者,呼吸机外部管路的处置,下列说法不正确的是(A ) A.应每日更换 B.可每周更换 C.应一人一用一消毒/灭菌或一次性使用 D.不要短于48小时更换,但管路有肉眼可见污染时,则应及时更换 12.为预防留置导尿患者发生导尿管相关尿路感染,下列关于尿道口、会阴区清洁消毒的策略,错误的是(C ) A.每日用生理盐水或无菌水清洗尿道口、会阴区 B.每日用温开水清洁尿道口、会阴区 C.每日使用抗菌溶液清洁尿道口、会阴区 D.大、小便失禁患者在清洁后应进行消毒 13.在转运人感染H7N9疑似或确诊患者途中,如病情容许时应给患者佩戴哪类口罩(B )?

EDA期末试卷 一、填空题 1.一般把EDA技术的发展分为MOS时代、CMOS 代和ASIC 三个阶段。 2.EDA设计流程包括设计输入、设计实现、实际设计检验和下载编程四个步骤。 3.EDA设计输入主要包括图形输入、HDL文本输入和状态机输入。 4.时序仿真是在设计输入完成之后,选择具体器件并完成布局、布线之后进行的时序关系仿真,因此又称为功能仿真。5.VHDL的数据对象包括变量、常量和信号,它们是用来存放各种类型数据的容器。 6.图形文件设计结束后一定要通过仿真,检查设计文件是否正确。 7.以EDA方式设计实现的电路设计文件,最终可以编程下载 到FPGA 和CPLD 芯片中,完成硬件设计和验证。 8.MAX+PLUS的文本文件类型是(后缀名).VHD 。9.在PC上利用VHDL进行项目设计,不允许在根目 录下进行,必须在根目录为设计建立一个工程目录(即文件夹)。

10.VHDL源程序的文件名应与实体名相同,否则无法通过编译。 二、选择题:。 11.在EDA工具中,能完成在目标系统器件上布局布线软件称为(C )A.仿真器 B.综合 器 C.适配器 D.下载器12.在执行MAX+PLUSⅡ的(D )命令,可以精确分析设计电路输入与输出波形间的延时量。 A .Create default symbol B. Simulator C. Compiler D. Timing Analyzer 13.VHDL常用的库是(A ) A. IEEE B.STD C. WORK D. PACKAGE 14.下面既是并行语句又是串行语句的是( C ) A.变量赋值 B.信号赋值 C.PROCESS语 句 D.WHEN…ELSE语句 15.在VHDL中,用语句(D )表示clock的下降沿。

1.简单PLD器件包括哪几种类型的器件?他们之间有什么相同点和 不同点? 答:PLD器件一般可分为4种:PROM、PLA、PAL、GAL器件 相同点: 简单PLD的典型结构是由与非门阵列、或门阵列组成,能够以“积之和” 的形式实现布尔逻辑函数,因为其任意一个组合逻辑都可以用“与或”表达式来描述,所以能够完成大量的组合逻辑功能,并且具有较高的速度和较好的性能。 不同点: PROM:(1)与阵列固定,或阵列可编程 (2)当输入的数目太大时,器件功耗增加,巨大阵列开关时间也会导 致其速度缓慢,但其价格低,易于编程,没有布局、布线问题,性能 完全可以预测。 PLA:(1)与阵列和或阵列都可编程 (2)由于与阵列可编程,使得PROM中由于输入增加而导致规模增加的问题不复存在,从而有效地提高芯片的利用率,其用于含有复杂的随 机逻辑值换的场合是较为理想,但其慢速特性和相对高的价格妨碍了 它被广泛使用。 PAL:(1)或阵列固定,与阵列可编程 (2)与阵列可编程特性使输入项可以增多,而固定的或阵列又使器件得以简化。在这种结构中,每个输出是若干乘积项之和,乘积项数目有 时固定的。其结构对于大多数逻辑函数是有效的,同时此结构也提供 了较高的性能和速度,一度成为PLD发展史的主流。 GAL:其吸收先进的浮栅技术,并与CMOS的静态RAM结合,成了E2PROM 技术,从而使GAL具有了可电擦写、可重复编程、可设置加密功能。 GAL的输出可由用户来定义,他的每个输出端都集成着一个可编程的 输出逻辑宏单元。 2.Altera公司MAX7000系列CPLD有什么特点? MAX7000系列是高密度、高性能的CMOS CPLD,采用先进的0.8umCMOS EEPROM技术制造,它提供600~5000可用门,引线端子到引线端子的延时为6ns,计数器频率可达151.5MHz,它主要有逻辑阵列块、宏单元、扩展乘积项、可编程连线阵列和I/O控制模块组成。

自动化培训考试试题姓名: 一、填空: 1、请写出STEP7中M区位、字节、字、双字表示形式 。 2、十六进制的1A,转变为十进制是。二进制数111101等于十进制数的。 3、请写出SIEMENS PLC在工业中的三种网络通讯方式:、 、。 4、PLC机的主要特点是、、。 5基本逻辑门电路有、、、、、利用此几种基本逻辑门电路的不同组合,可以构成各种复杂的逻辑门电路。 6、机电一体化’的英文单词。 7、STEP7基本软件提供、、等标准化的PLC编程语言。 8、ET200M系统中的主要接口通讯模块有________、_______________、_____________三种,ET200M与控制站采用通讯。 9、在用PROFIBUS通讯时,其两端的通讯连接器开关应拨到_____。 10、在用PROFIBUS—DP通讯时,当硬件下装后发现ET200M上的通讯模块与CPU上DP的同时闪亮,其可能的故障为____。 11、I/O变量的类型:OUTPUT为______型,INPUT______型,BOTH_________型。 12、要组态并生成趋势曲线,必须首先在__________________将你想显示的数据进行存档。 13、SIEMENS控制系统上位机组态软件为__________________,下位编程组态软件为 __________________。 14、控制系统一般由_______________、_______________、_____________构成。 15、WINCC主要功能有__________________、__________________、__________________、__________________、__________________等

精品文档 一、单项选择题(30分)9.嵌套使用IF语句,其综合结果可实现 A 。A.带优先级且条件相与的逻辑电路1.以下描述错误的是 C B.条 件相或的逻辑电路 C.三态控制电路是A.QuartusIIAltera提供的FPGA/CPLD集成开发环境D.双向控制电路 10.在VHDLAlteraB.是世界上最大的可编程逻辑器件供应商之一语言中,下列对时钟边沿检测描述中,错误的是 D 。 A.if clk'event and clk = ‘1' then B.if falling_edge(clk) then 前一代C.MAX+plusII是AlteraFPGA/CPLD集成开发环境QuartusII的更 C.if clk'event and clk = ‘0' then 新换代新产品D.if clk'stable and not clk = ‘1' then 11.下列那个流程是正确的基于.DQuartusII完全支持VHDL、Verilog的设计流程EDA软件的FPGA / CPLD设计流程 B A.原理图/HDL文本输入→适配→综合→功能仿真→编程下载→硬件测试开发工具中的专用综合器的是2.以下工具中属于FPGA/CPLD B B.原理图/HDL文本输入→功能仿真→综合→适配→编程下载→硬件测试 C .Active HDL D.QuartusII Leonardo Spectrum .AModelSim B.C.原理图/HDL文本输入→功能仿真→综合→编程下载→→适配硬件测试;.3以下器件中属于Xilinx 公司生产的是 C /HDL文本输入→功能仿真→适配→编程下载→综合→硬件测试 D.BMAX系列器件.原理图A.ispLSI系列器件 )语句的语句结构及语法规则语言中,下列对进程(PROCESS系列器件 C.XC9500系列器件D.FLEX 12.在VHDL 。A 的描述中,正确的是以下关于信号和变量的描述中错误的是4. B 为一无限循环语句;敏感信号发生更新时启动进程,执行完..信号是描述硬件系统的基本数据对象,它的性质类似于连接线PROCESSAA .信号的定义范围是结构体、进程B 成后,等待下一次进程启动C.除了没有方向说明以外,信号与实体的端口概念是一致的B.敏感信号参数表中,应列出进程中使用的所有输入信号CD.在进程中不能将变量列入敏感信号列表中.进程由说明部分、结构体部分、和敏感信号参数表三部分组成D.当前进程中声明的变量也可用于其他进程以下关于状态机的描述中正确的是5. B B MooreA.型状态机其输出是当前状态和所有输入的函数13.下列语句中,不属于并行语句的是 语句B.CASE 型的输出变化要领先一个时钟周期型状态机相比,.与BMooreMealy A.进程语句 …语句…ELSE D.WHEN .元件例化语句MealyC.型状态机其输出是当前状态的函数 C 设计现行工作VHDL语言共支持四种常用库,其中哪种库是用户的14.以上都不对D .VHDL B 下列标识符中,.库是不合法的标识符。6 END BPP0 A...D .CNot_Ack sig D

班级 学号 姓名 密 封 线 内 不 得 答 题 一、单项选择题(30分) 1.以下描述错误的是 C A .QuartusII 是Altera 提供的FPGA/CPLD 集成开发环境 B .Altera 是世界上最大的可编程逻辑器件供应商之一 C .MAX+plusII 是Altera 前一代FPGA/CPL D 集成开发环境QuartusII 的更新换代新产品 D .QuartusII 完全支持VHDL 、Verilog 的设计流程 2.以下工具中属于FPGA/CPLD 开发工具中的专用综合器的是 B A .ModelSim B .Leonardo Spectrum C .Active HDL D .QuartusII 3.以下器件中属于Xilinx 公司生产的是 C A .ispLSI 系列器件 B .MAX 系列器件 C .XC9500系列器件 D .FLEX 系列器件 4.以下关于信号和变量的描述中错误的是 B A .信号是描述硬件系统的基本数据对象,它的性质类似于连接线 B .信号的定义范围是结构体、进程 C .除了没有方向说明以外,信号与实体的端口概念是一致的 D .在进程中不能将变量列入敏感信号列表中 5.以下关于状态机的描述中正确的是 B A .Moore 型状态机其输出是当前状态和所有输入的函数 B .与Moore 型状态机相比,Mealy 型的输出变化要领先一个时钟周期 C .Mealy 型状态机其输出是当前状态的函数 D .以上都不对 6.下列标识符中, B 是不合法的标识符。 A .PP0 B .END C .Not_Ack D .sig 7.大规模可编程器件主要有FPGA 、CPLD 两类,下列对CPLD 结构与工作原理的描述中,正确的是 C 。 A .CPLD 即是现场可编程逻辑器件的英文简称 B .CPLD 是基于查找表结构的可编程逻辑器件 C .早期的CPL D 是从GAL 的结构扩展而来 D .在Altera 公司生产的器件中,FLEX10K 系列属CPLD 结构 8.综合是EDA 设计流程的关键步骤,在下面对综合的描述中, D 是错误的。 A .综合就是把抽象设计层次中的一种表示转化成另一种表示的过程 B .综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD 的基本结构相映射的网表文件 C .为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束 D .综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的(即综合结果是唯一的) 9.嵌套使用IF 语句,其综合结果可实现 A 。 A .带优先级且条件相与的逻辑电路 B .条件相或的逻辑电路 C .三态控制电路 D .双向控制电路 10.在VHDL 语言中,下列对时钟边沿检测描述中,错误的是 D 。 A .if clk'event and clk = ‘1’ then B .if falling_edge(clk) then C .if clk’event and clk = ‘0’ then D .if clk’stable and not clk = ‘1’ then 11.下列那个流程是正确的基于EDA 软件的FPGA / CPLD 设计流程 B A .原理图/HDL 文本输入→适配→综合→功能仿真→编程下载→硬件测试 B .原理图/HDL 文本输入→功能仿真→综合→适配→编程下载→硬件测试 C .原理图/HDL 文本输入→功能仿真→综合→编程下载→→适配硬件测试; D .原理图/HDL 文本输入→功能仿真→适配→编程下载→综合→硬件测试 12.在VHDL 语言中,下列对进程(PROCESS )语句的语句结构及语法规则的描述中,正确的是 A 。 A .PROCESS 为一无限循环语句;敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动 B .敏感信号参数表中,应列出进程中使用的所有输入信号 C .进程由说明部分、结构体部分、和敏感信号参数表三部分组成 D .当前进程中声明的变量也可用于其他进程 13.下列语句中,不属于并行语句的是 B A .进程语句 B .CAS E 语句 C .元件例化语句 D .WHEN …ELSE …语句 14.VHDL 语言共支持四种常用库,其中哪种库是用户的VHDL 设计现行工作 库 D A .IEEE 库 B .VITAL 库 C .STD 库 D .WORK 库 15.VHDL 语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 D 。 A .器件外部特性 B .器件的综合约束 C .器件外部特性与内部功能 D .器件的内部功能 二、EDA 名词解释,写出下列缩写的中文含义(10分) 1.CPLD :复杂可编程逻辑器件 2.ASIC :专用集成电路 3.LUT :查找表 4.EDA :电子设计自动化 5.ROM :只读存储器 三、程序填空题(20分) 以下是一个模为24(0~23)的8421BCD 码加法计数器VHDL 描述,请补充完整

计算器设计 专业:电子信息工程 设计者:

摘要 本文介绍了一个简单的计算器的设计,该设计采用了现场可编程逻辑器件FPGA设计,并基于VHDL语言实现加减乘除功能,并用十进制显示在数码管上。系统由计算部分、输入部分、选择部分、输出部分组成,计算部分为加法器、减法器、乘法器和除法器组成。使用Altera公司的QuartusII开发软件进行功能仿真并给出仿真波形,并下载到试验箱,用实验箱上的按键开关模拟输入,用数码管显示十进制计算结果。通过外部按键可以完成四位二进制数的加、减、乘、除四种运算功能,其结果简单,易于实现。 关键字:VHDL,计算器,QuartusII

目录 一.实验目的 (4) 二、流程图 (4) 三.顶层原理图 (5) 四、各个模块 (6) (1)加法器模块 (6) 1、封装元件 (6) 2、加法器程序 (7) 3、仿真结果 (7) (2)减法器模块 (8) 1、封装元件 (8) 2、减法器程序 (9) 3、仿真结果 (10) 4、硬件运行结果 (11) (3)乘法器模块 (12) 1、封装元件 (12) 2、乘法器的设计思想 (12) 3、乘法器程序 (13) 4、仿真结果 (14) 5、硬件运行结果 (14) (4)除法器模块 (15) 1、封装元件 (15) 2、除法器设计思想 (15) 3、除法器程序 (16) 4、仿真结果 (16) 5、硬件运行结果 (17) (5)8位除法器 (18) 1、封装元件 (18) 2、8位除法器设计思想 (18) 3、8位除法器程序 (19) 4、仿真结果 (21) (6)数码管七段译码电路 (22) 1、封装元件 (22) 2、共阴极七段显示码十六进制转换表 (22) 3、七段译码器程序 (23) 4、仿真结果 (23) (7)选择模块 (24) 1、封装元件 (24) 2、程序 (25) 五、管脚锁定 (25) 六、小结与收获 (26)

B卷 一、选择题(每题2分,共40分) 1.软件项目的可行性研究要进行一次( C )需求分析。 A.详细的B.全面的C.简化的、压缩的D.彻底的 2、系统流程图用于可行性分析中的( A )的描述。 A.当前运行系统B.当前逻辑模型C.目标系统D.新系统 3、程序的三种基本控制结构的共同特点是( D ) A.不能嵌套使用B.只能用来写简单程序 C.已经用硬件实现D.只有一个入口和一个出口 4、维护中,因误删除一个标识符而引起的错误是( C )副作用。 A.文档B.数据C.编码D.设计 5、( D )是以提高软件质量为目的的技术活动。 A.技术创新B.测试C.技术创造D.技术评审 6、面向对象方法学的出发点和基本原则是尽可能模拟人类习惯的思维方式,分析、设计和 实现一个软件系统的方法和过程,尽可能接近于人类认识世界解决问题的方法和过程。因此面向对象方法有许多特征,如软件系统是由对象组成的;( C );对象彼此之间仅能通过传递消息互相联系;层次结构的继承。 A.开发过程基于功能分析和功能分解B.强调需求分析重要性 C.把对象划分成类,每个对象类都定义一组数据和方法D.对既存类进行调整 7、原型化方法是用户和设计者之间执行的一种交互构成,适用于( A )系统。 A.需求不确定性高的B.需求确定的C.管理信息D.实时 8、为了提高测试的效率,应该( D )。 A.随机地选取测试数据B.取一切可能的输入数据作为测试数据

C.在完成编码以后制定软件的测试计划D.选择发现错误可能性大的数据作为测试数据 9、使用白盒测试方法时,确定测试数据应根据( A )和指定的覆盖标准。 A.程序的内部逻辑B.程序的复杂结构C.使用说明书D.程序的功能 10、开发软件所需高成本和产品的低质量之间有着尖锐的矛盾,这种现象称做( C ) A.软件工程 B.软件周期 C.软件危机 D.软件产生 11、软件按照设计的要求,在规定时间和条件下达到不出故障,持续运行的要求的质量特性 称为( B )。 A.可用性 B.可靠性 C.正确性 D.完整性 12、瀑布模型的关键不足在于( B ) A.过于简单 B.不能适应需求的动态变更 C.过于灵活 D.各个阶段需要进行评审 13、软件维护的副作用主要有以下哪几种( C ) A.编码副作用、数据副作用、测试副作用 B.编码副作用、数据副作用、调试副作用 C.编码副作用、数据副作用、文档副作用 D.编码副作用、文档副作用、测试副作用 14、在下面的软件开发方法中,哪一个对软件设计和开发人员的开发要求最高( B)。 A、结构化方法 B、原型化方法 C、面向对象的方法 D、控制流方法 15、软件工程方法学的目的是:使软件生产规范化和工程化,而软件工程方法得以实施的主 要保证是( C)。 A、硬件环境 B、软件开发的环境 C、软件开发工具和软件开发的环境 D、开发人员的 素质 16、软件开发模型是指软件开发的全部过程、活动和任务的结构框架。主要的开发模型有瀑 布模型、演化模型、螺旋模型、喷泉模型和智能模型。螺旋模型将瀑布模型和演化模型相结合,并增加了(1),它建立在(2)的基础上,沿着螺线自内向外每旋转一圈,就得到(2)的一个新版本。喷泉模型描述了(3)的开发模型,它体现了这种开发方法创建软件的过程所固有的(4)和(5)的特征。 B(1) A、系统工程 B、风险分析 C、设计评审 D、进度控制 D(2) A、模块划分 B、子程序分解 C、设计; D、原型 A(3) A、面向对象 B、面向数据流 C、面向数据结构 D、面向事件驱动 D(4) A、归纳 B、推理 C、迭代 D、递归 A(5) A、开发各阶段之间无“间隙” B、开发各阶段分界明显 C、部分开发阶段分界明显 D、开发过程不分段 二、判断题(每题2分,共30分) 1.螺旋模型是在瀑布模型和增量模型的基础上增加了风险分析活 动。( T ) 2.数据字典是对数据流图中的数据流,加工、数据存储、数据的源和终点进行详细定义。 ( F ) 3.JAVA语言编译器是一个CASE工具。( T )。

2007 至2008学年度第二学期期末考核 《EDA》试题(开卷) 卷号:B 时间:120 分钟 2008 年6 月 专业:电子信息工程学号:姓名: 一填空题(20分) 1、VHDL 2、DEVICE.LIB SYMBOLS.LIB 3、实际零件焊接到电路板时所指示的外观和焊点的位置 4、电子设计自动化电子CAD技术 5、A L T E R A,X I L I N X 6、WAIT 7、电路连接 8、SRAM-BASE 9、2.54mm 300mil 10、元件外观和元件引线端子的图形 二名词解释(20分) 1 PLD/FPGA PLD是可编程逻辑器件(Programable Logic Device)的简称,FPGA是现场可编程门阵列(Field Programable Gate Array)的简称,两者的功能基本相同,只是实现原理略有不同,所以我们有时可以忽略这两者的区别,统称为可编程逻辑器件或PLD/FPGA。 2.过孔 当需要连接两个层面上的铜膜走线时就需要过孔(Via),过孔 又称为贯孔、沉铜孔和金属化孔。 过孔分为穿透式(Through)、半隐藏式(Blind)和隐藏式(Buried) 3.铜膜线 就是连接两个焊盘的导线,称为Track,一般铜膜线走线在不 同层面取不同的走向,例如顶层走水平线,则底层走垂直线。顶 层和底层走线之间的连接采用过孔(Via)连接。 4 PROM、PAL和PLA PROM:与阵列固定,或阵列可编程,一般用作存储器,其输入为存储器的地址,输出为存储器单元的内容。但输入的数目太大时,器件功耗增加,其局限性大。 PLA:与或阵列均可编程,但是其慢速特性和相对PAL、PROM而高得多的价格妨碍了它被广泛使用。PAL:或阵列固定,与阵列可编程,其第二代产品GAL具有了可电擦写、可重复编程、可设置加密的功能。 5 自顶向下的/自下而上的设计方法 自下而上的设计方法,使用该方法进行硬件设计是从选择具体元器件开始,并用这些元器件进行逻辑电路设计,从而完成系统的硬件设计,然后再将各功能模块连接起来,完成整个系统的硬件设计,自顶向下的设计方法就是从系统的总体要求出发,自顶向下分三个层次对系统硬件进行设计。 第一个层次是行为描述第二个层次是数据流描述第三个层次为逻辑综合

1.一个项目的输入输出端口是定义在( A )1-5 ACDCD 6-10 CCACA A. 实体中;. B. 结构体中; C. 任何位置; D. 进程中。 2. MAXPLUS2中编译VHDL源程序时要求( C ) A. 文件名和实体可以不同名; B. 文件名和实体名无关; C. 文件名和实体名要相同; D. 不确定。 3. VHDL语言中变量定义的位置是(D ) A. 实体中中任何位置; B. 实体中特定位置; C. 结构体中任何位置; D. 结构体中特定位置。 4.可以不必声明而直接引用的数据类型是(C ) A. STD_LOGIC ; B. STD_LOGIC_VECTOR; C. BIT; D. ARRAY。 5. MAXPLUS2不支持的输入方式是(D ) A 文本输入;.B. 原理图输入;C. 波形输入;D. 矢量输入。 6.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是( C ) A. FPGA全称为复杂可编程逻辑器件; B. FPGA是基于乘积项结构的可编程逻辑器件; C. 基于SRAM的FPGA器件,在每次上电后必须进行一次配置; D. 在Altera公司生产的器件中,MAX7000系列属FPGA结构。 7.下面不属于顺序语句的是( C ) A. IF语句; B. LOOP语句; C. PROCESS语句; D. CASE语句。 8. VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,实体体描述的是( A ) A. 器件外部特性; B. 器件的内部功能; C. 器件的综合约束; D. 器件外部特性与内部功能。 9. 进程中的信号赋值语句,其信号更新是( C ) A. 按顺序完成; B. 比变量更快完成; C. 在进程的最后完成; D. 都不对。 10. 嵌套使用IF语句,其综合结果可实现:(A ) A. 带优先级且条件相与的逻辑电路; B. 条件相或的逻辑电路; C. 三态控制电路; D. 双向控制电路。 一、单项选择题:(20分) 1. IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述

EDA上机实验报告 实验1:T触发器 一、实验目的 1、认识T触发器。 2、掌握T触发器的逻辑功能和动作特点。

3、利用VHDL软件实现具有T触发器的数字电路。 二、实验原理 设计的是一个不带置位的T触发器,数据输入端为t,时钟输入端为clk,两个反相的输出端a,b。 当t=0时,T触发器保持前一状态的值; 当t=1时,T触发器状态在时钟边沿(上升沿)的作用下发生翻转。 三、程序及仿真图 library ieee; use ieee.std_logic_1164.all; entity T is port(t, clk: in std_logic; a: out std_logic; b: out std_logic); end T; architecture Behavioral of T is signal buf: std_logic:= '0'; begin process(clk) begin if clk' event and clk = '1' then if(t ='1') then buf <= not buf;

else buf <= buf; end if; end if; end process; a <= buf; b <= not buf; end Behavioral; 信号t的设置: 参数设置:

仿真图: 四.实验遇到的难点以及解决方法

开始输入程序的时候,综合总是显示正确,但是无法仿真成功,究其原因是没有对信号buf赋初值。在程序综合的时候,信号的初 值不是必须的,综合时初值是被忽略的,如果没有给信号buf赋初值,可成功综合但不能成功仿真,一定要注意这一点。 实验2函数发生器 一、实验原理及方法 脉冲发生器就是要产生一个脉冲波形,而可控脉冲发生器则是 要产生一个周期和占空比可变的脉冲波形。可控脉冲发生器的 实现原理比较简单,可以简单的理解为一个计数器对输入的时 钟信号进行分频的过程。通过改变计数器的上线来达到改变周 期的目的,通过改变电平翻转的阀值来达到改变占空比的目的。 二、VHDL实现 1、程序实现过程: entity hanshu is port(clk, reset: in std_logic; q: out std_logic_vector(7 downto 0)); end hanshu; architecture a of hanshu is

起重机械作业人员考核试题+答案 姓名:身份证号: 单位:成绩: 申请作业项目: 一、填空题(每小题2分,共20分) 二、判断题(每小题1分,共10分) 1、吊钩开口度比原尺寸增加15%时,吊钩应报废。(√) 2、新更换的钢丝绳应与原安装的钢丝绳同类型、同规格。(√) 3、起重机轨道接头的缝隙一般为5-10mm。(×) 4、葫芦式起重机在正常作业中可使缓冲器与止挡器冲撞,以达停车目的的。(×) 5、《特种设备作业人员证》每2年年复审一次。持证人员应当在复审期满3月前,向发证部门提出复审申请。(×) 6、流动式轮胎起重机可以吊载运行,汽车起重机不允许吊载运行。(√) 7、减速器正常工作时,箱体内必须装满润滑油。(×) 8 、当重物位置大于回转半径时,起重机可以缓慢起升,待重物水平拉近钢丝绳

垂直后,在起吊。(×) 9、起升机构可以使用编结接长的钢丝绳。(×) 10、桥式起重机司机室应设在导电滑线的一侧。(×) 三、选择题(每题1分,共10分) 1 A、2 B、1 C、半 3 2 A、打开 3、并尽量选用起重性能与技术参数接近的起重机。 A、2机、4机D、5机 4 A、打开 B、制动 5。 A、1050 B、800 C、1000 D、1200 6、《国务院关于修改<的决定》已经2009年1月14日国 务院第46 A、2002年6月1日 B、2003年6月1日 C、2004年2月1日 D、2009年5月1日 7 A、不准离开 B、可以离开 8、起重机械投入使用前或投入使用后30 A、市级质监部门登记 B、检验机构登记 C、县级质监部门登记C、省级质监部门登记 9、在冬季应延长空运转时间、 A、0°C B、15°C C、30°C 35°C 10 A、同 B、反 C、旁 四、名词解释(每题5分,共20分) 1、《条例》中起重机械的定义; 答:起重机械是指用于垂直升降或者垂直水平移动重物的机电设备,其范围规定