SystemVerilog断言及其应用

神州龙芯集成电路设计公司

陈先勇 徐伟俊 杨鑫 夏宇闻

[摘要]:在介绍SystemVerilog断言的概念、使用断言的好处、断言的分类、断言的组成以及断言如何被插入到被测设计(DUT)的基础上,本文详细地介绍了如何使用不同的断言语句对信号之间的复杂时序关系进行严格的检查,并针对每个例子展示了在ModelSim 6.1b仿真环境中所显示的波形。本文旨在帮助读者理解如何使用断言对设计中信号间复杂时序关系进行验证的方法,并由此介绍一些基本的SystemVerilog断言、操作符、代码段和断言验证方法学。

关键字:SystemVerilog,断言, DUT, SVA,Assertion

1.前言

当今,数字电路的规模和复杂度在不断增长,这使得对设计进行彻底的验证将成为一项巨大的挑战。在整个芯片设计过程中,验证工作所需的时间将占去设计周期的70%~80%,验证工程师的人数将是设计工程师的两倍。这就迫切需要提高验证工作的效率,以解决验证瓶颈问题。

传统上,对被测设计(DUT)的验证都是通过在DUT的输入端口加上具有特定时序激励,然后观察DUT的内部状态变化和最后的输出信号,以确定DUT工作是否正确。这种方法对简单的小规模的设计很有用。但当设计规模变大时,要想使用这种方法来验证DUT是不现实的。因为对于规模大的设计,要想遍历设计将遇到的各种情况,验证其正确性,需要成千上万的特定时序激励。并且如果设计稍有一点变动,这些时序激励就得重新编写。设计的复杂性迫使验证工程师使用随机测试平台来生成更多的验证激励。高级验证语言,如OVA,PSL等,便在创建复杂测试平台时得到了广泛的应用。但这些验证语言和RTL级的编码语言不一致,使得验证很容易出现错误,造成调试工作的不方便。

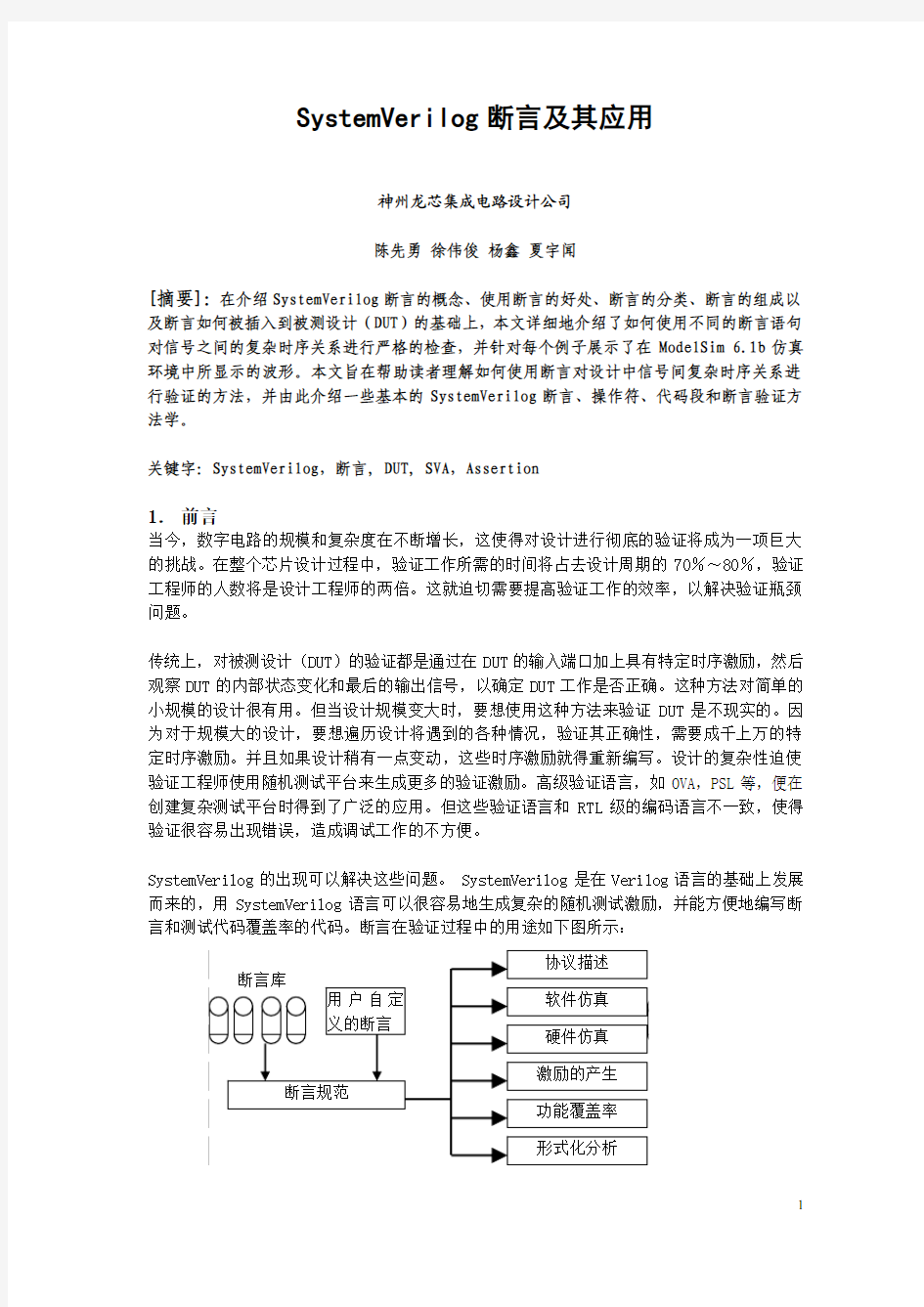

SystemVerilog的出现可以解决这些问题。 SystemVerilog是在Verilog语言的基础上发展而来的,用SystemVerilog语言可以很容易地生成复杂的随机测试激励,并能方便地编写断言和测试代码覆盖率的代码。断言在验证过程中的用途如下图所示:

图1 验证过程中的断言

由此可见,用SystemVerilog描述的断言可以应用于设计过程的各个阶段,它不仅能快而准确地定位设计中的错误,还能统计功能覆盖率。用SystemVerilog描述的断言能显著提高验证准确性和验证效率,加快设计进程,提高我们对设计的信心。

2.SVA概述

SystemVerilog语言是Verilog语言的增强,它增强了Verilog原有的编程能力,又引入了新的数据类型和验证方法。SystemVerilog断言(以下简称SVA)就属于这些新的验证方法中的一种。

那么什么是断言呢?断言就是对设计属性(行为)的描述,它是用描述性语言来描述设计的属性。在仿真过程中,如果一个被描述的属性不是我们期望的那样,那么断言就会失败;或者在仿真过程中,如果出现了一个不应该出现的属性,那么断言也会失败。

那么为什么要使用断言呢?原有的Verilog语言是一种过程性语言,设计它的目的是用于硬件描述,不是用于仿真验证,因此它不能很好地控制时序。要描述复杂的时序关系,Verilog 语言需要编写冗长的代码,很容易出错,且不易维护。SVA是一种描述性语言,可以完美地描述和控制时序相关的问题,而且语言本身简洁易读,容易维护。SVA还提供了许多内嵌的函数用于测试特定的时序关系和自动收集功能覆盖率数据。并且当断言失败时,仿真系统会根据失败断言的严重程度来决定是打印一条错误提示信息还是退出仿真过程,便于定位出错的位置。

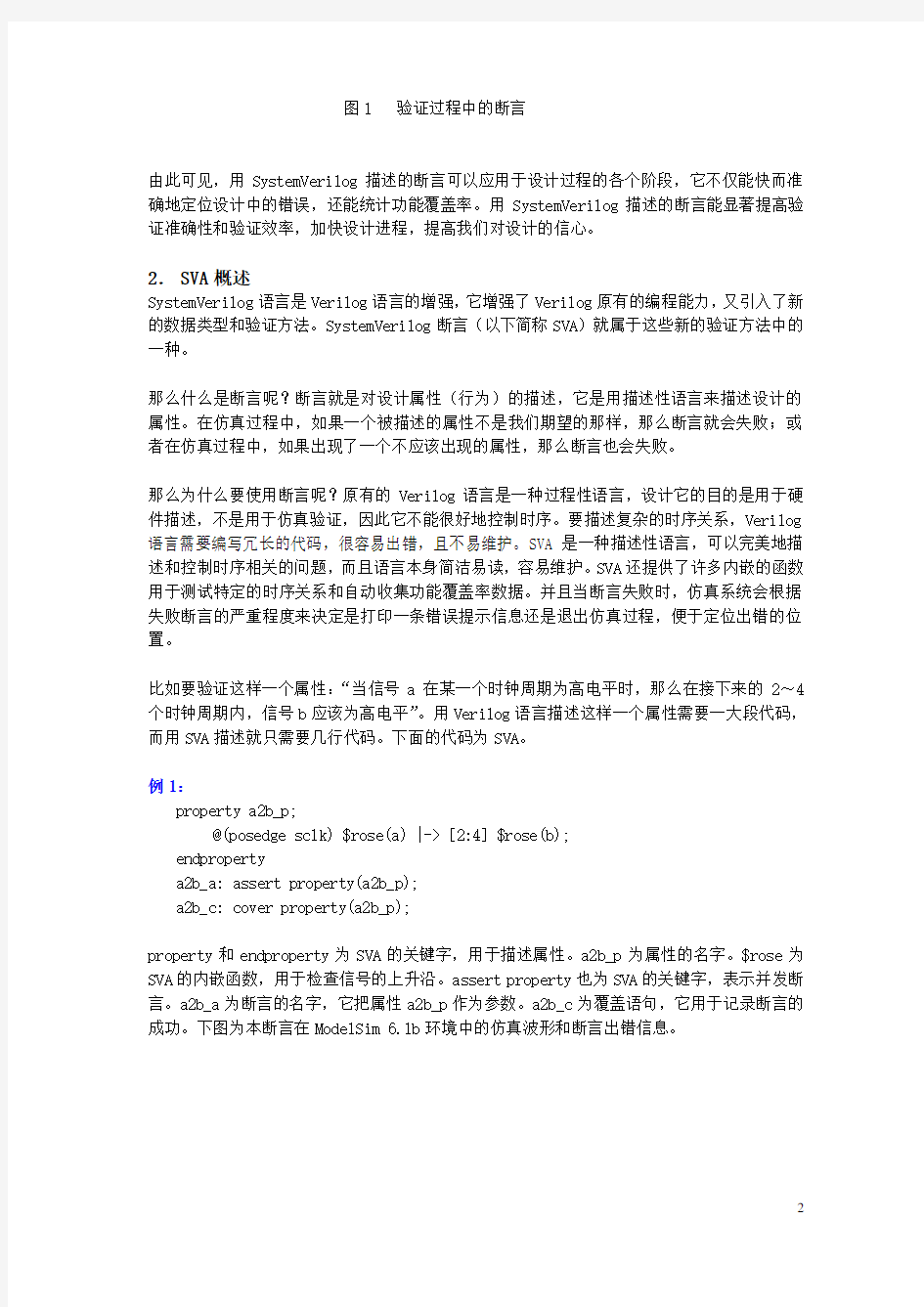

比如要验证这样一个属性:“当信号a在某一个时钟周期为高电平时,那么在接下来的2~4个时钟周期内,信号b应该为高电平”。用Verilog语言描述这样一个属性需要一大段代码,而用SVA描述就只需要几行代码。下面的代码为SVA。

例1:

property a2b_p;

@(posedge sclk) $rose(a) |-> [2:4] $rose(b);

endproperty

a2b_a: assert property(a2b_p);

a2b_c: cover property(a2b_p);

property和endproperty为SVA的关键字,用于描述属性。a2b_p为属性的名字。$rose为SVA的内嵌函数,用于检查信号的上升沿。assert property也为SVA的关键字,表示并发断言。a2b_a为断言的名字,它把属性a2b_p作为参数。a2b_c为覆盖语句,它用于记录断言的成功。下图为本断言在ModelSim 6.1b环境中的仿真波形和断言出错信息。

图1 断言例1的波形和断言错误提示信息

断言信号为高阻态表示断言没有被激活,断言信号为1表示断言被激活,正在检查时序属性。倒三角表示断言在此刻失败,正三角表示断言在此刻成功。从上图可以看出,断言a2b_a一共进行了3次时序检查,第1、3次失败,第2次成功。

第1次断言失败。在sclk(2)处,信号a被拉高,但这时采到的a的值仍为0。在sclk(3)处,信号a被拉低,但这时采到的a的值为1,而前一个时钟采到a的值为0,表示a的上升沿到来,即$rose(a)成立,整个断言被激活,然后进行后序时序检查。在接下来的2~4个时钟周期,并没有采样到信号b的上升沿,则在sclk(7)处断言被标记为失败,断言退出激活状态。

第2次断言成功。在sclk(9)处,采样到信号a的上升沿,断言被激活。在随后的第3个时钟周期又采样到信号b的上升沿,断言成功,随即断言退出激活状态。

第3次断言失败,其断言检测过程和第1、2次类似,请读者自己分析。

由此我们可以看出SVA在时序检查时的巨大优势:只需几句代码就可以检查一类时序问题。而且在检查时,仿真验证系统不仅会打印出错信息,还会在波形中进行标记。这对于我们检查信号间的时序关系非常方便。

3.SVA分类及组成

3.1 断言分类

SVA分为并发断言和即时断言。

并发断言的计算基于时钟周期,在时钟边沿根据变量的采样值计算表达式。它可以放在过程块(procedural block)、模块(module)、接口(interface)或一个程序块(program)的定义中。并发断言可以在静态(形式化)验证工具和动态(仿真)验证工具中使用。上面的例子就是并发断言。

即时断言基于事件的变化,表达式的计算就像Verilog中的组合逻辑赋值一样,是立即被求值的,而不是时序相关的。它必须放在过程块的定义中,只能用于动态仿真。一个即时断言的例子如下:

例2:

always_comb

immi_a: assert (a && b);

即时断言被当作过程块的一部分。当信号a或者信号b发生变化时,always_comb块被执行。区别即时断言和并发断言的关键词是“property”。我们在进行时序检查时,通常使用并发断言,而很少使用即时断言。

3.2 断言的组成和建立过程

任何复杂的时序模型,其功能总是由多个逻辑事件的组合来表示的。这些事件可以是简单的同一时钟沿被求值的布尔表达式,也可以是经过几个时钟周期求值计算得到的事件。SVA使用关键字sequence(序列)来表示这些事件。许多序列可以被有序地组合起来形成设计的属性,SVA用关键字property来表示属性。最后属性要在断言中被调用才能真正发挥作用。同时我们还应该用覆盖语句来记录断言成功的次数。由此可以看出断言的建立过程为“编写布尔表达式 —> 编写序列(sequence)-> 编写属性(property)—> 编写断言(assert property)和覆盖语句(cover property)”。它们的语法格式为:

序列 属性 断言和覆盖

sequence name_s;

endproperty

name_a:assert property

(property name);

name_c:cover property

(property name);

表1 序列、属性、断言语法格式

注意:上表中斜体字为名字。为了方便识别,序列以_s结尾,属性以_p结尾,断言以_a结尾,覆盖语句以_c结尾。

4.断言的具体应用举例

4.1 简单逻辑值检查

假设要检查“信号a在每个时钟上升沿都为高电平,如果信号在任何一个时钟上升沿不为高电平,断言将失败”。这可以通过下面的代码实现:

例3:

sequence s1_s;

@(posedge sclk) a;

endsequence

a1_a: assert property(s1_s);

c1_c: cover property(s1_s);

其检查波形和断言出错信息为:

在sclk(0)处,仿真刚开始,a还没有被赋值,为不定态x,所以在sclk(0)处,断言失败。在sclk(1)处,采样当a为0,断言失败。在其余时钟上升沿处,分析方法类似。最后断言在第0、1、2、7、12、13、14个时钟上升沿失败,在其余时钟上升沿成功。

我们除了可以使用仿真环境默认的断言错误提示信息外,还可以在断言中添加自己的提示信息,如例4所示:

例4:

sequence s1_s;

@(posedge sclk) a;

endsequence

a1_a: assert property(s1_s)

$display (“assertion success”,$time)

else

$display(“assertion faild”,$time);

其提示信息为:

上面例子中的a可以为单个信号,也可以为同一时钟周期的布尔表达式,如a&&b,a||b,还可以为跨越多个时钟周期的布尔表达式,如a ##2 b。下面的例子检查如果信号a在某个时钟周期为高电平,两个时钟周期后信号b也必须为高电平。

例5:

sequence s2_s;

@(posedge sclk) a ##2 b;

endsequence

a2_a: assert property(s2_s);

c2_c: cover property(s2_s);

其检查波形为:

4.2 信号边沿检查

SVA提供了3个内嵌函数,用于检查信号的边沿变化。

?$rose(布尔表达式或信号名)

当信号/表达式的最低位由0或x变为1时返回真值。

?$fell(布尔表达式或信号名)

当信号/表达式的最低位由1变为0或x时返回真值。

?$stable(布尔表达式或信号名)

当信号/表达式的最低位不发生变化时返回真值。

例6:

sequence rose_s;

@(posedge sclk) $rose(a);

endsequence

sequence fell_s;

@(posedge sclk) $fell(a);

endsequence

sequence stable_s;

@(posedge sclk) $stable(a);

endsequence

rose_a: assert property(rose_s);

fell_a: assert property(fell_s);

stable_a: assert property(stable_s);

其检查波形为:

rose_a用于检测信号a的上升沿,它只在“a在当前时钟周期为高电平,在前一个时钟周期为低电平或不定态x”的情况下才成功,如第3、8、11个时钟周期,在其它情况下失败。

fell_a用于检测信号a的下降沿,它只在“a在当前时钟周期为低电平,在前一个时钟周期为高电平或不定态x”的情况下才成功,如第3、8、11个时钟周期,在其它情况下失败。在sclk(0)处,采样到a为不定态x。在sclk(1)处,采样到a为0。a从x变到0,本仿真环境认为是a的下降沿,所有断言成功。

stable_a用于检查信号a不变的情况,它只在“a在当前时钟周期为一个电平,在前一个时钟周期也为同样的电平”的情况下成功。如第0、2、4、5、6、8、10、11、13个时钟周期。在sclk(0)处,采样到a为不定态x,仿真系统认为在0时刻之前a同样为不定态x,所有在sclk(0)处断言成功。

4.3 使用蕴含操作符进行检查

在例5中,属性在每个时钟上升沿都会被检查。如果信号a在某个时钟上升沿不为高电平,断言就会失败,仿真系统随即产生一条错误提示信号。显然,这不是一个有效的错误信息,因为我们关心的是信号a和信号b之间的时序关系,而不只是关系信号a的电平值。这个错误只表示我们在这个时钟周期没有检测到断言的有效起始点。虽然这些断言是良性的,但它会在一段时间内产生大量的错误信息。为了避免这种错误的产生,SVA提供了“蕴含”操作符(implication,|->)。其形式为:a |-> b。

蕴含操作符的左边项为“先行算子”(antecedent),右边项为“后序算子”(consequent)。先行算子是约束条件,当先行算子匹配(成功)时,后序算子才能被计算。如果先行算子不成功,那么整个属性就被默认成功,叫“空成功”(vacuous success)。蕴含结构只能被用在属性定义中,不能用在序列定义中。蕴含操作符分为两类:交叠蕴含操作符(overlapped implication,|->)和非交叠蕴含操作符(non_overlapped implication,|=>)。

非交叠蕴含操作符“|->”表示如果先行算子匹配,后序算子在同一个时钟周期开始计算。

交叠蕴含操作符“|=>”表示:如果先行算子匹配,后序算子在下一个时钟周期开始计算。 下面例子中,non_overloap_impli_a为含有非交叠蕴含操作符的断言,overlap_impli_a为含有交叠蕴含操作符的断言。

例7:

property overloap_impli_p;

@(posedge sclk) a |-> b;

endproperty

property non_overloap_impli_p;

@(posedge sclk) a |=> b;

Endproperty

overlap_impli_a: assert property(overloap_impli_p);

overlap_impli_c: cover property(overloap_impli_p);

non_overloap_impli_a: assert property(non_overloap_impli_p);

non_overloap_impli_c: cover property(non_overloap_impli_p);

其检查波形为:

overloap_impli_a用于检测“信号a在某个时钟周期为高电平,并且信号b在同一个时钟周期也为高电平”的情况。整个断言只有在检测到信号a为高电平时才能被激活。由图可以看出,在所有被激活的断言中,一共有8次成功,5次失败。

non_overlap_impli_a用于检测“信号a在某个时钟周期为高电平,并且信号b在下一个时钟周期也为高电平”的情况。整个断言只有在检测到信号a为高电平时才能被激活。由图可以看出,在所有被激活的断言中,一共有6次成功,6次失败。

4.3 使用序列的重复操作符进行检查

序列的重复操作符分为3类:连续重复,跳转重复和非连续重复。

“[*m]”为连续重复操作符。“a[*3]”表示a被连续重复3次,“a[*1:3]”表示a被连续重复1~3次。连续重复的相邻两次重复之间只有一个时钟间隔。

“[->m]”为跳转重复操作符。“a[->3]”表示a被跳转重复3次,“a[->1:3]”表示a 被跳转重复1~3次。跳转重复的每一次重复之前可以有任意个时钟周期的间隔。

“[=m]”为非连续重复操作符。“a[=3]”表示a被非连续重复3次,“a[=1:3]”表示a 被非连续重复1~3次。非连续重复的每一次重复之前可以有任意个时钟周期的间隔,最后一次重复之后可以有任意个时钟周期的间隔。

例8:

property cons_rep_p;

@(posedge sclk) $rose(a) |-> ##1 b[*3] ##1 c;

endproperty

property goto_rep_p;

@(posedge sclk) $rose(a) |-> ##1 b[->3] ##1 c;

endproperty

property non_cons_rep_p;

@(posedge sclk) $rose(a) |-> ##1 b[=3] ##1 c;

endproperty

cons_rep_a: assert property(cons_rep_p);

cons_rep_c: cover property(cons_rep_p);

goto_rep_a: assert property(goto_rep_p);

goto_rep_c: cover property(goto_rep_p);

non_cons_rep_a: assert property(non_cons_rep_p);

non_cons_rep_c: cover property(non_cons_rep_p);

上图中,在sclk(3)处a为高电平,3个断言都被激活。1个时钟周期后,b出现3次连续的重复,再过1个时钟周期后,c为高电平,这样3个断言都成功。

在sclk(10)处a为高电平,3个断言都被激活。1个时钟周期后,b为低电平,断言cons_rep_a 就失败。再过1个时钟周期,b出现3次不连续的重复,再过1个时钟周期,c为高电平,这样断言goto_rep_a和non_cons_rep_a成功。

在sclk(20)处a为高电平,3个断言都被激活。1个时钟周期后,b为低电平,断言cons_rep_a 就失败。再过1个时钟周期,b出现3次不连续的重复,再过1个时钟周期,c为低电平,断言goto_rep_a也失败。最后再过1个时钟周期,c为高电平,断言non_cons_rep_a成功。

5.结论

SVA作为SystemVerilog语言最重要的内容之一,它可以在以下地方监视信号间的各种时序关系:(1)设计模块的内部;(2)模块与模块间的连接信号;(3)和RTL代码放在一起进行综合,用于调试;(3)进行设计的功能覆盖。而且SVA和可综合的RTL级语言都被统一到了systemVerilog语言,使得设计工程师和验证工程师可以很好地沟通,方便管理,加快设计进程。

上面列举地SVA实例只是SVA内部的一小部分,读者要想更深入地研究SVA和SystemVerilog 语言,可以查阅“参考资料”中列出的文献。

SystemVerilog语言及其断言必然会在复杂逻辑电路的验证工作中,逐步取代Verilog和SystemC,成为新一代的硬件设计和验证语言。

参考文献:

【1】《SystemVerilog验证方法学》,夏宇闻,杨雷,陈先勇,徐伟俊,杨鑫 译,北京航空航天大学出版社,ISBN:978-7-81124-079-5。

【2】《Verilog数字系统设计教程》,夏宇闻 编著,北军航空航天大学,ISBN:7-81077-302-X。【3】《SystemVerilog应用手册》,陈俊杰等译,清华大学出版社,ISBN:7-302-13441-3/TP.8442。

【4】SystemVerilog语法手册,《IEEE Standard for SystemVerilog-Unified Hardware Design,Specification,and Verification Language》。

【5】《SYSTEMVERILOG FOR VERIFICATION》,CHRIS SPEAR,Synopsys,Inc.

你怎样看世界,你也就得到怎样的世界 下面是多年前某些专家对其领域的断言,当时听起来很有道理。随着时间的流逝,它们变得愚蠢透顶。 从古至今十大愚蠢断言: 10.“没有理由让某个人在家中配备一台计算机。”(1979年)——肯尼斯·奥尔森(Kenneth Olsen),DEC(数字设备公司)的奠基人和总裁。 9.“飞机是个有趣的玩具,但没有军事价值。”(1911年)——费迪南·福煦(Ferdinand Foch),法国陆军元帅,军事战略家,第一次世界大战指挥官。 8.“无论将来科学如何发达,人类不可能登陆月球。”(1967年2月25日)——李·弗雷斯特博士(Dr.Lee Forest),三极管发明人和无线电之父。 7.“(电视)上市6个月之后,不可能还有市场。每天盯着个三合板盒子,人们很快就会厌烦。”(1946年)——达里尔·扎努克(Darryl F. Zanuck),二十世纪福斯公司总裁。 6.“我们不喜欢他们的声音。再说,吉他乐队也正在退出舞台。”(1962年)——英国德卡唱片公司(Decca Records)拒绝了披头士乐队。 5.“对于大部分人来说,吸烟是有益的。”(1969年11月18日)——《新闻周刊》援引洛杉矶外科医生G·麦克唐纳博士(Dr.Ian G.MacDonald)的话。 4.“这个‘电话’缺点太多,无法作为通讯工具。这种玩意儿对我们没什么用。”(1876年)——西方联合公司(Western Union)的《内部备忘录》。 3.“地球是宇宙的中心。”(第二世纪)——托勒密(Ptolemy),古埃及天文学家。

2.“今天没发生什么重要的事。”(1776年7月4日,美国独立日)——英皇乔治三世。 1.“所有能够发明的,都已经被发明了。”(1899年)——查尔斯·杜埃尔(Charles H. Duell),美国专利局局长。 看过这些,再看一些和你一样的青少年所说的话。这些话你听见过,它们和上面那些断言同样可笑: ●“我家没人上过大学。想上大学没门!” ●“没有用的。我就是没法和我后爹相处,我们不是一路人。” ●“做个聪明乖巧的人是件很乏味的事。” ●“我老师总是挑我的错。”

SystemVerilog 语言简介 SystemVerilog 是一种硬件描述和验证语言(HDVL),它基于 IEEE 1364-2001 Verilog 硬件描述语言 (HDL) 并对其进行了扩展, , 包括扩充了 C 语言数据类型、结构、压缩和非压缩数组、 接口、断 言等等, 这些都使得 SystemVerilog 在一个更高的抽象层次上提高了 设计建模的能力。SystemVerilog 由 Accellera 开发,它主要定位在 芯片的实现和验证流程上, 并为系统级的设计流程提供了强大的连接 能力。 下面我们从几个方面对 SystemVerilog 所作的增强进行简要的 介绍, 期望能够通过这个介绍使大家对 SystemVerilog 有一个概括性 的了解。 1. 接口(Interface) Verilog 模块之间的连接是通过模块端口进行的。为了给组成设 计的各个模块定义端口, 我们必须对期望的硬件设计有一个详细的认 识。不幸的是,在设计的早期,我们很难把握设计的细节。而且,一 旦模块的端口定义完成后,我们也很难改变端口的配置。另外,一个 设计中的许多模块往往具有相同的端口定义,在 Verilog 中,我们必 须在每个模块中进行相同的定义,这为我们增加了无谓的工作量。 SystemVerilog 提供了一个新的、高层抽象的模块连接,这个连 接被称为接口(Interface)。接口在关键字 interface 和 endinterface 之间定义,它独立于模块。接口在模块中就像一个单一的端口一样使 用。在最简单的形式下,一个接口可以认为是一组线网。例如,可以 将 PCI 总线的所有信号绑定在一起组成一个接口。通过使用接口, 我们在进行一个设计的时候可以不需要首先建立各个模块间的互连。 随着设计的深入,各个设计细节也会变得越来越清晰,而接口内的信 号也会很容易地表示出来。当接口发生变化时,这些变化也会在使用 该接口的所有模块中反映出来,而无需更改每一个模块。 下面是一个 接口的使用实例: interface chip_bus; // 定义接口 wire read_request, read_grant; wire [7:0] address, data; endinterface: chip_bus

更多免费资料下载请进: https://www.doczj.com/doc/8d3646375.html, 中国最大的免费课件资料库

我们为什么去做愚蠢而不合理的事情:十大杰出社会心理学研究(五)——Stanley Milgram:服从权威还是墨守陈规? 2005个读者 译者: paradox 02/24/2008 原文引用双语对照及眉批 简介 究竟是人类的残酷还是只是墨守陈规?Stanley Milgram的实验给了我们什么启发? 有什么心理学实验可以如此有影响力,以至于只要参加了这个实验就可以改变你对于自己和人性的看法?什么实验过程可以促发人们大量地出汗和颤抖,使得10%的人极度难过,同时让其他人陷入歇斯底里的狂笑?什么发现可以如此强大有力,以至于它招致了很多心理学家的疯狂反驳?欢迎来到十大心理学研究的第六个提名,正如你所料,这是一个非常重要的研究。可是先不要争论,因为这个研究引来了大量的批评,有些人说它的断言过于浮夸。 解释人类的残酷 Stanley Milgram的著名实验是为了测试对于权威的服从而设计的(Milgram, 1963)。Milgram想知道,当被一个权威人物命令去伤害他人的时候,一个人究竟会残酷到什么地步。很多人在二战的恐怖之后想要知道(不是第一次想知道),人们如何会被激发,去对同类犯下如此残酷的罪行。不仅是那些武装部队,就连普通人都被强迫去实施最为残酷可怕的暴行。 但是Milgram没有去调查战争中的极端情况,他希望看看在实验室相对“正常”的环境下人们会有什么反应。当被要求给另一个人实施电击的时候人们会有什么表现?人们会无视自己的忧虑而遵从命令到什么样的程度?

被 试所处的实验情境最初比较简单。被试被告知他们参与了一个学习实验,他们执行电击,并且需要持续到实验的最后。他们是“老师”,而另外一个人是“学习 者”。他们坐在一个机器前,上面有标着逐渐增大的电压值的刻度盘。这就是“电击器”。上排的第三个电闸贴着“危险:强电击”的标签,之前两个电闸只是标着 “XXX”。 在实验过程中,每当“学习者”犯下一个错误的时候,被试就被命令执行不断增强的电击。当然学习者不断地犯错,于是老师(可怜的被试)必须持续给与学习者越来越强的电击,并且听到惨叫,直至最终学习者安静下来。 被 试实际上并没有释放电击,实验中的学习者只是一个按照预演演戏的演员。学习者看不到被试,所以他们只能根据自己的假设来装出被试给自己造成的痛苦程度。然 而,他们几乎可以肯定,到了实验最后,电击会变得极度痛苦,而学习者很可能会不省人事。当被试推诿,不愿实施电击的时候,以身着白色实验服的权威形象出现 的实验者会命令他们继续。 结果 在我阐明实验结果前,试图去想象一下你自己是实验的被试。为了一个记忆性的学习,你究竟会给另一个人实施多强的电击(至少你认为那是电击)?当你执行了标有“危险:强电击”的电击,使得学习者安静下来之后,你会怎么想?说实话,你会残酷到什么程度? 无论你认为自己会残酷到什么程度,你很可能都低估了自己,因为大多数人都低估了自己的残酷。就如同这个实验本身一样,实验结果如同触电一般有冲击力。Milgram的研究发现人们比你想象中更加愿意服从。63%的被试一直持续到实验的最后——即使在学习者痛苦地尖叫,对他求饶,直到最终不省人事的情况下,被试还是执行了所有强度的电击。这些可不是特别挑选出来的虐待狂,他们都是像你我一样的普通人,志愿参加这次研究。 这些结果应该如何解释? 在当时Milgram的研究成为了大新闻。Milgram用了情境的力量来解释实验结果。这个社会心理学实验完美地用事实说明了社会情境可以给人类行为带来的影响程度。

SystemVerilog Tutorials 下面的手册会帮助你了解一些SystemVerilog中最重要的新特点。手册还提供了一些代码样本和例子使你可以对语言有更好"感觉"。这些辅导假设你们已经了解了一些Verilog语言。如果没有,你可以先去看看Verilog设计者指南(V erilog Designer’s Guide)。 * Data types * RTL design * Interfaces * Clocking * Assertion-based verification * Classes * Testbench automation and constraints * The Direct Programming Interface (DPI) SystemVerilog 的数据类型 这个手册将描述Systemverilog新引进的数据类型。他们大多数都是可以综合的,并且可以使RTL级描述更易于理解和书写。 整型和实型 SystemVerilog引进了几种新的数据类型。C语言程序员会熟悉其中的大多数。引进新的数据类型构思是这样的,如果C语言和SystemVerilog有相同的数据类型可以使C语言算法模型更容易的转化为SystemVerilog模型。 Verilog的变量类型有四态:既是0,1,X,Z。SystemVerilog引进了新的两态数据类型,每一位只可以是0或是1。当你不需要使用的X和Z值时,譬如在写Testbench和做为for语句的循环变量。使用两态变量的RTL级模型,可以使模拟器更有效率。并且使用得当的话将不会对综合结果产生影响。 二态整型 类型描述例子 Bit user-defined size bit [3:0] a_nibble; Byte 8 bits, unsigned byte a, b; Shortint 16 bits, signed shortint c, d; Int 32 bits, signed int i,j; Longint 64 bits, signed longint lword;

SystemVerilog语言简介(doc 26页)

SystemVerilog语言简介 SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE 1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包括扩充了C语言数据类型、结构、压缩和非压缩数组、接口、断言等等,这些都使得SystemVerilog在一个更高的抽象层次上提高了设计建模的能力。SystemVerilog由Accellera 开发,它主要定位在芯片的实现和验证流程上,并为系统级的设计流程提供了强大的连接能力。下面我们从几个方面对SystemV erilog所作的增强进行简要的介绍,期望能够通过这个介绍使大家对SystemVerilog有一个概括性的了解。 1. 接口(Interface) Verilog模块之间的连接是通过模块端口进行的。为了给组成设计的各个模块定义端口,我们必须对期望的硬件设计有一个详细的认识。不幸的是,在设计的早期,我们很难把握设计的细节。而且,一旦模块的端口定义完成后,我们也很难改变端口的配置。另外,一个设计中的许多模块往往具有相同的端口定义,在Verilog中,我们必须在每个模块中进行相同的定义,这为我们增加了无谓的工作量。 SystemVerilog提供了一个新的、高层抽象的模块连接,这个连接被称为接口(Interface)。接口在关键字interface和e ndinterface之间定义,它独立于模块。接口在模块中就像一个

单一的端口一样使用。在最简单的形式下,一个接口可以认为是一组线网。例如,可以将PCI总线的所有信号绑定在一起组成一个接口。通过使用接口,我们在进行一个设计的时候可以不需要首先建立各个模块间的互连。随着设计的深入,各个设计细节也会变得越来越清晰,而接口内的信号也会很容易地表示出来。当接口发生变化时,这些变化也会在使用该接口的所有模块中反映出来,而无需更改每一个模块。下面是一个接口的使用实例:

PS:笔者强烈建议诸位注册一个EETOP的账号,每天签到或者发贴、回贴就有积分了,里面的资源非常丰富,各种软件、资料都能找到。 一、入门首先要掌握HDL(HDL=verilog+VHDL)。 第一句话是:还没学数电的先学数电。然后你可以选择verilog或者VHDL,有C语言基础的,建议选择VHDL。因为verilog太像C了,很容易混淆,最后你会发现,你花了大量时间去区分这两种语言,而不是在学习如何使用它。当然,你思维能转得过来,也可以选verilog,毕竟在国内verilog用得比较多。 接下来,首先找本实例抄代码。抄代码的意义在于熟悉语法规则和编译器(这里的编译器是硅编译器又叫综合器,常用的编译器有:Quartus、ISE、Vivado、Design Compiler、Synopsys的VCS、iverilog、Lattice的Diamond、Microsemi/Actel的Libero、Synplify pro),然后再模仿着写,最后不看书也能写出来。编译完代码,就打开RTL图,看一下综合出来是什么样的电路。 HDL是硬件描述语言,突出硬件这一特点,所以要用数电的思维去思考HDL,而不是用C语言或者其它高级语言,如果不能理解这句话的,可以看《什么是硬件以及什么是软件》。在这一阶段,推荐的教材是《Verilog传奇》、《Verilog HDL高级数字设计》或者是《用于逻辑综合的VHDL》。不看书也能写出个三段式状态机就可以进入下一阶段了。 此外,你手上必须准备Verilog或者VHDL的官方文档,《verilog_IEEE官方标准手册-2005_IEEE_P1364》、《IEEE Standard VHDL Language_2008》,以便遇到一些语法问题的时候能查一下。 二、独立完成中小规模的数字电路设计。 现在,你可以设计一些数字电路了,像交通灯、电子琴、DDS等等,推荐的教材是《Verilog HDL应用程序设计实例精讲》。在这一阶段,你要做到的是:给你一个指标要求或者时序图,你能用HDL设计电路去实现它。这里你需要一块开发板,可以选Altera的cyclone IV系列,或者Xilinx的Spantan 6。还没掌握HDL之前千万不要买开发板,因为你买回来也没用。这里你没必要每次编译通过就下载代码,咱们用modelsim仿真(此外还有QuestaSim、NC verilog、Diamond的Active-HDL、VCS、Debussy/Verdi等仿真工具),如果仿真都不能通过那就不用下载了,肯定不行的。在这里先掌握简单的testbench就可以了。推荐的教材是《WRITING TESTBENCHES Functional Verification of HDL Models》。 三、掌握设计方法和设计原则。 你可能发现你综合出来的电路尽管没错,但有很多警告。这个时候,你得学会同步设计原则、优化电路,是速度优先还是面积优先,时钟树应该怎样设计,怎样同步两个异频时钟 《Altera FPGA/CPLD 等等。推荐的教材是《FPGA权威指南》、《IP核芯志-数字逻辑设计思想》、 设计》第二版的基础篇和高级篇两本。学会加快编译速度(增量式编译、LogicLock),静态时序分析(timequest),嵌入式逻辑分析仪(signaltap)就算是通关了。如果有不懂的地方可以暂时跳过,因为这部分还需要足量的实践,才能有较深刻的理解。 四、学会提高开发效率。 因为Quartus和ISE的编辑器功能太弱,影响了开发效率。所以建议使用Sublime text 编辑器中代码片段的功能,以减少重复性劳动。Modelsim也是常用的仿真工具,学会TCL/TK 以编写适合自己的DO文件,使得仿真变得自动化,推荐的教材是《TCL/TK入门经典》。你可能会手动备份代码,但是专业人士都是用版本控制器的,所以,为了提高工作效率,必须掌握GIT。文件比较器Beyond Compare也是个比较常用的工具。此外,你也可以使用System Verilog来替代testbench,这样效率会更高一些。如果你是做IC验证的,就必须掌

转一篇Systemverilog的一个牛人总结 (2012-12-12 16:47:06) 转载▼ 标签: 分类:Dreamywork systemverilog 验证 面向对象 杂谈 Systemverilog 数据类型 l 合并数组和非合并数组 1)合并数组: 存储方式是连续的,中间没有闲置空间。 例如,32bit的寄存器,可以看成是4个8bit的数据,或者也可以看成是1个32bit的数据。 表示方法: 数组大小和位,必须在变量名前指定,数组大小必须是【msb:lsb】 Bit[3:0] [7:0] bytes ; 2)二维数组和合并数组识别: 合并数组: bit [3:0] [7:0] arrys; 大小在变量名前面放得,且降序 二维数组: int arrays[0:7] [0:3] ; 大小在变量名后面放得,可降序可升序 位宽在变量名前面,用于识别合并和非合并数组,位宽在后面,用于识别数组中元素个数。 3)非合并数组 一般仿真器存放数组元素时使用32bit的字边界,byte、shortint、int都放在一个字中。 非合并数组:字的地位存放变量,高位不用。 表示方法: Bit [7:0] bytes; 4)合并数组和非合并数组的选择 (1)当需要以字节或字为单位对存储单元操作。 (2)当需要等待数组中变化的,则必须使用合并数组。例如测试平台需要通过存储器数据的变化来唤醒,需要用到@,@只能用于标量或者合并数组。

Bit[3:0] [7:0] barray[3] ; 表示合并数组,合并数组中有3个元素,每个元素时8bit,4个元素可以组成合并数组 可以使用barry[0]作敏感信号。 l 动态数组 随机事物不确定大小。 使用方法:数组在开始是空的,同时使用new[]来分配空间,在new[n]指定元素的个数。 Int dyn[]; Dyn = new[5]; //分配5个元素空间 Dyn.delete() ; //释放空间 l 队列 在队列中增加或删除元素比较方便。 l 关联数组 当你需要建立一个超大容量的数组。关联数组,存放稀疏矩阵中的值。 表示方法: 采用在方括号中放置数据类型的形式声明: Bit[63:0] assoc[bit[63:0]]; l 常量: 1)Verilog 推荐使用文本宏。 好处:全局作用范围,且可以用于位段或类型定义 缺点:当需要局部常量时,可能引起冲突。 2)Parameter 作用范围仅限于单个module 3)Systemverilog: 参数可以在多个模块里共同使用,可以用typedef 代替单调乏味的宏。 过程语句 l 可以在for循环中定义变量,作用范围仅在循环内部 for(int i=0;i<10;i++) array[i] =i; l 任务、函数及void函数 1)区别:

英汉语言十大差异 语言毕竟是文化的载体,语言与文化,甚至历史、地理、风俗、政治、经济等常常水乳交融,它们无孔不入地反作用于语言,使语言打上深深的文化烙印。英汉翻译者,若不知英汉各自的特点,不知两者的差异,是不能想象的。不要以为,汉语是我们的母语,从牙牙学语开始,便开始接触汉语,因此,就想象自己很了解汉语。其实,这是一种误解。汉语到底有什么特点? 就汉语论汉语,因为没有距离,就看不真切,因为没有比较,就看不明白!只有当汉语和英语比肩而立,碰撞交流,才会燃爆出绚丽的火花,两者之差异,才会赫然呈现。 目前,从事英汉对比研究的学者和专著在我国并不少,但是,当我们放眼这个领域,就觉得有必要正面回答一个问题:英汉对比研究的目的是什么? 弄明白英汉的差异,并不是我们研究的最终目标,至多只能是一种手段而已,而手段总得服务于一定的目的。英汉对比研究的一个重要的目的应该是:服务于翻译。 译界的实践证明:只有对英汉之差异了然于心,译者才能做到下笔如有神。下面结合英汉翻译的实际,对英汉之间的明显差异作鸟瞰式分析和归纳。 1.英语重形合(Hypotaxis),汉语重意合(Parataxis) 汉语重意合,结构松弛,多以意思连接的积累式分句(Accumulative Clause)或独立的单句(independent Sentence),其彼此的逻辑关系多以句序之先后加以暗示。 有的语言学家以“竹节句法”写英句,所谓“竹节”,则指其断不可缺的种种连接词(Connectives);有以“流水句法”写汉句,所谓“流水”,指少用乃至不用连接词的行文流畅。 美国的翻译学家Eugene A.Nida在其Translating Meanings (1983)一书中曾经深入浅出地说明了英汉这一差异: 就汉语和英语而言,也许在语言学上最重要的一个区别就是形合和意合的对比,在英语以及大多数的印欧语言中,句子的从属关系大多是用连接词如,although,because,when,in order that,so及so that等词明确地表达出来。但是,这同一概念,我们用意合的方法基本上也可以表达出来;那就尽说,将两个句子放在一起并无连接词表明其相互关系,而从句子本身的意思中体现出来。例如,我们说because it is late,I must leave.在这里两个句子的逻辑关系是用连接词because加以表达的。然而我们也可以说it is late,I must leave.在这里,虽然无明确的词汇表明彼此的关系,但是这种关系显然是存在的。 以上Nida所言,有一点需要加以纠正。他说:“我们也可以说It is 1ate,I must leave.” 此议不妥,因为这样缺乏连接词的英句是不合其表达习惯的,至少也是拙句(C1umsy Sentence)。比如: An Englishman who could not speak Chinese was once travelling in China. 译文:一个英国人,不会说中国话,有一次在中国旅行。 英语原句是一个典型的形合句,而相应的汉译则是意合句。假如,将英语原句改成意合句,那读上去还有英语味吗? There was an Englishman.He could not speak Chinese.He was once travelling in China.

本教程将介绍新引入Systemverilog的数据类型。他们大多数是可综合的,而且使得RTL级描述更易于被编写和理解。 整型和实型 SystemVerilog 引入了几种新的数据类型。C语言程序员会熟悉其中的大多数。引进新的数据类型构思是这样的,如果C语言和SystemVeri log有相同的数据类型的话可以使C语言算法模型更容易的转化为Syst emVerilog模型。 Verilog的变量类型是四态类型:即0,1,X(未知值)和Z(高阻值)。SystemVerilog新引入了两态的数据类型,每一位只可以是0或者1。当你不需要使用的X和Z值时,譬如在写Testbench和做为For 语句的循环变量时。使用两态变量的RTL级模型,可以使仿真器效率更高。而且使用得当的话将不会对综合结果产生任何的影响。 注意:和C语言不一样,SystemVerilog指定了一些固定宽度的数据类型。 logic是一种比reg型更好更完善的数据类型。我们将会看到,你可

以使用logic型来替代过去您有可能使用reg型或wire型的地方。 数组 在Verilog-1995中,你可以定义标量或是矢量类型的线网和变量。你也可以定义一维数组变量类型的存储器数组。在Verilog-2001中允许多维的线网和变量数组存在,并且取消了部分存储器数组用法的限制。 SystemVerilog进一步完善了数组的概念,并对数组重新进行了定义,从而允许对数组进行更多的操作。 在SystemVerilog中,数组可以有压缩尺寸或是非压缩尺寸的属性,也可以同时具有两种属性。考虑下面的例子: reg [3:0][7:0] register [0:9]; 压缩尺寸是[3:0]和[7:0],非压缩尺寸是[0:9] 。(只要你喜欢可以有任意大小的压缩尺寸和非压缩尺寸) 压缩尺寸: 1)保证将在存储器中产生连续的数据 2)可以复制到任何其他的压缩对象中 3)可切片("部分选取") 4)仅限于位类型(bit, logic, int等),其中有些(如int)有固定的 尺寸 相比之下,非压缩数组在内存中的排列方式由仿真器任意选定。我们可以可靠地复制非压缩数组到另一个具有相同数据类型的数组中。对于不同数据类型的数组,你必须使用强制类型转换(有几个非压缩数组转换到压缩数组的规则)。其中非压缩数组可以是任意的类型,如实数数组。

类的继承 SystemVerilog支持单继承(类似Java,而不像C++). 有一个让SystemVerilog支持多重继承的提案[1], 但是短期内不会看到曙光。 目录 ? 1 什么是继承? ? 2 有什么好处 ? 3 开-关定律 ? 4 参考资料 什么是继承? 继承是面向对象编程范式的关键概念。类用来创建用户自定义类型. 继承使得用户可以用非常安全,非侵入的方式对类的行为进行增加或者修改。 使用继承可以定义子类型,在子类型中增加新的方法和数据。被继承的类一般称为基类(SystemVerilog中的超类),得到的新类一般称为引申类(或子类)。 为什么继承如此重要? 因为它使得复用得以实现。让我们通过实例来说明. 假设我们对一个图像模块进行建模. 对其中一部分,我们写了一个代表颜色的类: class Color; byte unsigned red; byte unsigned green; byte unsigned blue; function new(byte unsigned red_=255, byte unsigned green_=255, byte unsigned blue_=255); red=red_; green=green_; blue=blue_; endfunction:new function mix(Color other); function brighter(float percent); task draw_pixel(int x,int y);

Now现在它的下一个版本希望能够处理部分透明的图像。为此,我们给Color类增加了一个alpha成员,。alpha代表图像的透明度。alpha越大,图像的像素越结实(不透明)。'0'代表完全透明,使得图片的背景全部可见。因此,我们修改color类如下: class Color; byte unsigned red; byte unsigned green; byte unsigned blue; byte unsigned alpha; function new(byte unsigned red_=255, byte unsigned green_=255, byte unsigned blue_=255, byte unsigned alpha_=255); red=red_; green=green_; blue=blue_; alpha=alpha_; endfunction:new function mix(Color other);// new implementation -- would depend on // alpha values for both the colors function brighter(float percent);// original implementation good enough task draw_pixel(int x,int y);// new implementation // Other functions ... endclass:Color 注意,即使许多代码是由之前版本的Color类复制而来,我们还是需要单独维护两个版本的代码。这时继承就可以发挥作用,使用继承,我们可以简单的从原始的Color类继承出新类,来添加alpha成员。 class ColorWithAlpha extends Color; byte unsigned alpha; function new(byte unsigned red_=255, byte unsigned green_=255, byte unsigned blue_=255, byte unsigned alpha_=255);

东方早报/2011年/12月/11日/第B08版 书评 愚蠢和盲目的自信 张汝伦 “光明之子”是“极为愚蠢和盲目的”,因为他们的理想主义和乐观主义使得他们竟然对人类趋利的根本性没有足够的认识,而一厢情愿地从理想的角度来看待世界和人类,包括他们自己。 义利问题是儒家的中心问题,象山教人,以义利之辨为先。朱子更是说:“义利之说乃儒者第一义。”此实乃见道之言,非理学家迂阔不经之谈。人类的种种危机与困境,归根结底,乃是由于“熙熙攘攘,皆为利往。”人各有利,人人争利,现代性的意识形态又通过世俗化和去魅过程将前此各大宗教苦心孤诣的义利之说一并破除,遂使人们觉得,利字当头,义也就在其中,现代真正是一个“人欲”大解放的时代;然而也是一个人类有可能自我毁灭的时代。人性之恶在任何一个时代都没有像在现代表现得那样极端和超乎想象。另一方面,现代文明,即产生于十六、十七世纪的资产阶级文明,“面临着极为严峻的危险”(《光明之子与黑暗之子》,第4页。以下引文除特别注明外,皆引自该书)。其所以如此,在于现代人已经不再把义利问题作为一个头等重要的问题来考虑了。最近出版的美国现代神学家莱茵霍尔德?尼布尔的著作《光明之子与黑暗之子》,便可为此佐证。 “光明之子”与“黑暗之子”典出《圣经》。在《圣经》中,光明和黑暗通常分别代表善与恶。尼布尔在他的书里则用“光明之子”和“黑暗之子”分指两类人。一类是理想主义者,他们并非不知天下熙熙,皆为利来;天下攘攘,皆为利往。但他们对人性极为乐观,相信义利问题不是什么了不起的问题,“自我利益和普遍利益之间的张力和冲突,完全有可能得到一劳永逸的解决”。“自我利益和各个层面的普遍福祉之间,有可能达成某种朴素的和谐。”(第7页)“光明之子”是“那些意欲将自我利益置于更具普世性的规律之下,使之与更具普世性的善相和谐的人。”(第9页)在尼布尔看来,不仅洛克、亚当?斯密是这样的“光明之子”,马克思主义者也是这样的“光明之子”。“光明之子”相信善总会战胜恶,义应该先于利,自我利益要服从整体利益;他们相信人的良知与道德。“黑暗之子”相反,尼布尔称他们为“犬儒主义者”,这些人“除了自我之外别无所知。他们尽管邪恶,却明智,是因为他们懂得自我利益的力量”(第10页)。他们的信条是人不为己,天诛地灭。不但他们的行动没有任何道德约束,他们的优势“还在于它能够顶住光明之子们的道德抗议,对个体和国家的自我利益的力量进行刁钻而准确的估算”(第11页)。 相比之下,“光明之子”是“极为愚蠢和盲目的”,因为他们的理想主义和乐观主义使得他们竟然对人类趋利的根本性没有足够的认识,而一厢情愿地从理想的角度来看待世界和人类,包括他们自己。尼布尔尖锐地指出:“光明之子之所以愚蠢,不仅仅是因为他们低估了黑暗之子的自我利益的力量。他们也低估了这一力量在自己身上的显示。民主世界之所以几乎遭遇灭顶之灾,不仅仅是因为它从不敢相信纳粹居然真的拥有它所宣称的恶魔般的仇恨。文明拒绝承认在其自身所属的共同体之内的阶级利益所发挥的力量。”(第12页)这就是说,光明之子本身也不是没有自身利益,并且受此利益驱使;可它偏要相信自己能先义后利。结果必然是,当黑暗之子在洗劫一个又一个的国家的时候,“光明之子”出于自利的目的,却在袖手旁观,没有施以援手。 光明之子的愚蠢和盲目,主要表现为他们看不到或者不愿承认“由于顾及私利而败坏了普世性的理想,是人类品行中的一个难以根除的事实,其顽固超出了任何道德说教愿意承认的程度”(第18页)。人类品行的这一事实之所以难以根除,是因为它源于人类的生存冲动或生存欲望,因而是人性的一部分,而且是比较基本的一部分。无论是光明之子还是黑暗之子,同样都具有这个本性。不同的是,前者忽略或轻视了它的根本性,而后者深刻地理解它的根本性。就此而言,

基于断言的验证技术 SystemVerilog Tutorials 下面的手册会帮助你了解一些SystemVerilog中最重要的新特点。手册还提供了一些代码样本和例子使你可以对语言有更好"感觉"。这些辅导假设你们已经了解了一些Verilog语言。如果没有,你可以先去看看Verilog设计者指南(V erilog Designer’s Guide)。 * Data types * RTL design * Interfaces * Clocking * Assertion-based verification * Classes * Testbench automation and constraints * The Direct Programming Interface (DPI) SystemVerilog 的数据类型 这个手册将描述Systemverilog新引进的数据类型。他们大多数都是可以综合的,并且可以使RTL级描述更易于理解和书写。 整型和实型 SystemVerilog引进了几种新的数据类型。C语言程序员会熟悉其中的大多数。引进新的数据类型构思是这样的,如果C语言和SystemVerilog有相同的数据类型可以使C语言算法模型更容易的转化为SystemVerilog模型。 Verilog的变量类型有四态:既是0,1,X,Z。SystemVerilog引进了新的两态数据类型,每一位只可以是0或是1。当你不需要使用的X和Z值时,譬如在写Testbench和做为for语句的循环变量。使用两态变量的RTL级模型,可以使模拟器更有效率。并且使用得当的话将不会对综合结果产生影响。 二态整型 类型描述例子 Bit user-defined size bit [3:0] a_nibble;

Qi1)What is callback (Qi2)What is factory pattern (Qi3)Explain the difference between data types logic and reg and wire . (Qi4)What is the need of clocking blocks (Qi5)What are the ways to avoid race condition between testbench and RTL using SystemVerilog (Qi6)Explain Event regions in SV. (Qi7)What are the types of coverages available in SV (Qi8)What is OOPS (Qi9)What is inheritance and polymorphism (Qi10)What is the need of virtual interfaces (Qi11)Explain about the virtual task and methods . (Qi12)What is the use of the abstract class (Qi13)What is the difference between mailbox and queue

(Qi14)What data structure you used to build scoreboard (Qi15)What are the advantages of linkedlist over the queue (Qi16)How parallel case and full cases problems are avoided in SV (Qi17)What is the difference between pure function and cordinary function (Qi18)What is the difference between $random and $urandom (Qi19)What is scope randomization (Qi20)List the predefined randomization methods. (Qi21)What is the dfference between always_combo and always@(*)c (Qi22)What is the use of packagess (Qi23)What is the use of $cast (Qi24)How to call the task which is defined in parent object into derived class (Qi25)What is the difference between rand and randc (Qi26)What is $root (Qi27)What is $unit

INTRODUCTION In this tutorial, we will verify the Switch RTL core. Following are the steps we follow to verify the Switch RTL core. 1) Understand the specification 2) Developing Verification Plan 3) Building the Verification Environment. We will build the Environment in Multiple phases, so it will be easy for you to learn step by step. Phase 1) We will develop the testcase and interfaces, and integrate them in these with the DUT in top module. Phase 2) We will Develop the Environment class. Phase 3) We will develop reset and configuration methods in Environment class. Then using these methods, we will reset the DUT and configure the port address. Phase 4) We will develop a packet class based on the stimulus plan. We will also write a small code to test the packet class implementation. Phase 5) We will develop a driver class. Packets are generated and sent to DUT using driver. Phase 6) We will develop receiver class. Receiver collects the packets coming from the output port of the DUT. Phase 7) We will develop scoreboard class which does the comparison of the expected packet with the actual packet received from the DUT. Phase 8) We will develop coverage class based on the coverage plan. Phase 9) In this phase , we will write testcases and analyze the coverage report.

SystemVerilog中的随机化激励 神州龙芯集成电路设计公司 杨鑫 徐伟俊 陈先勇 夏宇闻 [摘要]:随着集成电路的验证工作日渐复杂,对验证的可靠性提出了越来越高的要求。传统的验证工作中也使用随机化激励以便减轻测试代码编写的工作量,以提升验证的可靠性。在SystemVerilog更强调了利用随机化激励函数以提高验证代码的效率和验证可靠性的重要性。本文以VMM库为例,阐述了如何在SystemVerilog中使用随机化函数来编写高效率的测试代码,重点介绍了可重用验证函数库的使用方法,以帮助读者理解如何使用SystemVerilog高效率地完成复杂的设计验证。 关键字:VMM SystemVerilog 激励随机化 1. 前言 随着电路工艺设计技术的不断发展,集成电路的逻辑设计变得越来越复杂,随之对验证工作提出了更高的要求。由于投片(tip-out)的费用较高,很有必要在投片前对芯片设计进行全面、可信的验证,以尽量减少“设计——测试——投片——调试——发现Bug修改设计”这一流程的迭代次数。因此在集成电路芯片的设计中,尤其是复杂逻辑设计中,对测试工作的效率和可靠性提出了更高的要求。 在传统的验证方法中,也有将激励随机化的方法,这样可以用较少的测试代码生成较多、较全面的测试激励。这些方法减少了人为因素的干扰,能有效地提高验证的工作效率和可靠性。 在SystemVerilog中,强调在验证中使用可重用的验证IP,包括如何生成随机化激励。对于如何尽可能地使用已有的验证IP,以及编写符合标准的可重用验证组件,SystemVerilog提供了一整套的工作机制,这使得符合规范的随机化激励组件能够很好地在多个设计间复用,这更进一步地提高了验证工作的效率和可靠性。 2. 在验证中使用随机化激励 在验证中,可以依照DUT(Design Under Test,被测设计,以下简称DUT)的验证要求来设计定向的激励,并对照DUT的预期响应,用人工的方法来判断设计是否正确。但也可以使用随机化激励来驱动DUT,并使用特定的机制来完成响应的自检测。 利用随机化来产生激励可以看作一种近似的自动化激励产生,因为随机化足够长的时间后,所生成的激励可以覆盖绝大部分的待验证特性。但是纯粹的随机化激励效率并不高,因为其中正确的,或是有意义的激励只占很少一部分。必须使用一定的约束条件限制随机化的范围,从而产生大量随机而有意义的激励。