高频版图布线理论基础

高频版图布线理论基础<一>

半导体工艺发展得异常迅速,CMOS运用不仅局限于低频(Low Frequency )、中频(Intermediate Frequency )电路中,也运用于高频(Radio Frequence)电路。这种情形说明:我们感兴趣频率的波长将与器件的尺寸相当。以下是我整理出来的资料,仅供大家参考.

接下来,我们需要讲清楚几个事情, 因为我们除了尽力减少不希望有的寄生外, 还应该考虑在无法消除这些寄生时, 是否有其他因素的干扰. 应该如何避免或加以利用. 1, 影响什么? 2, 避免什么? 3, 利用什么?

一, 集中(lumped)与分布(distributed)的界线

λ0 =c/f0 (1)

电磁波在真空中以光速估算。c约为3E+8 m/s,以10G Hz计算,波长约为3cm。器件尺寸在1/10波长之内,即器件尺寸大于的十分之一波长就要考虑。分布理论将被应用.在此系统中麦克斯韦尔方程(Maxwell's equations)将取代集中理论基尔霍夫定律(Kirchhoff's law,KVL/KCL)。所以在分布系统中,一段金属线将不仅仅是一段金属线,而应被认为是传输线,运用传输线理论来分析。

我们无需对整个芯片进行分布理论分析,毕竟芯片内部器件尺寸大多还都远小于所感兴趣的波长.不过, 高频电路关键走线,还是应该用传输线理论加以对待。比如,片上电感外径设到300um = 0.03 cm 这个值已经与3 cm 不再遥远了。如果在10倍以内,应用就更有价值了.又比如, 引出走线长度如果达到3000um= 0.

3 cm, 就完全无法回避了.对于高频MOSFET 电路分析时, 这里的划分又称为准静态QS(Quasi-static)与NQS(non quasi-static)非准静态分析.它们之间的关键在于非准静态引进了电流连续方程. 我们画射频电路版图时, MOS Pcell会

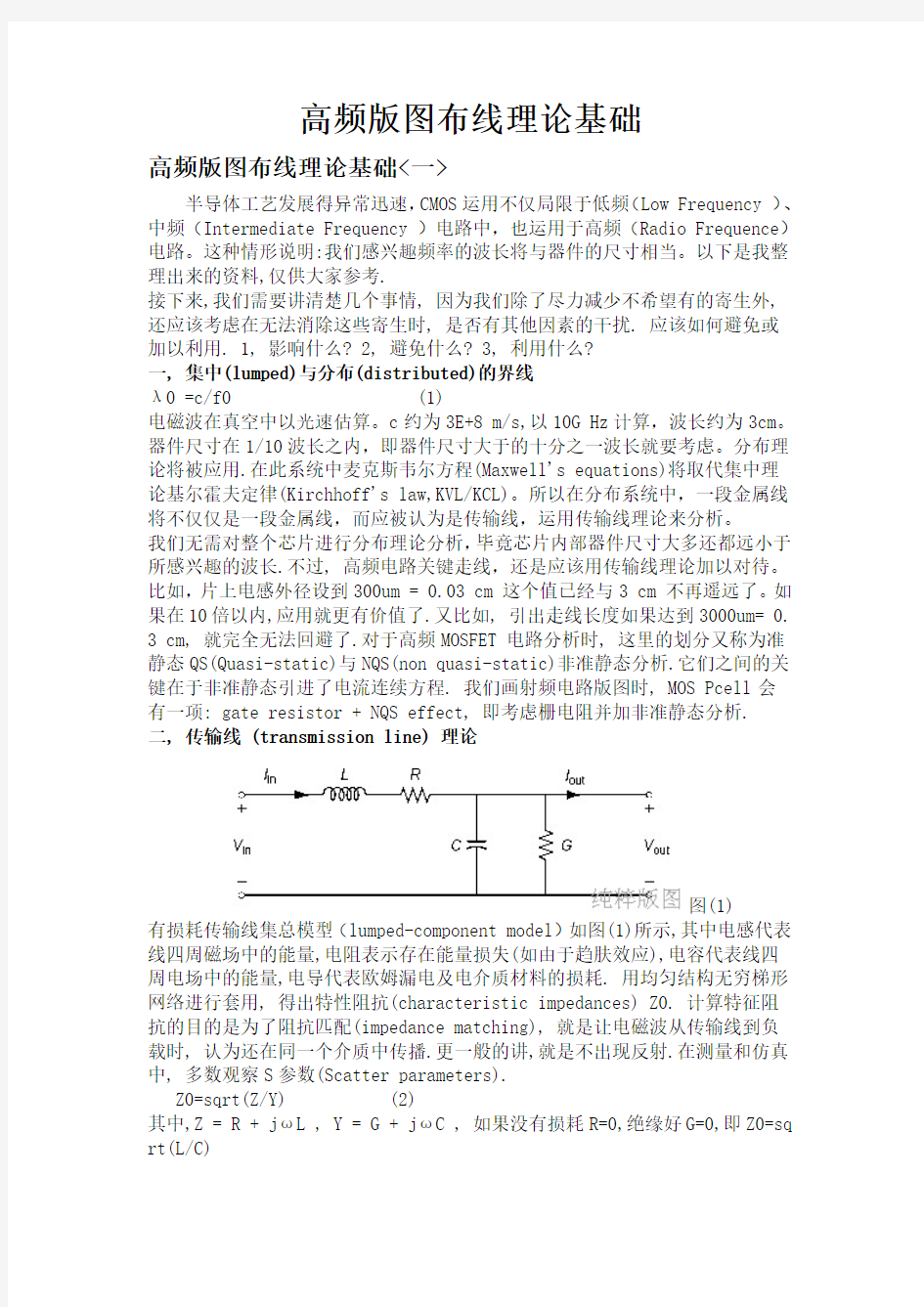

有一项: gate resistor + NQS effect, 即考虑栅电阻并加非准静态分析. 二, 传输线 (transmission line) 理论

图(1)

有损耗传输线集总模型(lumped-component model)如图(1)所示,其中电感代表线四周磁场中的能量,电阻表示存在能量损失(如由于趋肤效应),电容代表线四周电场中的能量,电导代表欧姆漏电及电介质材料的损耗. 用均匀结构无穷梯形网络进行套用, 得出特性阻抗(characteristic impedances) Z0. 计算特征阻抗的目的是为了阻抗匹配(impedance matching), 就是让电磁波从传输线到负载时, 认为还在同一个介质中传播.更一般的讲,就是不出现反射.在测量和仿真中, 多数观察S参数(Scatter parameters).

Z0=sqrt(Z/Y) (2)

其中,Z = R + jωL , Y = G + jωC , 如果没有损耗R=0,绝缘好G=0,即Z0=sq rt(L/C)

为了不混淆概念,这里作了整理:

Z 阻抗(impedance):包括

电阻R(resistance),

感抗(inductive reactance)XL = jωL ,

容抗(capacitive reactance)XC = 1/(jωC) 单位欧姆(Ω,ohm);

Y 导纳(admittance):包括

电导G(conductance),

感纳BL(inductive susceptance),

容纳BC(capacitive susceptance ),单位西蒙(s,seimen); 它们互为倒数关系.

另外,电抗(reactance)指阻抗虚数部分; 电纳(susceptance)指导纳虚数部分. 史密斯圆图(simth chart)上半圆为阻抗圆, 下半圆为导纳圆.

阻抗圆中,上半圆的电抗为正, 表示电阻与电感串联,

中心对称点下半圆为负的感纳,表示电导与感纳并联.

阻抗圆中,下半圆的电抗为负, 表示电阻与电容串联,

中心对称点上半圆为正的容纳,表示电导与容纳并联.

为了方便计算和分析,引入传播常数(propagation constant)

γ=sqrt(ZY)=α+jβ (3)

α称之为衰减常数(attenuation constant)单位napper/m,β称之为相位常数(phase constant)单位rad/m

经过变换和简化

α=Re[γ]≈ R/(2 * Z0) + G * Z0/2 (4)

如果R=G=0, α=0 ,即没有衰减

β=Im[γ]≈ ω*sqrt(LC) (5)

定义相位速度(phase velocity)为 ωt-βz=定值,即

ωt1-βz1=ωt2-βz2 (6)

νphase = (z2-z1)/(t2-t1)=ω/β (7)

λg = νphase /f = ω/(β*f)=2π/ β (8)

单位长度延时(per unit length delay)τ

τ=sqrt(LC) (9)

以上我们注意到,衰减和延时与频率无关.

在分布系统中,不再是电流电压的简单关系,而应视为电磁波进行分析. 电磁波在传输线中传输,最终到达负载.因为传输线阻抗 Z0 与负载阻抗 ZL 之间不能完全匹配,就会发生反射. 通常,对同轴电缆进行分析,以兼顾最大传输功率和最小衰减求导(即求极限)得到最优阻抗在30-77 ohms之间,折中取值为50 ohms.这就是常说的50欧姆匹配.

反射量与入射量的比称为反射系数Г (reflection coefficient)

ГL = (ZL – Z0) / (ZL + Z0) (10)

因为Z0,ZL均为复数,通过极化变换成三角函数形式进行变换,得出

ГL = ρ ∠Φ (11)

并进一步定义回波损耗(Return loss)和电压驻波比率(voltage standing wave ratio)

RL = -20Log (ρ) , ρ=|Г| (12)

VSWR = Emax / Emin = (1 + ρ) / (1 - ρ) (13)

不过负载是设计出来的,必然有其工作限制,截止频率为:

ωh = 2/sqrt(LC) (14)

三, 阻抗匹配 (impedances matching)

上面介绍的相同阻抗的匹配,但如果源阻抗30Ω,负载80Ω,如何相互匹配呢? 这里先介绍正弦光波从Z1向Z2传播时,通过增加中间媒介, 厚度为介质1的1/ 4波长, 阻抗Z3 = sqrt(Z1*Z2).同样电路中阻抗匹配,也需要增加匹配网络, 进行阻抗变换,以达到匹配.

阻抗变换网络首先应该是没有损耗的, 所以采用纯虚数集总元件, 或者是传输线. 不过, 集总元件的引入, 会带来带宽的限制和频率的限制.因为随着频率的上升, 集总元件网络能量存储单位是有限的, 而传输线却是无限的.

四, 趋肤效应 (skin effect)

图(1)模型是提到的电阻是由于趋肤效应(skin effect)引起的,与之类似的与频率相关的效应还有:边缘效应(edge effect)和接近效应(proximity effec t).在低频时,电流聚集在导体尖锐的边缘,因此使得电阻增加.中频的时,接近效应使得电流聚集到靠近信号线的地线部分,改变了两导体之间的磁场,减小了单位长度电感.当更多电流聚集到导体下面的地线上时,单位长度电阻也随之上升了.到了足够高频的时候,电流开始聚集在导体表面很浅的部分.但对于微带线(m icrostrip line),电流会更多的聚集在靠近相对介电常数(relative dielectri c constant)较高的衬底那边.体电阻率(bulk resistivity)越小,皮肤深度(ski n depth)越浅. 真空的相对介电常数为1,衬底的相对介电常数约为10. 在20C 时,铝的体电阻率约为2.65E-8 wm,铜的约为1.69E-8 wm. 趋肤效应会引起电流在表面深度 δ 下有1/e 的衰减.

Skin depth的计算公式如下:

δ=sqrt(2 / (ω*μ0*σ)) = sqrt( ρ / (π*f* μ0)) (15)

其中 μ0 真空磁导率 = 4 π*10^(-7)≈1.256E-6 H/m , H:henries=ws. σ为电导率(conductivity),ρ 电阻率(resistivity)

计算得到铜在10GHz时,皮肤深度约为0.65um .铜导体可以使用66/sqrt(f[MHz])来估算,铝导体使用81/sqrt(f[MHz])来估算. 最小带状导体厚度h (minimum t rack thickness)也有近似比例关系(一般情况下适用):

h = π*δ/2 (16)

电磁波渗入导体的时间(skin time):

τ = μ0 * σ* expt(a 2) (17)

a为导体特征尺寸

计算趋肤深度的意义是看导体是否受趋肤效应的影响, 如果导体厚度小于趋肤深度, 磁场将穿过导体. 比如片上电感器衬底通常采用PGS(patterned ground shield),以缓解涡流(eddy current)的造成的影响.常见有使用M1与POLY 制作图形屏蔽层. 90nm 典型铜工艺金属厚度P=0.15um,M1=0.2um,1X=0.25um,2X= 0.5um,4X=2.4um,12X=4um.如果屏蔽层过厚就会受趋肤效应的影响,磁场强度有会很大的衰减.不过,磁场已经穿过屏蔽层,而衬底也是可以导电的,所以感应电流还是会产生,最好的方法应该是除了增加屏蔽层,能让电感下的衬底变成绝缘体或者让变压器(transformer)中心磁化就更好了. 也因趋肤效应,不同的两个电感之间的距离,最好不小于其中最大一个的外径尺寸.

最后,趋肤效应会让动态电阻与频率的平方根成正比, 电阻会随频率不断的上升. 电感则会随频率下降,最终到达一个稳定值.

五, 微带线 (microstrip line)

传输线的类型很多,比如同轴线,带状线,微带线,双平行线,双绞线等。与芯片级版图走线类似的,微带线较为相近。但我们还不能完全应用,因为芯片级走线四周包裹着介电材料,而且没有地平面层。如果平行走线,或增加屏蔽线就更加复杂。在以后会进一步整理。

六, 结尾

整理这些资料的初衷, 是想了解高频版图布线的几个疑惑. 比如RF电路中IQ (in-phase and quadrature) 信号的传输, 应该用哪一层金属? 多宽? 间距是多少? 屏蔽线如何应用? 当然最好的方法就是用仿真软件进行电磁场仿真, 最后看结果即是. 不过要是有问题, 问题出在哪里? 如何改进? 恐怕软件还不能告诉你吧!!

这些资料还没有解决我的问题,在以后,我会继续整理这方面的资料. 做到有理有据画版图.

高频版图布线理论基础<二>

上篇我们介绍了高频与低频之间的界限,并介绍了最常见的传输线理论。由此引入了阻抗匹配,影响电阻的趋肤效应等概念。接下来,我们还需要寻找构成均匀传输线模型的其他方面的材料,比如有关储能元件电感、电容的计算,电导漏电的相关材料。当然,我们暂时还不会涉及到非均匀传输线概念的整理。本篇重点介绍阻抗匹配中最基础也是最实用的串、并联阻抗变换的概念,并以简单的集成螺旋电感模型的变换作为示范。本篇中可以找到的概念包括:带宽,-3dB 带宽,品质因子Q ,谐振,广义谐振等。目前主要的匹配方式有三种:串并联互换、传输线匹配和变压器变换。

一、串并联互换

图(1)

串并联互换的基本思路就是变换后阻抗相等,这也是我们想要的结果。因为变换首先考虑不能有能量的损耗,所以采用电抗元件,所以也称为LC阻抗变换。其他两种方式,如变压器:输入出阻抗比为初次级电感匝数比的平方。有一种形式的传输线匹配也是类似变压器的方式,即感应相同或相反的电流,从而达到阻抗变换的目的。1/4 波长传输线插入也常被使用。

根据图(1)写出等式:

Zs=Zp ==> Rs+jXs=Rp//jXp ==> 1/(Rs + jXs) = 1/Rp + 1/jXp (1)

(Rs – jXs)/[(Rs+jXs)(Rs-jXs)] = (Rs-jXs)/(Rs^2+Xs^2) = 1/Rp + 1/jXp (2)

实部与虚部分别相等,得到:

1/Rp = Rs/(Rs^2 + Xs^2) (3)

1/jXp = -jXs/(Rs^2 + Xs^2) (4)

整理后得到:

Rp = Rs(1+ Q^2) (5)

Xp = Xs(1+ 1/Q^2) (6)

其中:

Q = Rp/Xp = Xs/Rs (7)

如果Q>>1 , 由式5,6可得

Rp ≈ Rs * Q^2, Xp ≈ Xs (8)

公式5,6,7是后面演算的基础,也是最实用的等式。而式8 只是说明了,变换后电抗几乎不变,而电阻相差Q平方倍。

这里要解释一下Q值(Qulity factor)的定义:

Q LC = 2π* E max_store / E per_loss (9)

Q ind = 2π* (E max_L – E max_C) / E per_loss (10)

以RLC并联电路和类似模型的电感为例:Emax_store最大储能, Eper_loss为一周损耗

Emax_store= Emax_L = Emax_C

E max_L = V0^2/(2*ω^2*L), 电感储存磁场能量的最大值 (11)

E max_C = V0^2*C/2, 电容储存电场能量的最大值 (12)

E per_loss = T*V0^2/(2*R) 一个周期内的损耗 (13)

将11-13分别代入9,10得到:

Q LC = R* ω*C = R / ( ω*L) (14)

Q ind = R / ( ω*L) *[1 - ( ω/ ω0)^2] (15)

当电抗相互抵消,回路导纳最小或阻抗最大时,称回路为谐振。

jω0 C+1/jω0L = 0 ==> ω0 = 1/sqrt(L*C) (16)

通过磁场与电场能量相互的概念 E max_L = E max_C ,也可以得到同样的结果。ω0 称为谐振频率, 根据14可以写出并联网络Q值:

Q LC = Rp / Xp (17)

串联谐振网络,通过串并联对偶变换原则:L->C, C->L, G->Rs,V->I

Q LC = Rp / Xp = (1/G) / (1/Xc) = Xc/G => X L/Rs = Xs/Rs (18)

至此,我们就得到了式(7)的等式。不过,我们发现电感的Qind值有一些限制。比如电感工作频率应小于谐振频率。相等时,Q将为0; 大于时, Q将小于0,也就是呈现了电容的性质。我们还需要注意的是,谐振回路谐振时电感与电容的电流相等,但方向相反,其值是源电流的 Q 倍,所以布线时要注意要足够宽的线。

二、电感模型部分接入阻抗变换

图(2)

为了计算方便,令Cox=C1, Csi=C2,Rsi=R2。其中,Ls代表螺旋电感由Geen House方法求得;Rs表明串联的金属电阻,受涡流效应影响;Cs表示抽头时重叠电容;Cox表示电感与衬底的寄生电容;Rsi、Csi表示衬底本身的寄生电阻与电容。图2从左变换到右图,为一个典型的并联谐振回路。不过直接变换时,通常要满足Rsi >> Xsi ,并通过相关讨论得到的结论进行套用。实际的变换如图3为三个步骤。为了方便计算,在第a到b的变换中,也作些近似。

图(3)

(a) -> (b) :

R2 = R2s*(1+Q2^2) (19)

C2s = C2*(1+1/Q2^2) (20)

Q2 = R2/Xc2 = Xc2s/R2s (21)

假设C2s ≈ C2,即1/Q2^2 << 1,也就是Q2^2 >> 1, 重写式19,20得到:

R2 = R2s*Q2^2 (22)

C2s = C2 (23)

(b) -> (c) :

Rp = R2s*(1+Q^2) (24)

CΣ = C p*(1+1/Q^2) (25)

Q = R p/X p = XcΣ/R2s (26)

CΣ = C2*P (27)

P = C1 / (C1+C2) (28)

由式21得到 R2s = Xc2^2 / R2并将此式及12一同代入式24,25中,

Rp = Xc2^2 / R2 + XcΣ^2 / R2s

= 1/[(ω*C2)^2*R2] + R2/ P^2

= 1/[(ω*C2)^2*R2] + R2 * (C1 + C2)^2 / C1^2 (29) Cp = CΣ /(1+1/Q^2)

= CΣ*Q^2 / (1 + Q^2)

= CΣ* (R2*XcΣ/Xc2^2)^2 / [1+ R2*XcΣ/Xc2^2)^2]

= [CΣ* (R2*C2*ω/P)^2] / [1 + (R2*C2*ω/P)^2]

= [CΣ* (R2*C2*ω)^2] / [P^2 + (R2*C2*ω)^2]

= C1*C2*(R2*C2*ω)^2*(C1+C2) / {(C1*C2)^2 + [(R2*C2*ω)*(C1+C2)] ^2}

= C1*C2*(R2*ω)^2*(C1+C2) / {C1^2 + [(R2*ω)*(C1+C2)]^2} (30)

值得注意的是等式中的Q值,与整个回路的Q值要加以区分。式29将前一部分忽略,可得:

Rp = R2 / P^2 此式在直接变换中,利用变换后功率相等原则,可以迅速得到。

图(4)

对于设计RL与Rs匹配,要注意是串并变换,还是并串变换,这主要视电阻的大小而定。因为串联变换成并联,电阻增加Q平方倍,所以电阻小的一方应采用串联的方式。如图4所示,是一个L型的结构,如果源与负载均有一个L型网络就是π型,再将并联的电抗元件合并就是T型。由L型演变过来的π型或T型,其好处就是增加Q值的变换空间,充分利用了各节点的寄生参数。

三、带宽

上述介绍的串并联变换是谐振网络的阻抗匹配技术,一般应用于窄带范围。从频域上划分宽窄带,主要以信号带宽除以中心频率作为指标,

不大于0.1 为窄带(NB),

0.1-0.25 为宽带(WB),

不小于0.25 为超宽带(UWB)。

信号带宽就是我们常讲的3dB带宽(BW3dB),严格讲应该是-3dB带宽。以并联谐振回路为例,电流源Is为常数,电压特性也同样表达了阻抗特性。

输出电压为:

V(ω)=Is/Y=Is/(G+1/Xc+XL)=Is/[G+j(ωC-1/ωL)]

=(Is/G)/[1+j(ωC/G - 1/(G*ωL))]

=V(ω0)/[1+jQ( ω/ ω0 - ω0/ ω)] (31)

其中Q=ω0*C/G = 1/ω0*C*G

又定义ξ为广义谐振

ξ=Q( ω/ ω0 - ω0/ ω) (32)

如果频率在中心频率附近, ω≈ ω0 近似得到:

ξ=Q*2( ω- ω0)/ω0 = Q*2Δω/ω0 (33)

而选频特性又可得:

S=V(ω)/V(ω0)=1/[1+j ξ] (34)

代数化后得到:

S= expt(e,-jθ) / sqrt(1^2+ξ^2) (35)

θ= arctan ξ (36)

接下来令 ξ=1,即 S=1/sqrt(2)=0.707 刚好对应-3dB,将其展开得到: ξ=1=Q*2*2*π*Δf/(2*π*f0) =Q*2*Δf / f0

这里的2*Δf就是-3dB对应的带宽BW3dB,而 BW3dB / f0即为宽窄带指标。

BW3dB=f0 /Q (37)

通用的等式将是:

BWx = BW3dB * sqrt(1/x^2 - 1) (38)

显然,X最大值为1,而它也不可能小于0,所以X是介于 0-1 之间的一个值。Q值越大选择性越好,而带宽会变窄,X取值也会接近于1。

四、结尾

这篇中,我们讨论了最实用的串并联阻抗变换方法,也介绍了带宽。似乎我们还可以看到,通过改变中心频率或Q值,将窄带技术应用到宽带或超宽带中。

高频版图布线理论基础<三>

一、均匀结构无穷梯形网络模型

第一篇介说均匀传输线时说是套用了均匀结构无穷梯形网络模型公式,其基本的思路是:C点右边的阻抗等于B点右边阻抗,也等于A点右边的阻抗.这是一个很有用的概念,以至于让我摆脱了要解二阶偏微分方程的苦恼。

图(1)

Zin= Z + [(1/Y) // Zin ] (1)

Zin= Z/2 * [1+ sqrt(1+4/(Z*Y))] (2)

if |ZY|<<1, then

Zin = Z0 ≈ sqrt(Z/Y) (3)

同样

Z0 = Zdz+{[1/(Ydz)]//Z0} (4)

= Zdz+ Z0 /[1/(Ydz*Z0)]

当dz趋于零时的极限情形,可以利用1/(1+x)的一阶二项展开式

Z0 ≈Zdz + Z0[1-(Ydz)*Z0]

= Z0 + dz*[Z – Y*Z0^2]

Z0 =sqrt(Z/Y) = sqrt((R+jwL)/(G+jwC)) (5)

dz即Δz,表示线两个点之间距离.

二、传播常数

当研究传播常数时,也利用了基本思路,得到电压分压等式:

Vn+1= Vn * {[Z0//(1/(Ydz))] / [Zdz + (Z0 // (1/(Ydz)))]}

= Vn * {[Z0/(1+(Ydz))] / Z0}

= Vn * 1/[1+(Ydz*Z0)]

Vn+1/Vn = 1/[1+ (Ydz*Z0)] (6)

利用1/(1+x)展开

Vn+1/Vn = 1 – Ydz*Z0 (7)

(Vn+1-Vn)/Vn = - Ydz*Z0

∵ Z0 = sqrt(Z/Y) (8)

∴ dVn/Vn = -sqrt(Z*Y)*dz

dVn/Vn = -γ*dz (9)

两边同时积分可得

ln|Vn|+c1 = -γ*(z+c2) (10)

ln(Vn)=-γ*(z+c2)-c1

Vn = expt(e,-γ*(z+c2)-c1) (11)

V0 = expt(e,-γ*(0+c2)-c1) (12)

Vn = V0*expt(e,-γ*z) (13)

因为电压V0有两个分量相加, 入射Vin + 反射Vref. -γ*z表示正方向,γ*z 表示反方向.

Vn = Vin *expt(e,-γ*z) + Vref*expt(e,γ*z) (14)

又 Z0 = Vin/Iin = Vref/(-Iref) (15)

In = Iin *expt(e,-γ*z) – Iref*expt(e,γ*z) (16)

三、亥姆霍兹方程

利用电流电压公式对z两次微分后,得到亥姆霍兹方程(helmholtz equation)如图(2),也可以得到同样的结果.

图(2)

相关的亥姆霍兹方程可以浏览:

https://www.doczj.com/doc/8615530062.html,/wiki/Helmholtz_equation

四、有负载传输线阻抗

图(3)

ZL = (Vin+Vref) / (Iin-Iref)

= (Vin/Iin)*[(1+Vref/Vin)/(1-Vref/Vin)]

= Z0 * [(1+ГL)/(1-ГL)] (17)

ГL = (ZL-Z0)/(ZL+Z0) (18)

Гz = [Vref*expt(e,γ*z)] / [Vin*expt(e,-γ*z)]

= ГL*expt(e,2*γ*z) (19)

ZL 是负载阻抗,ГL是反射系数.增加负载后,出现反射,因而分量相加与相减得到的是负载反射系数.注意式17,隐含着长度变量z=0.所以ZL表示z=0的位置的阻抗Z(0).因而ГL =Г(0)也是z=0的反射系数.图(3)中Z=0加了标注,说明不应理解为起点在Zin的位置,而应在负载的位置.注意,加了负载后Zin不等于Z(0),除非Z=0,这一点不能与单独的传输线分析混淆起来.注意Z(0)不等于Z0,Z0仅表示特征阻抗,是一个通俗的写法.所以要得到任意点的阻抗Zz,需要进一步探讨.

归一化表示法:

~ZL = ZL/Z0 = (1+ГL)/(1-ГL) (20)

ГL = (ZL-Z0)/(ZL+Z0)= (~ZL-1)/(~ZL+1) (21)

Zz = [Vin*expt(e,-γ*z)+Vref*expt(e,γ*z)] /

[Iin*expt(e,-γ*z)-Iref*expt(e,γ*z)]

=Z0 * [1+ ГL*expt(e,-2*γ*z)]/[1- ГL*expt(e,-2*γ*z)]

=Z0 * [(~ZL+1)+(~ZL-1)*expt(e,-2*γ*z)]/[(~ZL+1)-(~ZL-1)*expt(e,-2*γ*z)]

=Z0 * [(~ZL+1)*expt(e,γ*z)+(~ZL-1)*expt(e,-γ*z)]/

[(~ZL+1)*expt(e,γ*z)-(~ZL-1)*expt(e,-γ*z)]

=Z0*{~ZL*[expt(e,γ*z)+expt(e,-γ*z)]+[expt(e,γ*z)-expt(e,-γ*z)] }/

{~ZL*[expt(e,γ*z)-expt(e,-γ*z)]+[expt(e,γ*z)+expt(e,-γ*z)] }

=Z0*[~ZL*cosh(γ*z)+sinh(γ*z)]/[~ZL*sinh(γ*z)+cosh(γ*z)]

=Z0*[~ZL+tanh(γ*z)]/[~ZL*tanh(γ*z)+1] (22)

~Zz = [~ZL+tanh(γ*z)]/[~ZL*tanh(γ*z)+1] (23)

式中sinh(x)双曲正弦=(1/2)*[e^x-e^(-x)],

cosh(x)双曲余弦=(1/2)*[e^x+e^(-x)], tanh(x)双曲正切=sinh(x)/cosh(x)

五、无损线阻抗变换

对于无损线:

γ=α+jβ = jβ, (24)

tanh(γ*z)=tanh(jβ*z)=jtan(β*z) (25)

~Zz= [~ZL+jtan(β*z)]/[~ZL*jtan(β*z)+1] (26)

Zz= Z0 * [ZL + Z0*jtan(β*z)]/[Z0 + ZL*jtan(β*z)] (27)

Zz也可以理解为长度z为的有载传输线的输入阻抗Zin.所以说Zin不等于Z(0)也不是Z0.

对于无损有载传输线:

短路时,ZL=0, Zz=Z0*jtan(β*z) (28)

开路时,ZL=∞, Zz=Z0*[ZL/(ZL*jtan(β*z)]

=Z0/jtan(β*z)

=Z0*-jcot(β*z) (29)

长度为1/2波长时,弧度为β*z=(λg/2)*(2*π/λg)=π,tan(π)趋于0.

Zz=Z0*[ZL]/[Z0]=ZL (30)

长度为1/4波长时,弧度为β*z=(λg/4)*(2*π/λg)=π/2 ,tan(π/2)趋于无穷大.

Zz=Z0*[Z0*jtan(β*z)]/[ZL*jtan(β*z)]

=Z0^2 / ZL (31)

由相位速度 Vphase= ω/β , β= 2*π/λg (32)

5.1传输线单支线串并联短截线(single shunt and series stub tuner)

图(4)

图4左为并联方式,右为串联方式。

如果是并联短路方式,则Zin=Ztl//Zso=Zs => Yin=Ytl+Ys (33)

Zin=Zs

Ztl=Z(d)=Z0 * [ZL + Z0*jtan(β*d)]/[Z0 + ZL*jtan(β*d)]

Zso=Z0*jtan(β*l)

Zs源阻抗,ZL负载阻抗,Ztl传输线短截阻抗,Zos短开路阻抗,Z0传输线特征阻抗

比如要连接ZL=100-j25Ω, Zs=25-j15Ω,传输线特征阻抗Z0=50Ω,如果是并联短路方式可以计算得到:d=0.168λg , l=0.083λg

如果是串联方式,则Zin=Ztl+Zso 也是类似的计算。

5.2传输线双支线并联短截线(double shunt stub tuner)

图(5)

双支线或多支线并联看起来复杂,但原理是相同的,只是多解几次并联。

Yin,1=Ytl,1+Ys,1

Yin,2=Ytl,2+Ys,2

Ytl,2=f(Yin,1) (34)

5.3 四分之一波长变换线

传输线取四分之一波长接入,从而影响整体阻抗的变化。

图(6)

由左31可知Zz=Z0^2 / Zl得出图6关系式:

Zin = Zl^2 /Z0 ==> Zl =sqrt(Zin*Z0) (35)

当然,还可以扩展,比如不是四分之一波长,取二分之一波长,或者取任意长度是否可行。比如不只接入一次,接入多个是否可行。接入多次又可以选择接入多个不同长度的传输线等等。

5.4 传输线变压器阻抗变换

传输线变压器是利用传输线之间互感耦合导致电流电压变化,从而达到阻抗变换的效果。常见的分类主要有:1,高频反相器;2,平衡与不平衡变换器;3,1:n阻抗变换器;4,3dB耦合器。

图(7)

图(7)介绍为4:1阻抗变换方式。互感产生方向相反等量电流I=Iin,造成负载电流是输入电流的双倍Il=I+I=2*I=2*Iin。由因为功率相等Vin*Iin = Vl*Il, Vl=Vin/2.

Rin=Vin/Iin , Rl=Vl/Il=(Vin/2)/2Iin= Vin/(4*Iin)=Rin/4, Rin=4*Rl (36)

图(8)

图(8)介绍为1:4阻抗变换方式。互感产生方向相反等量电流I=Iin/2,造成负载电流是输入电流的双倍Il=I==Iin/2。由因为功率相等Vin*Iin = Vl*Il, Vl=Vin*2.

Rin=Vin/Iin , Rl=Vl/Il=(Vin*2)/(Iin/2)= (Vin*4)/Iin=Rin*4, Rin=Rl/4 (37)

六、结尾

至此,我们已经了解到了传输线的基本概念,而且也了解到了无论是分布的传输线还是集中概念的LC元件,均可以完成阻抗变换的功能。不过,我们不会偏离IC版图相关性太远,整理传输线资料是我们继续下去的主线。接下来,我们将整理与IC版图布线较为相近的带线或微带线理论,也可能继续深入,用麦斯韦尔方程以另一个视角理解传输线理论,或许我们还有时间,搜寻有关不均匀传输线的概念。这些都是后篇中可能涉及到的一些概念。无论什么时候,网友们如发现资料中存在问题,均可以在论坛上发帖,我将给予更正或搜寻更多的相关资料进行补充。

高频版图布线理论基础<四>

(一)引言

上篇结尾时讲到,我们不能偏离ic layout(或on-chip)太远。 但这是一个过程,我们最终的目的是估算出合适的尺寸,那才是版图布线的本质。考虑布线的特性阻抗、衰减、功率等因素之后才能确定出合理的走线尺寸。

适合集成的平面传输结构有:带线(strip line)、微带线(microstrip line)、共面线(coplanar line)、槽线(slot line)和鳍线(fin line)。其中微带线可分为:标准微带线(或开式)standard、屏蔽微带线shielded、悬浮微带线floating、悬置微带线Suspended、倒置微带线invert、耦合微带线paralled coupled。共面线可分为:共面波导CPW(coplanar waveguide)与共面带状线CPS(coplanar stripline)。鳍线可分为:单侧鳍线unilateral、双侧鳍线(或平行)bilateral、对踵鳍线antipodal和绝缘鳍线insulated。还查到利用硅表面起伏制作的空气带隙传输线。这些结构之间常进行互补或转换。本文重点介绍 带线、微带线及共面线。此外,我们还应注意到传输线适用范围、比如频率和电磁波模式的限制。而对于这些传输线,无论如何变化,无非就在地线、导体、介质上的变化,比如改变形状、厚度、距离等。这些传输线中,我们又把带线、微带线、共面线作为我们今后的重点。

(二)带线特性阻抗的间接方法

带线是从同轴线演变而来,可以理解带线为将地平面线从中间剖开的扁平同轴线。求解带线的特性阻抗可以转化为解决电容的问题。

传输线特性阻抗:

Z0=sqrt(L/C)=sqrt(LC)/C

C=ε*s/d

L=μ*d/s

所以:

Z0=sqrt(εμ)/C

s为导体宽度,d为介质厚度, ε为介电系数,μ 为真空磁导率, 这就说明sqrt(εμ)相对常数,也说明传输线特性阻抗问题可以转化为解决电容的问题。

不过求解电容时,不能只求解平板电容值,难点出现在求解边缘电容上。S.B Cohn 将带状线厚度t设为0,通过施瓦茨-克里斯托费尔映射(Schwarz-christoffel mapping)变换公式,将复杂的情况转换为简单的2维问题,这样通过平板电容公式即可得出结论。而H.A Wheeler通过保角变换(Conformal mapping)方法演算

了有限厚度的带状线情况。因为相关资料从网络上搜索, 一般很难得到有用的相关资料,许多论文都集中在一些大型数据库中,而我们并没有条件得到,所以本篇也只能通过高校教材及免费阅读的部分资料来讨论零厚度带线电容的求解。当然除了保角变换方法外,还有其他静态分析方法及近似方法等。

(三)施瓦茨-克里斯托费尔变换

因为对称带线结构,我们可以先求解一半的电容(当然也可以求解四分之一的电容),然后加倍即可得到全部的电容值。如(图1.a)将厚度t设为0,并放置到w平面(坐标)中(图1.b)。现在我们要做的就是,将w平面中电容右半边变换到另一个z平面的上半面中(图1.c),再将z平面的上半面变换成w'平面的矩形(图1.d)。

图(1)带线的变换

为什么要进行如此的变换?这完全是为了便于求解和符合相关公式的定义。

图(2)施瓦茨-克里斯托费尔变换

施瓦茨-克里斯托费尔映射积分形式:

该方法就是将z平面的上半面变换到w平面的多边形。

其中A影响到变换的尺寸与位置,B影响到点到W=0时的距离,(z,z0)为边界条件。

接下来的任务就是套用公式,w-->z求解到k,w'-->z求解到K和K'.

如果将公式理解为:

W=Af(x)+B

那么A就是斜率,B就是平移量.也就是说,A决定了方向,而B决定了位置。

设ζ=t为实数。对于f点在(1,+∞)之间,取1/k是为了方便计算,(0 而出现K与K'的矩形,是因为雅可比椭圆函数、雅可比矩形的关系。 W-plane:[point,φi] a(+∞+jh,π),b(jh,π/2),c(0,π/2),d(w/2,2π),e(0,π/2),f(-jh,π/2),a' (+∞-jh,π) Z-plane:[xi] a(-∞),b(-1/k),c(-1),d(0),e(1),f(1/k),a'(+∞) W'-plane:[point,φi] a(jK',π),b(-K+jK',π/2),c(-K,π/2),d(0,π),e(K,π/2),f(K+jK',π/2),a '(jK',π) 当Wd(w/2,2π) 对应 Zd(0)时,z=z0=0,所以: Wd=B1=w/2 当We(0,π/2)对应 Ze(1)时,z=1,z0=0: 当Wf(-jh,π/2)对应 Zf(1/k)时,z=1/k,z0=0: 高频布线基本知识 内容目录 1. 引言 2. 信号完整性问题 3. 电磁兼容性问题 4. 电源完整性问题 5. 高频电路设计一般规范 6. 数模混合电路设计一般规范 一:高频电路的定义 *在数字电路中,是否是高频电路取决于信号的上升沿和下降沿,而不是信号的频率。 公式:F2 =1/(Tr×π),Tr为信号的上升/下降延时间。 *F2 > 100MHz,就应该按照高频电路进行考虑,下列情况必须按高频规则进行设计 –系统时钟频率超过50MHz –采用了上升/下降时间少于5ns的器件 –数字/模拟混合电路 *逻辑器件的上升/下降时间和布线长度限制上升/下主要谐波频谱分布最大传输线最大传输 降时间Tr分量F2=1/Fmax=10*距离(微带)线距离(微带线)πTr F2 74HC 13-15ns24MHz 240 MHz 117cm 91cm 74LS 9.5ns 34 MHz 340MHz 85.5cm 66.5cm 74H 4-6ns 80 MHz 800MHz 35 28 74S 3-4ns 106 MHz 1.1GHz 27 21 74HCT 5-15ns 64 MHz 640MHz 45 34 74ALS 2-10ns 160 MHz 1.6GHz 18 13 74FCT 2-5ns 160 MHz 1.6GHz 18 13 74F 1.5ns 212 MHz 2.1GHz 12.5 10.5 ECL12K 1.5ns 212 MHz 2.1GHz 12.5 10.5 ECL100K 0.75ns 424 MHz 4.2GHz 6 5 传统的PCB设计方法效率低: 原理图,传统的设计方法设计和输入布局、布线没有任何质量控制点,制作PCB每一步设计都是凭经验,发现问题就必须从头开始,功能、性能测试问题的查找非常困难 信号完整性问题: 1.反射问题 2.串扰问题 3.过冲和振荡 4.时延 反射问题:传输线上的回波。信号功率(电压和电流)的一部分传输到线上并达到负载处,但是有一部分被反射了。 多点反射 高频布线工艺和PCB板选材 -----需要探讨工艺和加工细节,可以联系QQ:748985601 摘要:本文通过对微带传输特性、常用板材性能参数进行比较分析,给出用于无线通信模拟前端、高速数字信号等应用中PCB板材选取方案,进一步从线宽、过孔、线间串扰、屏蔽等方面总结高频板PCB设计要点。 关键字:PCB板材、PCB设计、无线通信、高频信号 近年来在无线通信、光纤通信、高速数据网络产品不断推出,信息处理高速化、无线模拟前端模块化,这些对数字信号处理技术、IC工艺、微波PCB设计提出新的要求,另外对PCB板材和PCB工艺提出了更高要求。 如商用无线通信要求使用低成本的板材、稳定的介电常数(εr变化误差在±1-2%间)、低的介电损耗(0.005以下)。具体到手机的PCB板材,还需要有多层层压、PCB加工工艺简易、成品板可靠性高、体积小、集成度高、成本低等特点。为了挑战日益激烈的市场竞争,电子工程师必须在材料性能、成本、加工工艺难易及成品板的可靠性间采取折衷。 目前可供选用的板材很多,有代表性的常用板材有:环氧树脂玻璃布层压板FR4、多脂氟乙烯PTFE、聚四氟乙烯玻璃布F4、改性环氧树脂FR4等。特殊板材如:卫星微波收发电路用到蓝宝石基材和陶瓷基材;微波电路基材GX系列、RO3000系列、RO4000系列、TL系列、TP-1/2系列、F4B-1/2系列。它们使用的场合不同,如FR4用于1GHz以下混合信号电路、多脂氟乙烯PTFE多用于多层高频电路板、聚四氟乙烯玻璃布纤维F4用于微波电路双面板、改性环氧树脂FR4用于家用电器高频头(500MHz以下)。由于FR4板材易加工、成本低、便于层压,所以得到广泛应用。 下面我们从微带传输线特性、多层板层压工艺、板材参数性能比较等多个方面分析,给出了对于特殊应用的PCB板材选取方案,总结了高频信号PCB设计要点,供广大电子工程师参考。 1微带传输线传输特性 板材的性能指标包括有介电常数εr、损耗因子(介质损耗角正切)tgδ、表面光洁度、表面导体导电率、抗剥强度、热涨系数、抗弯强度等。其中介电常数εr、损耗因子是主要参数。 高速数据信号或高频信号传输常用到微带线(Microstrip Line),由附着在介质基片两边的导带和导体Array接地板构成,且导带一部分 暴露在空气中,信号在介质 基片和空气这两种介质中 传播引起传输相速不等会 产生辐射分量、如果合理选 用微带尺寸这种分量很小。 图一基片结构示意 1、图1所示为一超外差式七管收音机电路,试简述其工作原理。(15分) 图1 解:如图所示,由B1及C1-A 组成的天线调谐回路感应出广播电台的调幅信号,选出我们所需的电台信号f1进入V1基极。本振信号调谐在高出f1一个中频(465k Hz )的f2进入V1发射极,由V1三极管进行变频(或称混频),在V1集电极回路通过B3选取出f2与f1的差频(465kHz 中频)信号。中频信号经V2和V3二级中频放大,进入V4检波管,检出音频信号经V5低频放大和由V6、V7组成变压器耦合功率放大器进行功率放大,推动扬声器发声。图中D1、D2组成1.3V±0.1V 稳压,提供变频、一中放、二中放、低放的基极电压,稳定各级工作电流,保证整机灵敏度。V4发射一基极结用作检波。R1、R4、R6、R 10分别为V1、V2、V3、V5的工作点调整电阻,R11为V6、V7功放级的工作点调整电阻,R8为中放的AGC 电阻,B3、B4、B5为中周(内置谐振电容),既是放大器的交流负载又是中频选频器,该机的灵敏度、选择性等指标靠中频放大器保证。B6、B7为音频变压器,起交流负载及阻抗匹配的作用。(“X”为各级IC 工作电流测试点). 15’ 2、 画出无线通信收发信机的原理框图,并说出各部分的功用。 答: 上图是一个语音无线电广播通信系统的基本组成框图,它由发射部分、接收部分以及无线信道三大部分组成。发射部分由话筒、音频放大器、调制器、变频 器、功率放大器和发射天线组成。接收设备由接收天线、高频小信号放大器、混频器、中频放大器、解调器、音频放大器、扬声器等组成。 低频音频信号经放大后,首先进行调制后变成一个高频已调波,然后可通过上变频,达到所需的发射频率,经小信号放大、高频功率放大后,由天线发射出去。 由天线接收来的信号,经放大后,再经过混频器,变成一固定中频已调波,经放大与滤波的检波,恢复出原来的信息,经低频功放放大后,驱动扬声器。 3、对于收音机的中频放大器,其中心频率f0=465 kHz .B0.707=8kHz ,回路电容C=200 PF ,试计算回路电感和 QL 值。若电感线圈的 QO=100,问在回路上应并联多大的电阻才能满足要求。 答:回路电感为0.586mH,有载品质因数为58.125,这时需要并联236.66k Ω的电阻。 4、 图示为波段内调谐用的并联振荡回路,可变电容 C 的变化范围为 12~260 pF ,Ct 为微调电容,要求此回路的调谐范围为 535~1605 kHz ,求回路电感L 和Ct 的值,并要求C 的最大和最小值与波段的最低和最高频率对应。 解: 022 612 0622 11244651020010100.5864465200f L f C mH πππ-===????=≈??2由()03 03 4651058.125810 L L 0.707f Q f Q B =?===?0.707由B 得: 9 003120000 0000010010171.222465102001024652158.125 1171.22237.6610058.125 L L L L L L L Q R k C C C Q Q R g g g R Q Q R R R k Q Q Q ΩωππωωΩ∑ -===≈??????=== ++=-==?≈--因为:所以:( ),t C C C ∑ =+??=?????== 33根据已知条件,可以得出:回路总电容为因此可以得到以下方程组16051053510 电子工程师必须懂的高频PCB设计、EMI、EMC等设计技 巧 数字器件正朝着高速、低耗、小体积、高抗干扰性的方向发展,这一发展趋势对印刷电路板的设计提出了很多新要求。作者根据多年在硬件设计工作中的经验,总结一些高频布线的技巧,供大家参考。 (1)高频电路往往集成度较高,布线密度大,采用多层板既是布线所必须的,也是降低干扰的有效手段。 (2)高速电路器件管脚间的引线弯折越少越好。高频电路布线的引线最好采用全直线,需要转折,可用45°折线或圆弧转折,满足这一要求可以减少高频信号对外的发射和相互间的耦合。 (3)高频电路器件管脚间的引线越短越好。 (4)高频电路器件管脚间的引线层间交替越少越好。所谓“引线的层间交替越少越好”是指元件连接过程中所用的过孔(Via)越少越好,据测,一个过孔可带来约0.5 pF的分布电容,减少过孔数能显著提高速度。 (5)高频电路布线要注意信号线近距离平行走线所引入的“交叉干扰”,若无法避免平行分布,可在平行信号线的反面布置大面积“地”来大幅度减少干扰。同一层内的平行走线几乎无法避免,但是在相邻的两个层,走线的方向务必取为 相互垂直。 (6)对特别重要的信号线或局部单元实施地线包围的措施,即绘制所选对象的外轮廓线。利用此功能,可以自动地对所选定的重要信号线进行所谓的“包地”处理,当然,把此 功能用于时钟等单元局部进行包地处理对高速系统也将非 常有益。 (7)各类信号走线不能形成环路,地线也不能形成电流 环路。 (8)每个集成电路块的附近应设置一个高频去耦电容。(9)模拟地线、数字地线等接往公共地线时要用高频扼 流环节。在实际装配高频扼流环节时用的往往是中心孔穿有导线的高频铁氧体磁珠,在电路原理图上对它一般不予表达,由此形成的网络表(netlist)就不包含这类元件,布线时就 会因此而忽略它的存在。针对此现实,可在原理图中把它当做电感,在PCB元件库中单独为它定义一个元件封装,布 线前把它手工移动到靠近公共地线汇合点的合适位置上。(10)模拟电路与数字电路应分开布置,独立布线后应单点连接电源和地,避免相互干扰。 (11)DSP、片外程序存储器和数据存储器接入电源前,应加滤波电容并使其尽量靠近芯片电源引脚,以滤除电源噪声。另外,在DSP与片外程序存储器和数据存储器等关键部分 周围建议屏蔽,可减少外界干扰。 PCB板基础知识、布局原则、布线技巧、设计规则 PCB 板基础知识 一、PCB 板的元素 1、工作层面对于印制电路板来说,工作层面可以分为 6 大类,信号层(signal layer))内部电源/接地层内部电源接地层(internal plane layer))机械层(主要用来放置物理边界和放置尺寸标注等信息,起到相应机械层(mechanical layer))的提示作用。EDA 软件可以提供 16 层的机械层。防护层(包括锡膏层和阻焊层两大类。锡膏层主要用于将表面贴防护层(mask layer))元器件粘贴在 PCB 上,阻焊层用于防止焊锡镀在不应该焊接的地方。印层(在 PCB 板的 TOP 和 BOTTOM 层表面绘制元器件的外观丝印层(silkscreen layer))轮廓和放置字符串等。例如元器件的标识、标称值等以及放置厂家标志,生产日期等。同时也是印制电路板上用来焊接元器件位置的依据,作用是使 PCB 板具有可读性,便于电路的安装和维修。其他工作层(禁止布线层 Keep Out Layer 其他工作层(other layer))钻孔导引层 drill guide layer 钻孔图层 drill drawing layer 复合层multi-layer 2、元器件封装是实际元器件焊接到 PCB 板时的焊接位置与焊接形状,包括了实际元器件的外形尺寸,所占空间位置,各管脚之间的间距等。元器件封装是一个空间的功能,对于不同的元器件可以有相同的封装,同样相同功能的元器件可以有不同的封装。因此在制作 PCB 板时必须同时知道元器件的名称和封装形式。(1)元器件封装分类通孔式元器件封装(THT,through hole technology)表面贴元件封装(SMT Surface mounted technology )另一种常用的分类方法是从封装外形分类: SIP 单列直插封装 DIP 双列直插封装 PLCC 塑料引线芯片载体封装 PQFP 塑料四方扁平封装 SOP 小尺寸封装 TSOP 薄型小尺寸封装 PPGA 塑料针状栅格阵列封装 PBGA 塑料球栅阵列封装 CSP 芯片级封装 (2) 元器件封装编号编号原则:元器件类型+引脚距离(或引脚数)+元器件外形尺寸 例如 AXIAL-0.3 DIP14 (3)常见元器件封装 RAD0.1 RB7.6-15 等。 电阻类普通电阻 AXIAL- ×× ,其中××表示元件引脚间的距离;可变电阻类元件封装的编号为 VR × , 其中×表示元件的类别。电容类非极性电容编号 RAD ×× ,其中××表示元件引脚间的距离。极性电容编号 RB xx - yy ,xx 表示元件引脚间的距离,yy 表示元件的直径。二极管类编号 DIODE- ×× ,其中××表示元件引脚间的距离。晶体管类器件封装的形式多种多样。集成电路类 SIP 单列直插封装 DIP 双列直插封装 PLCC 塑料引线芯片载体封装 PQFP 塑料四方扁平封装 SOP 小尺寸封装 TSOP 薄型小尺寸封装 PPGA 塑料针状栅格阵列封装 PBGA 塑料球栅阵列封装 CSP 芯片级封装 3、铜膜导线是指 PCB 上各个元器件上起电气导通作用的连线,它是 PCB 设计中最重要的部分。对于印制电路板的铜膜导线来说,导线宽度和导线间距是衡量铜膜导线的重要指标,这两个方面的尺寸是否合理将直接影响元器件之间能否实现电路的正确连接关系。印制电路板走线的原则:◆走线长度:尽量走短线,特别对小信号电路来讲,线越短电阻越小,干扰越小。◆走线形状:同一层上的信号线改变方向时应该走 135°的斜线或弧形,避免 90°的拐角。◆走线宽度和走线间距:在 PCB 设计中,网络性质相同的印制板线条的宽度要求尽量一致,这样有利于阻抗匹配。走线宽度通常信号线宽为: 0.2~ . 高频电路原理与分析 期末复习资料 陈皓编 10级通信工程 2012年12月 1. 单调谐放大电路中,以LC并联谐振回路为负载,若谐振频率f0=10.7MH Z,C Σ = 50pF,BW0.7=150kH Z,求回路的电感L和Q e。如将通频带展宽为300kH Z,应在回路两端并接一个多大的电阻? 解:(1)求L和Q e (H)= 4.43μH (2)电阻并联前回路的总电导为 47.1(μS) 电阻并联后的总电导为 94.2(μS) 因 故并接的电阻为 2.图示为波段内调谐用的并联振荡回路,可变电容C的变化范围为12~260 pF,Ct为微调电容,要求此回路的调谐范围为535~1605 kHz,求回路电感L 和C t的值,并要求C的最大和最小值与波段的最低和最高频率对应。 12 min , 22(1210) 3 3 根据已知条件,可以得出: 回路总电容为因此可以得到以下方程组 160510 t t C C C LC L C ππ ∑ - =+ ? ?== ? ?+ ? ? 题2图 3.在三级相同的单调谐放大器中,中心频率为465kH Z ,每个回路的Q e =40,试 问总的通频带等于多少?如果要使总的通频带为10kH Z ,则允许最大的Q e 为多少? 解:(1 )总的通频带为 121212121232 260109 121082601091210260108 10198 1 253510260190.3175-12 6 1605 535 ()()10103149423435 t t t t C C C C pF L mH π-----?+==?+=?-??-= ?==??+?=≈ 高频布线工艺和PCB板选材 国家数字交换系统工程技术研究中心 张建慧饶龙记[郑州1001信箱787号] 摘要:本文通过对微带传输特性、常用板材性能参数进行比较分析,给出用于无线通信模拟前端、高速数字信号等应用中PCB板材选取方案,进一步从线宽、过孔、线间串扰、屏蔽等方面总结高频板PCB设计要点。 关键字:PCB板材、PCB设计、无线通信、高频信号 近年来在无线通信、光纤通信、高速数据网络产品不断推出,信息处理高速化、无线模拟前端模块化,这些对数字信号处理技术、IC工艺、微波PCB设计提出新的要求,另外对PCB板材和PCB工艺提出了更高要求。 如商用无线通信要求使用低成本的板材、稳定的介电常数(εr变化误差在±1-2%间)、低的介电损耗(0.005以下)。具体到手机的PCB板材,还需要有多层层压、PCB加工工艺简易、成品板可靠性高、体积小、集成度高、成本低等特点。为了挑战日益激烈的市场竞争,电子工程师必须在材料性能、成本、加工工艺难易及成品板的可靠性间采取折衷。 目前可供选用的板材很多,有代表性的常用板材有:环氧树脂玻璃布层压板FR4、多脂氟乙烯PTFE、聚四氟乙烯玻璃布F4、改性环氧树脂FR4等。特殊板材如:卫星微波收发电路用到蓝宝石基材和陶瓷基材;微波电路基材GX系列、RO3000系列、RO4000系列、TL系列、TP-1/2系列、F4B-1/2系列。它们使用的场合不同,如FR4用于1GHz以下混合信号电路、多脂氟乙烯PTFE多用于多层高频电路板、聚四氟乙烯玻璃布纤维F4用于微波电路双面板、改性环氧树脂FR4用于家用电器高频头(500MHz以下)。由于FR4板材易加工、成本低、便于层压,所以得到广泛应用。 下面我们从微带传输线特性、多层板层压工艺、板材参数性能比较等多个方面分析,给出了对于特殊应用的PCB板材选取方案,总结了高频信号PCB设计要点,供广大电子工程师参考。 1微带传输线传输特性 板材的性能指标包括有介电常数εr、损耗因子(介质损耗角正切)tgδ、表面光洁度、表面导体导电率、抗剥强度、热涨系数、抗弯强度等。其中介电常数εr、损耗因子是主要参数。 高速数据信号或高频信号传输常用到微带线(Microstrip Line),由附着在介质基片两边的导带和导体 接地板构成,且导带一部分 暴露在空气中,信号在介质 基片和空气这两种介质中 传播引起传输相速不等会Array产生辐射分量、如果合理选 用微带尺寸这种分量很小。 图 复习材料 1、什么是D类功率放大器,为什么它的集电极效率高? D类放大器是一种工作在开关状态的功率放大器,两个晶体管在输入激励控制下交替饱和导通或截止,饱和导通时,有电流流过,但饱和压降很低;截止时,流过晶体管的电流为零。所以晶体管的平均功耗很小,效率很高。 2、高频谐振放大器中,为使放大器稳定工作,可以采取哪些措施?一般采取提高稳定性的措施为:(1)采用外电路补偿的办法如采用中和法或失配法(2)减小负载电阻,适当降低放大器的增益(3)选用fT比较高的晶体管4)选用温度特性比较好的晶体管,或通过电路和其他措施,达到温度的自动补偿。 3、无线通信为什么要用高频信号?“高频”信号指的是什么? 高频信号指的是适合天线发射、传播和接收的射频信号。采用高频信号的原因主要是:(1)频率越高,可利用的频带宽度就越宽,信道容量就越大,而且可以减小或避免频道间的干扰;(2)高频信号更适合电线辐射和接收,因为只有天线尺寸大小可以与信号波长相比拟时,才有较高的辐射效率和接收效率。这样,可以采用较小的信号功率,传播较远的距离,也可获得较高的接收灵敏度。 4、当工作频率提高后,高频功放通常出现增益下降,最大输出功率和集电极效率降低,这是由哪些因素引起的?主要原因是1.放大器本身参数,如α、β随频率下降。2.电路失谐,集电极阻抗减小。3.少数载流子渡越时间效应。4.非线性电抗效应,如CbˊC 的影响。5.发射极引线电感的影响,对高频反馈加深。 5、克拉波和西勒振荡线路是怎样改进电容反馈振荡器性能的? 由于克拉波振荡器在回路中串行接入了一个小电容,使得晶体管的接入系数很小,耦合变弱,因此,晶体管本身的参数对回路的影响大幅度减小了,故使频率稳定度提高,但使得频率的调整范围变小,所以,西勒振荡器是在克拉波振荡器的基础上,在回路两端再并联一个可调电容,来增大频率调节范围。由于存在外接负载,当接入系数变小时,会带来增益的下降。 6、自动增益(AGC)控制电路的主要作用是什么? 自动增益(AGC)控制电路的主要作用是当输入电压在接收机允许的范围内升高时,保持接收机 集成电路版图设计 班级12级微电子姓名陈仁浩学号2012221105240013 摘要:介绍了集成电路版图设计的各个环节及设计过程中需注意的问题,然后将IC版图设计与PCB版图设计进行对比,分析两者的差异。最后介绍了集成电路版图设计师这一职业,加深对该行业的认识。 关键词: 集成电路版图设计 引言: 集成电路版图设计是实现集成电路制造所必不可少的设计环节,它不仅关系到集成电路的功能是否正确,而且也会极大程度地影响集成电路的性能、成本与功耗。近年来迅速发展的计算机、通信、嵌入式或便携式设备中集成电路的高性能低功耗运行都离不开集成电路掩模版图的精心设计。一个优秀的掩模版图设计者对于开发超性能的集成电路是极其关键的。 一、集成电路版图设计的过程 集成电路设计的流程:系统设计、逻辑设计、电路设计(包括:布局布线验证)、版图设计版图后仿真(加上寄生负载后检查设计是否能够正常工作)。集成电路版图设计是集成电路从电路拓扑到电路芯片的一个重要的设计过程,它需要设计者具有电路及电子元件的工作原理与工艺制造方面的基础知识,还需要设计者熟练运用绘图软件对电路进行合理的布局规划,设计出最大程度体现高性能、低功耗、低成本、能实际可靠工作的芯片版图。集成电路版图设计包括数字电路、模拟电路、标准单元、高频电路、双极型和射频集成电路等的版图设计。具体的过程为: 1、画版图之前,应与IC 工程师建立良好沟通在画版图之前,应该向电路设计者了解PAD 摆放的顺序及位置,了解版图的最终面积是多少。在电路当中,哪些功能块之间要放在比较近的位置。哪些器件需要良好的匹配。了解该芯片的电源线和地线一共有几组,每组之间各自是如何分布在版图上的? IC 工程师要求的工作进度与自己预估的进度有哪些出入? 2、全局设计:这个布局图应该和功能框图或电路图大体一致,然后根据模块的面积大小进行调整。布局设计的另一个重要的任务是焊盘的布局。焊盘的安排要便于内部信号的连接,要尽量节省芯片面积以减少制作成本。焊盘的布局还应该便于测试,特别是晶上测试。 3、分层设计:按照电路功能划分整个电路,对每个功能块进行再划分,每一个模块对应一个单元。从最小模块开始到完成整个电路的版图设计,设计者需要建立多个单元。这一步就是自上向下的设计。 4、版图的检查: (1)Design Rules Checker 运行DRC,DRC 有识别能力,能够进行复杂的识别工作,在生成最终送交的图形之前进行检查。程序就按照规则检查文件运行,发现错误时,会在错误的地方做出标记,并且做出解释。 高频电路原理与分析期末复习资料 陈皓编 10级通信工程 2012年12月 1.单调谐放大电路中,以LC 并联谐振回路为负载,若谐振频率f 0 =10.7MH Z , C Σ= 50pF ,BW 0.7=150kH Z ,求回路的电感L 和Q e 。如将通频带展宽为300kH Z ,应在回路两端并接一个多大的电阻? 解:(1)求L 和Q e (H )= 4.43μH (2)电阻并联前回路的总电导为 47.1(μS) 电阻并联后的总电导为 94.2(μS) 因 故并接的电阻为 2.图示为波段内调谐用的并联振荡回路,可变电容 C 的变化范围为 12~260 pF ,Ct 为微调电容,要求此回路的调谐范围为 535~1605 kHz ,求回路电感L 和C t 的值,并要求C 的最大和最小值与波段的最低和最高频率对应。 题2图 12min 12max ,22(1210) 22(26010)3 3根据已知条件,可以得出: 回路总电容为因此可以得到以下方程组16051053510t t t C C C LC L C LC L C ππππ∑ --=+? ?== ??+?? ??== ??+? 3.在三级相同的单调谐放大器中,中心频率为465kH Z ,每个回路的Q e =40,试 问总的通频带等于多少?如果要使总的通频带为10kH Z ,则允许最大的Q e 为多少? 解:(1)总的通频带为 4650.51 5.928()40 e z e Q kH =≈?= (2)每个回路允许最大的Q e 为 4650.5123.710 e e Q =≈?= 4.图示为一电容抽头的并联振荡回路。谐振频率f 0 =1MHz ,C 1 =400 pf ,C 2= 100 pF 121212121232 260109 121082601091210260108 10198 1 253510260190.3175-12 6 1605 535 ()()10103149423435 t t t t C C C C pF L mH π-----?+==?+=?-??-= ?==??+?=≈ 高頻佈線工藝和PCB板選材 國家數位交換系統工程技術研究中心 張建慧饒龍記[鄭州1001信箱787號] 摘要:本文通過對微帶傳輸特性、常用板材性能參數進行比較分析,給出用於無線通信類比前端、高速數位信號等應用中PCB板材選取方案,進一步從線寬、過孔、線間串擾、遮罩等方面總結高頻板PCB設計要點。 關鍵字:PCB板材、PCB設計、無線通信、高頻信號 近年來在無線通信、光纖通信、高速資料網路產品不斷推出,資訊處理高速化、無線模擬前端模組化,這些對數位信號處理技術、IC工藝、微波PCB設計提出新的要求,另外對PCB板材和PCB工藝提出了更高要求。 變化誤差在如商用無線通信要求使用低成本的板材、穩定的介電常數(ε r ±1-2%間)、低的介電損耗(0.005以下)。具體到手機的PCB板材,還需要有多層層壓、PCB加工工藝簡易、成品板可靠性高、體積小、集成度高、成本低等特點。為了挑戰日益激烈的市場競爭,電子工程師必須在材料性能、成本、加工工藝難易及成品板的可靠性間採取折衷。 目前可供選用的板材很多,有代表性的常用板材有:環氧樹脂玻璃布層壓板FR4、多脂氟乙烯PTFE、聚四氟乙烯玻璃布F4、改性環氧樹脂FR4等。特殊板材如:衛星微波收發電路用到藍寶石基材和陶瓷基材;微波電路基材GX系列、 B-1/2系列。它們使用的RO3000系列、RO4000系列、TL系列、TP-1/2系列、F 4 場合不同,如FR4用於1GHz以下混合信號電路、多脂氟乙烯PTFE多用於多層高頻電路板、聚四氟乙烯玻璃布纖維F4用於微波電路雙面板、改性環氧樹脂FR4用於家用電器高頻頭(500MHz以下)。由於FR4板材易加工、成本低、便於層壓,所以得到廣泛應用。 下面我們從微帶傳輸線特性、多層板層壓工藝、板材參數性能比較等多個方面分析,給出了對於特殊應用的PCB板材選取方案,總結了高頻信號PCB設計要點,供廣大電子工程師參考。 1微帶傳輸線傳輸特性 板材的性能指標包括有介電常數ε 、損耗因數(介質損耗角正切)tgδ、表 r 面光潔度、表面導體導電率、抗剝強度、熱漲係數、抗彎強度等。其中介電常數、損耗因數是主要參數。 ε r 高速資料信號或高頻信號傳輸常用到微帶線(Microstrip Line),由附著在介質基片兩邊的導帶和導 體接地板構成,且導帶一部 分暴露在空氣中,信號在介 質基片和空氣這兩種介質 中傳播引起傳輸相速不等Array會產生輻射分量、如果合理 選用微帶尺寸這種分量很 小。 高頻混合訊號積體電路的應用及設計趨勢 https://www.doczj.com/doc/8615530062.html, Application and Design Trend on High Frequency Mixed mode IC Design 瑞昱半導體研發中心 類比IC設計部經理林盈熙前言 隨著通訊、消費性電子產品及電腦應用的多元化,混合訊號積體電路的應用及設計趨勢也隨之複雜化。除了要考慮以往的電路技術層面的問題,也隨著先進製程的演變,設計流程所要解決的困難也增加了許多。此篇文章將目前業界研發高頻混合訊號積體電路所面臨的問題,及未來可能的解決方法與讀者進行討論。期待能藉由拋磚引玉的方式,讓更多的產業先進了解相關的問題。 產品及應用的趨勢 科技的進步除了帶來生活的便利之外,以往的通訊、娛樂及資訊取得的方式也產生很大的變革。通訊及網路的便捷讓人們樂於分享多媒體資訊。此外,資訊的取得與分享也隨著移動的需求轉而無線化及寬頻化。使用者對於多媒體資訊的品質需求也激發高速及高容量的產品走向。綜觀以上的變化,積體電路產品的應用趨勢可分為下列的三大方向 ?通訊(Communication) ?WLAN ?Digital Cellular Phone/ Wi-Fi Phone ?Modem/Remote Access ?消費性電子(Consumer) ?Digital Camera/ Video ?DVD ?Digital TV/HDTV ?電腦(Computer) ?Portable PC ?Live Plug-in Peripheral 此外因應消費者的需求及系統技術的變化,IEEE也制定了許多不同的無線通訊的規格。從低傳輸速率到高傳輸速率分別有不同的規格規範,並且在不同的傳輸距離之下系統的要求也有相異。細部的區分如下圖所示。 傳輸距離與轉輸速率的不同的無線通訊規格 一文读懂高频pcb线路板制作相关知识 众所周知高频PCB线路板涉及才高频材料,对工艺的要求也比较高。今天小编来分享一下高频电路板的制作工艺和注意事项。 首先我们从构造上去了解高频PCB板的制作 高频PCB主要由焊盘、过孔、安装孔、导线、元器件、接插件、填充、电气边界等组成,各组成部分的主要功能如下: 焊盘:用于焊接元器件引脚的金属孔。 过孔:有金属过孔和非金属过孔,其中金属过孔用于连接各层之间元器件引脚。 安装孔:用于固定电路板。 导线:用于连接元器件引脚的电气网络铜膜。 接插件:用于电路板之间连接的元器件。 填充:用于地线网络的敷铜,可以有效的减小阻抗。 电气边界:用于确定电路板的尺寸,所有电路板上的元器件都不能超过该边界。 其次了解高频电路板制作原理是必须: 在高频电路设计中,电源以层的形式设计,在大多数情况下都比以总线的形式设计要好得多,这样回路总可以沿着阻抗最小的路径走。此外电源板还得为PCB上所有产生和接受的信号提供一个信号回路,这样可以最小化信号回路,从而减小噪声,这点常常为低频电路设计人员所忽视。 在高频PCB设计中,我们应该遵循下面的原则: 电源与地的统一,稳定。 仔细考虑的布线和合适的端接可以消除反射。 仔细考虑的布线和合适的端接可以减小容性和感性串扰。 需要抑制噪声来满足EMC要求。 了解了高频电路板构成和制作原理我们就不难理解高频电路板加工注意点 1、阻抗控制要求比较严格,相对线宽控制的很严格,一般公差百分之二左右。 2、由于板材特殊,所以PTH沉铜时的附着力不高,通常需要借助等离子处理设备等先对过孔及表面进行粗化处理,以增加PTH孔铜和阻焊油墨的附着力。 3、做阻焊之前不能磨板,不然附着力会很差,只能用微蚀药水等粗化。 PCB Layout 中的高频电路布线技巧 1、多层板布线 高频电路往往集成度较高,布线密度大,采用多层板既是布线所必须,也是降低干扰的有效手段。在PCB Layout阶段,合理的选择一定层数的印制板尺寸,能充分利用中间层来设置屏蔽,更好地实现就近接地,并有效地降低寄生电感和缩短信号的传输长度,同时还能大幅度地降低信号的交叉干扰等,所有这些方法都对高频电路的可靠性有利。有资料显示,同种材料时,四层板要比双面板的噪声低20dB。但是,同时也存在一个问题,PCB半层数越高,制造工艺越复杂,单位成本也就越高,这就要求我们在进行PCB Layout时,除了选择合适的层数的PCB板,还需要进行合理的元器件布局规划,并采用正确的布线规则来完成设计。 2、高速电子器件管脚间的引线弯折越少越好 高频电路布线的引线最好采用全直线,需要转折,可用45度折线或者圆弧转折,这种要求在低频电路中仅仅用于提高铜箔的固着强度,而在高频电路中,满足这一要求却可以减少高频信号对外的发射和相互间的耦合。 3、高频电路器件管脚间的引线越短越好 信号的辐射强度是和信号线的走线长度成正比的,高频的信号引线越长,它就越容易耦合到靠近它的元器件上去,所以对于诸如信号的时钟、晶振、DDR的数据、LVDS线、USB线、HDMI线等高频信号线都是要求尽可能的走线越短越好。 4、高频电路器件管脚间的引线层间交替越少越好 所谓“引线的层间交替越少越好”是指元件连接过程中所用的过孔(Via)越少越好。据侧,一个过孔可带来约0.5pF的分布电容,减少过孔数能显著提高速度和减少数据出错的可能性。 5、注意信号线近距离平行走线引入的“串扰” 高频电路布线要注意信号线近距离平行走线所引入的“串扰”,串扰是指没有直接连接的信号线之间的耦合现象。由于高频信号沿着传输线是以电磁波的形式传输的,信号线会起到天线的作用,电磁场的能量会在传输线的周围发射,信号之间由于电磁场的相互耦合而产生的不期望的噪声信号称为串扰(Crosstalk)。PCB板层的参数、信号线的间距、驱动端和接收端的电气特性以及信号线端接方式对串扰都有一定的影响。所以为了减少高频信号的串扰,在布线的时候要求尽可能的做到以下几点: PCB线路板知识 PCB设计基本概念 1、“层(Layer) ”的概念 与字处理或其它许多软件中为实现图、文、色彩等的嵌套与合成而引入的“层”的概念有所同,Protel的“层”不是虚拟的,而是印刷板材料本身实实在在的各铜箔层。现今,由于电子线路的元件密集安装。防干扰和布线等特殊要求,一些较新的电子产品中所用的印刷板不仅有上下两面供走线,在板的中间还设有能被特殊加工的夹层铜箔,例如,现在的计算机主板所用的印板材料多在4层以上。这些层因加工相对较难而大多用于设置走线较为简单的电源布线层,并常用大面积填充的办法来布线。上下位置的表面层与中间各层需要连通的地方用软件中提到的所谓“过孔(Via)”来沟通。有了以上解释,就不难理解“多层焊盘”和“布线层设置”的有关概念了。举个简单的例子,不少人布线完成,到打印出来时方才发现很多连线的终端都没有焊盘,其实这是自己添加器件库时忽略了“层”的概念,没把自己绘制封装的焊盘特性定义为”多层(Mulii一Layer)的缘故。要提醒的是,一旦选定了所用印板的层数,务必关闭那些未被使用的层,免得惹事生非走弯路。 2、过孔(Via) 为连通各层之间的线路,在各层需要连通的导线的文汇处钻上一个公共孔,这就是过孔。工艺上在过孔的孔壁圆柱面上用化学沉积的方法镀上一层金属,用以连通中间各层需要连通的铜箔,而过孔的上下两面做成普通的焊盘形状,可直接与上下两面的线路相通,也可不连。一般而言,设计线路时对过孔的处理有以下原则:(1)尽量少用 过孔,一旦选用了过孔,务必处理好它与周边各实体的间隙,特别是容易被忽视的中间各层与过孔不相连的线与过孔的间隙,如果是自动布线,可在“过孔数量 PCB设计电路中的布线方法和技巧 PCB又被称为印刷电路板(Printed Circuit Board),它可以实现电子元器件间的线路连接和功能实现,也是电源电路设计中重要的组成部分。 多层板布线: 高频电路往往集成度较高,布线密度大,采用多层板既是布线所必须,也是降低干扰的有效手段。在PCB Layout阶段,合理的选择一定层数的印制板尺寸,能充分利用中间层来设置屏蔽,更好地实现就近接地,并有效地降低寄生电感和缩短信号的传输长度,同时还能大幅度地降低信号的交叉干扰等,所有这些方法都对高频电路的可靠性有利。同种材料时,四层板要比双面板的噪声低20dB。但是,同时也存在一个问题,PCB半层数越高,制造工艺越复杂,单位成本也就越高,这就要求在进行PCB Layout时,除了选择合适的层数的PCB板,还需要进行合理的元器件布局规划,并采用正确的布线规则来完成设计。 1、高速电子器件管脚间的引线弯折越少越好 高频电路布线的引线最好采用全直线,需要转折,可用45度折线或者圆弧转折,这种要求在低频电路中仅仅用于提高铜箔的固着强度,而在高频电路中,满足这一要求却可以减少高频信号对外的发射和相互间的耦合。 2、高频电路器件管脚间的引线层间交替越少越好 所谓“引线的层间交替越少越好”是指元件连接过程中所用的过孔(Via)越少越好。一个过孔可带来约0.5pF的分布电容,减少过孔数能显着提高速度和减少数据出错的可能性。 3、高频电路器件管脚间的引线越短越好 信号的辐射强度是和信号线的走线长度成正比的,高频的信号引线越长,它就越容易耦合到靠近它的元器件上去,所以对于诸如信号的时钟、晶振、DDR的数据、LVDS线、USB 线、HDMI线等高频信号线都是要求尽可能的走线越短越好。 4、注意信号线近距离平行走线引入的“串扰” 高频电路布线要注意信号线近距离平行走线所引入的“串扰”,串扰是指没有直接连接的 第三章集成电路版图设计 每一个电路都可以做的很完美,对应的版图也可以画的很艺术,需要的是耐心和细心,当然这需要知识,至少我这么认为。 3.1认识设计规则(design rule) 什么是设计规则?根据实际工艺水平(包括光刻精度、刻蚀能力、对准容差等)和成品率要求,给出的一组同一工艺层及不同工艺层之间几何尺寸的限制,主要包括线宽、间距、覆盖、露头、凹口、面积等规则,分别给出它们的最小值,以防止掩膜图形的断裂、连接和一些不良物理效应的出现。芯片上每个器件以及互连线都占有有限的面积。它们的几何图形形状由电路设计者来确定。(从图形如何精确地光刻到芯片上出发,可以确定一些对几何图形的最小尺寸限制规则,这些规则被称为设计规则) 制定设计规则的目的:使芯片尺寸在尽可能小的前提下,避免线条宽度的偏差和不同层版套准偏差可能带来的问题,尽可能地提高电路制备的成品率。 设计规则中的主要内容:Design Rule通常包括相同层和不同层之间的下列规定: 最小线宽 Minimum Width 最小间距 Minimum Spacing 最小延伸 Minimum Extension 最小包围 Minimum Enclosure 最小覆盖 Minimum Overlay 集成电路版图设计规则通常由集成电路生产线给出,版图设计者必须严格遵守!!! 3.2模拟集成电路版图设计中遵从的法则 3.2.1电容的匹配 对于IC layout工程师来说正确地构造电容能够达到其它任何集成元件所不能达到的匹配程度。下面是一些IC版图设计中电容匹配的重要规则。 1)遵循三个匹配原则:它们应该具有相同方向、相同的电容类型以及尽可能的靠近。这些规则能够有效的减少工艺误差以确保模拟器件的功能。 2)使用单位电容来构造需要匹配的电容,所有需要匹配的电容都应该使用这些单位电容来组成,并且这些电容应该被并联,而不是串联。3)使用正方块电容,并且四个角最好能够切成45度角。周长变化是导致不匹配的最主要的随机因素,周长和面积的比值越小,就越容 高频开关电源PCB布局与布线技巧 目前的交换式稳压器和电源设计更精巧、性能也更强大,但其面临的挑战之一,在于不断加速的开关频率使得PCB设计更加困难。PCB布局正成为区分一个开关电源设计好坏的分水岭。本文将就如何在第一次就实现良好PCB布局提出建议。 以一个将24V降为3.3V的3A交换式稳压器为例。乍看之下,一个10W稳压器不会太困难,所以设计师通常会忍不住直接进入建构阶段。 不过,在采用像美国国家半导体的Webench等设计软件后,我们可观察该构想实际上会遭遇哪些问题。输入上述要求后,Webench会选出该公司‘Simpler Switcher’系列的LM25576(一款包括3A FET的42V 输入组件)。它采用的是带散热垫的TSSOP‐20封装。 Webench选项包括对体积或效率的设计最佳化,这些均为单一选项。即高效率要求低开关频率(降低FET内的开关损耗)。因此需要大容量的电感和电容,因而需更大PCB空间。 注意:最高效率是84%,且此最高效率是当输入‐输出间的压差很低时实现的。此例中,输入/输出比率大于7。一般情况,用两个级降低级‐级比率,但透过两个稳压器得到的效率不会更好。 接着,我们选择最小PCB面积的最高开关频率。高开关频率最可能在布局方面产生问题。随后Webench 产生包含所有主动和被动组件的电路图。 电路设计 参考图1的电流通路:把FET在导通状态下流经的通路标记为红色;把FET在关断状态下的回路标记为绿色。我们观察到两种不同情况:两种颜色区域和仅一种颜色的区域。我们必须特别关注后一种情况,因为此时电流在零以及满量程电压间交替变化。这些均为高di/dt区域。 图1 高di/dt的交流电在PCB导线周围产生大量磁场,该磁场是该电路内其它组件甚至同一或邻近PCB上其它电路的主要干扰源。由于假设公共电流路径不是交流电,因此它不是关键路径,di/dt的影响也小得多。另一方面,随着时间变化,这些区域的负载更大。本例中,从二极管阴极到输出以及从输出地到二极管阳极是公共通路。当输出电容充放电时,该电容具有极高的di/dt。连接输出电容的所有线路必须满足两个条件:由于电流大,它们要宽;为最小化di/dt影响,它们必须尽量短。 高频PCB电路布线经验总结 如果数字逻辑电路的频率达到或者超过45MHZ~50MHZ,而且工作在这个频率之上的电路已经占到了整个电子系统一定的份量(比如说1/3),通常就称为高频电路。高频电路设计是一个非常复杂的设计过程,其布线对整个设计至关重要! 【第一招】多层板布线 高频电路往往集成度较高,布线密度大,采用多层板既是布线所必须,也是降低干扰的有效手段。在PCB Layout阶段,合理的选择一定层数的印制板尺寸,能充分利用中间层来设置屏蔽,更好地实现就近接地,并有效地降低寄生电感和缩短信号的传输长度,同时还能大幅度地降低信号的交叉干扰等,所有这些方法都对高频电路的可靠性有利。有资料显示,同种材料时,四层板要比双面板的噪声低20dB。但是,同时也存在一个问题,PCB半层数越高,制造工艺越复杂,单位成本也就越高,这就要求我们在进行PCB Layout时,除了选择合适的层数的PCB板,还需要进行合理的元器件布局规划,并采用正确的布线规则来完成设计。 【第二招】高速电子器件管脚间的引线弯折越少越好 高频电路布线的引线最好采用全直线,需要转折,可用45度折线或者圆弧转折,这种要求在低频电路中仅仅用于提高铜箔的固着强 度,而在高频电路中,满足这一要求却可以减少高频信号对外的发射和相互间的耦合。 【第三招】高频电路器件管脚间的引线越短越好 信号的辐射强度是和信号线的走线长度成正比的,高频的信号引线越长,它就越容易耦合到靠近它的元器件上去,所以对于诸如信号的时钟、晶振、DDR的数据、LVDS线、USB线、HDMI线等高频信号线都是要求尽可能的走线越短越好。 【第四招】高频电路器件管脚间的引线层间交替越少越好 所谓“引线的层间交替越少越好”是指元件连接过程中所用的过孔(Via)越少越好。据侧,一个过孔可带来约0.5pF的分布电容,减少过孔数能显著提高速度和减少数据出错的可能性。 【第五招】注意信号线近距离平行走线引入的“串扰” 高频电路布线要注意信号线近距离平行走线所引入的“串扰”,串扰是指没有直接连接的信号线之间的耦合现象。由于高频信号沿着传输线是以电磁波的形式传输的,信号线会起到天线的作用,电磁场的能量会在传输线的周围发射,信号之间由于电磁场的相互耦合而产生的不期望的噪声信号称为串扰(Crosstalk)。PCB板层的参数、信号线的间距、驱动端和接收端的电气特性以及信号线端接方式对串扰都有一定的影响。所以为了减少高频信号的串扰,在布线的时候要求尽可能的做到以下几点: 在布线空间允许的条件下,在串扰较严重的两条线之间插入一条地线或地平面,可以起到隔离的作用而减少串扰。PCB高频布线基本知识

PCB高频布线工艺和PCB板选材重点讲义资料

高频电路原理与分析试题库

电子工程师必须懂的高频pcb设计emiemc等设计技巧

PCB板基础知识

高频电路原理与分析

高频布线工艺PB板选材

高频电路复习材料

集成电路版图设计论文

高频电路原理与分析

高频布线工艺和PCB板选材Word版

高频混合讯号积体电路的应用及设计趋势

一文读懂高频pcb线路板制作相关知识

PCB Layout 中的高频电路布线技巧

PCB线路板知识

PCB设计电路中的布线方法和技巧

电路版图设计与规则

高频开关电源PCB布局与布线技巧

高频PCB电路布线经验总结