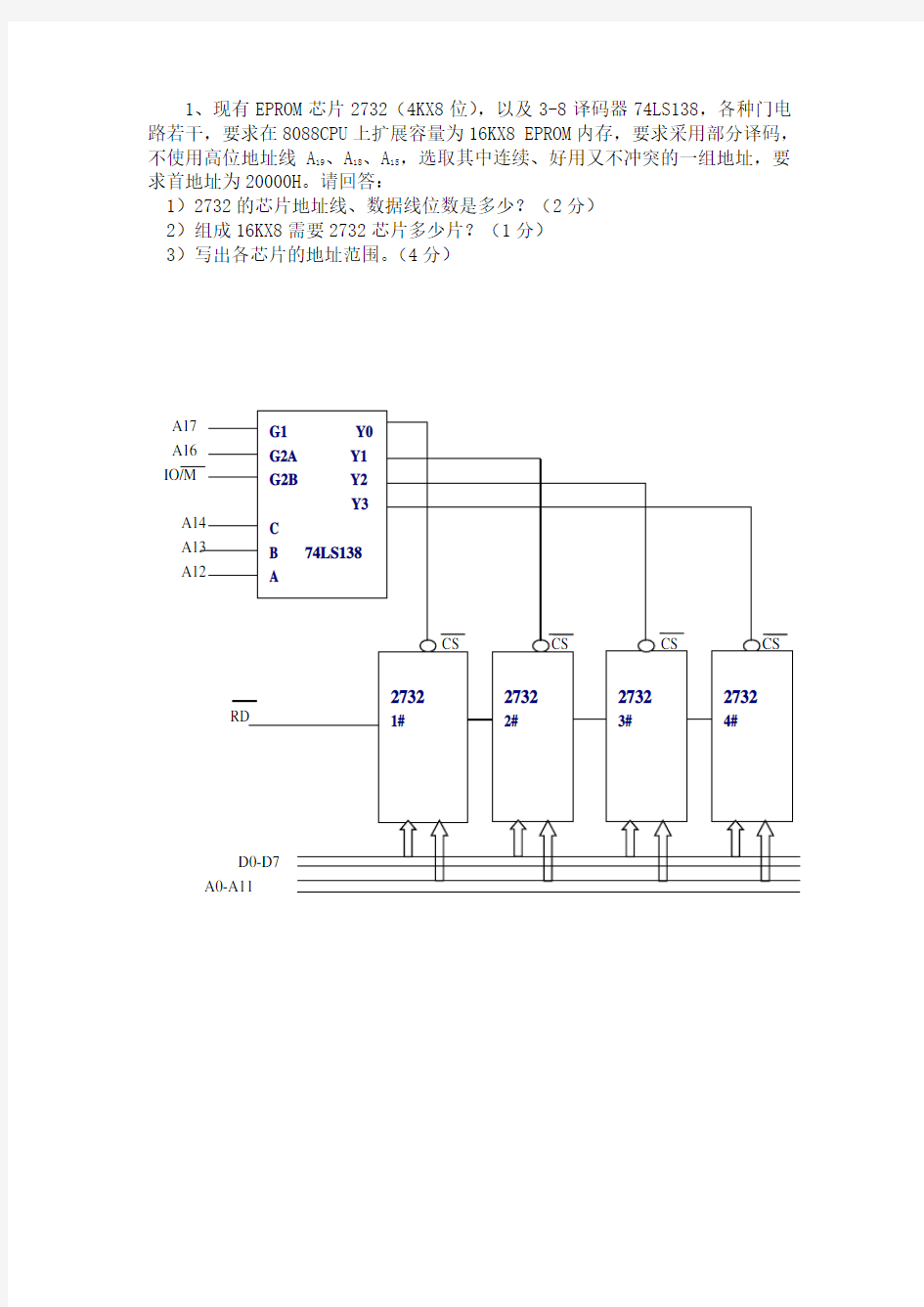

1、现有EPROM芯片2732(4KX8位),以及3-8译码器74LS138,各种门电路若干,要求在8088CPU上扩展容量为16KX8 EPROM内存,要求采用部分译码,

不使用高位地址线A

19、A

18

、A

15

,选取其中连续、好用又不冲突的一组地址,要

求首地址为20000H。请回答:

1)2732的芯片地址线、数据线位数是多少?(2分)2)组成16KX8需要2732芯片多少片?(1分)

3)写出各芯片的地址范围。(4分)

1)地址线12根,数据线8根;

2)4片;

3)1# 20000H~20FFFH 2# 21000H~21FFFH

3# 22000H~22FFFH 4# 23000H~23FFFH

2、有一个2732EPROM(4KX8)芯片的译码电路如下图所示,试求:

①计算2732芯片的存储容量;

②给出2732芯片的地址范围;

③是否存在地址重叠区?

① 4KB

②08000H---09FFFH

③存在重叠区08000H---08FFFH

09000H---09FFFH

3、某CPU有地址线16根(A0~A15),数据线8根(D0~D7)及控制信号RD、WR、MERQ(存储器选通)、IORQ(接口选通)。如图所示,利用RAM芯片2114(1KX4)扩展成2KX8的内存,请写出芯片组1和芯片组2的地址范围。

1

G MERQ

11A 12A 13

A 14A 15A &

A G 2

B G 21

Y C 13874LS B 0

Y 1#2114

CS

2#2114

CS 3#2114

CS 4#2114

CS 第1组

第2组

WR

RD

47~D D 0

9~A A 03~D D A

10

A

答:第1组:C000H~C3FFH

第2组:C400H~C7FFH

4、下面是一个8微机的与EPROM的连接图,请写出每片EPROM的地址范围。

74LS138

EPROM1:1000H~17FFH

EPROM2:1800H~1FFFH

EPROM3:2000H~27FFH

5、某微机的存储器系统总容量为64K。其中ROM占用4K,地址范围是:C000H~CFFFH;RAM占用2K,其地址范围是:E000H~E7FFH。现采用2K?8的ROM芯片(控制信号有CE、WE)和2K?4的RAM芯片(控制信号有CE、WE、OE)来构成该存储器系统中以上给定的6K 区域。请画出连接图。

2KROM 2KROM

2KRAM C000H~CFFFH E000H~E7FFH

现有一微机系统的内存扩展连接图如下,请问:

1. 在图中,RAM芯片的容量是多大?扩展的存储器容量是多大?。

2.请写出图中各芯片组的地址空间。

74LS138

1.RAM芯片容量为8k?4,存储器容量为16kB,。

2. RAM1芯片组地址范围:88000H~89FFFH

RAM2芯片组地址范围:8A000H~8BFFFH

微机原理(存储器)

深圳大学实验报告 课程名称:微型计算机技术 实验项目名称:静态储存器扩展实验 学院:信息工程学院 专业:电子信息工程 指导教师:骆剑平 报告人:罗沛鸿学号:2012130294 班级:电子3班实验时间: 实验报告提交时间: 教务处制

一.实验目的 1. 了解存储器扩展的方法和存储器的读/写。 2. 掌握CPU 对16 位存储器的访问方法。 二.实验设备 PC 机一台,TD-PITE 实验装置或 TD-PITC 实验装置一套,示波器一台。 三.实验内容 编写实验程序,将0000H~000FH 共16 个数写入SRAM 的从0000H 起始的 一段空间中,然后通过系统命令查看该存储空间,检测写入数据是否正确。 四.实验步骤和代码 1. 实验接线图如图4.4 所示,按图接线。 2. 编写实验程序,经编译、链接无误后装入系统。 3. 先运行程序,然后再停止程序运行。 4. 通过D 命令查看写入存储器中的数 据:D8000:0000 回车,即可看到存储 器中的数据,应为0001、0002、…、 000F 共16个字。 5. 改变实验程序,按非规则字写存储器,观察实验结果。 6. 改变实验程序,按字节方式写存储器,观察实验现象。 实验编程: SSTACK SEGMENT STACK DW 32 DUP(?) SSTACK ENDS CODE SEGMENT START PROC FAR ASSUME CS:CODE MOV AX,8000H MOV DS,AX

AAO: MOV SI, 0000H MOV CX,0010H MOV AX,0000H AA1: MOV[SI],AX INC AX INC SI INC SI LOOP AA1 NOP HERE: JMP HERE START ENDP CODE ENDS END START 五.实验结果:

1、现有EPROM芯片2732(4KX8位),以及3-8译码器74LS138,各种门电路若干,要求在8088CPU上扩展容量为16KX8 EPROM内存,要求采用部分译码, 不使用高位地址线A 19、A 18 、A 15 ,选取其中连续、好用又不冲突的一组地址,要 求首地址为20000H。请回答: 1)2732的芯片地址线、数据线位数是多少?(2分)2)组成16KX8需要2732芯片多少片?(1分) 3)写出各芯片的地址范围。(4分)

1)地址线12根,数据线8根; 2)4片; 3)1# 20000H~20FFFH 2# 21000H~21FFFH 3# 22000H~22FFFH 4# 23000H~23FFFH 2、有一个2732EPROM(4KX8)芯片的译码电路如下图所示,试求: ①计算2732芯片的存储容量; ②给出2732芯片的地址范围; ③是否存在地址重叠区? ① 4KB ②08000H---09FFFH ③存在重叠区08000H---08FFFH 09000H---09FFFH 3、某CPU有地址线16根(A0~A15),数据线8根(D0~D7)及控制信号RD、WR、MERQ(存储器选通)、IORQ(接口选通)。如图所示,利用RAM芯片2114(1KX4)扩展成2KX8的内存,请写出芯片组1和芯片组2的地址范围。

1 G MERQ 11A 12A 13 A 14A 15A & A G 2 B G 21 Y C 13874LS B 0 Y 1#2114 CS 2#2114 CS 3#2114 CS 4#2114 CS 第1组 第2组 WR RD 47~D D 0 9~A A 03~D D A 10 A 答:第1组:C000H~C3FFH 第2组:C400H~C7FFH

第五章存储器及其接口 1.单项选择题 (1)DRAM2164(64K╳1)外部引脚有() A.16条地址线、2条数据线 B.8条地址线、1条数据线 C.16条地址线、1条数据线 D.8条地址线、2条数据线 (2)8086能寻址内存贮器的最大地址范围为() A.64KB B.512KB C.1MB D.16KB (3)若用1K╳4b的组成2K╳8b的RAM,需要()。 A.2片 B.16片 C.4片 D.8片 (4)某计算机的字长是否2位,它的存储容量是64K字节编址,它的寻址范围是()。 A.16K B.16KB C.32K D.64K (5)采用虚拟存储器的目的是() A.提高主存的速度 B.扩大外存的存储空间 C.扩大存储器的寻址空间 D.提高外存的速度 (6)RAM存储器器中的信息是() A.可以读/写的 B.不会变动的 C.可永久保留的 D.便于携带的 (7)用2164DRAM芯片构成8086的存储系统至少要()片 A.16 B.32 C.64 D.8 (8)8086在进行存储器写操作时,引脚信号M/IO和DT/R应该是() A.00 B。01 C。10 D。11 (9)某SRAM芯片上,有地址引脚线12根,它内部的编址单元数量为()A.1024 B。4096 C。1200 D。2K (11)Intel2167(16K╳1B)需要()条地址线寻址。 A.10 B.12 C.14 D.16 (12)6116(2K╳8B)片子组成一个64KB的存贮器,可用来产生片选信号的地址线是()。 A.A 0~A 10 B。A ~A 15 C。A 11 ~A 15 D。A 4 ~A 19 (13)计算一个存储器芯片容量的公式为() A.编址单元数╳数据线位数B。编址单元数╳字节C.编址单元数╳字长D。数据线位数╳字长(14)与SRAM相比,DRAM() A.存取速度快、容量大B。存取速度慢、容量小 C.存取速度快,容量小D。存取速度慢,容量大 (15)半导动态随机存储器大约需要每隔()对其刷新一次。A.1ms B.1.5ms C.1s D.100μs (16)对EPROM进行读操作,仅当()信号同时有效才行,。A.OE、RD B。OE、CE C。CE、WE D。OE、WE 2.填空题 (1)只读存储器ROM有如下几种类型:_________. (2)半导体存储器的主要技术指标是_________。

** 习题 ** 选择最合适的答案 1.分页存储管理的存储保护是通过( )完成的. A.页表(页表寄存器) B.快表 C.存储键 D.索引动态重定 2.把作业地址空间中使用的逻辑地址变成内存中物理地址称为()。 A、加载 B、重定位 C、物理化 D、逻辑化 3.在可变分区存储管理中的紧凑技术可以()。 A.集中空闲区 B.增加主存容量 C.缩短访问时间 D.加速地址转换 4.在存储管理中,采用覆盖与交换技术的目的是( )。 A.减少程序占用的主存空间 B.物理上扩充主存容量 C.提高CPU效率 D.代码在主存中共享 5.存储管理方法中,( )中用户可采用覆盖技术。 A.单一连续区 B. 可变分区存储管理 C.段式存储管理 D. 段页式存储管理 6.把逻辑地址转换成物理地址称为()。 A.地址分配 B.地址映射 C.地址保护 D.地址越界 7.在内存分配的“最佳适应法”中,空闲块是按()。 A.始地址从小到大排序 B.始地址从大到小排序 C.块的大小从小到大排序 D.块的大小从大到小排序 8.下面最有可能使得高地址空间成为大的空闲区的分配算法是()。 A.首次适应法 B.最佳适应法 C.最坏适应法 D.循环首次适应法 9.那么虚拟存储器最大实际容量可能是( ) 。 A.1024K B.1024M C.10G D.10G+1M 10.用空白链记录内存空白块的主要缺点是()。 A.链指针占用了大量的空间 B.分配空间时可能需要一定的拉链时间 C.不好实现“首次适应法” D.不好实现“最佳适应法” 11.一般而言计算机中()容量(个数)最多. ** B.RAM C.CPU D.虚拟存储器

微机原理及单片机应用实验 实验报告 实验存储器读写实验 实验内容 对指定地址区间的RAM(4000H~4FFH)先进行写数据55AAH,然后将其内容读出再写到5000H~5FFH中。 实验步骤 l、在系统提示符“P”状态下,按SCAL键。 2、输入执行地址1850后,按EXEC键。 3、稍后按RST键退出,用存贮器读方法检查4000H~43FFH中的内容和5000~53FFH中的内容应都是55AA。 实验程序清单 CODE SEGMENT ;RAM.ASM ASSUME CS:CODE PA EQU 0FF20H ;字位口 PB EQU 0FF21H ;字形口 PC EQU 0FF22H ;键入口 ORG 1850h START: JMP START0 BUF DB ?,?,?,?,?,? data1: db0c0h,0f9h,0a4h,0b0h,99h,92h,82h,0f8h,80h,90h,88h,83h,0c6h,0a1h db 86h,8eh,0ffh,0ch,89h,0deh,0c7h,8ch,0f3h,0bfh,8FH START0: MOV AX,0H MOV DS,AX ;写数据段地址 MOV BX,4000H ;内存首址 MOV AX,55AAH ;要写入的字 MOV CX,0200H ;数据长度 RAMW1: MOV DS:[BX],AX ;写数据 ADD BX,0002H ;下一个单元 LOOP RAMW1 ;循环写 MOV AX,4000H ;首址 MOV SI,AX ;SI置源首址 MOV AX,5000H

MOV DI,AX ;DI置目首址 MOV CX,0400H ;数据长度 CLD ;增址 REP MOVSB ;串传送 call buf1 ;写”62256-” mov cx,0ffh con1: push cx call disp ;显示 pop cx loop con1 call buf2 ;写”--good” con2: call disp ;显示 jmp con2 DISP: MOV AL,0FFH ;显示子程序 ,5ms MOV DX,PA OUT DX,AL MOV CL,0DFH ;20H ;显示子程序 ,5ms MOV BX,OFFSET BUF DIS1: MOV AL,[BX] MOV AH,00H PUSH BX MOV BX,OFFSET DATA1 ADD BX,AX MOV AL,[BX] POP BX MOV DX,PB OUT DX,AL MOV AL,CL MOV DX,PA OUT DX,AL PUSH CX DIS2: MOV CX,00A0H LOOP $ POP CX CMP CL,0FEH ;01H JZ LX1

第5章存储器系统 主要内容: 存储器系统的概念 半导体存储器的分类及其特点 半导体存储芯片的外部特性及其与系统的连接 存储器接口设计(存储器扩展技术) 高速缓存 §5.1 概述 主要内容: 存储器系统及其主要技术指标 半导体存储器的分类及特点 两类半导体存储器的主要区别 一、存储器系统 1. 存储器系统的一般概念 将两个或两个以上速度、容量和价格各不相同 的存储器用硬件、软件或软硬件相结合的方法 连接起来 系统的存储速度接近最快的存储器,容量接近 最大的存储器。 构成存储系统。 2. 两种存储系统 在一般计算机中主要有两种存储系统: 主存储器 Cache存储系统 高速缓冲存储器 主存储器 虚拟存储系统 磁盘存储器

Cache存储系统 对程序员是透明的 目标: 提高存储速度 Cache 主存储器 虚拟存储系统 对应用程序员是透明的。 目标: 扩大存储容量 主存储器 磁盘存储器 3. 主要性能指标 存储容量(S)(字节、千字节、兆字节等) 存取时间(T)(与系统命中率有关) 命中率(H) T=H*T1+(1-H)*T2 单位容量价格(C) 访问效率(e) 4. 微机中的存储器 通用寄存器组及 指令、数据缓冲栈片内存储部件 高速缓存 内存储部件 主存储器 联机外存储器 外存储部件 脱机外存储器

二、半导体存储器 1. 半导体存储器 半导体存储器由能够表示二进制数“0”和“1”的、具有记忆功能的半导体器件组成。 能存放一位二进制数的半导体器件称为一个存储元。 若干存储元构成一个存储单元。 2. 半导体存储器的分类 随机存取存储器(RAM) 内存储器 只读存储器(ROM 随机存取存储器(RAM) 静态存储器(SRAM) RAM 动态存储器(DRAM) 只读存储器(ROM) 掩模ROM 只读存储器一次性可写ROM EPROM EEPROM 3. 主要技术指标 存储容量 存储单元个数×每单元的二进制数位数 存取时间 实现一次读/写所需要的时间 存取周期 连续启动两次独立的存储器操作所需间隔的最小时间 可靠性 功耗

第五章虚拟存储器 一、单项选择题 1. 虚拟存储器的最大容量___。 *A. 为内外存容量之和 B. 由计算机的地址结构决定(((实际容量 C. 是任意的 D. 由作业的地址空间决定 虚拟存储器是利用程序的局部性原理,一个作业在运行之前,没有必要全部装入内存,而只将当前要运行那部分页面或段装入便可以运行,其他部分放在外部存储器内,需要时再从外存调入内存中运行,首先它的容量必然受到外存容量的限制,其次寻址空间要受到计算机地址总线宽度限制。最大容量(逻辑容量)收内外存容量之和决定,实际容量受地址结构决定。2.在虚拟存储系统中,若进程在内存中占3块(开始时为空),采用先进先出页面淘汰算法,当执行访问页号序列为1﹑2﹑3﹑4﹑1﹑2﹑5﹑1﹑2﹑3﹑4﹑5﹑6时,将产生___次缺页中断。(开始为空,内存中无页面,3块物理块一开始会发生三次缺页。) A. 7 B. 8 C. 9 D. 10 3. 实现虚拟存储器的目的是___. A.实现存储保护 B.实现程序浮动 C.扩充辅存容量 D.扩充主存容量 4. 作业在执行中发生了缺页中断,经操作系统处理后,应让其执行___指令.(书本158页,(2)最后一句话) A.被中断的前一条 B.被中断的 C.被中断的后一条 D.启动时的第一条 5.在请求分页存储管理中,若采用FIFO页面淘汰算法,则当分配的页面数增加时,缺页中断的次数________。(在最后一题做完后再作答)答案错误选择:D A.减少 B. 增加 C. 无影响 D. 可能增加也可能减少 6. 虚拟存储管理系统的基础是程序的________理论. A. 局部性 B. 全局性 C. 动态性 D.虚拟性 7. 下述_______页面淘汰算法会产生Belady现象. A. 先进先出* B. 最近最少使用 C. 最近不经常使用 D. 最佳 二. 填空题 1. 假设某程序的页面访问序列为1. 2. 3. 4. 5. 2. 3. 1. 2. 3. 4. 5. 1. 2. 3. 4且开始执行时主存中没有页面,则在分配给该程序的物理块数是3 且采用FIFO方式时缺页次数是____13____; 在分配给程序的物理块数是4且采用FIFO方式时,缺页次数是___14______; 在分配给程序的物理块数是3且采用LRU方式时,缺页次数是______14____。在分配给程序的物理块数是4且采用LRU方式时,缺页次数是_____12____。