延安大学计算机学院实验报告专用纸

学号1110218014074 姓名王楠班级计科18 课程名称计算机组成原理

实验项目名称Cache控制器设计实验任课教师指导教师

实验组别第组同组者

教师评语及成绩:

实验成绩:教师签字:

(请按照实验报告的有关要求书写,一般必须包括:1、实验目的;2、实验内容;3、实验步骤与方法;4、实验数据与程序清单;5、出现的问题及解决方法;6、实验结果、结果分析与体会等内容。)

【1】实验目的

(1)掌握Cache控制器的原理及其设计方法。

(2)熟悉CPLD应用设计及EDA软件的使用。

【2】实验原理

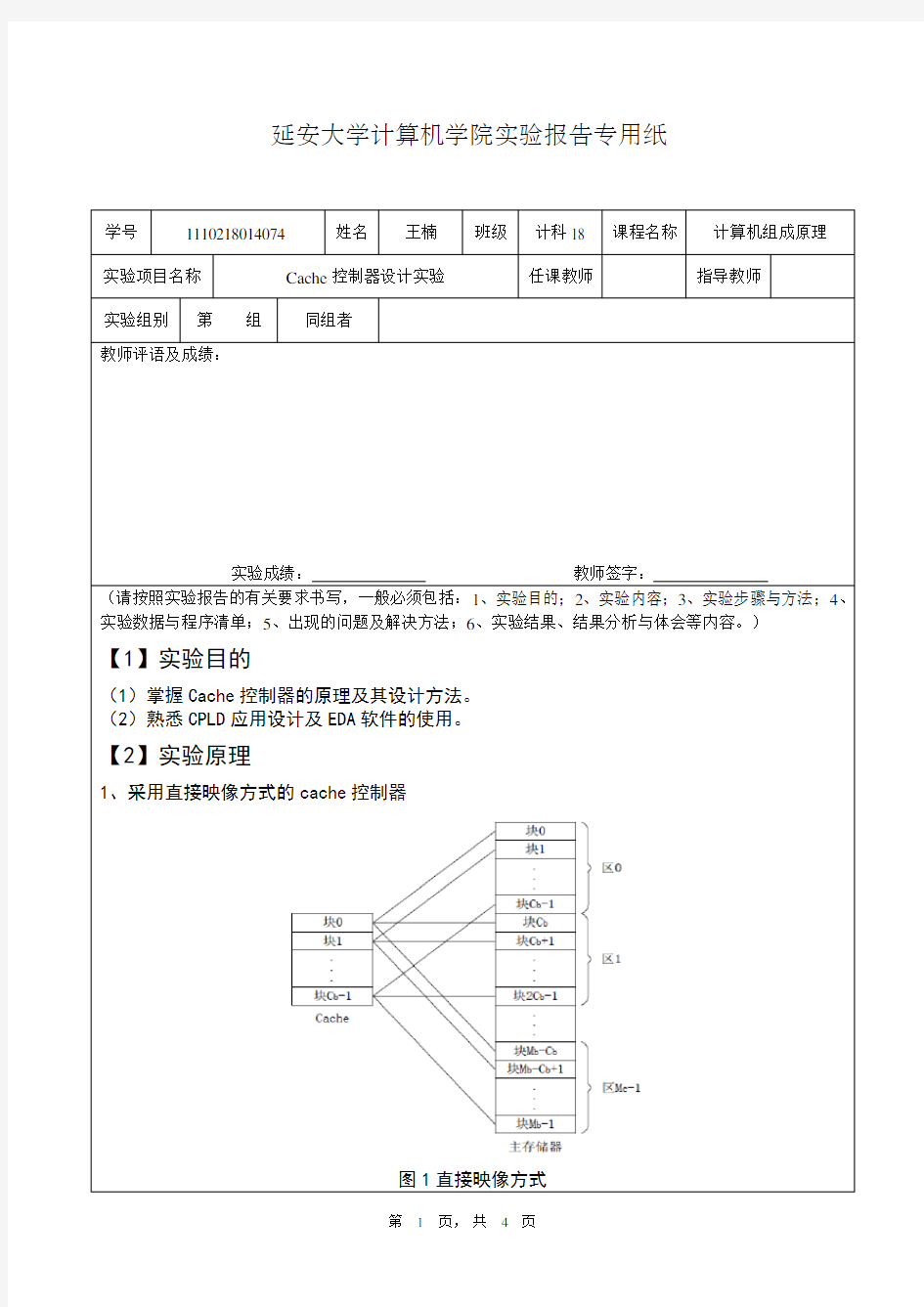

1、采用直接映像方式的cache控制器

图1直接映像方式

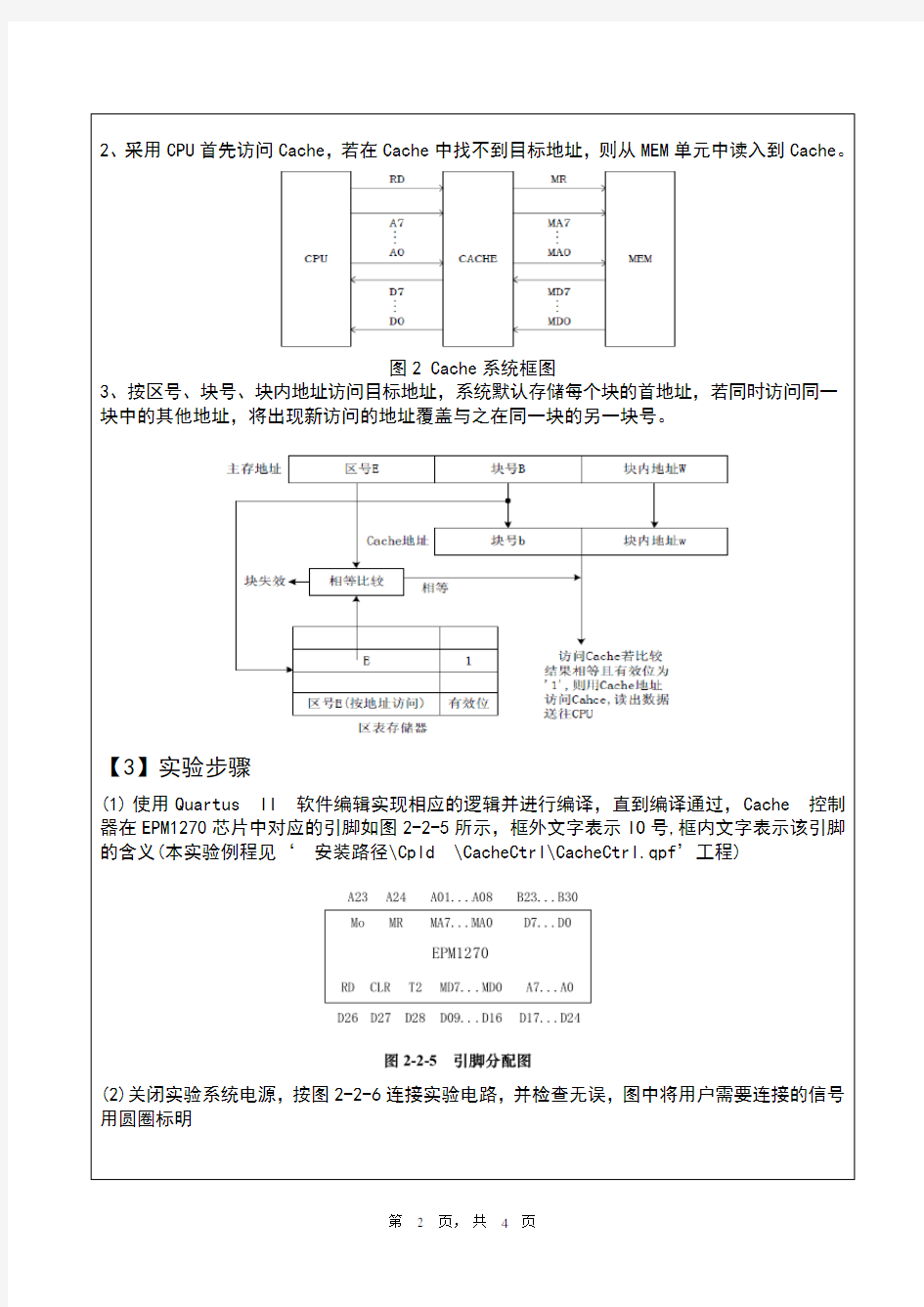

2、采用CPU首先访问Cache,若在Cache中找不到目标地址,则从MEM单元中读入到Cache。

图2 Cache系统框图

3、按区号、块号、块内地址访问目标地址,系统默认存储每个块的首地址,若同时访问同一块中的其他地址,将出现新访问的地址覆盖与之在同一块的另一块号。

【3】实验步骤

(1)使用Quartus II 软件编辑实现相应的逻辑并进行编译,直到编译通过,Cache 控制器在EPM1270芯片中对应的引脚如图2-2-5所示,框外文字表示IO号,框内文字表示该引脚的含义(本实验例程见‘安装路径\Cpld \CacheCtrl\CacheCtrl.qpf’工程)

(2)关闭实验系统电源,按图2-2-6连接实验电路,并检查无误,图中将用户需要连接的信号用圆圈标明

(3)打开实验系统电源,将生成的POF文件下载到EMP1270中去,CPLD单元介绍见实验1.2。

(4)将时序与操作台单元的开关KK3置为‘运行’档,CLR信号由CON单元的CLR模拟给出,按动CON单元的CLR按钮,清空区表。

(5)预先往主存写入数据:联机软件提供了机器程序下载功能,以代替手动读写主存,机器程序以指定的格式写入到以TXT为后缀的文件中,机器指令的格式如下:

如$P 1F 11,表示机器指令的地址为1FH,指令值为11H,本次实验只初始化00-0FH共16个单元,初始数据如下,程序中分号‘;'为注释符,分号后面的内容在下载时将被忽略掉。

用联机软件的“[转储] - [装载]”功能将该格式(*.TXT) 文件装载入实验系统。装入过程中,在软件的输出区的‘结果’栏会显示装载信息,如当前正在装载的是机器指令还是微指令,还剩多少条指令等。

(6)联机软件在启动时会读取所有机器指令和微指令,在指令区显示,软件启动后,也可以.选择菜单命令“[转储] - [ 刷新指令区]”读取下位机指令,并在指令区显示。点击指令区的‘主存’TAB按钮,两列数据中显示了主存的所有数据,第- -列为主存地址,第二列为该地址中的数据。对上面文件检查机器程序是否正确,如果不正确,则说明写入操作失败,应重新写入,可以通过联机软件单独修改某个单元的指令,单击需修改单元的数据,此时该单元变为编.辑框,输入2位数据并回车,编辑框消失,写入数据以红色显示。

一、引言 支点在下,重心在上,恒不稳定的系统或装置的叫倒立摆。倒立摆控制系统是一个复杂的、不稳定的、非线性系统,是进行控制理论教学及开展各种控制实验的理想实验平台。 问题的提出 倒立摆系统按摆杆数量的不同,可分为一级,二级,三级倒立摆等,多级摆的摆杆之间属于自有连接(即无电动机或其他驱动设备)。对倒立摆系统的研究能有效的反映控制中的许多典型问题:如非线性问题、鲁棒性问题、镇定问题、随动问题以及跟踪问题等。通过对倒立摆的控制,用来检验新的控制方法是否有较强的处理非线性和不稳定性问题的能力。 倒立摆的控制问题就是使摆杆尽快地达到一个平衡位置,并且使之没有大的振荡和过大的角度和速度。当摆杆到达期望的位置后,系统能克服随机扰动而保持稳定的位置。 倒立摆的控制方法 倒立摆系统的输入来自传感器的小车与摆杆的实际位置信号,与期望值进行比较后,通过控制算法得到控制量,再经数模转换驱动直流电机实现倒立摆的实时控制。直流电机通过皮带带动小车在固定的轨道上运动,摆杆的一端安装在小车上,能以此点为轴心使摆杆能在垂直的平面上自由地摆动。作用力u平行于铁轨的方向作用于小车,使杆绕小车上的轴在竖直平面内旋转,小车沿着水平铁轨运动。当没有作用力时,摆杆处于垂直的稳定的平衡位置(竖直向下)。为了使杆子摆动或者达到竖直向上的稳定,需要给小车一个控制力,使其在轨道上被往前或朝后拉动。 本次设计中我们采用其中的牛顿-欧拉方法建立直线型一级倒立摆系统的数学模型,然后通过开环响应分析对该模型进行分析,并利用学习的古典控制理论和Matlab /Simulink仿真软件对系统进行控制器的设计,主要采用根轨迹法,频域法以及PID(比例-积分-微分)控制器进行模拟控制矫正。

计算机组成原理实验报告 实验1:VERILOG 设计基础 专业班级:14级计算机二班 学号:14048001 姓名:杨娜 学号:14048003 姓名:周蓉 实验地点:理工楼901 实验时间:2016年5月14日

实验十VGA显示控制器的设计 一、实验目的 1、学习VERILOG的基本语法和编程规则 2、掌握通用寄存器等常用基本数字模块的VERILOG描述和基本设计方法 3、理解带使能控制和异步清零的8位寄存器的设计原理 4、掌握使用VERILOG设计和验证带使能控制和异步清零的8位寄存器的方法 5、掌握移位寄存器的设计方法 二、实验任务 1、设计一个带使能控制和异步清零的8位寄存器REG8X,实现8位输入的锁存,在时钟的上升沿处得到一个8位的输出和一个8位的反向输出,将结果显示在发光二极管。 模块的端口描述如下: 模块的参考物理结构如下: R7 R6 R i R 0 7 6 i 0 带使能控制和异步清零的8位寄存器 模块的使用注意事项

1.数据源D(7..0)一直加在寄存器的数据输入端; 2.周期性的时钟信号Clock一直加在寄存器的时钟输入端 3.使能信号Enable控制寄存器是否接受数据。当Enable = '0'时,寄存器不 接受数据,保持原来的状态不变;当Enable = '1'时,在时钟信号Clock正 跳变时,寄存器接受并保存当时D(7..0)的数据; 4.本寄存器其它方面的功能与上述的寄存器相同。 完成的参考电路图如下:dout=q 2、设计一个有左、右移位功能的8位寄存器REGSHIFT8,并仿真验证。

三、实验内容 1、通过输入数据先进行计算,并通过实验进行验证REG8X。 (1)、将清零信号Resetn(sw17)设为0,将输入信号D(sw7~sw0)设为10101010,观察输出信号Q(ledr7~ledr0)和Qb(ledg7~ledg0),观察并记录输出。 (2)、将清零信号Resetn(sw17)设为1,在时钟信号处输入一个上升沿(按下key0),观察并记录输出。 (3)、将输入信号D(sw7~sw0)设为01010101,观察并记录输出。 (4)、在时钟信号处输入一个上升沿(按下key0),观察并记录输出。 (5)、自行完善设计表格,观察并记录测试输出。 实验数据表 2、通过输入数据先进行计算,并通过实验进行验证REGSHIFT8。 (1)、测试清零信号Resetn (2)、测试移位功能 (3)、测试寄存功能 (4)、自行设计表格观察并记录测试输出。 实验数据表

实验2:MIPS指令系统和MIPS体系结构 一.实验目的 (1)了解和熟悉指令级模拟器 (2)熟悉掌握MIPSsim模拟器的操作和使用方法 (3)熟悉MIPS指令系统及其特点,加深对MIPS指令操作语义的理解 (4)熟悉MIPS体系结构 二. 实验内容和步骤 首先要阅读MIPSsim模拟器的使用方法,然后了解MIPSsim的指令系统和汇编语言。(1)、启动MIPSsim(用鼠标双击MIPSsim.exe)。 (2)、选择“配置”->“流水方式”选项,使模拟器工作在非流水方式。 (3)、参照使用说明,熟悉MIPSsim模拟器的操作和使用方法。 可以先载入一个样例程序(在本模拟器所在的文件夹下的“样例程序”文件夹中),然后分别以单步执行一条指令、执行多条指令、连续执行、设置断点等的方式运行程序,观察程序的执行情况,观察CPU中寄存器和存储器的内容的变化。 (4)、选择“文件”->“载入程序”选项,加载样例程序 alltest.asm,然后查看“代码”窗口,查看程序所在的位置(起始地址为0x00000000)。 (5)、查看“寄存器”窗口PC寄存器的值:[PC]=0x00000000。 (6)、执行load和store指令,步骤如下: 1)单步执行一条指令(F7)。 2)下一条指令地址为0x00000004,是一条有 (有,无)符号载入字节 (字节,半字,字)指令。 3)单步执行一条指令(F7)。 4)查看R1的值,[R1]= 0xFFFFFFFFFFFFFF80 。 5)下一条指令地址为0x00000008,是一条有 (有,无)符号载入字 (字节,半字,字)指令。 6)单步执行1条指令。 7)查看R1的值,[R1]=0x0000000000000080 。 8)下一条指令地址为0x0000000C ,是一条无 (有,无)符号载入字节 (字节,半字,字)指令。 9)单步执行1条指令。 10)查看R1的值,[R1]= 0x0000000000000080 。 11)单步执行1条指令。 12)下一条指令地址为0x00000014 ,是一条保存字 (字节,半字,字)指令。 13)单步执行一条指令。

电动车控制器原理及编程2008-10-29 15:34

电动车控制器原理及编程 https://www.doczj.com/doc/7613739181.html,/html/blog/7597/45892.htm 云翔电动车维修的BLOG https://www.doczj.com/doc/7613739181.html, 原信息URL:https://www.doczj.com/doc/7613739181.html,/html/blog/7597/45892.htm 控制器 无刷控制器硬件电路详解 电动车无刷电机是目前最普及的电动车用动力源,无刷电机以其相对有刷电机长寿,免维护的特点得到广泛应用,然而由于其使用直流电而无换向用的电刷,其换向控制相对有刷电机要复杂许多,同时由于电动车负载极不稳定,又使用电池作电源,因此控制器自身的保护及对电机,电源的保护均对控制器提出更多要求。 自电动车用无刷电动机问世以来,其控制器发展分两个阶段:第一阶段为使用专用无刷电动机控制芯片为主组成的纯硬件电路控制器,这种电路较为简单,其中控制芯片的代表是摩托罗拉的MC33035,这个不是这里的主题,所以也不作深入介绍。第二阶段是以MCU为主的控制芯片。这是这篇文章介绍的重点,在MCR 版本的设计中,揉和了模拟、数字、大功率MOSFET驱动等等许多重要应用,结合MCU智能化控制,是一个非常有启迪性的设计。 今以应用最广泛的以PIC16F72为智能控制中心,350W的整机电路为例,整机电路如图1: 图1:350W整机电路图 整机电路看起来很复杂,我们将其简化成框图再看看: 图2:电路框图 电路大体上可以分成五部分: 一、电源稳压,供应部分; 二、信号输入与预处理部分; 三、智能信号处理,控制部分; 四、驱动控制信号预处理部分; 五、功率驱动开关部分。 下面我们先来看看此电路最核心的部分:PIC16F72组成的单片机智能处理、控制部分,因为其他电路都是为其服务或被其控制,弄清楚这部分,其它电路就比较容易明白。 图3:PIC16F72在控制器中的各引脚应用图 我们先来简单介绍一下PIC16F72的外部资源:该单片机有28个引脚,去掉电源、复位、振荡器等,共有22个可复用的IO口,其中第13脚是CCP1输出口,可输出最大分辨率达10BIT的可调PWM信号,另有AN0-AN4共5路AD模数转换输入口,可提供检测外部电路的电压,一个外部中断输入脚,可处理突发事件。内部软件资源我们在软件部分讲解,这里并不需要很关心。

1 引言 支点在下,重心在上,恒不稳定的系统或装置的叫倒立摆。倒立摆控制系统是一个复杂的、不稳定的、非线性系统,是进行控制理论教学及开展各种控制实验的理想实验平台。 1.1 问题的提出 倒立摆系统按摆杆数量的不同,可分为一级,二级,三级倒立摆等,多级摆的摆杆之间属于自有连接(即无电动机或其他驱动设备)。对倒立摆系统的研究能有效的反映控制中的许多典型问题:如非线性问题、鲁棒性问题、镇定问题、随动问题以及跟踪问题等。通过对倒立摆的控制,用来检验新的控制方法是否有较强的处理非线性和不稳定性问题的能力。 倒立摆的控制问题就是使摆杆尽快地达到一个平衡位置,并且使之没有大的振荡和过大的角度和速度。当摆杆到达期望的位置后,系统能克服随机扰动而保持稳定的位置。 1.2 倒立摆的控制方法 倒立摆系统的输入来自传感器的小车与摆杆的实际位置信号,与期望值进行比较后,通过控制算法得到控制量,再经数模转换驱动直流电机实现倒立摆的实时控制。直流电机通过皮带带动小车在固定的轨道上运动,摆杆的一端安装在小车上,能以此点为轴心使摆杆能在垂直的平面上自由地摆动。作用力u平行于铁轨的方向作用于小车,使杆绕小车上的轴在竖直平面内旋转,小车沿着水平铁轨运动。当没有作用力时,摆杆处于垂直的稳定的平衡位置(竖直向下)。为了使杆子摆动或者达到竖直向上的稳定,

需要给小车一个控制力,使其在轨道上被往前或朝后拉动。 本次设计中我们采用其中的牛顿-欧拉方法建立直线型一级倒立摆系统的数学模型,然后通过开环响应分析对该模型进行分析,并利用学习的古典控制理论和Matlab /Simulink仿真软件对系统进行控制器的设计,主要采用根轨迹法,频域法以及PID(比例-积分-微分)控制器进行模拟控制矫正。 2 直线倒立摆数学模型的建立 直线一级倒立摆由直线运动模块和一级摆体组件组成,是最常见的倒立摆之一,直线倒立摆是在直线运动模块上装有摆体组件,直线运动模块有一个自由度,小车可以沿导轨水平运动,在小车上装载不同的摆体组件。 系统建模可以分为两种:机理建模和实验建模。实验建模就是通过在研究对象上加上一系列的研究者事先确定的输入信号,激励研究对象并通过传感器检测其可观测的输出,应用数学手段建立起系统的输入-输出关系。这里面包括输入信号的设计选取,输出信号的精确检测,数学算法的研究等等内容。 鉴于小车倒立摆系统是不稳定系统,实验建模存在一定的困难。因此,本文通过机理建模方法建立小车倒立摆的实际数学模型,可根据微分方程求解传递函数。 2.1 微分方程的推导(牛顿力学方法) 微分方程的推导在忽略了空气阻力和各种摩擦之后,可将直线一级倒立摆系统抽象成小车和匀质杆组成的系统,如图1所示。做以下假设: M小车质量m摆杆质量 b小车摩擦系数I 摆杆惯量

实验1 Cache性能分析 1 实验目的 (1)加深对Cache的基本概念、基本组织结构以及基本工作原理的理解。 (2)掌握Cache容量、相联度、块大小对Cache性能的影响。 (3)掌握降低Cache 2 实验平台 采用MyCache模拟器。 MyCache模拟器的使用方法: (1) 双击MyCache.exe,启动模拟器。 (2) 系统打开操作界面,如下图所示: (3) 写不命中时的调块策略。可以直接从列表中选择。 (4) 访问地址可以选择来自地址流文件,也可以选择手动输入。如果是前者,则可以通过单击“浏览”按钮,从模拟器所在文件夹下的“地址流”文件夹中选取地址流文件(.din)文件,然后执行。执行得方式可以是单步,也可以选择一次执行结束。如果选择手动输入,就可以在“执行控制”区域中输入块地址,然后单击“访问”按钮。系统会在界面的右边显示访问类型、地址、块号以及块内地址。 3 实验内容和步骤 3.1 Cache容量对不命中率的影响 (1) 启动MyCache。 (2) 单击“复位”按钮,将各参数设置为默认值。 (3) 选择一个地址流文件。具体方法:选择“访问地址”→“地址流文件”选项,然后单击“浏览”按钮,从本模拟器所在的文件夹下的“地址流”文件夹中选取。 (4) 选择不同的Cache容量,包括2KB,4 KB,8 KB,16 KB,32 KB,64 KB,128 KB和256 KB,分别执行模拟器(单击“执行到底”按钮就可执行),然后在表1.1中记录各种情况下的不命中率。 地址流文件名:all.din 表1.1 不同容量下Cache的不命中率

(5)指明地址流文件名,以容量为横坐标,画出不命中率虽Cache容量变化而变化的曲线 (6) 根据该模拟结果,能得出什么结论? 相同的地址流文件,Cache容量越大,Cache的不命中率越低,命中率越高,但当Cache 容量达到一定程度时,Cache的命中率将不变。 3.2 相联度对不命中率的影响 (1) 单击“复位”按钮,将各参数设置为默认值。此时的Cache容量为64KB。 (2) 选择一个地址流文件。具体方法:选择“访问地址”→“地址流文件”选项,然后单击“浏览”按钮,从本模拟器所在的文件夹下的“地址流”文件夹中选取。 (3) 选取不同的Cache相联度,包括直接映像、2路、4路、8路、16路和32路。分别执行模拟器(单击“执行到底”按钮),然后再表1.2中记录各种情况下的不命中率。 地址流文件名:all.din (4) 把Cache的容量设置为256KB,重复(3)步骤填表1.3。

HUNAN UNIVERSITY 课程实习报告 题目: 8086/8088指令系统 学生姓名 学生学号 专业班级计算机科学与技术2班 指导老师 完成日期2013年4月21日

一、实验目的 利用debug工具的e和u功能找出8086/8088指令系统的指令格式中各种操作吗编码对应的指令功能,得到8086/8088操作吗从00~FF所对应的的汇编指令的名字。并加以分析总结,形成你的关于8086/8088指令系统操作码编码方法的实验报告。 二、实验过程 1、编写C++程序,生成debug的输入文件(shuru.txt) 2、将shuru.txt复制到debug的根目录下,在debug界面输入如下指令“debug

打开out2.txt,对256条记录进行分析。 三、256条记录 指令码汇编指令 ------------------------------------------------------------- 0B76:0100 0000 ADD [BX+SI],AL 0B76:0100 0100 ADD [BX+SI],AX 0B76:0100 0200 ADD AL,[BX+SI] 0B76:0100 0300 ADD AX,[BX+SI] 0B76:0100 0400 ADD AL,00 0B76:0100 050000 ADD AX,0000 0B76:0100 06 PUSH ES 0B76:0100 07 POP ES 0B76:0100 0800 OR [BX+SI],AL 0B76:0100 0900 OR [BX+SI],AX 0B76:0100 0A00 OR AL,[BX+SI] 0B76:0100 0B00 OR AX,[BX+SI] 0B76:0100 0C00 OR AL,00 0B76:0100 0D0000 OR AX,0000 0B76:0100 0E PUSH CS 0B76:0100 0F DB 0F 0B76:0100 1000 ADC [BX+SI],AL 0B76:0100 1100 ADC [BX+SI],AX 0B76:0100 1200 ADC AL,[BX+SI] 0B76:0100 1300 ADC AX,[BX+SI] 0B76:0100 1400 ADC AL,00 0B76:0100 150000 ADC AX,0000 0B76:0100 16 PUSH SS 0B76:0100 17 POP SS 0B76:0100 1800 SBB [BX+SI],AL 0B76:0100 1900 SBB [BX+SI],AX 0B76:0100 1A00 SBB AL,[BX+SI] 0B76:0100 1B00 SBB AX,[BX+SI] 0B76:0100 1C00 SBB AL,00 0B76:0100 1D0000 SBB AX,0000 0B76:0100 1E PUSH DS 0B76:0100 1F POP DS 0B76:0100 2000 AND [BX+SI],AL 0B76:0100 2100 AND [BX+SI],AX 0B76:0100 2200 AND AL,[BX+SI] 0B76:0100 2300 AND AX,[BX+SI] 0B76:0100 2400 AND AL,00 0B76:0100 250000 AND AX,0000

基于中颖SH79F081的电动自行车控制器设计 摘要:方波驱动的无刷直流电机由于力矩大, 运行可靠, 在电动车控制器中广泛应用, 方波驱动最大的缺点在于换相时的电流突变引起的转矩脉动, 导致噪声较大, 但好的控制策略可以大大改善换相噪声. 电动车控制器设计的难点在于电流控制, 本文就电动车控制器设计的一些关键地方加以描述. 关键词:电动车控制器直流无刷电机换相同步整流 概述 电动自行车上使用的电机普遍采用永磁直流电机. 所谓永磁电机, 是指电机线圈采用永磁体激磁, 不采用线圈激磁的方式. 这样就省去了激磁线圈工作时消耗的电能, 提高了电机机电转换效率, 这对使用车载有限能源的电动车来讲, 可以降低行驶电流, 延长续行里程. 永磁直流电机按照电机的通电形式来分, 可分为有刷电机和无刷电机两大类, 有刷电机由于采用机械换相装置导致可靠性和寿命降低, 因此逐渐退出电动车市场. 无刷电机又可分为有传感器和无传感器两类, 对于无位置传感器的无刷电机, 必须要先将车用脚蹬起来, 等电机具有一定的旋转速度以后, 控制器才能识别到无刷电机的相位, 然后控制器才能对电机供电. 由于无位置传感器无刷电机不能实现零速度启动, 所以现在生产的电动车上用得较少. 目前电动车行业内使用的无刷电机, 普遍采用有位置传感器无刷电机. 有位置传感器永磁直流无刷电机按照内部传感器的安装位置不同, 又可分为60度电机和120度电机. 在120°的霍尔信号中, 不可能出现二进制000和111的编码,

所以在一定程度上避免了因霍尔零件故障而导致的误操作. 因为霍尔组件是开漏输出, 高电平依靠电路上的上拉电阻提供, 一旦霍尔零件断电, 霍尔信号输出就是111. 一旦霍尔零件短路, 霍尔信号输出就是000, 而60°的霍尔信号在正常工作时这两种信号均会出现, 所以一定程度上影响了软件判断故障的准确率. 因此目前市面马达已经逐渐舍弃60°相位的霍尔排列. 2. 永磁直流电机基本原理 2.1. 主回路电路 1.

倒立摆系统的控制器设计

摘 要 倒立摆是一种典型的非线性,多变量,强耦合,不稳定系统,许多抽象的控制概念如系统的稳定性、可控性、系统的抗干扰能力等都可以通过倒立摆直观的反应出来;倒立摆的控制思想在实际中如实验、教学、科研中也得到广泛的应用;在火箭飞行姿态的控制、人工智能、机器人站立与行走等领域有广阔的开发和利用前景。因此,对倒立摆系统的研究具有十分重要的理论和实践意义。 本文首先将直线倒立摆抽象为简单的模型以便于受力分析进行机理建模,然后通过牛顿力学原理进行分析,得出相应的模型,进行拉氏变化带入相应参数得出摆杆角度和小车位移、摆杆角度和小车加速度、摆杆角度和小车所受外界作用力、小车位移与小车所受外界作用力的传递函数,其中摆杆角度和小车加速度之间的传递函数为: 02()0.02725()()0.01021250.26705s G s V s s Φ==- ………… (1) 即我们在本次设计中主要分析的系统的传递函数。 然后从时域角度着手,分析直线一级倒立摆的开环单位阶跃响应和单位脉冲响应,利用Matlab 中的Simulink 仿真工具进行仿真,得出结论该系统的开环响应是发

散的。 最后分别利用根轨迹分析法,频域分析法和PID 控制法对倒立摆系统进行校正。 针对目标一:调整时间0.5(2%)s t s =误差带,最大超调量%10%≤p σ,选取参数利用根轨迹法进行校正,得出利用超前校正环节的传递函数为: 135.1547( 5.0887) ()135.1547c s G s s +=+ ………………………… (2) 针对目标二:系统的静态位置误差常数为10;相位裕量为 50 ;增益裕量等于或大于10 分贝。通过频域法得出利用超前校正环节的传递函数为: 1189.6(8.15) ()99.01c s G s s +=+ …………………………… ……………………(3) 针对目标三: 调整时间误差带)%2(2s t s =,最大超调量,%15%≤p σ,设计或调整PID 控制器参数,得出调整后的传递函数为: 150()21020c G s s s =++ ………………………………………. .(4)

实验一Cache模拟器的实现 一.实验目的 (1)加深对Cache的基本概念、基本组织结构以及基本工作原理的理解。 (2)掌握Cache容量、相联度、块大小对Cache性能的影响。 (3)掌握降低Cache不命中率的各种方法以及这些方法对提高Cache性能的好处。 (4)理解LRU与随机法的基本思想以及它们对Cache性能的影响。 二、实验内容和步骤 1、启动Cachesim 2.根据课本上的相关知识,进一步熟悉Cache的概念和工作机制。 Cache概念:高速缓冲存 Cache工作机制:大容量主存一般采用DRAM,相对SRAM速度慢,而SRAM速度快,但价格高。程序和数据具有局限性,即在一个较短的时间内,程序或数据往往集中在很小的存储器地址范围内。因此,在主存和CPU之间可设置一个速度很快而容量相对较小的存储器,在其中存放CPU当前正在使用以及一个较短的时间内将要使用的程序和数据,这样,可大大加快CPU访问存储器的速度,提高机器的运行效率 3、依次输入以下参数:Cache容量、块容量、映射方式、替换策略和写策略。Cache容量块容量映射方式替换策略写策略 8 32 全相联映射先进先出算法写回法(1)Cache容量: 启动CacheSim,提示请输入Cache容量,例如1、2、4、8......。此处选择输入4。 (2)块容量: 如下图所示,提示输入块容量,例如1、2、4、8......。此处选择输入16。

(3)映射方式: 如下图所示,提示输入主存储器和高速缓存之间的assoiativity方法(主存地址到Cache地址之间的映射方式),1代表直接映射(固定的映射关系)、2代表组相联映射(直接映射与全相联映射的折中)、3代表全相联映射(灵活性大的映射关系)。此处选择全相联映射。 (4)替换策略: 如下图所示,提示输入替换策略,1代表先进先出(First-In-First-Out,FIFO)算法、2代表近期最少使用(Least Recently Used,LRU)算法、3代表最不经常使用(Least Frequently Used,LFU)、4代表随机法(Random)。此处选择先进先出。 (5)写策略: 如下图所示,提示输入Cache的读写操作,1代表写直达法(存直达法)即写操作时数据既写入Cache又写入主存、2代表写回法(拷回法)即写操作时只把数据写入Cache而不写入主存,但当Cache数据被替换出去时才写回主存。

杭电计组实验1-全加器设计实验 杭州电子科技大学计算机学院实验报告实验项目:实验1-全加器设计实验课程名称:计算机组成原理与系统结构课程设计姓名: 学号: 同组姓名: 学号: 实验位置(机号): 自己的笔记本实验日期: 指导教师: 实验内容(算法、程序、步骤和方法)一、实验目的(1),学习ISE工具软件的使用及仿真方法(2)学习FPGA程序的下载方法(3)熟悉Nexys3实验板(4)掌握运用VerilogHDL进行结构描述与建模的技巧和方法(5)掌握二进制全加器的原理和设计方法二、实验仪器ISE工具软件三、步骤、方法(1)启动XilinxISE 软件,选择File-NewProject,输入工程名,默认选择后,点击Next按钮,确认工程信息后点击Finish按钮,创建一个完整的工程。 (2)在工程管理区的任意位置右击,选择NewSource命令。弹出NewSourceWizard对话框,选择VerilogModule,并输入Verilog文件名shiyan1,点击Next按钮进入下一步,点击Finish完成创建。 (3)编辑程序源代码,然后编译,综合;选择Synthesize--XST项中的CheckSyntax右击选择Run命令,并查看RTL视图;如果编译出错,则需要修改程序代码,直至正确。 (4)在工程管理区将View类型设置成Simulation,在任意位置右击,选择NewSource命令,选择VerilogTestFixture选项。输入文件名shiyan1_test,点击Next,点击Finish,完成。编写激励代码,观察仿真波形,如果验证逻辑有误,则修改代码,重新编译,仿真,直至正确。 (5)由于实验一并未链接实验板,所以后面的链接实验板的步骤此处没有。 操作过程及结果一、操作过程实验过程和描述: moduleshiyan1(A,B,C,F,Ci);inputA,B,C;outputF,Ci;wireA,B,C,F,Ci;wi reS1,S2,S3;xorXU1(F,A,B,C),XU2(S1,A,B);andAU1(S2,A,B),AU2(S3,S1,C);or OU1(Ci,S2,S3);endmodule仿真代码 moduleshiyan1_test;//InputsregA;regB;regC;//OutputswireF;wireCi;/ /InstantiatetheUnitUnderTest(UUT)shiyan1uut(.A(A),.B(B),.C(C),.F(F),. Ci(Ci));initialbegin//InitializeInputsA=0;B=0;C=0;//Wait100nsforgloba lresettofinish#100;//AddstimulushereA=0;B=0;C=0;#100A=0;B=0;C=1;#100A =0;B=1;C=0;#100A=0;B=1;C=1;#100A=1;B=0;C=0;#100A=1;B=0;C=1;#100A=1;B= 1;C=0;#100A=1;B=1;C=1;EndRTL图 二、结果 思考题: ((1)根据查看顶层模块RTL的最外层的输入输出接口,和实验指导书式(14.1)所示电路相比,该电路图的输入输出引脚和这个加法器的引脚图式是相符合的。 ((2))尝试使用数据流描述方式现实现

实验一Cache模拟器得实现 一、实验目得 (1)加深对Cache得基本概念、基本组织结构以及基本工作原理得理解。 (2)掌握Cache容量、相联度、块大小对Cache性能得影响。 (3)掌握降低Cache不命中率得各种方法以及这些方法对提高Cache性能得好处。 (4)理解LRU与随机法得基本思想以及它们对Cache性能得影响. 二、实验内容与步骤 1、启动Cachesim 2、根据课本上得相关知识,进一步熟悉Cache得概念与工作机制。 Cache概念:高速缓冲存 Cache工作机制:大容量主存一般采用DRAM,相对SRAM速度慢,而SRAM速度快,但价格高。程序与数据具有局限性,即在一个较短得时间内,程序或数据往往集中在很小得存储器地址范围内。因此,在主存与CPU之间可设置一个速度很快而容量相对较小得存储器,在其中存放CPU当前正在使用以及一个较短得时间内将要使用得程序与数据,这样,可大大加快CPU访问存储器得速度,提高机器得运行效率 3、依次输入以下参数:Cache容量、块容量、映射方式、替换策略与写策略. (1)Cache容量: 启动CacheSim,提示请输入Cache容量,例如1、2、4、8、、、、、、。此处选择输入4。 (2)块容量: 如下图所示,提示输入块容量,例如1、2、4、8、、、、、、。此处选择输入16。 (3)映射方式: 如下图所示,提示输入主存储器与高速缓存之间得assoiativity方法

(主存地址到Cache地址之间得映射方式),1代表直接映射(固定得映射关系)、2代表组相联映射(直接映射与全相联映射得折中)、3代表全相联映射(灵活性大得映射关系)。此处选择全相联映射。 (4)替换策略: 如下图所示,提示输入替换策略,1代表先进先出(First-In—First—Out,FIFO)算法、2代表近期最少使用(Least RecentlyUsed,LRU)算法、3代表最不经常使用(Least Frequently Used,LFU)、4代表随机法(Random)。此处选择先进 先出. (5)写策略: 如下图所示,提示输入Cache得读写操作,1代表写直达法(存直达法)即写操作时数据既写入Cache又写入主存、2代表写回法(拷回法)即写操作时只把数据写入Cache而不写入主存,但当Cache数据被替换出去时才写回主存。此处选写回法

纯电动汽车整车控制器的设计 发表时间:2019-07-05T11:27:03.790Z 来源:《电力设备》2019年第4期作者:王坚 [导读] 摘要:随着社会的发展与科技的进步,各个城市的汽车使用户喷井式增加。 (柳州五菱汽车工业有限公司广西柳州 545007) 摘要:随着社会的发展与科技的进步,各个城市的汽车使用户喷井式增加。传统的内燃机汽车消耗石油,排出大量废气,使得城市的空气质量不断下降。纯电动汽车由于不使用传统化石能源,对环境不造成污染,受到人们的青睐。随着科技的进步,电动汽车的核心技术不断地革新与突破,逐渐完善的城市基础设施提供了有利的帮助,电动汽车已经成为潜力股,逐步取代传统汽车变为可能。本文从汽车结构出发,结合整车信息传输过程,设计了整车控制器的软硬件结构。 关键词:纯电动汽车;整车控制器;硬件设计;软件设计 纯电动汽车作为新能源汽车的一种,以其清洁无污染、驱动能源多样化、能量效率高等优点成为现代汽车的发展趋势。整车控制器(vehicle control unit,VCU)作为纯电动汽车整车控制系统的中心枢纽,主要实现数据采集和处理、控制信息传递、整车能量管理、上下电控制、车辆部件控制和错误诊断及处理、车辆安全监控等功能。国外在纯电动汽车整车控制器的产品开发中,积极推行整车控制系统架构的标准化和统一化,汽车零部件厂商提供硬件电路和底层驱动软件,整车厂只需要开发核心应用软件,有利的推动了整车行业的快速发展。虽然国内各大汽车厂商基本掌握了整车控制器的设计方案,开发技术进步明显,但是对核心电子元器件、开发环境的严重依赖,所以导致了整车控制器的国产化水平较低。本文以复合电源纯电动汽车作为研究对象,针对电动汽车应有的结构和特性,对整车控制器的设计和开发展开研究。 一、整车控制系统分析与设计 (一)整车控制系统分析 复合电源纯电动汽车整车控制系统主要由整车控制器、能量管理系统、整车通信网络以及车载信息显示系统等组成。首先纯电动汽车整车控制器通过采集启动、踏板等传感器信号以及与电机控制器、能量管理系统等进行实时的信息交互,获取整车的实时数据,然后整车控制器通过所有当前数据对驾驶员意图和车辆行驶状态进行判断,从而进入不同的工况与运行模式,对电机控制系统或制动系统发出操控命令,并接受各子控制器做出的反馈。 保障纯电动汽车安全可靠运行,并对各个子控制器进行控制管理的整车控制器,属于纯电动汽车整车控制系统的核心设备。整车控制器实时地接收传感器传输的数据和驾驶操作指令,依照给定的控制策略做出工况与模式的判断,实现实时监控车辆运行状态及参数或者控制车辆的上下电,以整车控制器为中心通信节点的整车通信网络,实现了数据快速、可靠的传递。 (二)整车控制系统设计 复合电源的结构设计,选择了超级电容与DC/DC串联的结构,双向DC/DC跟踪动力电池电压来调整超级电容电压,使两者电压相匹配。为了车辆驾驶运行安全,同时为了更好地使超级电容吸收纯电动汽车的再生制动能量,在复合电源系统中动力电池与一组由IGBT组成双向可控开关,防止了纯电动汽车处于再生制动状态时,动力电池继续供电,降低再生制动能量的吸收效率。 整车CAN通信网络设计,由整车控制器(VCU)、电机控制器(motor control unit,MCU)、电池管理系统(battery management system,BMS)、双向DC/DC控制器以及汽车组合仪表等控制单元(Electronic Control Unit,ECU)组成了复合电源纯电动汽车的整车通信网络。 二、整车控制器硬件设计及软件设计 (一)整车控制器结构设计 整车控制器的硬件结构根据其基本的功能需求进行设计,如图1所示。支持芯片正常工作的微控制器最小系统是整车控制器的核心,基础的信号处理模块,CAN通信与串口通信组成的通信接口模块,以及LCD显示等其他模块分别作为它的各大功能模块。 图1 整车控制器硬件结构图 (二)整车控制器硬件设计 从功能上可以把整车控制器分为6个模块。 1)微控制器模块:本设计选用美国德州仪器公司TI的数字信号处理芯片TMS320F2812为主控芯片,负责数据的运算及处理,控制方法的实现,是整车控制器的控制核心。此芯片运算速度快,控制精度高的特点基本满足了整车控制器的设计需求。TMS320F2812的最小系统主要由DSP主控芯片、晶振电路、电源电路以及复位电路组成。 2)辅助电源模块:由于整车控制器的控制系统中用到多种芯片,所以需要设计辅助电源电路为各个芯片提供电源,使其正常工作,因此输出电平有多种规格。采用芯片LM317、LM337可分别产生+5V和-5V的供电电压。 3)信号调理模块:输入整车控制器的踏板信号是1~4.2V模拟电压信号,TMS320F2812的12位16通道的A/D采样模块输入的信号范围为0~3.0V,因此需要对踏板输入的模拟电压信号进行相应的调理运算,以满足DSP的A/D采样电平要求。选用德州仪器的OPA4350轨至轨运算放大器,在输入级采用RC低通滤波电路与电压跟随电路以滤除干扰信号,减小输入的模拟信号失真。开关信号先经RC低通滤波电路滤除高频干扰,再作为电压比较器LM393的正端输入,电压比较器的负端输入接分压电路,将LM393的输出引脚外接光耦芯片,在起到电平转换作用的同时,进一步隔离干扰信号,提高信号的安全性与可靠性。 4)通讯模块:TMS320F2812具有一个eCAN模块,支持CAN2.0B协议,可以实现CAN网络的通讯,但是其仅作为CAN控制器使用。选用3.3V单电源供电运行的CAN发送接收器SN65HVD232D,其兼容TMS320F2812的引脚电平,用于数据速率高达1兆比特每秒(Mbps)的应

控制系统课程设计---直线一级倒立摆控制器设计

H a r b i n I n s t i t u t e o f T e c h n o l o g y 课程设计说明书(论文) 课程名称:控制系统设计课程设计 设计题目:直线一级倒立摆控制器设计 院系: 班级: 设计者: 学号: 指导教师:罗晶周乃馨 设计时间:2013.9.2——2013.9.13

哈尔滨工业大学课程设计任务书 姓名:院(系):英才学院 专业:班号: 任务起至日期:2013 年9 月 2 日至2013 年9 月13 日 课程设计题目:直线一级倒立摆控制器设计 已知技术参数和设计要求: 本课程设计的被控对象采用固高公司的直线一级倒立摆系统GIP-100-L。 系统内部各相关参数为: M小车质量0.5 Kg ;m摆杆质量0.2 Kg ;b小车摩擦系数0.1 N/m/sec ;l摆杆转动轴心到杆质心的长度0.3 m ;I摆杆惯量0.006 kg*m*m ;T采样时间0.005 秒。 设计要求: 1.推导出系统的传递函数和状态空间方程。用Matlab 进行阶跃输入仿真,验证系统的稳定性。 2.设计PID控制器,使得当在小车上施加0.1N的脉冲信号时,闭环系统的响应指标为: (1)稳定时间小于5秒;

(2)稳态时摆杆与垂直方向的夹角变化小于0.1 弧度。 3.设计状态空间极点配置控制器,使得当在小车上施加0.2m的阶跃信号时,闭环系统的响应指标为:(1)摆杆角度θ和小车位移x的稳定时间小于3秒 (2)x的上升时间小于1秒 (3)θ的超调量小于20度(0.35弧度) (4)稳态误差小于2%。 工作量: 1. 建立直线一级倒立摆的线性化数学模型; 2. 倒立摆系统的PID控制器设计、MATLAB仿真及 实物调试; 3. 倒立摆系统的极点配置控制器设计、MATLAB仿 真及实物调试。

汕头大学实验报告 学院: 工学院系: 计算机系专业: 计算机科学与技术年级: 13实验时间: 2015.6.16 姓名: 林子伦学号: 2013101030实验名称:基于SPIM-CACHE的Cache实验 一.实验目的: (1)熟悉SPIM-CACHE模拟器环境 (2)深入认识CACHE的工作原理及其作用。 二.实验内容: (1)阅读实验指导书资料(虚拟教室提供了英文论文的电子版本); (2)下载SPIM-CACHE软件,理解英文论文的基本内容之后,给出几种典型的cache配置,运行英文论文提供的代码,记录运行时CACHE命中率等重要数据;(3)运行Fig.4代码,了解mapping functions 即映射规则 (4)运行Fig.7代码,了解temporal and spatial locality 即时空局部性,进一步理解cache的工作原理; (5)运行Fig.8代码,运行学习replacement algorithms 即替代算法,理解其工作原理。 三.实验地点,环境 实验地点:软件工程实验室 实验环境: 操作系统:Microsoft Windows 8 中文版 处理器:Intel(R) Core(TM) i3-3120M CPU @ 2.50GHz 2.50GHz 内存: 4.00GB(3.82GB 可用) 四.实验记录及实验分析(80%): 4.1实验前配置: 1) 按下图配置好Spim设置

2)关于实验中cache设置如下(具体配置根据下面实验要求) ——》 ——》 Cache size ——cache大小 Block size ——块大小 Mapping ——组相连 4.2实验一:fig4.s 实验目的:Algorithm and corresponding code to study mapping functions Cache配置:256-B size, 16-B line size, four-way set associative 实验操作: 1) Ctrl+O 打开运行代码fig4.s 代码如下: .data 0x10000480 Array_A: .word 1,1,1,1,2,2,2,2 .data 0x10000CC0 Array_B: .word 3,3,3,3,4,4,4,4 .text .globl _start _start: la $2,Array_A li $6,0 li $4,8 loop: lw $5,0($2) add $6,$6,$5 addi $2,$2,4

计算机科学与技术系 实验报告 专业名称计算机科学与技术 课程名称计算机组成原理 项目名称静态随机存储器实验 班级 学号 姓名 同组人员无 实验日期 2016.5.10

一、实验目的与要求 (一)实验目的: 掌握静态随机存储RAM工作特性及数据的读写方法 实验要求: 1.实验之前,应认真准备,写出实验步骤和具体设计内容,否则实验效率会很低,一次实验时间根本无法完成实验任务; 2.应在实验前掌握所以控制信号的作用,写出实验预习报告并带入实验室; 3.实验过程中,应认真进行实验操作,既不要因为粗心造成短路等事故而损坏设备,又要自习思考实验有关内容; 4.实验之后,应认真思考总结,写出实验报告,包括实验步骤和具体实验结果,遇到的问题和分析与解决思路。还应写出自己的心得体会,也可以对教学实验提出新的建议等。实验报告要上交老师。 二、实验逻辑原理图与分析 2.1 画实验逻辑原理图 D7 - - - - - - - - - - - - - -D0 O E C S D7- - - - - - - - - - - - - - D0 R D A10—A8 A7- - - - - - - - - - - - -A0 WE 读写译码 74LS273 74LS245 IN单元AD7 | AD0

2.2 逻辑原理图分析 1、存储器数据线接至数据总线,数据总线上接有8个LED 灯显示D7—D0 的内容。地址线接至地址总线,地址总线上接有8 个LED 灯显示A7—A0 的内容,地址由地址锁存器(74LS273,位于PC&AR单元)给出。 2、数据开关(位于IN单元)经一个三态门(74LS245)连至数据总线,分时给出地址和数据。地址寄存器为8位,接入6116的地址A7—A0,6116 的高三位地址A10—A8 接地,所以其实际容量为256 字节。 3、实验箱中所有单元的时序都连接至时序控制台操作,CRL都连接至CON 按钮。实验时T3由时序单元给出,其余信号由CON单元的二进制开关模拟给出,其中,IOM应为低,RD、WR高有效,MR、MW低有效,LDAR高有效。 三、数据通路图及分析(画出数据通路图并作出分析) 数据总线 ×××××××× OE# CE# ××××××××WR# MEM单元 A1 A8 ××××××××RD# ×××××××× AR单元 ≥1 ×××××××× IN单元