计算机组成原理实验三

堆栈寄存器实验

一、实验目的:

1、熟悉堆栈概念。

2、熟悉堆栈寄存器的组成和硬件电路。

二、实验要求:

完成3个堆栈寄存器的数据写入与读出。

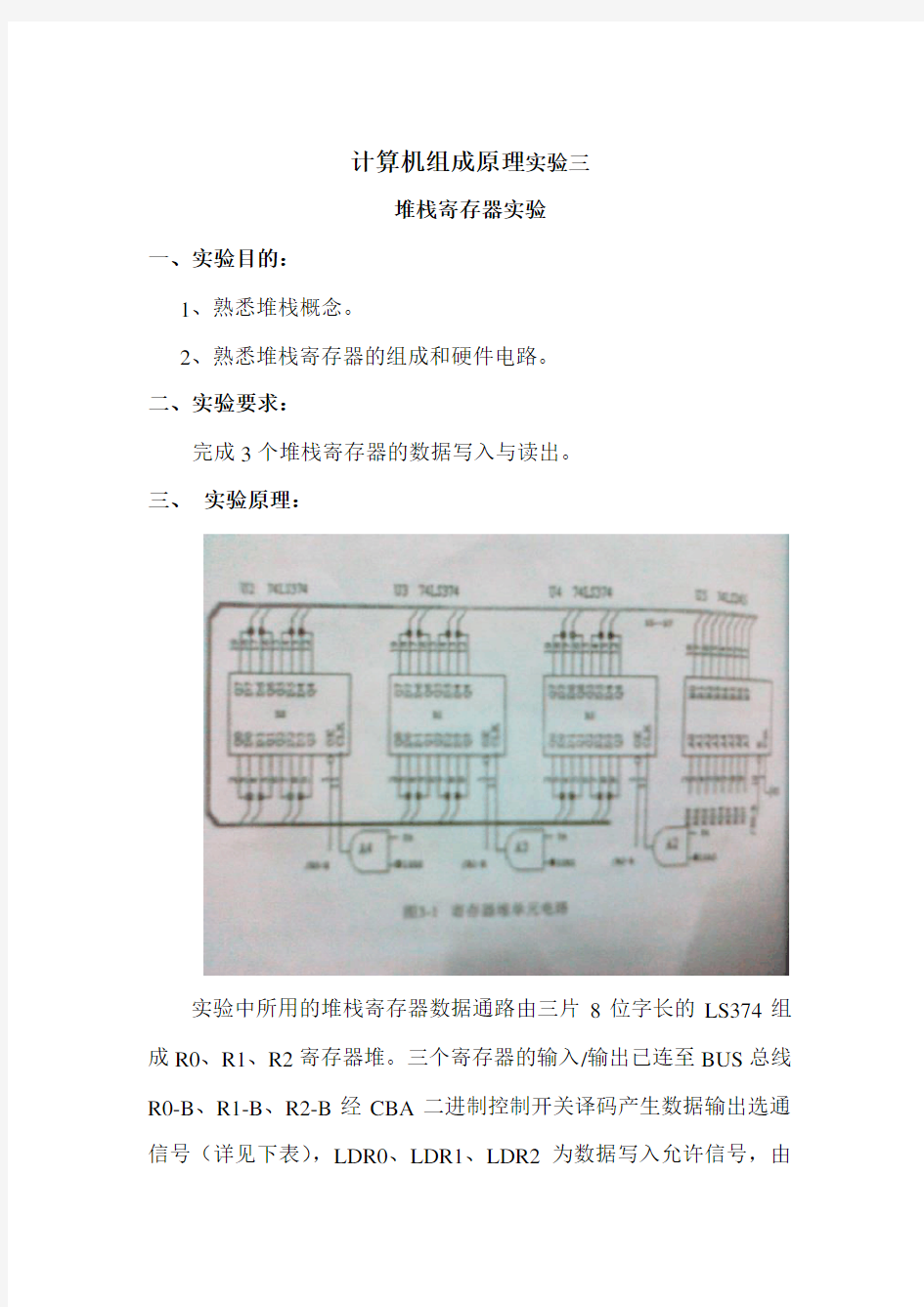

三、实验原理:

实验中所用的堆栈寄存器数据通路由三片8位字长的LS374组成R0、R1、R2寄存器堆。三个寄存器的输入/输出已连至BUS总线R0-B、R1-B、R2-B经CBA二进制控制开关译码产生数据输出选通信号(详见下表),LDR0、LDR1、LDR2为数据写入允许信号,由

二进制控制开关来模拟,均为高电平有效;T4信号为寄存器数据写入脉冲,上升沿有效。在手动实验状态(即“H”装态)每按动一次“单步”命令键,产生一个T4信号。

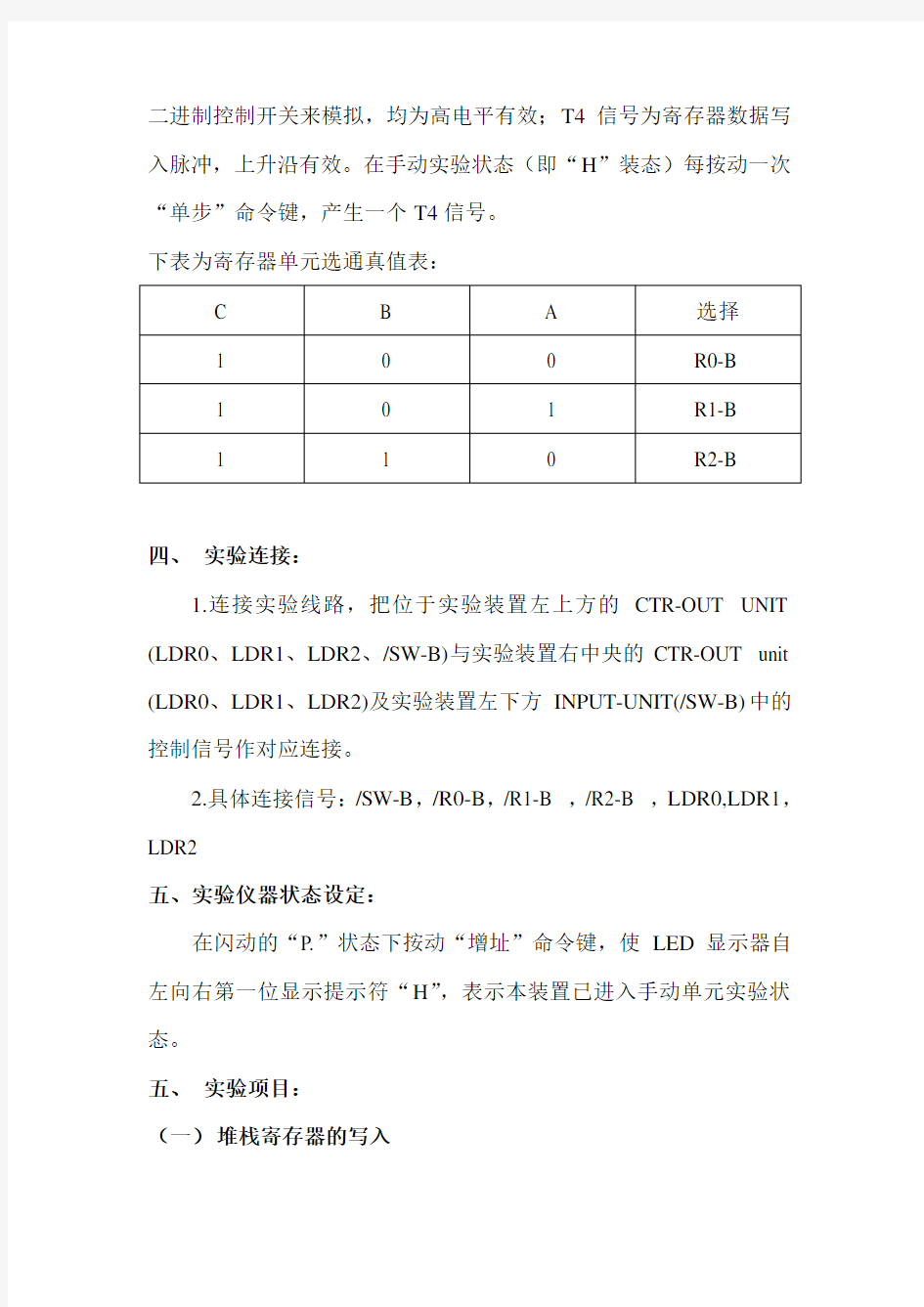

下表为寄存器单元选通真值表:

C B A 选择

1 0 0 R0-B

1 0 1 R1-B

1 1 0 R2-B

四、实验连接:

1.连接实验线路,把位于实验装置左上方的CTR-OUT UNIT (LDR0、LDR1、LDR2、/SW-B)与实验装置右中央的CTR-OUT unit (LDR0、LDR1、LDR2)及实验装置左下方INPUT-UNIT(/SW-B)中的控制信号作对应连接。

2.具体连接信号:/SW-B,/R0-B,/R1-B ,/R2-B ,LDR0,LDR1,LDR2

五、实验仪器状态设定:

在闪动的“P.”状态下按动“增址”命令键,使LED显示器自左向右第一位显示提示符“H”,表示本装置已进入手动单元实验状态。

五、实验项目:

(一)堆栈寄存器的写入

拨动二进制数据开关(INPUT-UNIT )向R0和R1寄存器置数(置数灯亮表示它所对应的数据位为“1”、反之为“0”)。具体操作步骤图示如下:

六、

七、

八、

[CBA=001] [LDR0=1] [LDR=1] [LDR1=0] [LDR1=1] [LDR2=0] [LDR2=0] [按“STEP ”] [按“STEP ”]

(二)堆栈寄存器的读出

关闭数据输入三态门(CBA=000),分别打开通用寄存器R0、R1、R2输出控制位,当CBA=100时,总线指示灯(BUS-DISP UNIT )显示R0中的数据01H ;当CBA=101时,总线指示灯显示R1中的数据80H ;当CBA=110时,总线指示灯显示R2中等的数据(随机),可以观察到,显示的随机数为11111111. (六)实验总结

通过本次实验的数据和理论分析进行比较、验证,我们熟悉了堆栈概念,熟悉了堆栈寄存器的组成和硬件电路等。

数据开关

(00000001)

三态门

寄存器R0 (00000001)

置数开关 (10000000)

寄存器R1 (10000000)

寄存器实验报告

一、实验目的 1. 了解寄存器的分类方法,掌握各种寄存器的工作原理; 2. 学习使用V erilog HDL 语言设计两种类型的寄存器。 二、实验设备 PC 微机一台,TD-EDA 实验箱一台,SOPC 开发板一块。 三、实验内容 寄存器中二进制数的位可以用两种方式移入或移出寄存器。第一种方法是以串行的方式将数据每次移动一位,这种方法称之为串行移位(Serial Shifting),线路较少,但耗费时间较多。第二种方法是以并行的方式将数据同时移动,这种方法称之为并行移位(Parallel Shifting),线路较为复杂,但是数据传送的速度较快。因此,按照数据进出移位寄存器的方式,可以将移位寄存器分为四种类型:串行输入串行输出移位寄存器(Serial In- Serial Out)、串行输入并行输出移位寄存器(Serial In- Parallel Out)、并行输入串行输出移位寄存器(Parallel In- Serial Out)、并行输入并行输出移位寄存器(Parallel In-Parallel Out)。 本实验使用V erilog HDL 语言设计一个八位并行输入串行输出右移移位寄存器(Parallel In- Serial Out)和一个八位串行输入并行输出寄存器(Serial In- Parallel Out),分别进行仿真、引脚分配并下载到电路板进行功能验证。 四、实验步骤 1.并行输入串行输出移位寄存器实验步骤 1). 运行Quartus II 软件,选择File New Project Wizard 菜单,工程名称及顶层文件名称为SHIFT8R,器件设置对话框中选择Cyclone 系列EP1C6Q240C8 芯片,建立新工程。 2.) 选择File New 菜单,创建V erilog HDL 描述语言设计文件,打开文本编辑器界面。 3.) 在文本编辑器界面中编写V erilog HDL 程序,源程序如下: module SHFIT8R(din,r_st,clk,load,dout); input [7:0]din; input clk,r_st,load; output dout; reg dout; reg [7:0]tmp; always @(posedge clk) if(!r_st) begin dout<=0; end else begin if(load) begin tmp=din; end else

电子通信与软件工程 系2013-2014学年第2学期 《数字电路与逻辑设计实验》实验报告 --------------------------------------------------------------------------------------------------------------------- 班级: 姓名: 学号: 成绩: 同组成员: 姓名: 学号: --------------------------------------------------------------------------------------------------------------------- 一、 实验名称:集成计数器及寄存器的运用 二、实验目的: 1、熟悉集成计数器逻辑功能与各控制端作用。 2、掌握计数器使用方法。 三、 实验内容及步骤: 1、集成计数器74LS90功能测试。74LS90就是二一五一十进制异步计数器。逻辑简图为图8、1所示。 四、 五、 图8、1 六、 74LS90具有下述功能: ·直接置0(1)0(2)0(.1)R R ,直接置9(S9(1,·S,.:,=1) ·二进制计数(CP 、输入QA 输出) ·五进制计数(CP 2输入Q D Q C Q B 箱出) ·十进制计数(两种接法如图8.2A 、B 所示) ·按芯片引脚图分别测试上述功能,并填入表 8、1、表8、2、表8、3中。

图8、2 十进制计数器 2、计数器级连 分别用2片74LS90计数器级连成二一五混合进制、十进制计数器。 3、任意进制计数器设计方法 采用脉冲反馈法(称复位法或置位法)。可用74LS90组成任意模(M)计数器。图8、3就是用74LS90实现模7计数器的两种方案,图(A)采用复位法。即计数计到M异步清0。图(B)采用置位法,即计数计到M一1异步置0。 图8、3 74LS90 实现七进进制计数方法 (1)按图8、3接线,进行验证。 (2)设计一个九进制计数器并接线验证。 (3)记录上述实验的同步波形图。 四、实验结果:

实验四典型时序电路的功能测试与综合仿真报告 15291204张智博一.74LS290构成的24位计数器 方法:第一片74290的Q3与第二片的INB相连,R01,R02相连,INA,R91,R92悬空构成24位计数器。50Hz,5v方波电压源提供时钟信号,用白炽灯显示输出信号。 实验电路: 实验现象:

输出由000000变为000001,000010,000011,000100,001000,001001,001010,001011,001100,010001,010000,010010,010011,010100,011000,011001,011010,011011,011100,100000,100001,100010,100011,100100,最终又回到000000,实现一次进位。 二.74LS161构成的24位计数器 方法:运用多次置零法 用两片74LS161构成了24位计数器,两片计数器的时钟信号都由方波电压源提供,第一片芯片的Q3和第二片芯片的Q0通过与非门,构成两个74LS161的LOAD信号,第一片的CO接第二片的ENT,其他ENT和ENP接Vcc(5v)。输出接白炽灯。 电路图: 实验现象:以下为1—24的计数过程

三.74LS194构成的8位双向移位寄存器 方法:通过两片194级联,控制MA,MB的值,来控制左右移动 实验电路由两片74LS194芯片构成。两个Ma接在一起,两个Mb接在一起,第一片的Dr,第二片的Dl,分别通过开关接到Vcc(5v)上。第一片的Q3接到第二片的Dr,第二片的Q0接到第一片的Dl。8个输出端分别接白炽灯。 实验电路:

计算机原理与设计 实验报告 实验三多周期MIPS CPU的控制部件用有限状态机实现多周期CPU的控制部 件

一.实验目的 1、了解MIPS—CPU控制器的功能和工作原理; 2、掌握用有限状态机技术实现多周期控制器的方法; 3、熟练掌握用Verilog HDL语言设计多周期控制器的方法; 4、熟练掌握对多周期控制器的仿真实验验证和硬件测试两种调试方法; 5、掌握向MIPS-CPU顶层数据通路中增加控制单元的方法,并通过仿真验证和硬件测试两种方法对电路进行故障定位的调试技术。 二.实验内容 (1)MIPS—CPU控制器的有限状态机设计,根据MIPS—CPU 各种类型指令执行要求和有限状态机的设计原理,将多周期控制器的指令执行划分为多个状态,确定每一种指令的有限状态机,最后归纳为完整的多周期控制器有限状态机。通过Verilog HDL语言实现多周期控制器有限状态机。 (2)根据MIPS—CPU控制器的接口要求,在有限状态机的

基础上,用Verilog HDL实现完整的MIPS—CPU控制器的设计,并根据仿真波形,验证设计的正确性,并对出现的故障进行定位,修改程序,重新编译; (3)设计控制器的硬件下载测试方案。将编译通过的电路下载到实验台中。根据硬件调试结果验证设计的正确性,并对出现的故障进行定位,修改程序重新编译;最终完成控制器的硬件电路设计; (4)在MIPS—CPU指令系统的数据通路基础上,增加控制单元电路,并进行编译,仿真波形和调试。根据仿真波形,验证设计的正确性,并对出现的故障进行定位,修改程序,重新编译; (5)对增加了控制单元的顶层数据通路设计硬件下载测试方案。将编译通过的电路下载到实验台中。根据硬件调试结果验证设计的正确性,并对出现的故障进行定位,修改程序,重新编译;最终完成增加了控制单元的顶层数据通路设计。三.实验原理与步骤 1.把指令执行分成多个阶段,每个阶段在一个时钟周期内完成 (1).时钟周期以最复杂阶段所花时间为准 (2).尽量分成大致相等的若干阶段 (3).每个阶段内最多只能完成:1次访存或1次寄存器堆读/写或1次ALU

寄存器组的设计与实现 第______ _________组 成员___ ____ ____ 实验日期___ _____ _____ 实验报告完成日期___________ 1、实验目的 1、学习掌握Quartus软件的基本操作; 2、理解寄存器组的工作原理和过程; 3、设计出寄存机组并对设计的正确性进行验证; 二、实验内容

1、设计出功能完善的寄存器组,并对设计的正确性进行验证。要求如下: (1)用图形方式设计出寄存器组的电路原理图 (2)测试波形时用时序仿真实现,先将不同的数据连续写入 4个寄存器后,再分别读出 (3)将设计文档封装成器件符号。 (4)数据的宽度最好是16位 2、能移位的暂存器实验,具体要求如下: (1)用图形方式设计出能移位的暂存器电路原理图,分别实 现左移、逻辑右移和算术右移。 (2)测试波形时要用时序仿真实现,测试数据不要全为0也 不要全为1,算术右移的测试数据要求为负数(即符号位为 1) (3)将设计文档封装成器件符号。 (4)数据的宽度最好是16位 三、能完善的寄存器组设计思想 1、对于寄存器组设计思路 利用具有三态功能的寄存器堆74670芯片进行设计,根据实验要求,需要设计16位的存储器组,则需要74670芯片4片,在寄存器组工作时,同时对4片74670芯片进行读写操作控制,封装后即可作为包含有4个寄存器的16位寄存器组在主机系统中调用。 2、对74670器件的学习 74670(三态输出4×4寄存器堆)提供4个4位的寄存器,在功能上可对4个寄存器去分别进行写操作和读操作。在寄存器进行写操作时,通过WB、WA两个寄存器选择端的组合和00、01、10、11、来选择寄存器,公国GWN写操作端控制进行三态控制,在GWN为低电平时将数据写入端数据D4D3D2D1写入该寄存器;在寄存

成绩:实验报告 课程名称:计算机组成原理 实验项目:寄存器的原理及操作 姓名: 专业:计算机科学与技术 班级: 学号:

计算机科学与技术学院 实验教学中心 20 16年6月20日

实验项目名称:寄存器的原理及操作 一、实验目的 1.了解模型机中 A, W 寄存器结构、工作原理及其控制方法。 2.了解模型机中寄存器组 R0..R3 结构、工作原理及其控制方法。 3.了解模型机中地址寄存器 MAR,堆栈寄存器 ST,输出寄存器 OUT寄存器结构、工作原理及其控 制方法。 二、实验内容 1、A、W寄存器:利用 COP2000实验仪上的K16..K23 开关做为DBUS的数据,其它开关做为控制信号, 将数据写入寄存器A, W。 2、R0、R1、R2、R3 寄存器实验:利用COP2000实验仪上的K16..K23 开关做为DBUS的数据,其它开 关做为控制信号,对数据寄存器组R0..R3 进行读写。 3、MAR、ST、OUT寄存器:利用COP2000实验仪上的K16..K23 开关做为DBUS的数据,其它开关做为 控制信号,将数据写入地址寄存器MAR,堆栈寄存器ST,输出寄存器OUT。 三、实验用设备仪器及材料 伟福 COP2000 系列计算机组成原理实验系统 四、实验原理及接线 实验 1:A,W 寄存器实验

实验 2 :R0,R1, R2,R3寄存器实验

MAR为存储器地址寄存器,其功能是存储操作数在内存中的地址,信号MAREN的功能是将数据总线DBUS上数据 MAR,信号 MAROE的功能是将MAR的值送到地址总线ABUS上 ST 堆栈寄存器的作用,是出现中断或子程序调用时,保存断点处PC 的值,以便中断或子程序结束时, 能继续执行原程序。图中,信号STEN的作用是将数据总线DBUS上数据存入堆栈寄存器ST 中

实验六移位寄存器的设计 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。 二、实验预习要求 1、复习有关寄存器及串行、并行转换器有关内容。 2、查阅CC40194、CC4011及CC4068 逻辑线路。熟悉其逻辑功能及引脚排列。 3、在对CC40194进行送数后,若要使输出端改成另外的数码,是否一定要使寄存器清零? 4、使寄存器清零,除采用R C输入低电平外,可否采用右移或左移的方法?可否使用并行送数法?若可行,如何进行操作? 5、若进行循环左移,图6-4接线应如何改接? 6、画出用两片CC40194构成的七位左移串 /并行转换器线路。 7、画出用两片CC40194构成的七位左移并 /串行转换器线路。 三、实验设备及器件 1、+5V直流电源 2、单次脉冲源 3、逻辑电平开关 4、逻辑电平显示器 5、CC40194×2(74LS194)CC4011(74LS00) CC4068(74LS30) 四、设计方法与参考资料 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图6-1所示。 其中D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串行输 C为直接无条件清零端; 入端,S L为左移串行输入端;S1、S0为操作模式控制端;R

杭州电子科技大学计算机学院 实验报告 实验项目: 课程名称:计算机组成原理与系统结构设计 姓名: 学号: 同组姓名: 学号 : 实 验 位 置 ( 机 号 ) : 实验日期: 指 导 教 师: 实验 内容 (算 法、 程 序、 步骤 和 方 法) 一、 实验目的 (1 )学会使用Verilog HDL 进行时序电路的设计方法。 (2)掌握灵活应用Verilog HDL 进行各种描述与建模的技巧和方法。 (3 )学习寄存器堆的数据传送与读 /写工作原理,掌握寄存器堆得设计方法。 二、 实验仪器 ISE 工具软件 三、 步骤、方法 (1) 启动Xilinx ISE 软件,选择File->New Project,输入工程名shiyan2,默认选择后,点 击Next 按钮,确认工程信息后点击 Finish 按钮,创建一个完整的工程。 (2) 在工程管理区的任意位置右击,选择 New Source 命令。弹出 New Source Wizard 对 话框, 选择Verilog Module,并输入Verilog 文件名,点击Next 按钮进入下一步, 点击Finish 完成创建。 (3) 编辑程序源代码,然后编译,综合;选择 Synthesize--XST 项中的Check Syntax 右击 选择 Run 命令,并查看RTL 视图;如果编译出错,则需要修改程序代码,直至正确。 (4) 在工程管理区将 View 类型设置成 Simulation ,在任意位置右击,选择 New Source 命 令,选择Verilog Test Fixture 选项。点击Next ,点击Finish ,完成。编写激励代码,观察仿 真波形,如果验证逻辑有误,则修改代码,重新编译,仿真,直至正确。 (5) 由于实验四并未链接实验板,所以后面的链接实验板的步骤此处没有。

实验四 译码器的设计及延迟估算 1、 设计译码器并估算延迟 设计一个用于16bit 寄存器堆的译码器,每一个寄存器有32bit 的宽度,每个bit 的寄存器单元形成的负载可以等效为3个单位化的晶体管(后面提到负载都为单位化后的负载)。 译码器的结构可参考典型的4-16译码器 译码器和寄存器堆的连接情况(Output 输出为1的一行寄存器被选中) ① 假定4个寄存器地址位的正反8个输入信号,每个信号的输入负载可以等效为10。确定 译码器的级数,并计算相关逻辑努力,以此来确定每一级中晶体管的尺寸(相当于多少个单位化的晶体管)及整个译码电路的延迟(以单位反相器的延迟的本征延迟Tp0为单位)。 解: 96332,10int =?==ext g C C C ,9.696/10F ==? 假定每一级的逻辑努力:G=1,又因为分支努力(每个信号连接8个与非门): 81*8*1B ==, 路径努力8.7686.91=??==GFB H 所以,使用最优锥形系数就可得到最佳的电路级数39.36.3ln 8.76ln 6.3ln ln ===H N ,故N 取3级。 因为逻辑努力:2121G =??=,路径努力:6.15386.92=??==GFB H 则使得路径延时最小的门努力 36.5)6.153(3/1===N H h 。 所以: . 36.5136.5,68.2236.5, 36.5136.5132211=========g h f g h f g h f

故第一级晶体管尺寸为7.68 1036.5=?; 第二级尺寸为956.1768.27.6=?; 第三级尺寸为96244.9636.5956.17≈=?。 故延迟为:0008.22)36.5136.5436.51(p p p t t t =+++++= ② 如果在四个寄存器地址输入的时候,只有正信号,反信号必须从正信号来获得。每个正信号的输入的等效负载为20,使用与①中同样的译码结构,在这种条件下确定晶体管的大小并评估延迟(以单位反相器的延迟的本征延迟Tp0为单位)。 解:因为输入时通过两级反相器,使这两个反相器分摊原来单个反相器的等效扇出,将两级反相器等效为一级,故其逻辑努力32.236.5h ==, 故36.5,68.2,32.2,32.24321====f f f f 所以: 第一级尺寸为:()9.2832.210=?; 第二级尺寸为:728.632.29.2=?; 第三级尺寸为:03.1868.2728.6=?; 第四级尺寸为:65.9636.503.18=? 正信号通路的延迟为:()0036.2236.5136.5436.5132.2132.2p p p t t t =++++++++= 反信号通路情况与上问相同,延迟为0008.22)36.5136.5436.51(p p p t t t =+++++= 2、 根据单位反相器(NMOS:W=0.5u L=0.5u PMOS:W=1.8u L=0.5u),设计出实 际电路,并仿真1题中第一问的路径延迟。 设计出实际电路如下:

成绩: 计算机原理实验室实验报告 本说明打印前删除!!proteus 实验报告格式必须保持原样,蓝色部分按照实验内容自行填写;全班统一使用A4大小纸张,部分困难学生可以使用等大小纸张,自绘实验报告格式;全部实验完成后,学委按照实验顺序把每个学生的实验报告(含首页)装订成册,按照学号顺序排列,提交给实验指导老师(询问代课老师,学校将实验工作指派给了哪位老师)。 学委提交报告时,需要同时提交(附录)实验成绩登记表一份。其中表头部分课程,班级,班级总人数照实填写,项目填写本学期本课程的实验数量;学号姓名栏按照顺序填写,报告一栏填写该同学交报告的份数(每项目每人一份报告);出勤和成绩栏留空,由实验室填写;特殊情况填写在备注处,若空间不够请写于背面并在备注处标明;若有学号超过58号的情况,请在背后按照格式登记所有项目;空学号可以不留空位置,顺序递进。 课程:计算机组成原理 姓名:刘翔翔 专业:软件工程 学号:1420561 21 日期:2016年6月 太原工业学院 计算机工程系

实验二:输寄存器实验 实验环境PC机+Win 7+proteus仿真器实验日期2016.06.01 一.实验内容 基本要求 1.理解CPU运算器中寄存器的作用 2.设计并验证寄存器组(至少四个寄存器) 扩展要求 3.实现更多的寄存器(至少8个) 思考题: 思考随着寄存器的增多,电路设计的复杂度是什么比例增大? 二.理论分析或算法分析 1.基本要求 使用74LS373充当寄存器,74LS139做地址译码,74LS245用作输入,数码管显示寄存器内的数据。74LS139为二-四译码器,用两根线作为地址线接到74LS139的输入端,输出端分别接到每个74LS373的OE上,再用一个74LS139配合反相器产生控制每个74LS373的LE的信号。74LS245的输出端分别对应接到373输入端的每个管脚上的。74LS373的输出端对应接到数码管的对应管教上,以实现数据的显示。先在各个寄存器中输入不同的数据,然后关闭74ls248(输入),选择不同的373(寄存器),在数码管上显示不同的数据。 2.扩展要求 与基本要求相比大体不变,地址译码部分选择74LS138来做地址译码器。原理图连接方式原理不变,验证方式不变。

实验六 移位寄存器功能测试及应用 --实验报告要求 一. 实验目的(0.5分) 1. 熟悉寄存器、移位寄存器的电路结构和工作原理。 2. 掌握中规模4位双向移位寄存器逻辑功能及使用方法。 3. 熟悉移位寄存器的应用。 二. 实验电路 D0、D1 、D2 、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;SR 为右移串行输入端,SL 为左移串行输入端;S1、S0 为操作模式控制端;R C 为直接无条件清零端;CP 为时钟脉冲输入端。 三 图2 CC40194/74LS194 逻辑功能测试 图1 CC40194/74LS194的逻辑符号及引脚功能 图3 环形计数器

四. 实验原理(0.5分) 1.移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用。 74LS194有5种不同操作模式:即并行送数寄存,右移(方向由Q0-->Q3),左移(方向由Q3→Q0),保持及清零。 2.移位寄存器应用很广,可构成移位寄存器型计数器:顺序脉冲发生器;串行累加器;可用数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。 (1)环行计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位。 (2)实现数据、并行转换器 a)串行∕并行转换器 串行∕并行转换器是指串行输入的数码,经转换电路之后变换成并行输出。 b)并行∕串行转换器 并行∕串行转换器是指并行输入的数码经转换电路之后,换成串行输出。 五. 实验内容与步骤(共1分) 1. 2.测试74LS194的逻辑功能(0.5分) (1)在实验箱上选取一个16P插座,按定位标记插好74LS194集成块。 (2)将实验挂箱上+5V直流电源接40194的16脚,地接8脚。S1、S0、SL、SR、D0、D1、D2、D3分别接至逻辑电平开关的输出插口;Q0、Q1、Q2、Q3接至发光二极管。CP端接单次脉冲源。 (3)改变不同的输入状态,逐个送入单次脉冲,观察寄存器输出状态,记录之。 a)清除:令=0,其它输入均为任意态,这时寄存器输出Q0、 Q1、 Q2 、Q3应均为0。清除后,至=1。 b)送数:令=S1=S0=1 ,送入任意4位二进制数,如D0、D1、D2、D3=1010,加CP脉冲,观察CP=0、CP由1→0、CP=1三种情况下寄存器输出状态的变化,观察寄存输出状态变化是否发生在CP脉冲的上升沿。 (c)右移:清零后,令=1, S1=0 S0=1,由右移输入端S R送入二进制数码如0100,由CP端连续加4个脉冲,观察输出情况,记录之。 (d)左移:先清零或予至,再令=1 S1=1,S0=0,由左移输入端S L送入二进制数码

移位寄存器实验报告 姓名:陈素学号:3120100621 专业:软件工程课程名称:逻辑与计算机设计基础实验同组学生姓名:张闻 实验时间:y yyy-mm-dd 实验地点:紫金港东4-509 指导老师:一、实验目的和要求 掌握移位寄存器的工作原理及设计方法 掌握串、并数据转换的概念与方法 了解序列信号在CPU控制器设计中的应用 二、实验内容和原理 2.1 实验原理 带并行置入的移位寄存器 移位寄存器:每来一个时钟脉冲,寄存器中的数据按顺序向左或向右移动一位必须采用主从触发器或边沿触发器 不能采用电平触发器 数据移动方式:左移、右移 数据输入输出方式 串行输入,串行输出 串行输入,并行输出 并行输入,串行输出 串行输入的移位寄存器 使用D触发器,可构成串行输入的移位寄存器 2.2 标题 <正文>

带并行输入的右移移位寄存器 数据输入移位寄存器的方式:串行输入、并行输入 带并行输入的8位右移移位寄存器 module shift_reg(clk, S, s_in, p_in, Q); input wire clk, S, s_in; input wire [7:0] p_in; output wire [7:0] Q; wire [7:0] D; wire nS; FD FDQ0(.C(clk), .D(D[0]), .Q(Q[0])), FDQ1(.C(clk), .D(D[1]), .Q(Q[1])), FDQ2(.C(clk), .D(D[2]), .Q(Q[2])), FDQ3(.C(clk), .D(D[3]), .Q(Q[3])), FDQ4(.C(clk), .D(D[4]), .Q(Q[4])), FDQ5(.C(clk), .D(D[5]), .Q(Q[5])), FDQ6(.C(clk), .D(D[6]), .Q(Q[6])), FDQ7(.C(clk), .D(D[7]), .Q(Q[7])); OR2 D0_L(.I0(L_0), .I1(R_0), .O(D[0])), D1_L(.I0(L_1), .I1(R_1), .O(D[1])), D2_L(.I0(L_2), .I1(R_2), .O(D[2])), D3_L(.I0(L_3), .I1(R_3), .O(D[3])), D4_L(.I0(L_4), .I1(R_4), .O(D[4])), 串行输入 S

设计示例2:寄存器堆设计 1、 功能概述: MIPS 指令格式中的寄存器号是5bits ,指令可以访问25=32个32位的寄存器。这样的一堆寄存器“堆在一起”构成一个寄存器堆(Register File )。模块框图如图1所示: Regfile 图1 模块框图 2、 结构框图: 3、 接口说明: 表1: 寄存器堆模块接口信号说明表 clk we wdata Valid Valid waddr rst_n 图2 寄存器堆写时序框图

4、设计电路源代码 //功能描述风格寄存器堆的设计 module regfile( input clk, input rst_n, //写端口 input we, //写使能 input[4:0] waddr, //写寄存器下标 input[31:0] wdata, //待写入寄存器堆的数据 //读端口1 input[4:0]raddr1, //读端口1寄存器下标 output[31:0] rdata1,//从端口1读出的寄存器堆的数据 //读端口2 input[4:0]raddr2, //读端口2寄存器下标 output[31:0] rdata2 //从端口2读出的寄存器堆的数据); reg[31:0] regs[0:31]; //32个32位寄存器堆 //Write operation always @ (posedge clk or negedge rst_n) begin if(!rst_n) begin:reset_all_registers //将32个寄存器复位为0. integer i; for(i=0;i<32;i=i+1) regs[i] = 32'd0; end else begin //写寄存器堆有效时,更新寄存器堆中某个寄存器的数据 if((we == 1'b1) && (waddr != 5'h0)) begin regs[waddr] <= wdata; end end end //Read port1 operation assign rdata1 = (raddr1 == 5'd0) ? 32'd0 : regs[raddr1]; //Read port2 operation assign rdata2 = (raddr2 == 5'd0) ? 32'd0 : regs[raddr2];

6.9 通用寄存器实验报告 一、实验目的: 1、了解通用寄存器组的用途及对CPU的重要性。 2、掌握通用寄存器组的设计方法。 二、实验内容: 1、通用寄存器组的作用 通用寄存器组是CPU的重要组成部分。 (1)从存储器和外部设备(除DMA方式外)取来的数据要放在通用寄存器中; (2)向存储器和外部设备(除DMA方式外)输出的数据从通用寄存器中取出; (3)参加算术运算和逻辑运算的数据从通用寄存器组中取出,同时通用寄存器也是运算结果的暂存地。 (4)通用寄存器组有两个读端口,负责提供进行算术逻辑单元需要的源操作数和目的操作数;有一个写端口,负责将运算结果保存到指定的寄存器内。 2、通用寄存器组功能实现 根据通用寄存器组的功能要求,一个只有四个16位寄存器的通用寄存器组的框图如下图所示: ⑴寄存器部分: 当reset为低电平时,将四个16位寄存器R0-R3复位为0;当寄存器的write和sel

为高电平时,在时钟信号clk的上升沿将D端的输入D[15-0]写入寄存器,然后送到寄存器的输出Q[15-0]。4个寄存器的允许写信号write和外部产生的目的寄存器写信号DRWr 直接相连。每个寄存器还有另一个选择信号sel,它决定哪一个寄存器进行写操作。4个寄存器的选择信号分别和2-4译码器产生的sel00、sel01、sel10、sel11相连。只有当一个寄存器被选中(sel为高电平时),才允许对该寄存器进行写操作。 ⑵ 2-4译码器: 2-4译码器的输入sel[1-0]接DR[1-0],2-4译码器对2位的输入信号sel[1-0]进行2-4译码,产生4个输出sel00、sel01、sel10、sel11,分别送往4个寄存器R0、R1、R2和R3的选择端sel。 ⑶ 4选1多路器 4选1多路选择器1从4个寄存器R0、R1、R2和R3的输出Q[15-0]选择1路送到DR_data[15-0],给算术逻辑单元提供目的操作数;选择信号sel[1-0]接DR[1-0]。4选1多路选择器2从4个寄存器R0、R1、R2和R3的输出Q[15-0]选择1路送到SR_data[15-0],给算术逻辑单元提供源操作数;选择信号sel[1-0]接SR[1-0]。 三、实验要求: 1、实验设计目标 设计一个通用寄存器组满足以下要求: (1)通用寄存器组中有4个16位的寄存器。 (2)当复位信号reset=0时,将通用寄存器组中的4个寄存器清零。 (3)通用寄存器组中有1个写入信号,当DRWr=1时,在时钟clk的上升沿将数据总线上的数写入DR[1-0]指定的寄存器。 (4)通用寄存器组中有两个读出端口,一个对应算术逻辑单元的目的操作数DR,另一个对应算术逻辑单元的源操作数SR。DR[1-0]选择目的操作数;SR[1-0]选择源操作数。 (5)设计要求层次设计。底层的设计实体有三个:16位寄存器,具有复位功能和允许写功能;一个2-4译码器,对应寄存器写选择;一个4选1多路开关,负责选择寄存器的读出。顶层设计构成一个完整的通用寄存器组。 2、顶层设计实体的引脚要求 引脚要求对应关系如下: (1)clk对应试验台上的时钟(单脉冲)。 (2)reset对应实验台上的CPU复位信号CPU_RST。 (3)SR[1-0]对应实验台开关SA1,SA0。

寄 存 器 实 验 报 系别:信息技术系 专业:计算机科学与技术 班级:计科142 姓名:康道顺 学号:201401014233

实验一寄存器实验 一、实验目的 (1)了解模型机中A, W寄存器结构、工作原理及其控制方法。 (2)了解模型机中寄存器组R0..R3结构、工作原理及其控制方法。 二、实验要求 (1)A、W寄存器:利用COP2000实验仪上的K16..K23开关做为DBUS的数据, 其它开关做为控制信号,将数据写入寄存器A,W。 (2)R0、R1、R2、R3寄存器实验:利用COP2000实验仪上的K16..K23开关 做为DBUS的数据,其它开关做为控制信号,对数据寄存器组R0..R3进 行读写。 三、实验说明 寄存器的作用是用于保存数据的,因为我们的模型机是8位的,因此在本模型机中大部寄存器是8位的,标志位寄存器(Cy, Z)是二位的。 COP2000用74HC574来构成寄存器。74HC574的功能如下: 注意: 1. 在CLK的上升沿将输入端的数据打入到8个触发器中

74HC574工作波形图 四、实验原理 实验1:A,W寄存器实验 (1)原理图 寄存器A原理图 寄存器W原理图(2)工作波形图

寄存器A,W写工作波形图 (4)实验数据 例:将55H写入A寄存器 二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据55H。 置控制信号为: 按住CLOCK脉冲键,CLOCK由高变低,这时寄存器A的黄色选择指示灯亮,表明选择A寄存器。放开CLOCK键,CLOCK由低变高,产生一个上升沿,数据55H 被写入A寄存器。 a)将66H写入W寄存器 。。。。。。 实验2:R0,R1,R2,R3寄存器实验 (1)原理图

实验三寄存器组的设计与实现 一、实验目的 1. 学习掌握Quartus II 的图形编辑、编译、仿真的设计流程; 2. 学习74670三态输出寄存器堆的使用; 3. 理解寄存器组的工作原理和过程,设计出4个16位寄存器组并对设计的正确性进行验证 二、实验任务及要求 1. 设计出功能完善的寄存器组,并对设计的正确性进行验证。具体要求如下: (1) 用图形方式设计出寄存器组的电路原理图。 (2) 测试波形要用时序仿真实现,先将不同的数据连续写入4个寄存器后,再分别读出。 (3) 将设计文件封装成器件符号。 (4) 数据的宽度最好为16位。 三、实验装置 安装有Quartus II软件的PC机1台 四、设计思想 运用具有三态功能的芯片74670进行设计,74670为4*4(4个4位寄存器)的寄存器堆,使用四片74670并联,同时对4 片74670 芯片进行读写操作控制,从而实现4个16位数据的存储与输出。 五、逻辑电路图

74670芯片图:三态输出的4*4寄存器堆 六、实验结果: 见原理图,波形图以及元件封装图。 1.原理图分析:见设计思想

2.波形图分析: 当RE为1,WE不为1时,实现输入功能,WB,WA控制数据输入到哪个寄存器组当RE为1,WE为1时,出现高阻状态,此时既不输入也不输出 当WE为1,RE不为1时,实现输出功能,RB,RA控制哪个寄存器组的数据输出 3.封装元件的功能说明: d[15..0]16位输入数据 q[15..0]16位输出数据 gwn:写入数据使能控制端,低有效 wa,wb:选择控制端,四种组合控制16位数输入到相应四种寄存器组 grn:读出数据使能控制端,低有效 ra,rb:选择控制端,四种组合控制从四种寄存器组读出相应16位数

2.1 寄存器实验 姓名:孙坚学号:134173733 班级:13计算机日期:2015.4.3 一.实验要求:利用CPTH 实验仪上的K16..K23 开关做为DBUS 的数据,其它开关做为控制信号,将数据写入寄存器,这些寄存器包括累加器A,工作寄存器W,数据寄存器组R0..R3,地址寄存器MAR,堆栈寄存器ST,输出寄存器OUT。 二.实验目的:了解模型机中各种寄存器结构、工作原理及其控制方法。 三.实验电路:寄存器的作用是用于保存数据的,因为我们的模型机是8位的,因此在本模型机中大部寄存器是8 位的,标志位寄存器(Cy, Z)是二位的。 CPTH 用74HC574 来构成寄存器。74HC574 的功能如下: 1. 在CLK的上升沿将输入端的数据打入到8 个触发器中 2. 当OC = 1 时触发器的输出被关闭,当OC=0 时触发器的输出数据

四.实验数据及步骤: 实验1:A,W 寄存器实验 寄存器A,W 写工作波形图

连接线表: 系统清零和手动状态设定:K23-K16开关置零,按[RST]钮,按[TV/ME]键三次,进入"Hand......"手动状态。 在后面实验中实验模式为手动的操作方法不再详述. 将66H写入A寄存器 二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据66H 置控制信号为: 按住STEP脉冲键,CK由高变低,这时寄存器A 的黄色选择指示灯亮,表明选择A 寄存器。放开STEP 键,CK 由低变高,产生一个上升沿,数据66H 被写入A 寄存器。 将88H写入W寄存器 二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据88H 置控制信号为: 按住STEP脉冲键,CK由高变低,这时寄存器W 的黄色选择指示灯亮,表明选择W 寄存器。放开STEP 键,CK 由低变高,产生一个上升沿,数据88H 被写入W 寄存器。 注意观察: 1.数据是在放开STEP键后改变的,也就是CK的上升沿数据被打入。 2.WEN,AEN为高时,即使CK有上升沿,寄存器的数据也不会改变。

寄存器堆设计 1、功能概述: MIPS指令格式中的寄存器号是5bits,指令可以访问25=32个32位的寄存器。这样的一堆寄存器“堆在一起”构成一个寄存器堆(Register File)。 2、接口说明: 寄存器堆模块接口信号说明表 脉冲reg, 复位端reg, 写使能端reg, 写地址reg, 写数据reg, 读地址一reg, 读地址二reg, 读数据一reg, 读数据二reg; 设计思路: 1、复位处理是利用标志位flag实现的,当复位时,flag=0;利用i来计数,当i<31 时,flag都等于0;直到i=32,复位完成,flag=1,这时,才可以进行写操作。 2、当复位时,需要32个脉冲才能将寄存器全部复位。复位未完成,flag一直等于 0。若复位未完成时,进行写操作,这时,并不能写进去,便出错了。所以,进行32分频,当寄存器可以写入时,复位已完成。 3、设计电路源代码 //----32个32位寄存器堆 module regfile( input reg, //脉冲 input reg, //复位端 input reg, //写使能端 input [4:0] reg读地址一 input [4:0] reg读地址二 input [4:0] reg, //写地址 input [31:0] reg, //写数据 output [31:0] reg读数据一 output [31:0] reg读数据二

); //---------------------------------- reg [31:0]regfiles[0:31]; //实现寄存功能 reg [4:0] i; //实现flag的变换reg flag; //实现复位的标志reg reg; //实现写数据的脉冲 reg [4:0]count; //---32分频处理 always@(posedge reg or posedge reg) begin if(reg) begin count<=5'd0; reg<=1'b0; end else if(count<5'd16) begin count<=count+1'b1; end else begin count<=5'd0; reg<=~reg; end end //---复位处理 always@(posedge reg or posedge reg) begin if(reg) begin i<=5'd0;

实验七 移位寄存器及其应用 一、实验目的 1. 掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2. 熟悉移位寄存器的应用——环形计数器。 二、实验原理 1. 移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又有右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为74LS194或CC40194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图 1所示。 图 1 74LS194的逻辑符号及其引脚排列 其中D 3、D 2、D 1、D 0为并行输入端, Q 3、Q 2、Q 1、Q 0为并行输出端;S R 为右移串行输入端,S L 为左移串行输入端,S 1、S 0为操作模式控制端;CR 为直接无条件清零端;CP 为时钟脉冲输入端。74LS194有5种不同操作模式:即并行送数寄存,右移(方向由Q 3→Q 0),左移(方向由Q 0→Q 3),保持及清零。S 1、S 0和CR 端的控制作用如表 1所示。 表 1

2.移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计致器和串行累加器的线路及其原理。 (1) 环形计数器:把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图2所示,把输出端Q 0和右移串行输入端S R 相连接,设初始状态Q 3 Q 2 Q 1 Q =1000, 则在时钟脉冲作用下Q 3Q 2 Q 1 Q 将依次变为0100→0010→0001→1000→……,可见它是具 有四个有效状态的计数器,这种类型的计效器通常称为环形计数器。图2电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。