VHDL大总结

一、填空题

1.两种标识符

短、扩展

2.4种基本数据类型

常量、变量、信号、文件

3.常量说明格式

constant 常数名: 数据类型:=表达式;

4.三种数据变换方法?

函数转换、常数转换、类型标记

5.四种运算操作符?

逻辑、关系、算术、并置

6.如何启动进程?

(1).必须包含一个显示的敏感信号变量

(2).或者包含一个wait语句

7.五种基本结构?

库(library)、包集合(package)、实体(entity)、结构体(architecture)、配置(configuration) 8.信号与变量代入?

(1).<=

(2).:=

9.列举可编程逻辑器件?

PROM→PLA→PAL→CPLD→FPGA→EPROM→EEPROM→GAL

10.数据类型

整数、位、位矢量、符号、布尔量、时间、错误等级、标准逻辑

11.四种端口模式?

IN—OUT—INOUT—BUFFER

12.三种子结构描述语句?BLOCK—PROCESS—SUBPROGRAMS

13.结构体三种描述方式

寄存器传输(RTL)--数据流、结构描述、行为描述14.标识符规则?

(1).不以数字靠头

(2).下划线不连续

(3).不与保留字重复

(4).下划线前后必须有英文字母或者数字

(5).最后一个不能使用下划线(连字符)

15.扩展标识符

\12@+\

16.赋值?

(1).信号、变量可以多次赋值

(2).常量只能定义时赋值(进程内部,子函数内部)17.高阻、不定态?

'Z'------------'X'

18.进程位置?

结构体内部

19.变量位置?

进程内部---包内部----子程序内部

20.进程执行机制?

敏感信号发生跳变

21.优先级?

if语句之间具有不同优先级

22.时序电路的去驱动信号?

时钟

23.时序电路在何时发生变化?

时钟信号的边沿

24.两种状态机?

(1).moore-----f(现状)

(2).mealy-----f(现状,输入)

25.什么有九值逻辑

标准逻辑(STD_LOGIC)

26.定义信号a,4位标准逻辑向量?

SIGNAL A : STD_LOGIC_VECTOR(3 DOWNTO 0);

27.定义变量b,整型,范围0 到9

SIGNAL B: TNTEGER RANGE 0 TO 9;

28.空操作?

NULL

29.CPLD与FPGA?

(1).基于乘积项技术—内带存储

(2).基于查找表技术—需要外部扩展存储,比如扩展EEPROM

30.IF语句三种类型?

(1).门闩(shuan)控制

(2).二选一控制

(3).多选一控制

31.常用库与包集合?

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

32."/="的功能?

在条件判断时判断操作符两端不相等

33.串行与并行?

(1).赋值语句—并行

(2).IF语句------串行

二、判断题

1.缺少库文件

LIBRARY IEEE

2.缺少包集合

USE IEEE.STD_LOGIC_1164.ALL

3.实体定义的分号问题

port(aaa;bbb;ccc);

或者

port(

aaa;

bbb;

ccc

);

4.带入语句问题

(1).信号---<=

(2).变量---:=

5.引号问题?

(1).字符----' '

(2).字符串----" "

6.末尾分号问题

(1).END CASE;

(2).END PROCESS;

7.PROCESS必须赶上敏感信号?

包含W AIT ON语句可以不列出

8.VHDL与C语言没差别?

(1).运行基础—CPU+RAM;逻辑、触发器组成的数字电路

(2).执行方式---串行;并行

(3).验证方式---变量值;时序逻辑关系

9.进程之间传递

用信号,非变量

10.默认值

数值型变量默认为0---------- 不要加引号(位变量)11.类型定义?

type wr is (wr0, wr1, wr2);定义的是类型

需要为该类型定义对象才可以赋值

12.设计方法?

(1).传统------------自下至上

(2).VHDL----------自上至下

13.层次设计?

高层次可以调用低层次

14.进程语句数量

一个程序可以多个进程语句

15.运算符优先级

NOT>乘法>正负>关系>逻辑

16.signalsel : integer?

right

17.进程内和进程外?

原则上不一致,在没有敏感信号的前提下,可以认为一致

18.定义实体至少包含一条port map?

false

19.时间效率?

状态机比计数器更有效,更紧凑

三、简答题

1.名称映射与位置映射?

(1).名称:COM1 : U1 PORT MAP (A<=N1,B<=N2,C<=N3);

(2).位置:PORT(A,B:IN BIT;

C:OUT BIT);

引用时:U2:AND2 PORT MAP(NSEL, D1,AB);

2.调用库里面包含的元件的方法?

(1).COMPONENT

(2).PORT MAP

3.信号与变量的区别?

(1).信号延时赋值,变量立即赋值

(2).<=; :=

(3).信号在器件内部相当于连线,变量没有

(4).信号在结构体内定义,而变量在PROCESS中定义

4.三种描述方式的区别?

5.条件带入语句与条件语句的区别?

(1).后者只能在进程内部使用

(2).带入语句必须有ELSE,而条件语句可以没有

(3).带入语句不能嵌套,而条件语句可以

6.两种状态机的区别?

7.简述CPLD与FPGA?

(1).CPLD—乘积项技术—

(2).FPGA—查找表技术--需要配置外部程序寄存芯片

8.进程语句的特点?

(1).并发执行,信号传递,可以存取结构体或实体中所定义的信号

(2).内部语句都是顺序执行

(3).启动进程--必须包含敏感信号或者wait语句

9.简述VHDL基本结构

库、包集合、实体、结构体、配置

10.可编程逻辑器件的优点?

(1).集成度高—可以替代几千块通用芯片

(2).完善先进的开发工具

(3).可以反复擦除、编程,方便设计和修改

(4).可以灵活的定义管脚

(5).保密性很好

四、编程题

1.二选一电路

ENTITY MUX IS

PORT(

D0:IN BIT;

D1:IN BIT;

SEL:IN BIT;

Q:OUT BIT

);

ARCHITECTURE CONNECT OF MUX IS SIGNAL TEMP1,TEMP2,TEMP3:BIT; BEGIN

CALE:

BLOCK

BEGIN

TEMP1<=D0 AND SEL;

TEMP2<=D1 AND (NOT SEL);

TEMP3<=TEMP1 OR TEMP2;

Q<=TEMP3;

END BLOCK CALE;

END CONNECT;

END CONNECT;

2.四选一电路

3.四位加法计数器

4.八-三编码器

5.四位逐位进位全加器

6.数值比较器

7.三-八译码器

8.二-十(BCD)优先权编码器

9.精确计时电路

10.触发器

11.四状态循环

12.异或门设计

13.二输入与非门

14.三态门

15.6分频器

16.二-四译码器

17.四-十六译码器

18.8进制异步复位计数器

五、附加

19.I F语句

门闩控制

IF (A='1') THEN

C<=B;

END IF;

二选择控制

IF (SEL='1') THEN

***;

ELSE

***;

END IF ;

多选择控制

IF ** THEN

XXX;

ELSIF **THEN

XXX;

ELSE

XXX;

END IF;

20.C ASE语句

CASE SEL IS

WHEN 0=>Q<=I0;

WHEN 1=>Q<=I1;

WHEN OTHERS=>Q<="XXXXXX"; END CASE;

21.并发信号带入语句

实质是一个进程语句的缩写

22.条件信号带入语句

Q<=I0 WHEN SEL="00" ELSE

I1 WHEN SEL="01" ELSE

'X';

23.选择信号带入语句

WITH SEL SELECT

Q<=I0 WHEN 0,

I1 WHEN 1,

I2 WHEN 2,

'X' WHEN OTHERS;

硬件描述语言实验附录 姓名:xxx 学号:xxx 指导教师:xxx 目录 硬件描述语言实验附录 (1) 实验1.三输入与门电路实验 (2) 实验2. 三—八译码器实验 (3) 实验3. D触发器实验 (4) 实验4. 分频器实验 (5) 实验5. 状态机实验 (8)

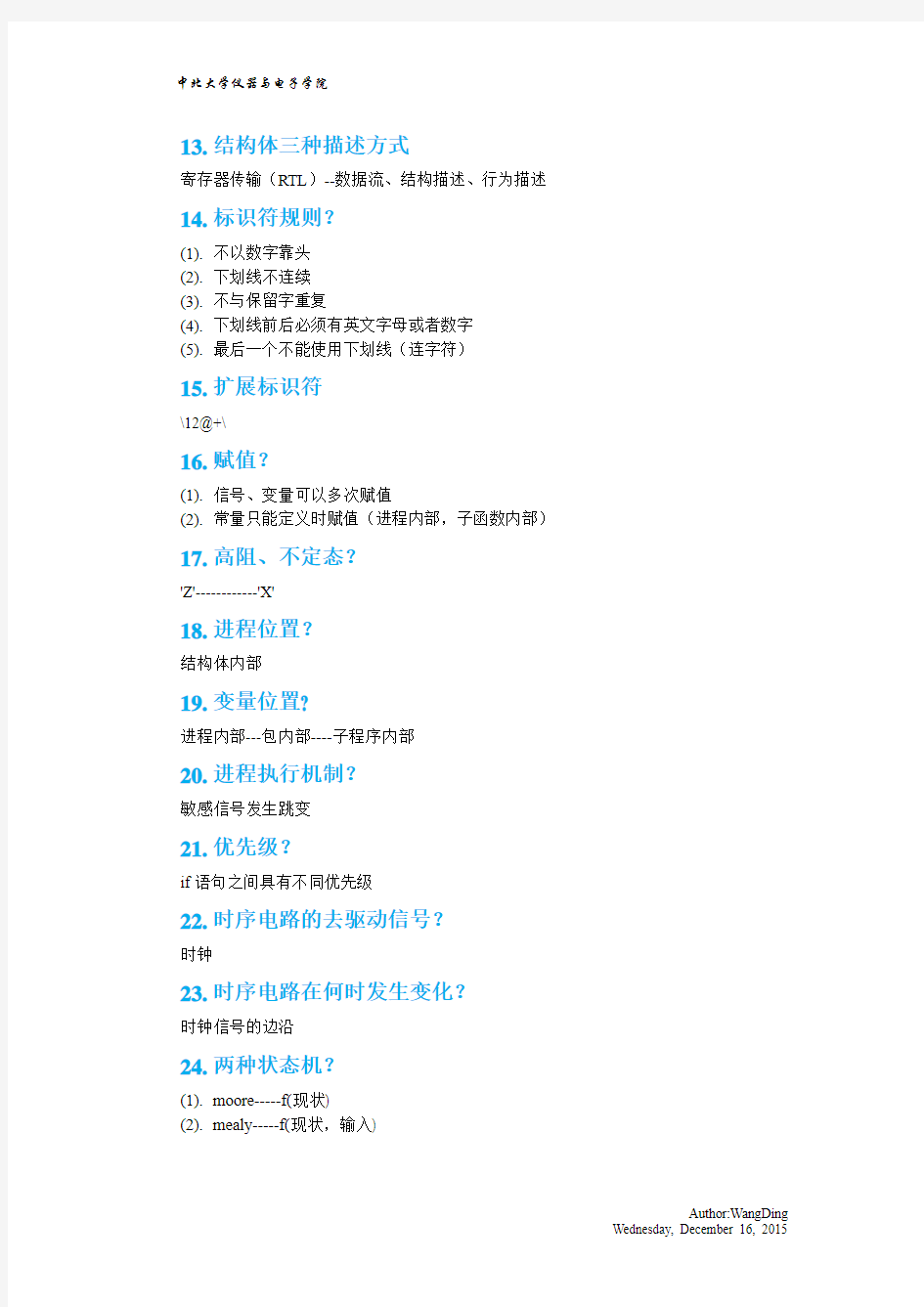

实验1.三输入与门电路实验 --三输入与门电路threeinput --姓名:王定 --学号:1306034248 --中北大学 LIBRARY IEEE; --调用库 USE IEEE.STD_LOGIC_1164.ALL;--库文件 -------------------------------------------------------------- ENTITY threeinput IS --定义实体名,其名称必须与VHDL文本文件名称相同PORT( A: IN STD_LOGIC; --输入端口,时钟输入 B: IN STD_LOGIC; --输入端口,个位写入使能 C: IN STD_LOGIC; --输入端口,十位写入使能 CO: OUT STD_LOGIC); --输出端口,溢出标志 END ENTITY threeinput; --结束端口定义 -------------------------------------------------------------- ARCHITECTURE RTL OF threeinput IS--定义结构体 BEGIN PROCESS(A,B,C) IS --开始,必须带上 BEGIN CO<=A AND B AND C ; END PROCESS; END ARCHITECTURE RTL; --结束结构体 表1. 三输入与门电路VHDL实验代码 图1. 三输入与门电路仿真波形图,A,B,C输入,CO输出

VHDL大总结 一、填空题 1.两种标识符 短、扩展 2.4种基本数据类型 常量、变量、信号、文件 3.常量说明格式 constant 常数名: 数据类型:=表达式; 4.三种数据变换方法? 函数转换、常数转换、类型标记 5.四种运算操作符? 逻辑、关系、算术、并置 6.如何启动进程? (1).必须包含一个显示的敏感信号变量 (2).或者包含一个wait语句 7.五种基本结构? 库(library)、包集合(package)、实体(entity)、结构体(architecture)、配置(configuration) 8.信号与变量代入? (1).<= (2).:= 9.列举可编程逻辑器件? PROM→PLA→PAL→CPLD→FPGA→EPROM→EEPROM→GAL 10.数据类型 整数、位、位矢量、符号、布尔量、时间、错误等级、标准逻辑 11.四种端口模式? IN—OUT—INOUT—BUFFER 12.三种子结构描述语句?BLOCK—PROCESS—SUBPROGRAMS

13.结构体三种描述方式 寄存器传输(RTL)--数据流、结构描述、行为描述14.标识符规则? (1).不以数字靠头 (2).下划线不连续 (3).不与保留字重复 (4).下划线前后必须有英文字母或者数字 (5).最后一个不能使用下划线(连字符) 15.扩展标识符 \12@+\ 16.赋值? (1).信号、变量可以多次赋值 (2).常量只能定义时赋值(进程内部,子函数内部)17.高阻、不定态? 'Z'------------'X' 18.进程位置? 结构体内部 19.变量位置? 进程内部---包内部----子程序内部 20.进程执行机制? 敏感信号发生跳变 21.优先级? if语句之间具有不同优先级 22.时序电路的去驱动信号? 时钟 23.时序电路在何时发生变化? 时钟信号的边沿 24.两种状态机? (1).moore-----f(现状) (2).mealy-----f(现状,输入)