74LS192引脚图管脚及功能表

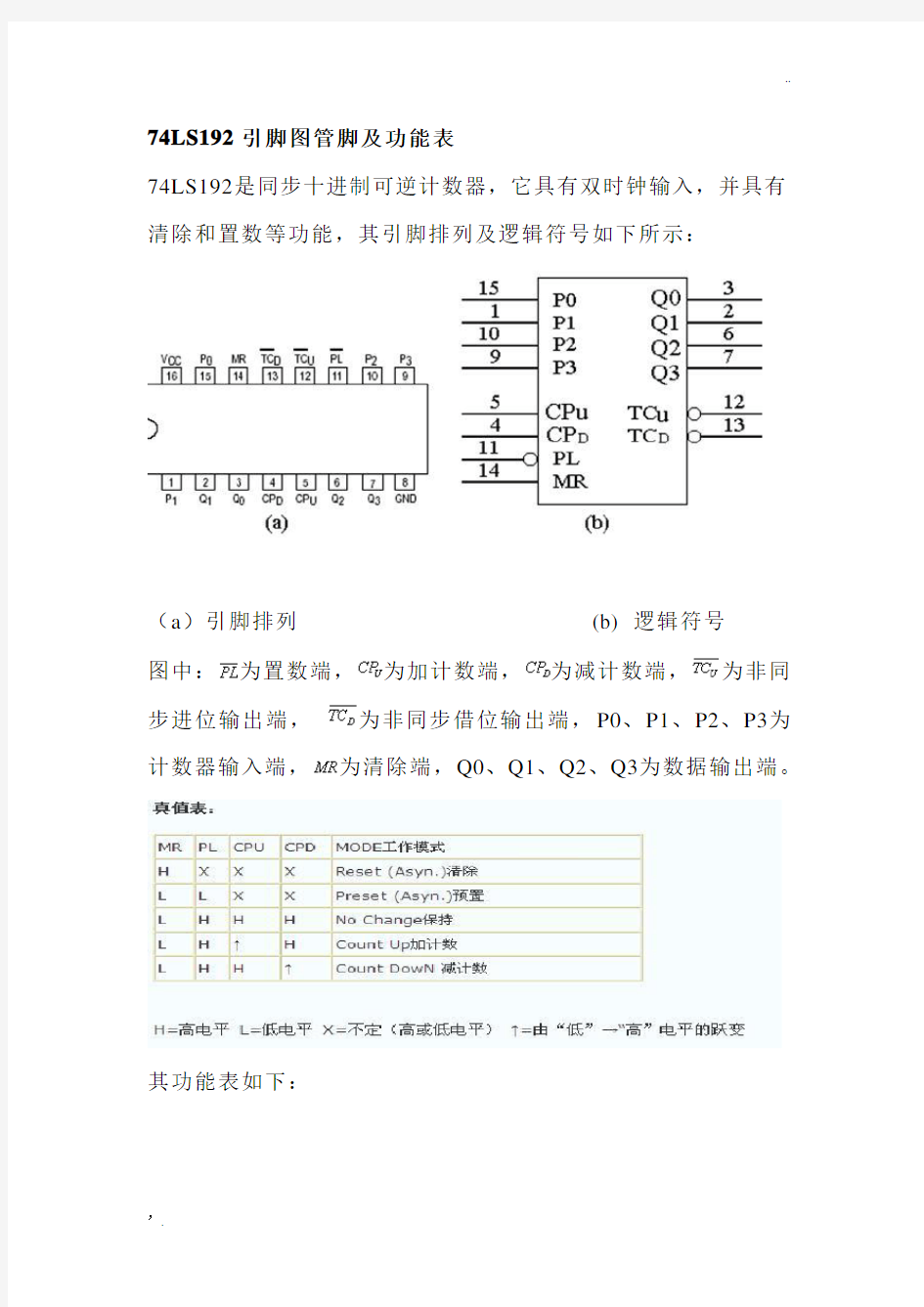

74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:

(a)引脚排列(b) 逻辑符号

图中:为置数端,为加计数端,为减计数端,为非同步进位输出端,为非同步借位输出端,P0、P1、P2、P3为计数器输入端,为清除端,Q0、Q1、Q2、Q3为数据输出端。

其功能表如下:

例如:用74LS192芯片设计出三十进制计数器

用192 采用级联法做成3*10 的一个芯片满十进一另一个芯片到3 即0011的时候提供清零脉冲恢复到0000 详见图

74LS373 引脚图、内部结构、参数、典型应用电路 【功能简介】 74LS373是一款常用的地址锁存器芯片,由八个并行的、带三态缓冲输出的D触发器构成。在单片机系统中为了扩展外部存储器,通常需要一块74LS373芯片。本文将介绍74LS373的工作原理,内容涵盖引脚图、内部结构、主要参数以及在单片机扩展系统中的典型应用电路。 【内部逻辑结构图】 74LS373地址锁存器的内部逻辑结构如图一所示。 图1

【74LS373的真值表(功能表)】 G—与8031/8051的ALE相连,控制八个D型锁存器的导通与截止:高电平时,八个D型锁存器正常运行(导通),即锁存器的输出端 与输入端D的反相信号始终同步;低电平时锁存器截止,D锁存器输出 端的状态保持不变。 OE(Output Enable = Output Control)—使能端,接地时锁存 【74LS373引脚排列图】

【74LS373电气参数】 拖动图片放大! 74ls373推荐工作条件 【74LS373在单片机扩展系统中的典型应用电路】 当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端G为高电平时,输出Q0-Q7的状态与输入端D1-D7状态相同;当G发生负的跳变时,输入端D0-D7 数据锁入Q0-Q7。51单片机的ALE信号可以直接与74LS373的G 连接。在MCS-51单片机系统中,其连接方法如下图所示。其中输入端1D-8D接

至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允 许信号ALE。输出允许端OE接地,表示三态输出门一直导通,可以送出地址信 号。 1D-8D为8个输入端。 1Q-8Q为8个输出端。 【说明】基础比较好的同学请直接忽略。 G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。 OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。 (1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态); (2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态. 锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。

实验四触发器及其功能转换 一、实验目的 1、掌握基本RS、JK、D和T触发器的逻辑功能 2、掌握集成触发器的逻辑功能及使用方法 3、熟悉触发器之间相互转换的方法 二、实验原理 触发器具有两个稳定状态,用以表示逻辑状态“1”和“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存贮器件,是构成各种时序电路的最基本逻辑单元。 1、基本RS触发器 图4-1为由两个与非门交叉耦合构成的基本RS触发器,它是无时钟控制低电平直接触发的触发器。基本RS触发器具有置“0”、置“1”和“保持”三种功能。通常称S为置“1”端,因为S=0(R=1)时触发器被置“1”;R为置“0”端,因为R=0(S=1)时触发器被置“0”,当S=R=1时状态保持;S=R=0时,触发器状态不定,应避免此种情况发生,表9-1为基本RS触发器的功能表。 基本RS触发器。也可以用两个“或非门”组成,此时为高电平触发有效。

2、JK触发器 在输入信号为双端的情况下,JK触发器是功能完善、使用灵活和通用性较强的一种触发器。本实验采用74LS112双JK触发器,是下降边沿触发的边沿触发器。引脚功能及逻辑符号如图4-2所示。 JK触发器的状态方程为 Q n+1=J Q n+K Q n J和K是数据输入端,是触发器状态更新的依据,若J、K有两个或两个以上输入端时,组成“与”的关系。Q与Q为两个互补输出端。通常把 Q=0、Q=1的状态定为触发器“0”状态;而把Q=1,Q=0定为“1”状态。 图4-2 74LS112双JK触发器引脚排列及逻辑符号 下降沿触发JK触发器的功能如表4-2 表4-2

系列芯片功能表汇总

————————————————————————————————作者:————————————————————————————————日期: ?

74系列标准数字电路功能表——中文资料 名称类别功能 7400TTL 2输入端四与非门 7401 TTL 集电极开路2输入端四与非门 7402 TTL2输入端四或非门 7403TTL集电极开路2输入端四与非门 7404TTL六反相器 7405TTL 集电极开路六反相器 7406 TTL 集电极开路六反相高压驱动器 7407TTL 集电极开路六正相高压驱动器 7408 TTL2输入端四与门 7409TTL集电极开路2输入端四与门 7410 TTL 3输入端3与非门 74107 TTL 带清除主从双J-K触发器 74109 TTL带预置清除正触发双J-K触发器 7411TTL 3输入端3与门 74112 TTL 带预置清除负触发双J-K触发器 7412 TTL 开路输出3输入端三与非门 74121TTL 单稳态多谐振荡器 74122 TTL 可再触发单稳态多谐振荡器 74123 TTL 双可再触发单稳态多谐振荡器 74125TTL三态输出高有效四总线缓冲门 74126 TTL三态输出低有效四总线缓冲门 7413 TTL4输入端双与非施密特触发器 74132 TTL 2输入端四与非施密特触发器 74133 TTL 13输入端与非门 74136 TTL 四异或门 74138 TTL 3-8线译码器/复工器 74139 TTL 双2-4线译码器/复工器 7414 TTL 六反相施密特触发器 74145TTL BCD—十进制译码/驱动器 7415 TTL 开路输出3输入端三与门 74150 TTL 16选1数据选择/多路开关 74151 TTL 8选1数据选择器 74153TTL双4选1数据选择器 74154TTL 4线—16线译码器 74155 TTL 图腾柱输出译码器/分配器 74156 TTL 开路输出译码器/分配器 74157 TTL 同相输出四2选1数据选择器 74158TTL 反相输出四2选1数据选择器 7416 TTL 开路输出六反相缓冲/驱动器

1、描述集成电路工艺技术水平的五个技术指标及其物理含义 ⑴集成度(Integration Level):以一个IC芯片所包含的元件(晶体管或门/数)来衡量,(包括有源和无源元件)。 ⑵特征尺寸 (Feature Size) /(Critical Dimension):特征尺寸定义为器件中最小线条宽度(对MOS器件而言,通常指器件栅电极所决定的沟道几何长度),也可定义为最小线条宽度与线条间距之和的一半。 ⑶晶片直径(Wafer Diameter):当前的主流晶圆的尺寸为12寸(300mm),正在向18寸(450mm)晶圆迈进。 ⑷芯片面积(Chip Area):随着集成度的提高,每芯片所包含的晶体管数不断增多,平均芯片面积也随之增大。 ⑸封装(Package):指把硅片上的电路管脚,用导线接引到外部接头处,以便于其它器件连接。封装形式是指安装半导体集成电路芯片用的外壳。 2、简述集成电路发展的摩尔定律。 集成电路芯片的集成度每三年提高4倍,而加工特征尺寸缩小倍,这就是摩尔定律。当价格不变时,集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍 3、集成电路常用的材料有哪些? 集成电路中常用的材料有三类:半导体材料,如Si、Ge、GaAs?以及InP?等;绝缘体材料,如SiO2、SiON?和Si3N4?等;金属材料,如铝、金、钨以及铜等。

4、集成电路按工艺器件类型和结构形式分为哪几类,各有什么特点。 双极集成电路:主要由双极晶体管构成(NPN型双极集成电路、PNP型双极集成电路)。优点是速度高、驱动能力强,缺点是功耗较大、集成度较低。 CMOS集成电路:主要由NMOS、PMOS构成CMOS电路,功耗低、集成度高,随着特征尺寸的缩小,速度也可以很高。 BiCMOS集成电路:同时包括双极和CMOS晶体管的集成电路为BiCMOS集成电路,综合了双极和CMOS器件两者的优点,但制作工艺复杂。 5、解释基本概念: 微电子、集成电路、集成度、场区、有源区、阱、外延 微电子:微电子技术是随着集成电路,尤其是超大型规模集成电路而发展起来的一门新的技术。微电子技术包括系统电路设计、器件物理、工艺技术、材料制备、自动测试以及封装、组装等一系列专门的技术,微电子技术是微电子学中的各项工艺技术的总和。微电子学是研究在固体(主要是半导体)材料上构成的微小型化电路、电路及微电子系统的电子学分支。 集成电路:通过一系列特定的加工工艺,将晶体管、二极管等有源器件和电阻、电容等无源器件,按照一定的电路互连,“集成”在一块半导体单晶片(如硅或砷化镓)上,封装在一个外壳内,执行特定电路或系统功能。 集成度:集成电路的集成度是指单块芯片上所容纳的元件数目。

74系列芯片引脚图资料大全 作者:佚名来源:本站原创点击数:57276 更新时间:2007年07月26日【字体:大中小】 为了方便大家我收集了下列74系列芯片的引脚图资料,如还有需要请上电子论坛https://www.doczj.com/doc/5d7601268.html,/b bs/ 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373

反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND

集成电路分析 集成工业的前后道技术:半导体(wafer)制造企业里面,前道主要是把mos管,三极管作到硅片上,后道主要是做金属互联。 集成电路发展:按规模划分,集成电路的发展已经历了哪几代? 参考答案: 按规模,集成电路的发展已经经历了:SSI、MSI、LSI、VLSI、ULSI及GSI。它的发展遵循摩尔定律 解释欧姆型接触和肖特基型接触。 参考答案: 半导体表面制作了金属层后,根据金属的种类及半导体掺杂浓度的不同,可形成欧姆型接触或肖特基型接触。 如果掺杂浓度比较低,金属和半导体结合面形成肖特基型接触。 如果掺杂浓度足够高,金属和半导体结合面形成欧姆型接触。 、集成电路主要有哪些基本制造工艺。 参考答案: 集成电路基本制造工艺包括:外延生长,掩模制造,光刻,刻蚀,掺杂,绝缘层形成,金属层形成等。 光刻工艺: 光刻的作用是什么?列举两种常用曝光方式。 参考答案: 光刻是集成电路加工过程中的重要工序,作用是把掩模版上的图形转换成晶圆上的器件结构。 曝光方式:接触式和非接触式 25、简述光刻工艺步骤。 参考答案: 涂光刻胶,曝光,显影,腐蚀,去光刻胶。 26、光刻胶正胶和负胶的区别是什么? 参考答案: 正性光刻胶受光或紫外线照射后感光的部分发生光分解反应,可溶于显影液,未感光的部分显影后仍然留在晶圆的表面,它一般适合做长条形状;负性光刻胶的未感光部分溶于显影液

中,而感光部分显影后仍然留在基片表面,它一般适合做窗口结构,如接触孔、焊盘等。常规双极型工艺需要几次光刻?每次光刻分别有什么作用? 参考答案: 需要六次光刻。第一次光刻--N+隐埋层扩散孔光刻;第二次光刻--P+隔离扩散孔光刻 第三次光刻--P型基区扩散孔光刻;第四次光刻--N+发射区扩散孔光刻;第五次光刻--引线接触孔光刻;第六次光刻--金属化内连线光刻 掺杂工艺: 掺杂的目的是什么?举出两种掺杂方法并比较其优缺点。 参考答案: 掺杂的目的是形成特定导电能力的材料区域,包括N型或P型半导体区域和绝缘层,以构成各种器件结构。 掺杂的方法有:热扩散法掺杂和离子注入法掺杂。与热扩散法相比,离子注入法掺杂的优点是:可精确控制杂质分布,掺杂纯度高、均匀性好,容易实现化合物半导体的掺杂等;缺点是:杂质离子对半导体晶格有损伤,这些损伤在某些场合完全消除是无法实现的;很浅的和很深的注入分布都难以得到;对高剂量的注入,离子注入的产率要受到限制;一般离子注入的设备相当昂贵, 试述PN结的空间电荷区是如何形成的。 参考答案: 在PN结中,由于N区中有大量的自由电子,由P区扩散到N区的空穴将逐渐与N区的自由电子复合。同样,由N区扩散到P区的自由电子也将逐渐与P区内的空穴复合。于是在紧靠接触面两边形成了数值相等、符号相反的一层很薄的空间电荷区,称为耗尽层。简述CMOS工艺的基本工艺流程(以1×poly,2×metal N阱为例)。 参考答案: 形成N阱区,确定nMOS和pMOS有源区,场和栅氧化,形成多晶硅并刻蚀成图案,P+扩散,N+扩散,刻蚀接触孔,沉淀第一金属层并刻蚀成图案,沉淀第二金属层并刻蚀成图案,形成钝化玻璃并刻蚀焊盘。 表面贴装技术:电子电路表面组装技术(Surface Mount Technology,SMT), 称为表面贴装或表面安装技术。它是一种将无引脚或短引线表面组装元器件(简称SMC/SMD,中文称片状元器件)安装在印制电路板(Printed Circuit Board,PCB)的表面或其它基板的表面上,通过再流焊或浸焊等方法加以焊接组装的电路装连技术。[1]工艺流程简化为:印刷-------贴片-------焊接-------检修 有源区和场区:有源区:硅片上做有源器件的区域。(就是有些阱区。或者说是采用STI等隔离技术,隔离开的区域)。有源区主要针对MOS而言,不同掺杂可形成n或p型有源区。有源区分为源区和漏区(掺杂类型相同)在进行互联

74系列芯片引脚图、功能、名称、资料大全(含74LS、74HC等),特别推荐为了方便大家,我收集了下列74系列芯片的引脚图资料。 说明:本资料分3部分:(一)、TXT文档,(二)、图片,(三)、功能、名称、资料。 (一)、TXT文档 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门 LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373

反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘

1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门 74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器 74LS245 │20 19 18 17 16 15 14 13 12 11│ )│ DIR=1 A=>B │ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND

74ls373引脚图管脚功能表 74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片, (1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态); (2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态. 锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~Q7 状态与输入端D1~D7状态相同;当C发生负的跳变时,输入端D0~D7 数据锁入Q0~Q7。51单片机的ALE信号可以直接与74LS373的C连接。74ls373与单片机接口:

1D~8D为8个输入端。1Q~8Q为8个输出端。 G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。 OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。 在MCS-51单片机系统中,常采用74LS373作为地址锁存器使用,其连接方法如上图所示。其中输入端1D~8D接至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允许信号ALE。输出允许端OE接地,表示输出三态门一直打开

在各个领域中常用芯片汇总 1. 音频pcm编码DA转换芯片cirrus logic的cs4344,cs4334,4334是老封装,据说已经停产,4344封装比较小,非常好用。还有菲利谱的8211等。 2. 音频放大芯片4558,833,此二芯片都是双运放。为什么不用324等运放个人觉得应该是对音频的频率响应比较好。 3. 74HC244和245,由于244是单向a=b的所以只是单向驱动。而245是用于数据总线等双向驱动选择。同时245的封装走线非常适合数据总线,它按照顺序d7-d0。 4. 373和374,地址锁存器,一个电平触发,一个沿触发。373用在单片机p0地址锁存,当然是扩展外部ram的时候用到62256。374有时候也用在锁数码管内容显示。 5. max232和max202,有些为了节约成本就用max202,主要是驱动能力的限制。 6. 网络接口变压器。需要注意差分信号的等长和尽量短的规则。 7. amd29系列的flash,有bottom型和top型,主要区别是loader区域设置在哪里?bottom型的在开始地址空间,top型号的在末尾地址空间,我感觉有点反,但实际就是这么命名的。 8. 164,它是一个串并转换芯片,可以把串行信号变为并行信号,控制数码管显示可以用到。 9. sdram,ddrram,在设计时候通常会在数据地址总线上加22,33的电阻,据说是为了阻抗匹配,对于这点我理论基础学到过,但实际上没什么深刻理解。 10. 网卡控制芯片ax88796,rtl8019as,dm9000ae当然这些都是用在isa总线上的。 11. 24位AD:CS5532,LPC2413效果还可以 12. 仪表运放:ITL114,不过据说功耗有点大 13. 音频功放:一般用LM368 14. 音量控制IC. PT2257/9. 15. PCM双向解/编码ADC/DAC CW6691.

反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS24 5 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373 反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│

Y =A+C )│四总线三态门74LS125 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器74LS245 │20 19 18 17 16 15 14 13 12 11│ )│ DIR=1 A=>B │1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND 页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器 正逻辑与门,与非门: Vcc 4B 4A 4Y 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = AB )│ 2输入四正与门74LS08 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 1Y 2A 2B 2Y GND Vcc 4B 4A 4Y 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ __ │14 13 12 11 10 9 8│ Y = AB )│ 2输入四正与非门74LS00 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 1Y 2A 2B 2Y GND Vcc 1C 1Y 3C 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ ___ │14 13 12 11 10 9 8│ Y = ABC )│ 3输入三正与非门74LS10 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 2A 2B 2C 2Y GND

Si4463芯片使用小结 一、芯片介绍 Silicon Labs 的Si4463芯片 是高性能的低电流收发器,其覆盖 了119MHz 至1050 MHz 的 Sub-1GHz频段。还是 EZRadioPRO 系列的一部分,该系 列包含覆盖各种应用的完整发射 器、接收器和收发器产品线。所有 器件都具有杰出的灵敏度-126 dBm,同时实现了极低的活动和休 眠电流消耗。 二、功能实现 1、引脚说明 Si4463有20个引脚,主要引脚功能可以分为两大类:硬件引脚和软件引脚。硬件引脚 主要由电源、射频部分组成,软件引脚主要分为SPI、芯片使能以及GPIO。硬件引脚在原 理图、PCB设计部分需要注意,此处主要是介绍芯片的程序操作,硬件部分就此带过。下 表列举了si4463的21个引脚(包括芯片正下方的Exposed pad引脚)的具体引脚号和功能 简述: 表1 Si4463引脚简述 Si446x Pin Number Pin Name Pin Function Exposed pad, 18 GND Ground 6, 8 VDD Supply input 2,3 Rxp,Rxn used for Rx 4,7 Tx,TXRamp used for Tx 16,17 Xin,Xout crystal 11 NIRQ Interrupt output, active low 1 SDN Shutdown input, active high 15 NSEL SPI select input 12 SCLK SPI clock input

14 SDI SPI data input 13 SDO SPI data output 9 GPIO0 GPIO 10 GPIO1 GPIO 19 GPIO2 GPIO 20 GPIO3 GPIO 2、功能实现 1)SPI操作 芯片的12-15脚为SPI引脚,最大支持速率达到10MHz.芯片支持标准的SPI总线协议,操作方便。 整个芯片的所有SPI操作都可以分成两种方式:写命令和读数据。SPI操作最需要注意的一点是芯片状态,因为芯片不可能随时随地处在SPI就绪状态,所以每次操作SPI时必须读取芯片的当前状态(CTS),确保操作成功。 图CTS读取流程 写命令的流程如下: 图写命令 Si4463至少有28条命令ID,每个命令都有不同的含义,有的可以直接操作芯片执行各项功能,有的可以读取芯片各种状态。上述的读取CTS也是其中一种命令。命令内容详情可参阅Siliconlabs官方文档“AN633.pdf” 读数据流程如下:

总结芯片功能 线性稳压块:2951、LP2951、m5236、2950 开机芯片:东芝TM87XX、IBM:TB6805F、TB6806F、TB6808F、TB62501F、TMP48U I/O芯片:PC97338、PC87391、PC87392、pc87393、SMSC系列:FDC7N869、FDC37N958、LPC47N227、LPC47N267 系统供电芯片:MAX1632、MAX1631、MAX1904、MAX1634、MAX785、MAX786、SB3052、SC1402、LTC1628 CPU供电芯片:MAX1711、MAX1714、MAX1717、MAX1718、MAX1897 供电芯片搭配使用:ADP3203/ADP3415、ADP3410/ADP3421、ADP3410/ADP3422 充电芯片:MAX1645、MAX745、MAX1772、MAX1773、ADP3806、TC490/591、MB3887、MB3878、MAX1908 ,LT1505G CPU温度控制芯片:MAX1617、MAX1020A、AD1030A、CM8500 MAX1989 显卡品牌:ATI、NVIDIA、S3、NEOMAGIC、TRIDENT、SMI、INTEL、FW82807和CH7001A 搭配使用网卡芯片:RTL8100、RTL8139、Intel DA82562、RC82540、3COM、BCM440 网卡隔离:LF8423、LF-H80P、H-0023、H0024、H0019、ATPL-119 声卡芯片:ESS1921、ESS1980S、STAC9704、AU8810、4299-JQ、TPA0202、4297-JQ、8552TS、8542TS、CS4239-KQ、BA7786、AD1981B、AN12942 PC卡芯片:R5C551、R5C552、R5C476、R54472 PC卡供电芯片:TPS2205、TPS2206、TPS2216、TPS2211、PU2211、M2562A、M2563A、M2564A COM口芯片:MAX3243、MAX213、ADM213、HIN213、SP3243、MC145583 键盘芯片:H8C/2471、H8/3434、H8/3431、PC87570、PC87591 键盘芯片:具有开机功能:H8/3434、H8/3437、H8/2147、H8/2149、H8/2161、H8/2168、PC87570、PC87591、H8S/XXX M38857、M38867、M38869 笔记本IO芯片大全PC87591S(VPCQ01)/PC 87591L(VPC01)/PC 97317IBW/PC 87393 VGJ

74 系列芯片的引脚图 [日期:2008-12-29 ] [来源:net 作者:佚名] [字体:大中小] (投递新闻) 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373 反相器: Vcc 6A6Y5A5Y4A4Y六非门74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A)│ │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A1Y2A2Y3A3Y GND 驱动器: Vcc 6A6Y5A5Y4A4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A)│六驱动器(OC高压输出) 74LS07 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A1Y2A2Y3A3Y GND Vcc -4C 4A4Y -3C 3A3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门74LS125 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘

-1C 1A1Y -2C 2A2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐8位总线驱动器74LS245 │20 19 18 17 16 15 14 13 12 11│ )│DIR=1 A=>B │ 1 2 3 4 5 6 7 8 9 10│DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND 页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器 正逻辑与门,与非门: Vcc 4B 4A4Y3B 3A3Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = AB )│2输入四正与门74LS08 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A1B 1Y2A2B 2Y GND Vcc 4B 4A4Y3B 3A3Y ┌┴—┴—┴—┴—┴—┴—┴┐ __ │14 13 12 11 10 9 8│ Y = AB )│2输入四正与非门74LS00 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A1B 1Y2A2B 2Y GND Vcc 1C 1Y3C 3B 3A3Y ┌┴—┴—┴—┴—┴—┴—┴┐ ___ │14 13 12 11 10 9 8│ Y = ABC )│3输入三正与非门74LS10 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A1B 2A2B 2C 2Y GND Vcc H G Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ )│8输入与非门74LS30 │1 2 3 4 5 6 7│________

英文bonding,意译为“芯片打线”邦定是芯片生产工艺中一种打线的方 式,一般用于封装前将芯片内部电路用金线与封装管脚连接,一般bonding后(即电路与管脚连接后)用黑色胶体将芯片封装,同时采用先进的外封装技术COB(Chip On Board),这种工艺的流程是将已经测试好的晶圆植入到特制的电路板上,然后用金线将晶圆电路连接到电路板上,再将融化后具有特殊保护功能的有机材料覆盖到晶圆上来完成芯片的后期封装。此种工艺使用在廉价的产品生产中。在后期的诸多外来因素影响下都会导致此产品诸多品质问题。 观点一:其实邦定这种工艺抗震动和抗潮湿能力极差,寿命短比较短。究其 原因:邦定厂不可能有集成电路封装厂那么好的温湿度、空气净化、防静电条件,邦定的电路板也不可能有集成电路基板的稳定,检测条件也有限。而且芯片一般是来自台湾的一些二流晶圆厂 观点二:邦定封装方式的好处是制成品在防腐、抗震及稳定性方面, 相对于传统SMT贴片方式要高很多。目前大量应用的 SMT贴片技术是将芯片的管脚焊接在电路板上,这种生产工艺不太适合移动存储类产品的加工,在封装的测试中存在虚焊、假焊、漏焊等问题,在日常使用过程中由于线路板上的焊点长期暴露在空气中受到潮湿、静电、物理磨损、微酸腐蚀等自然和人为因素影响,导致产品容易出现短路、断路、甚至烧毁等情况。而邦定芯片是将芯片内部电路通过金线与电路板封装管脚连接,再用具有特殊保护功能的有机材料精密覆盖,完成后期封装,芯片完全受到有机材料的保护,与外界隔离,不存在潮湿、静电、腐蚀情况的发生;同时,有机材料通过高温融化,覆盖到芯片上之后经过仪器烘干,与芯片之间无缝连接,完全杜绝芯片的物理磨损,稳定性更高。 邦定1 板的类型:纤维板——坚实耐用 纸板———比较便宜的板子,很脆,易折断 HUB主要芯片方案:主要品牌慧荣、擎泰、联盛安国、创惟 创惟GL850G简介:拥有低耗电、温度低及接脚数减少等产品特性。它支援4个下游连接埠,采用48pin LQFP封装,可完全支援USB 2.0/1.1规格,因此无论是与主机端或是与其他USB设备介面的传输连接(高速/全速/低速设备传输)皆能完全相容。GL850G同时拥有过载保护功能,提供良好的EMI/ESD处理,亦提供self-power及bus-power 自动侦测模式,使用者将无需作重新插拔的动作。

您的数字ID 是:463099 您的密码是:1.8667 附录三 常用芯片引脚图 一、单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O 接口引脚、4条控制引脚、2条电源引脚、2条时钟引脚。引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时的地址/数据复用口。P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为通用I/O 接口,第二功能作为为单片机的控制信号。 ALE/PROG :地址锁存允许/编程脉冲输入信号线(输出信号) PSEN :片外程序存储器开发信号引脚(输出信号) EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD :复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc :主电源引脚(+5V ) Vss :数字电路地引脚(0V ) Vpd :内部RAM 备用电源引脚(+5V ) V REF :A/D 转换器基准电源引脚(+5V ) AGND :A/D 转换器参考地引脚 XTAL1、XTAL2:内部振荡器反相器输 P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS

第 4 章芯片制造概述 本章介绍芯片生产工艺的概况。(1)通过在器件表面生成电路元件的工艺顺序,来阐述4种最基本的平面制造工艺。(2)解释从电路功能设计图到光刻掩膜版生产的电路设计过程。(3)阐述了晶圆和器件的相关特性与术语。 4.1 晶圆生产的目标 芯片的制造,分为4个阶段:原料制作、单晶生长和晶圆的制造、集成电路晶圆的生产、集成电路的封装。 前两个阶段已经在前面第3章涉及。本章讲述的是第3个阶段,集成电路晶圆生产的基础知识。 集成电路晶圆生产(wafer fabrication)是在晶圆表面上和表面制造出半导体器件的一系列生产过程。 整个制造过程从硅单晶抛光片开始,到晶圆上包含了数以百计的集成电路芯片。 晶圆生产的阶段 4.2 晶圆术语 下图列举了一片成品晶圆。

晶圆术语 晶圆表面各部分的名称如下: (1)器件或叫芯片(Chip,die,device,circuit,microchip,bar):这是指在晶圆表面占大部分面积的微芯片掩膜。 (2)街区或锯切线(Scribe lines,saw lines,streets,avenues):在晶圆上用来分隔不同芯片之间的街区。街区通常是空白的,但有些公司在街区放置对准靶,或测试的结构。 (3)工程试验芯片(Engineering die,test die):这些芯片与正式器件(或称电路芯片)不同。它包括特殊的器件和电路模块用于对晶圆生产工艺的电性测试。 (4)边缘芯片(Edge die):在晶圆的边缘上的一些掩膜残缺不全的芯片。由于单个芯片尺寸增大而造成的更多边缘浪费会由采用更大直径晶圆所弥补。 推动半导体工业向更大直径晶圆发展的动力之一就是为了减少边缘芯片所占的面积。 (5)晶圆的晶面(Wafer Crystal Plane):图中的剖面标明了器件下面的晶格构造。此图中显示的器件边缘与晶格构造的方

FPGA配置芯片 1.Altera FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。 AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持Cyclone系列。使用Altera串行配置器件来完成。Cyclone期间处于主动地位,配置期间处于从属地位。配置数据通过DATA0引脚送入FPGA。配置数据被同步在DCLK 输入上,1个时钟周期传送1位数据。(见附图) PS则由外部计算机或控制器控制配置过程。通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,在PS配置期间,配置数据从外部储存部件,通过DATA0引脚送入FPGA。配置数据在DCLK 上升沿锁存,1个时钟周期传送1位数据。(见附图) JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。 FPGA在正常工作时,它的配置数据存储在SRAM中,加电时须重新下载。在实验系统中,通常用计算机或控制器进行调试,因此可以使用PS。在实用系统中,多数情况下必须由FPGA主动引导配置操作过程,这时FPGA将主动从外围专用存储芯片中获得配置数据,而此芯片中fpga配置信息是用普通编程器将设计所得的pof格式的文件烧录进去。 专用配置器件:epc型号的存储器 常用配置器件:epc2,epc1,epc4,epc8,epc1441(现在好象已经被逐步淘汰了)等 对于cyclone cycloneII系列器件,ALTERA还提供了针对AS方式的配置器件,EPCS系列.如EPCS1,EPCS4配置器件也是串行配置的.注意,他们只适用于cyclone系列. 除了AS和PS等单BIT配置外,现在的一些器件已经支持PPS,FPS等一些并行配置方式,提升配置了配置速度。当然所外挂的电路也和PS有一些区别。还有处理器配置比如JRUNNER 等等,如果需要再baidu吧,至少不下十种。比如Altera公司的配置方式主要有Passive Serial(PS),Active Serial(AS),Fast Passive Parallel(FPP),Passive Parallel Synchronous(PPS),Passive Parallel Asynchronous(PPA),Passive Serial Asynchronous(PSA),JTAG等七种配置方式,其中Cyclone支持的配置方式有PS,AS,JTAG三种. 对FPGA芯片的配置中,可以采用AS模式的方法,如果采用EPCS的芯片,通过一条下载线进行烧写的话,那么开始的"nCONFIG,nSTATUS"应该上拉,要是考虑多种配置模式,可以采用跳线设计。让配置方式在跳线中切换,上拉电阻的阻值可以采用10K 在PS模式下tip:如果你用电缆线配置板上的FPGA芯片,而这个FPGA芯片已经有配置芯片在板上,那你就必须隔离缆线与配置芯片的信号.(祥见下图).一般平时调试时不会把配置芯片焊上的,这时候用缆线下载程序.只有在调试完成以后,才把程序烧在配置芯片中, 然后将芯片焊上.或者配置芯片就是可以方便取下焊上的那种.这样出了问题还可以方便地调试. 在AS模式下tip: 用过一块板子用的AS下载,配置芯片一直是焊在板子上的,原来AS方式在用线缆对配置芯片进行下载的时候,会自动禁止对FPGA的配置,而PS方式需要电路上隔离。 一般是用jtag配置epc2和flex10k,然后epc2用ps方式配置flex10k.这样用比较好.(这是我在网上看到的,可以这样用吗?怀疑中)望达人告知.