标题:Spartan6 FPGA 读写DDR3出现有规律的错误?

问题描述:

1、我在调试DDR3时,用了一片MT41JM16JT-15E的DDR3,此片FLASH与SP605开发板相比MT41JM16JT-187E(本来想定此款的,但是此款没有工业级的)。遇到了如下几个问题:

●用了MIG生成之后DDR3控制器之后,参考ug388和ug416,按照步骤发现数据

全部正确的,灯也正常。

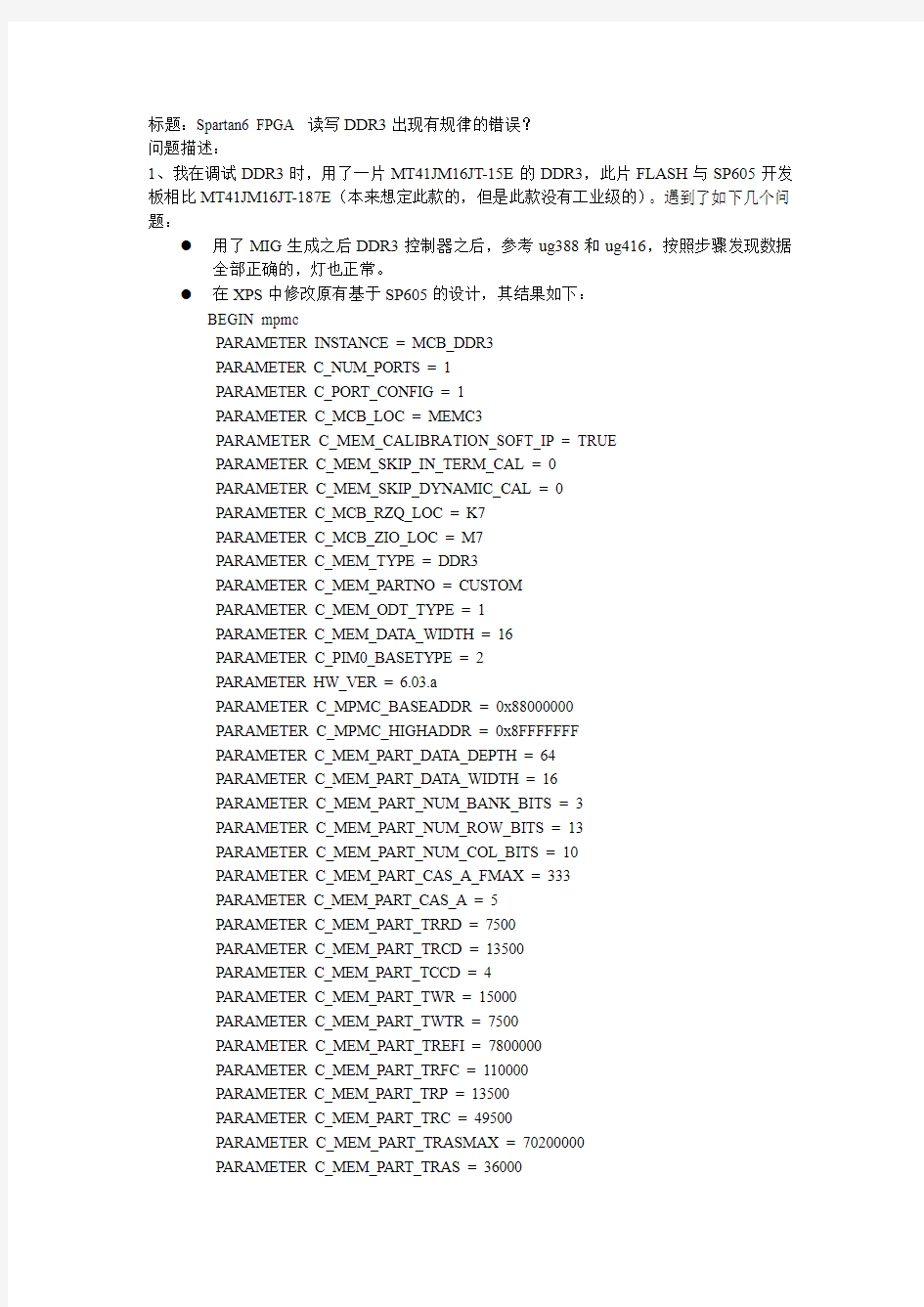

●在XPS中修改原有基于SP605的设计,其结果如下:

BEGIN mpmc

PARAMETER INSTANCE = MCB_DDR3

PARAMETER C_NUM_PORTS = 1

PARAMETER C_PORT_CONFIG = 1

PARAMETER C_MCB_LOC = MEMC3

PARAMETER C_MEM_CALIBRA TION_SOFT_IP = TRUE

PARAMETER C_MEM_SKIP_IN_TERM_CAL = 0

PARAMETER C_MEM_SKIP_DYNAMIC_CAL = 0

PARAMETER C_MCB_RZQ_LOC = K7

PARAMETER C_MCB_ZIO_LOC = M7

PARAMETER C_MEM_TYPE = DDR3

PARAMETER C_MEM_PARTNO = CUSTOM

PARAMETER C_MEM_ODT_TYPE = 1

PARAMETER C_MEM_DATA_WIDTH = 16

PARAMETER C_PIM0_BASETYPE = 2

PARAMETER HW_VER = 6.03.a

PARAMETER C_MPMC_BASEADDR = 0x88000000

PARAMETER C_MPMC_HIGHADDR = 0x8FFFFFFF

PARAMETER C_MEM_PART_DATA_DEPTH = 64

PARAMETER C_MEM_PART_DATA_WIDTH = 16

PARAMETER C_MEM_PART_NUM_BANK_BITS = 3

PARAMETER C_MEM_PART_NUM_ROW_BITS = 13

PARAMETER C_MEM_PART_NUM_COL_BITS = 10

PARAMETER C_MEM_PART_CAS_A_FMAX = 333

PARAMETER C_MEM_PART_CAS_A = 5

PARAMETER C_MEM_PART_TRRD = 7500

PARAMETER C_MEM_PART_TRCD = 13500

PARAMETER C_MEM_PART_TCCD = 4

PARAMETER C_MEM_PART_TWR = 15000

PARAMETER C_MEM_PART_TWTR = 7500

PARAMETER C_MEM_PART_TREFI = 7800000

PARAMETER C_MEM_PART_TRFC = 110000

PARAMETER C_MEM_PART_TRP = 13500

PARAMETER C_MEM_PART_TRC = 49500

PARAMETER C_MEM_PART_TRASMAX = 70200000

PARAMETER C_MEM_PART_TRAS = 36000

BUS_INTERFACE SPLB0 = mb_plb

PORT MPMC_Clk0 = clk_66_6667MHzPLL0

PORT MPMC_Rst = sys_periph_reset

PORT MPMC_Clk_Mem_2x = clk_666_6667MHzPLL0_nobuf

PORT MPMC_Clk_Mem_2x_180 = clk_666_6667MHz180PLL0_nobuf

PORT MPMC_PLL_Lock = Dcm_all_locked

PORT mcbx_dram_addr = fpga_0_MCB_DDR3_mcbx_dram_addr_pin

PORT mcbx_dram_ba = fpga_0_MCB_DDR3_mcbx_dram_ba_pin

PORT mcbx_dram_ras_n = fpga_0_MCB_DDR3_mcbx_dram_ras_n_pin

PORT mcbx_dram_cas_n = fpga_0_MCB_DDR3_mcbx_dram_cas_n_pin

PORT mcbx_dram_we_n = fpga_0_MCB_DDR3_mcbx_dram_we_n_pin

PORT mcbx_dram_cke = fpga_0_MCB_DDR3_mcbx_dram_cke_pin

PORT mcbx_dram_clk = fpga_0_MCB_DDR3_mcbx_dram_clk_pin

PORT mcbx_dram_clk_n = fpga_0_MCB_DDR3_mcbx_dram_clk_n_pin

PORT mcbx_dram_dq = fpga_0_MCB_DDR3_mcbx_dram_dq_pin

PORT mcbx_dram_dqs = fpga_0_MCB_DDR3_mcbx_dram_dqs_pin

PORT mcbx_dram_dqs_n = fpga_0_MCB_DDR3_mcbx_dram_dqs_n_pin

PORT mcbx_dram_udqs = fpga_0_MCB_DDR3_mcbx_dram_udqs_pin

PORT mcbx_dram_udqs_n = fpga_0_MCB_DDR3_mcbx_dram_udqs_n_pin

PORT mcbx_dram_udm = fpga_0_MCB_DDR3_mcbx_dram_udm_pin

PORT mcbx_dram_ldm = fpga_0_MCB_DDR3_mcbx_dram_ldm_pin

PORT mcbx_dram_odt = fpga_0_MCB_DDR3_mcbx_dram_odt_pin

PORT mcbx_dram_ddr3_rst = fpga_0_MCB_DDR3_mcbx_dram_ddr3_rst_pin

PORT rzq = fpga_0_MCB_DDR3_rzq_pin

PORT zio = fpga_0_MCB_DDR3_zio_pin

END

但是程序进入DDR3运行时发现程序跑飞。

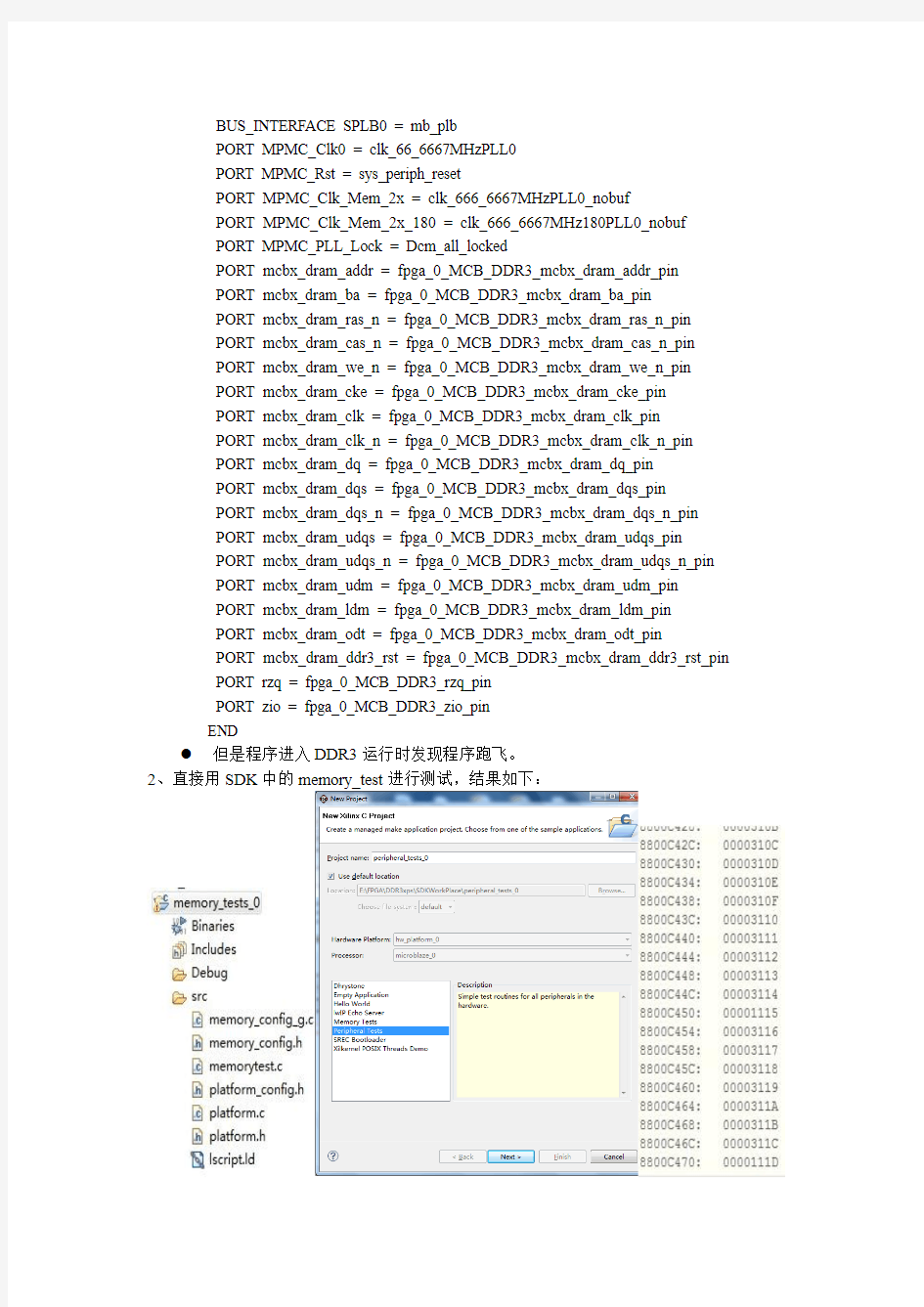

2、直接用SDK中的memory_test进行测试,结果如下:

结论:很明显在0x8800C450和0x8800C470地址时,数据发生了变异。

注:DDR3为64M*16的,其在FPGA中的基地址为:0x88000000 - 0x8FFFFFFF

从0x8F000000开始测试的结果,基本一致。

3、MIG中配置的DDR3如下:所用的DDR3型号为:MT41J64M16JT-15E IT:GTR

4、继续测试发现如下结果:

结论:第一个0x88000000数据不用管

左图可以看出,在每次地址后4位为0时(即每次16个字节第一个字节),就会出现问题;

右图可以看出当高16位数据与低16位数据一致时,数据就正常。

5、某天不经意间将这块板卡的3.3V电源换成2.5V电源,发现DDR3工作正常了。非常奇怪。

●修改之前电源方案:Spartan6的BANK0,BANK1,BANK2为3.3V;BANK3为

1.5V。DDR3中的供电电源如下图:

●修改之后的电源方案为:Spartan6的BANK0,BANK1,BANK2为2.5V;BANK3

为1.5V。

DDR3的供电为上图中的VCC3V3变成2.5V。其他均不变。此时DDR3工作

正常。

6、期间还做过两个实验,将SP605开发板的电源变成3.3V,开发板上DDR3工作正常。说明Spartan6支持其他BANK供电3.3V,DDR3 BANK供电1.5V。另一个实验为,将自己画的那块板卡上的DDR3芯片换成完全与开发板一致的芯片,问题没有结果,说明不是MIG

或者是控制器的问题。

7、基于以上的分析和定位是否能确定问题基本就是PCB的问题,但是PCB我们是严格按照DDR3布板的要求去画的,期间也改过一版的。

8、希望调试过DDR3或者对这个问题有见解的给予帮助,谢谢。如果涉及到大量工作的,可以通过双方合作的形式展开。

9、附件为问题的WORD版,因为图片好像无法上传。

其他模块原理图,PCB图以及DDR3电源芯片资料。若需要可以联系我。

联系方式:QQ:309602530。Email:zhangyibing1986090@https://www.doczj.com/doc/5b12086636.html,。

若能帮助解决问题有重谢,谢谢。

差分对的约束设置 第一步,差分对的设置 差分对的设置有很多方法,下面介绍两种最常用的方法。 1.点击菜单Logic→Assign Differential Pair... 弹出以下对话框。 点击你想要创建差分对的Net1和Net2,填入差分的名字,点击Add后就成功创建了差分对。 点击Auto Generate按钮后,弹出以下对话框:

在第一个输入框填入Net的主要名字后,在下面的框中填入差分线的标志如N,P。点击Generate即可自动产生差分对。 2.在约束管理器中设置差分对。 在DSN上点击右键,在菜单中选择Create→Differential Pair。即可弹出下面的对话框。

和上一种方法的设置差不多,这里就不再叙述了。 第二步差分对约束规则的设置 差分对各项约束可以在约束管理器中的 Electric→Net→routing→Differential Pair中直接在各差分对上填入各项约束数值就可生效,但更好的方法是创建约束规则后赋给各个差分对。 在DSN上点击右键,在菜单中选择Create→Electrical CSet后,弹出下面的对话框; 输入规则名后点Ok,在Electric→constraimt set→outing→Differential Pair中可以看到新规则。 在表格中输入各项数值即可完成新规则的设置。如图所示 差分对约束参数主要有以下几个:

1coupling paramaters 主要包括了 Primary Gap 差分对最优先线间距(边到边间距)。 Primary Width 差分对最优先线宽。 Neck Gap 差分对Neck模式下的线间距(边到边间距),用于差分对走线在布线密集区域时切换到Neck值。 Neck Width差分对Neck模式下的线宽,用于差分对走线在布线密集区域时切换到Neck值。如图所示 设置数值时在表格中右键菜单中选择change,会出现以下各层数值表格,可以在每一层上设置不同的数值。 需要注意的是在物理(physical)约束中同样可以设置差分规则,但是电气规则约束在布线时更优先,同时电气规则可以设置更多的约束,推荐在电气规则中设置差分走线的约束。 2 Min Line Specing 差分对最小间距,一定要小于或等于"Primary gap"与(-)tolerance的数值,并且也要小于或等于"Neck gap"与(-)tolerance的数值。对于不符合约束的差分对,会显示“DS”的DRC错误提示。

程序流程图规范 1.引言 国际通用的流程图形态和程序: 开始(六角菱型)、过程(四方型)、决策(菱型)、终止(椭圆型)。在作管理业务流程图时,国际通用的形态:方框是流程的描述;菱形是检查、审批、审核(一般要有回路的);椭圆一般用作一个流程的终结;小圆是表示按顺序数据的流程;竖文件框式的一般是表示原定的程序;两边文件框式的一般是表示留下来的资料数据的存储。 2.符号用法 程序流程图用于描述程序内部各种问题的解决方法、思路或算法。 图1-1 标准程序流程图符号 1)数据:平行四边形表示数据,其中可注明数据名、来源、用途或其 它的文字说明。此符号并不限定数据的媒体。 2)处理:矩形表示各种处理功能。例如,执行一个或一组特定的操作,

从而使信息的值,信息形式或所在位置发生变化,或是确定对某一流向的选择。矩形内可注明处理名或其简要功能。 3)特定处理:带有双纵边线的矩形表示已命名的特定处理。该处理为 在另外地方已得到详细说明的一个操作或一组操作,便如子例行程序,模块。矩形内可注明特定处理名或其简要功能。 4)准备:六边形符号表示准备。它表示修改一条指令或一组指令以影 响随后的活动。例如,设置开关,修改变址寄存器,初始化例行程序。 5)判断:菱形表示判断或开关。菱形内可注明判断的条件。它只有一 个入口,但可以有若干个可供选择的出口,在对符号内定义各条件求值后,有一个且仅有一个出口被激活,求值结果可在表示出口路径的流线附近写出。 6)循环界限:循环界限为去上角矩形或去下角矩形,分别表示循环的 开始和循环的结束。一对符号内应注明同一循环标识符。可根据检验终止循环条件在循环的开始还是在循环的末尾,将其条件分别在上界限符内注明(如:当A>B)或在下界限符内注明(如:直到C Allegro 16.3约束规则设置 约束管理器是一个交叉的平台,以工作簿和工作表的形式在 Cadence PCB设计流程中用于管理所有工具的高速电子约束。可以使用约束管理器和SigXplorer Expert 开发电路的拓扑并得出电子约束,可以包含定制约束、定制测量和定制激励。 所谓约束就是用户定义的限制条件,当在板上走线和放置元件时会遵守这些约束。电子约束(ECSets)就是限制PCB 上与电行为有关的对象,比如可以设置某个网络最大传输延迟为2ns。 以下图为一约束设置窗口。 一、说明 先解释一下约束的类型以及约束中用到的简写名词,如下图所示: 1、NCIs(NET CLASS) 由众多nets或者buses、differential pairs、Xnet所组成的类,可对其赋予相似的约束。如下图所示。 2、NCC(Net Class-Class) 一般用在约束组与组之间的间距的时候使用,如下图。 3、DPr(Differential Pairs)差分对 一组差分对一般由两条Xnet或者net以差分走线的方式组成,如下图。差分对的形成有两种方式:一是由模型指定的差分对,再者就是由用户自己定义的差分对。 ?模型定义的差分对:可以在器件信号模型中指定差分对,可以使用PCB Design,PCB SI,SigXplores 来将模型指定给相应的元件。 ?用户定义的差分对:可以在约束管理器中 Net 一级的对象中创建差分对,可以灵活的更改差分对命名和更改差分对成员,但是没有模型指定差分对的精确性。 以下是设置差分对规则时,需要赋予约束的项。 针对以上约束中用到的一些约束点进行解释说明: 1 流水灯流程框图: N Y 流水灯程序: /*********************************************************** 描述 : LED 流水灯的控制; 8个LED 会进行流水灯的演示; ***********************************************************/ #include #define uint unsigned int sbit PP=P3^6 ; /*********************************************************** * 名称 : Delay() * 功能 : 延时,延时时间为 10ms * del * 输入 : del * 输出 : 无 ***********************************************************/ void Delay(uint del) { uint i,j; for(i=0; i Allegro16.6约束规则设置详解 前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。 目录: 一、基本约束规则设置 1、线间距设置 2、线宽设置 3、设置过孔 4、区域约束规则设置 5、设置阻抗 6、设置走线的长度范围 7、设置等长 7.1、不过电阻的NET等长 7.2、过电阻的XNET等长 7.3、T型等长 8、设置通用属性 9、差分规则设置 9.1、创建差分对 9.2、设置差分约束 10、Pin Delay 二、高级约束规则设置 11、单个网络长度约束 12、a+b类长度约束 13、a+b-c类长度约束 14、a+b-c在最大和最小传播延迟中的应用 1、线间距设置 (1)、设置默认间距规则 点击CM图标,如下图所示,打开约束管理器。 单击Spacing,再点击All Layers,如下图所示。右边有一个DEFAULT就是默认规则,我们可以修改其值。 按住Shift键,点击第一个和最后一个即可选中所示,然后输入一个值,这样就都修改了,如下图所示 (2)、定义特殊的间距约束 点选Default按鼠标右键,执行Create-Spacing CSet 加入新规则。取一个有意义点的名字,如下图所示,单击OK。 其值是从默认规则拷贝的,先修改其值。 按住Shift键选中所有,输入12,回车。 然后为所需要设置的网络分配规则 单击左边的Net-All Layers,在右边工作簿中,为GND网络设置12MIL_SPACE规则,在Referenced Spacing CSet下选中12MIL_SPACE,如下图所示 系统总体业务流程图 图 1-1: 系统初始化流程说明 1-1: 目标进行系统初始化,使系统进入可处理正常业务状态。 业务背景系统安装后,系统的参数、基础资料等都没有,系统还不能处理具体的业务。用户必须根据实际的业务管理需要,设置系统控制参数、科目、核算项目等后,才能处理正常业务。 适用 范 围 在系统启用之前,适用所有的行业。 序号责任部门责任人1 启用账套——启用账套,设置账套期间财务/IT部系统管理 员 2 系统参数设置——设置系统参数财务/IT部系统管理 员 3 用户设置——将系统用户和每个用户的权限在系统中 设定 财务部主管会计 4 币别设置——在系统中设置币别财务部总账会计 5 核算项目、科目设置——在系统中设置科目和核算项 目 财务部主管会计 6 期初数据录入——将期初余额录入系统财务部主管会计 7 数据检查——系统检查期初余额是否平衡,数据是否 正确还需人工做进一步的检查。 财务部主管会计 凭证处理业务流程说明相关内容见表2-2: 目标实现凭证的生成、审核、过账和修改所有的操作 业务背景用户在实现初始化之后,系统已成功启用。财务人员需要以凭证的方式记录公司发生的实际经济业务。同时,按照实际的工作要求,对凭证进行审核、过账,发现错误进行修改。 适用范围1.1、各种方式产生的凭证,包括手工凭证、系统生成凭证、模式凭证、自动转 账凭证、外部引入凭证、凭证冲销等6种方式产生的凭证。 2.2、凭证的所有处理业务,凭证的生成、审核、过账、修改和删除。 序号责任部门责任人 1 新增凭证——手工录入、引入或者系统产生的凭证。财务部会计 2 凭证查询——查询符合条件的凭证财务部财务人员 3 凭证审核——会计主管审核系统内的凭证财务部总账会计 4 凭证反审核——发现已审核的凭证错误,将其反审核, 进入可修改状态 财务部主管会计 5 凭证过账——将符合条件的凭证登记到账薄财务部主管会计 6 凭证反过账——发现已过账的凭证错误,将其反过账, 进入可修改状态 财务部主管会计 凭证录入与审核 业务流程图 流程图 本标准等同采用国际标准ISO 5807—1985《信息处理一数据流程图、程序流程图、系统流程图程序网络图、系统资源图的文件编制符号及约定》。 l 引言 图可广泛用于描绘各种类型的信息处理问题及其解决方法。图的使用并不局限于本标准中所给的 示例 在应用中,所确定的内部规则必须满足实际的处理或数据规格说明。本标准中给出一些指导性原 则,遵循这些原则可以增强图的可读性,有利于图与正文的交叉引用。 图中包含具有确定含义的符号、简单的说u性文字和各种连线。本标准不涉及说明性文字的内容, 但每个符号有一个无歧义。有意义的名称,它在整个文件编制中都是一致的。 图可以分为洋细程度不同的层次,层次的数目取决于信息处理问题的规模和复杂性。这些详细程 度不同的层次应用使得不同部分及各部分间相互关系可作为一个整体来理解。 正常情况下,要有一个表明整个系统主要组成部分的图,该图作为层次图形的顶层图。每一较低 层都对上一层的一个或几个部分进行详细的描述。 2 范围和应用领域 本标准规定在信息处理文件编制中使用的各种符号,并给出在下列图中使用这些符号的约定: a.数据流程图; b.程序流程图; c.系统流程图; d.程序网络图; e.系统资源图。 3 引用标准 GB 5271.1—85数据处理词汇 01部分基本术语 4 术语 GB 5271.1中的术语以及下述术语适用于本标准。 4.1 基本符号 当处理或数据媒体的精确性质或形式未知时,或者当不需要描述实际的媒体时所使用的符号。 4.2 特定符号 当处理或数据媒体的精确性质或形式已经知道时,或者当需要描述实际的媒体时所使用的符号。 4.3 流程图 对某一个问题的定义、分析或解法的图形表示,图中用各种符号来表示操作、数据、流向以及装 置等。 5 数据流程图 数据流程图表示求解某一问题的数据通路。同时规定了处理的主要阶段和所用的各种数据媒体。 数据流程图包括: a.指明数据存在的数据符号,这些数据符号也可指明该数据所使用的媒体; b.指明对数据执行的处理的处理符号,这些符号也可指明该处理所用到的机器功能; c.指明几个处理和(或)数据媒体之间的数据流的流线符号; 给HC_操行分表增加约束唯一约束和聚集索引 首先唯一性约束不能为空 修改某列的定义 alter table HC_操行分表 alter column HC_姓名varchar(10)not null go alter table HC_操行分表 add constraint PK_caoxingfen primary key Clustered(HC_姓名) go 给操行分定义一个约束,操行分不能超过或不能低于分 alter table HC_操行分表 alter column HC_成绩int not null go alter table HC_操行分表 add constraint CK_checkNum check(HC_成绩between 0 and 100) go ---创建规则绑定到指定的列上 create rule CK_checkNum as @score1 between 0 and 100 GO exec sp_bindrule'CK_checkNum','HC_操行分表.HC_成绩' -给HC_会员信息表增加约束和规则,限制性别为男和女 规则 create rule SexLimit as @sexl in('男','女') GO exec sp_bindrule'SexLimit','HC_会员信息表.HC_性别' GO 约束 alter table HC_会员信息表 add constraint CK_sexlimit check(HC_性别in('男','女')) go ----给电话增加约束为[][][][][][]的形式的约束 alter table HC_会员信息表 add constraint CK_phoNum 前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。 目录: 一、基本约束规则设置 1、线间距设置 2、线宽设置 3、设置过孔 4、区域约束规则设置 5、设置阻抗 6、设置走线的长度范围 置详解(图文并茂) 则设约束规.616o r g Alle (为了不侵犯别人的成果,所以在这里做了特殊说明,以示敬意)首先感谢詹书庭编写这篇文章,为我们学习交流Cadence allegro 苦用心! 俗话说的好,社会在发展,技术在进步,技术的进步在于不断的学习交流和实践。所以为了方便大家学习交流,为大家提供一个良好 QQ )! 学习交流 Cadence allegro 请加QQ 群: 一起来学AllegRo 【2】.群号: 331730476 .以下是正文 这篇文章写得很好,操作步骤详细,截图一目了然,通俗易懂,唯一的缺点就是部分截图不是很清晰,我对个别图片做了调整和替 换,不易替换的不清晰图片,仔细看下也能明白其中的意思。 此文章由丹心静居整理---2014.10.13 加入。对原文作者表示歉意的交流平台,在这里留下我们的群原文作者的群拒绝任何人 (QQ 软件提供了丰富的知识和方法。请大家认真学习,不要辜负作者的良 2014-10-13 第 1 页,共 83 页 二、高级约束规则设置 11、单个网络长度约束 12、a+b 类长度约束 13、a+b-c 类长度约束 14、a+b-c 在最大和最小传播延迟中的应用 y a l e D n i P 、10约束分差设置、.29分对差创建、.19设置则分规差、 9属性用置通设、 8等长型T 、.37等长NET X 阻的过电、.27等长NET 阻的电不过、.17置等长 设、 7 约束规则设置 约束管理器是一个交叉的平台,以工作簿和工作表的形式在 Cadence PCB设计流程中用于管理所有工具的高速电子约束。可以使用约束管理器和SigXplorer Expert 开发电路的拓扑并得出电子约束,可以包含定制约束、定制测量和定制激励。 所谓约束就是用户定义的限制条件,当在板上走线和放置元件时会遵守这些约束。电子约束(ECSets)就是限制PCB 上与电行为有关的对象,比如可以设置某个网络最大传输延迟为2ns。 以下图为一约束设置窗口。 一、说明 先解释一下约束的类型以及约束中用到的简写名词,如下图所示: 由众多nets或者buses、differential pairs、Xnet所组成的类,可对其赋予相似的约束。如下图所示。 2、NCC(Net Class-Class) 一般用在约束组与组之间的间距的时候使用,如下图。 3、DPr(Differential Pairs)差分对 一组差分对一般由两条Xnet或者net以差分走线的方式组成,如下图。差分对的形成有两种方式:一是由模型指定的差分对,再者就是由用户自己定义的差分对。 ?模型定义的差分对:可以在器件信号模型中指定差分对,可以使用PCB Design,PCB SI,SigXplores 来将模型 指定给相应的元件。 ?用户定义的差分对:可以在约束管理器中 Net 一级的对象中创建差分对,可以灵活的更改差分对命名和更改差分对成员,但是没有模型指定差分对的精确性。 以下是设置差分对规则时,需要赋予约束的项。 针对以上约束中用到的一些约束点进行解释说明: 差分对的worksheets包含5个主要的约束目录: (1)Pin Delay 此值指一对网络之间管脚封装上的延迟,单位是时间ns 或者长度mil。 (2) 不耦合长度(Uncoupled Length) 不耦合长度约束是用来限制差分对的一对网络之间的不匹配长度。若“gather control”设置为ignore,则实际不不耦合长度不包括两个驱动和接收之间的耦合带之外的长度。若“gather control”设置为“include”,包含出芯片的这段不耦合长度。当不耦合(即在差分对刚刚从芯片出来的走线通常是不耦合的,不耦合有一定的长度)长度超过“max”时产生冲突。 (3)相位偏差(Static Phase Tolerance) 相位偏差约束确保差分对成员在转换时是同相和同步的。实际的数值(actual value)从长度上或者时间上反应了差分对成员之间的差值,当差值超出 tolerance 值时,就会有冲突。 (4)最小线间距(Min Line Spacing) 最小线间距约束指差分对之间的最小距离,如果小于设定的最小值则报错。添加的最小线间距约束值必须小于或者等于Primary Gap减去(-)Tolerance,并且也要小于或者等于Neck Gap减去(-)Tolerance。 (5)耦合参数(Coupling Parameters) 这里面包括6个部分需要设置。1、Primary gap :设置的是差分对之间的边到边理想间距,(+/-)tolerance 值是允许Diff Pairs的偏差值,如果间距偏差在范围内,差分对被认为是耦合的;2、Primary width:差分对成员的理想宽度;3、Neck gap:约束的是最小允许的边到边的差分间距,当在密集区域走线时,可能切换到neck模式,最小可允许的gap 包括Neck Gap 减去(-)Tolerance,当差分对间距小于ECSet 指定给差分对网络的Min neck width 规则值时,Neck Gap 覆盖任何Primary Gap 值,确保 Neck gap 不要低于任何Min line spaing 值,如果设置了(-)tolerance 值,不需要定义Neck gap ,因为已经说明了需要的Neck gap。;4、Neck width:最小可允许的差分对宽度,当在比较密集的区域走线的时,可能需要切换到neck模式;5、(+)Tolerance;6、(-)Tolerance。 使用差分计算器可以完成综合线宽和线距的计算以获得特殊的差分阻抗。在约束管理器中右键点击Primary Gap, 1-1: 系统总体业务流程图图1-1: 系统初始化流程说明 目标进行系统初始化,使系统进入可处理正常业务状态。 业务背景系统安装后,系统的参数、基础资料等都没有,系统还不能处理具体的业务。用户必须根据实际的业务管理需要,设置系统控制参数、科目、核算项目等后,才能处理正常业务。 适用 范围 在系统启用之前,适用所有的行业。 序号责任部门责任人1启用账套——启用账套,设置账套期间财务/IT部系统管理 员 2系统参数设置——设置系统参数财务/IT部系统管理 员 3用户设置——将系统用户和每个用户的权限在系统中 设定 财务部主管会计4币别设置——在系统中设置币别财务部总账会计5核算项目、科目设置——在系统中设置科目和核算项 目 财务部主管会计6期初数据录入——将期初余额录入系统财务部主管会计7数据检查——系统检查期初余额是否平衡,数据是否 正确还需人工做进一步的检查。 财务部主管会计 相关内容见表 2-2: 凭证处理业务流程说明 凭证录入与审核 业务流程图 目 标 实现凭证的生成、审核、过账和修改所有的操作 业务 背 景 用户在实现初始化之后,系统已成功启用。财务人员需要以凭证的方式记录公司 发生的实际经济业务。同时,按照实际的工作要求,对凭证进行审核、过账,发 现错误进行修改。 适用 范 围 1. 1、各种方式产生的凭证,包括手工凭证、系统生成凭证、模式凭证、自动 转账凭证、外部引入凭证、凭证冲销等 6 种方式产生的凭证。 2. 2、凭证的所有处理业务,凭证的生成、审核、过账、修改和删除。 序 号 责任部门 责任人 1 新增凭证——手工录入、引入或者系统产生的凭证。 财务部 会计 2 凭证查询——查询符合条件的凭证 财务部 财务人员 3 凭证审核——会计主管审核系统内的凭证 财务部 总账会计 4 凭证反审核——发现已审核的凭证错误,将其反审核, 进入可修改状态 财务部 主管会计 5 凭证过账——将符合条件的凭证登记到账薄 财务部 主管会计 6 凭证反过账——发现已过账的凭证错误,将其反过账, 进入可修改状态 财务部 主管会计 C o n s t r a i n t M a n a g e r 约束规则基本设置 Revised by Petrel at 2021 约束规则的设置 孙海峰在PCB设计中规则设置是必不可少的,它也可以被称为DRC检查规则,用来确定电路板的走线规则是否符合设计要求。在AllegroPCB的电路板设计过程中,设计约束规则主要包括时序规则、走线规则、间距规则、信号完整性规则等以及物理规则等设置。 首先,需要认识一下,AllegroPCB的约束管理器: 在PCB设计界面中,执行Setup/Constraints/ConstraintManager命令,弹出AllegroConstraintManager对话框,如下图。 在约束管理器中,设计者可以对电路板的电气规则、物理规则、间距规则等设计规则进行设置定义。约束规则可以按板层、网络或者区域进行设置。 约束管理器是Cadence系统提供的专用规则设置系统,主要有菜单栏、工具栏、工作表选择区、工作状态报告栏四部分,在工作表中选择一个对象,然后右击,在弹出的命令菜单中,可以进行任意操作。 工作表选择区内可以选择电气规则、物理规则、间距规则等规则设置。在对应Net文件夹内,可以创建指定网络的对象分组,如:系统、设计、总线、差分对、扩展网络(XNet)、网络、相对或匹配群组,也可以创建基于相关属性的电气规则(ECSet)、物理规则(PCSet)、间距规则(SCSet)等。 约束管理器的约束对象分为引脚对、总线和匹配群组,她们相互之间存在优先级差异,即底层对象会集成顶层对象指定约束,为底层对象指定的约束优先高于上层继承的约束,对象层次的优先级为系统、设计、总线、差分对、扩展网络、相对或匹配群组、引脚对。 一、电气规则设置 在约束管理器中,选择Electrical选项卡,其中可以为设计或网络来设置时序规则、信号完整性规则、布线的电气规则(延时、差分对)等,执行Objects/Create/ElectricalCSet命令可新建电气规则。 Allegro16.3约束设置 Allegro16.3约束设置差分对的约束设置第一步,差分对的设置差分对的设置有很多方法,下面介绍两种最常用的方法。1.点击菜单Logic→Assign Differential Pair... 弹出以下对话框。点击你想要创建差分对的Net1和Net2,填入差分的名字,点击Add后就成功创建了差分对。点击Auto Generate按钮后,弹出以下对话框:在第一个输入框填入Net的主要名字后,在下面的框中填入差分线的标志如N,P。点击Generate即可自动产生差分对。2.在约束管理器中设置差分对。在DSN上点击右键,在菜单中选择 Create→Differential Pair。即可弹出下面的对话框。和上一种方法的设置差不多,这里就不再叙述了。第二步差分对约束规则的设置差分对各项约束可以在约束管理器中的Electric→Net→routing→Differential Pair中直接在各差分对 上填入各项约束数值就可生效,但更好的方法是创建约束规则后赋给各个差分对。在DSN上点击右键,在菜单中选择Create→Electrical CSet后,弹出下面的对话框;输入规则名后点Ok,在Electric→constraimt set→outing→Differential Pair中可以看到新规则。在表格中输入各项数值即可完成新规则的设置。如图所示差分对约束参数主要有以下几个: 1coupling paramaters 主要包括了Primary Gap 差分对最 优先线间距(边到边间距)。Primary Width 差分对最优先线宽。Neck Gap 差分对Neck模式下的线间距(边到边间距),用于差分对走线在布线密集区域时切换到Neck值。Neck Width差分对Neck模式下的线宽,用于差分对走线在布线 密集区域时切换到Neck值。如图所示设置数值时在表格中右键菜单中选择change,会出现以下各层数值表格,可以 在每一层上设置不同的数值。需要注意的是在物理(physical)约束中同样可以设置差分规则,但是电气规则约束在布线时更优先,同时电气规则可以设置更多的约束,推荐在电气规则中设置差分走线的约束。2 Min Line Specing 差分对最小间距,一定要小于或等于"Primary gap"与(-)tolerance的数值,并且也要小于或等于"Neck gap"与(-)tolerance的 数值。对于不符合约束的差分对,会显示“DS”的DRC错误 提示。3 Dynamic Phase:动态相位检查,在16.3版本新加 入的功能。对差分对路径中每个转角之间造成的路径差异进行检查。如在整个差分对网络中,正向与反向之间的走线差距不能超过“x mils”。如果整个路径中的某一个位置,发生了两个信号之间相位偏移超过了规定的“x mils”,这个误差必须在“y mils”范围内补偿回来。如下图x=20,y=600.设定约束 时tolerance填入x值,max length填入y值。对于不符合 约束的走线的路径会以高亮显现,并且显示DY错误。4 Static Phase Tolerance 这个约束设置了两根差分线之间的差值, 程序流程图规范 1. 引言 国际通用的流程图形态和程序: 开始(六角菱型)、过程(四方型)、决策(菱型)、终止(椭圆型)在作管理业务流程图时,国际通用的形态:方框是流程的描述;菱形是检查、审批、审核(一般要有回路的);椭圆一般用作一个流程的终结;小圆是表示按顺序数据的流程;竖文件框式的一般是表示原定的程序;两边文件框式的一般是表示留下来的资料数据的存储。 2. 符号用法 程序流程图用于描述程序内部各种问题的解决方法、思路或算法 /1irn O ③特毎处理 a匸O CZZ)■ ■ ■冃— 勒箝环(上〉 界礙⑥纸环(下) ⑨t£A? 苻 ?rm 图1-1 标准程序流程图符号 1)数据:平行四边形表示数据,其中可注明数据名、来源、用途或其它的文字说明。此符号并不限定数据的媒体。 2)处理:矩形表示各种处理功能。例如,执行一个或一组特定的操作, 从而使信息的值,信息形式或所在位置发生变化,或是确定对某一 流向的选择。矩形内可注明处理名或其简要功能。 3)特定处理:带有双纵边线的矩形表示已命名的特定处理。该处理为在另外地方已得到详细说明的一个操作或一组操作,便如子例行程序,模块。 矩形内可注明特定处理名或其简要功能。 4)准备:六边形符号表示准备。它表示修改一条指令或一组指令以影响随后的活动。例如,设置开关,修改变址寄存器,初始化例行程序。 5)判断:菱形表示判断或开关。菱形内可注明判断的条件。它只有一个入口,但可以有若干个可供选择的出口,在对符号内定义各条件求值后,有一个且仅有一个出口被激活,求值结果可在表示出口路径的流线附近写出。 6)循环界限:循环界限为去上角矩形或去下角矩形,分别表示循环的开始和循环的结束。一对符号内应注明同一循环标识符。可根据检验终止循环条件在循环的开始还是在循环的末尾,将其条件分别在 上界限符内注明(如:当A>B)或在下界限符内注明(女口:直到C ALLEGRO约束规则设置步骤(以DDR为例) Dyyxh@pcbtech tzyhust@https://www.doczj.com/doc/5b12086636.html, 本文是我对约束规则设置方面的一些理解,希望对新手能有所帮助。由于本人水平有限,错误之处难免,希望大家不吝赐教! 在进行高速布线时,一般都需要进行线长匹配,这时我们就需要设置好constraint规则,并将这些规则分配到各类net group上。下面以ddr为例,具体说明这些约束设置的具体步骤。1.布线要求 DDR时钟: 线宽10mil,内部间距5mil,外部间距30mil,要求差分布线,必需精确匹配差分对走线误差,允许在+20mil以内 DDR地址、片选及其他控制线:线宽5mil,内部间距15mil,外部间距20mil,应走成菊花链状拓扑,可比ddrclk线长1000-2500mil,绝对不能短 DDR数据线,ddrdqs,ddrdm线:线宽5mil,内部间距15mil,外部间距20mil,最好在同一层布线。数据线与时钟线的线长差控制在50mil内。 2.根据上述要求,我们在allegro中设置不同的约束 针对线宽(physical),我们只需要设置3个约束:DDR_CLK, DDR_ADDR, DDR_DATA 设置好了上述约束之后,我们就可以将这些约束添加到net上了。点击physical rule set 中的attach……,再点击右边控制面板中的more, 弹出对话框 如上图所示,找到ckn0和ckp0,点击apply,则弹出 选中左边列表中的NET_PHYSICAL_TYPE, 在右边空格内输入DDR_CLK, 点击apply,弹出 即这两个net已经添加上了NET_PHYSICAL_TYPE属性,且值为DDR_CLK. 类似的,可以将DDR数据线,数据选通线和数据屏蔽线的NET_PHYSICAL_TYPE设为DDR_DATA, DDR地址线,片选线,和其他控制线的NET_PHYSICAL_TYPE设为DDR_ADDR. 上述步骤完成后,我们就要将已经设好的约束分配到这些net group上。 如下图点击assignment table…… 图1-1: 系统初始化流程说明1-1: 相关内容见表2-2: 凭证录入与审核 业务流程图 流程说明 相关内容见表2-3: 规程 目标 确保原始数据以凭证形式变为软件数据,并通过审核得以确认。 业务背景1.已建立会计制度; 2.原始凭据真实、合法、完整; 规程适用范围1.直接由普通原始凭据制作凭证; 2.由软件的业务数据生成凭证或由手工录入此类凭证; 序号处理说明责任部门责任人1根据已审核过的原始凭据,在K/3系统\总账系统\凭 证录入中录入凭证并自检,或检查由系统自动生成凭 证的准确性。 财务部总账会计 2要求当天的业务凭据,当天生成或录入总账凭证。财务部总账会计3原始凭据真实、合法、有效。财务部总账会计4会计记账凭证的编制期不能早于实际业务的发生期。财务部总账会计5审核录入凭证是否信息完整准确。财务部主管会计6如凭证录入有问题,则通知制单人依据原始凭据检查 和修改凭证,此工作要求在1个工作日内完成。 财务部主管会计 7如凭证录入无问题,则在K/3系统\凭证查询功能中对 已录入凭证进行审核,此工作要求在凭证检查无误后 1个工作日内完成。 财务部主管会计 表 2-3 凭证反审核业务 凭证反审核业务流程图 流程说明 相关内容见表2-4: 规程 目标 对发现问题的已审核凭证进行反审核,使之返回至未审核状态以便于改正。 业务背景已审核的凭证在账簿生成或报表生成等后续处理过程中发现有误;问题凭证为已审核凭证或已过账凭证; 规程适用范围1.审核与反审核必须为同一人; 2.如果此凭证已过账,则需先反过账后再反审核; 3.适用于本会计期间修改或跨会计期间修改; 序号处理说明责任部门责任人 第一部分金蝶供应链初始化流程介绍 教学目的:通过学习掌握供应链与其他系统的联系 教学要求:了解各模块间的联系 教学重点、难点:供应链与其他系统的联系 教学内容:整体操作流程 整体操作流程 第二部分供应链系统初始化处理 教学目的:通过学习掌握如何建立一个新帐套并对其进行初始化设置 教学要求:①掌握供应链系统初始化流程及操作 ②了解系统参数的设置 ③熟悉各基础资料的设置 ④初始数据录入 教学重点、难点:①初始化操作流程 ②了解核算参数设置的含义 ③基础资料的设置 教学内容:初始化准备工作、初始化的操作流程 序言 1、什么是初始化(提问:请尝试以自己的语言解释什么是初始化) ◎名词解释:初始化就是完成手工与电脑系统的工作交接、数据交接、管理交接 2、初始化的重要作用和影响。(教材中说明) 一、初始化准备工作 1、新建帐套 2、在总帐系统进行引入会计科目工作 二、初始化流程 注意:供应链系统,只要在其中任意一个系统进行初始化,其他系统也会同时完成) 1、“工具”→“系统初始化”→“核算参数设置”(细讲各参数的设置对后日的影响) ◆核算方式 ①选择[数量核算],表示在K/3供应链中只对物料进出的数量核算,存货核 算系统将不再具有核算物料成本的功能,财务人员要根据供应链部分产生 的单据在总帐中手工制作凭证。(建议:如用户只是运用本系统进行仓库物 料数量统计时,才选择此选项) ②选择[数量金额核算],表示在K/3供应链中不仅核算物料数量,且核算金 额,并在存货核算系统中自动生成凭证并传送到总帐中。(建议:如用户使 用K/3系统是为了将供应链和财务系统更好的结合起来,则选择此项。) ③启用门店系统是在门店账套中才能勾选,一旦启用供应链管理中只能使用 门店管理,在分销章节教材中有详细说明 注意:核算参数一经设定并结束初始化后将不能返回再修改 2、设置系统维护模块中系统设置(详细介绍各选项作用) 3、设置资料维护模块(此处可参与总帐的设置方法) 步骤:币别→凭证字→计量单位→结算方式→科目→核算项目(部门、职员、供应商、客户)→核算项目(仓库、物料)→辅助资料(价格类型)→供应商供货信息 →价格资料→折扣资料→备注资料 黑体字部分为初始化必须设置的内容 其中以下几项内容在设置时要特别注意: ◆计量单位 注意:一个计量单位组系统只默认一个计量单位,默认计量单位的系数为1。 此计量单位组中其它的计量单位都为辅助计量单位,辅助计量单位的系数是多少,则其为默认计量单位的多少倍。在设置物料信息时,物料只能获取到默认的计量单位,所以用户有多少必须要用的计量单位,则必须要设置多少个计量单位组。 操作要点: 1、如果计量单位组下有计量单位,必须先将计量单位删除,才能删除该计量 单位组。 ◆仓库 仓库分为普通仓、待验仓、赠品仓等。 普通仓一般指企业实际存在的仓库,可以进行日常物料收发业务。 待验仓和赠品仓一般指虚拟、假定的仓库,其与实仓的区别是它只能核算数量,不核算金额。 A llegro中的约束规则设置 Allegrophan 刚好五个字 修订记录 日期版本描述作者2008-12V1.0初版,学完的总结。适用于Cadence15.5版本。Allegrophan 2009-09-08V1.1小改,修改部分措辞Allegrophan 2009-10-14V1.2小改,更正、修改几个错漏之处。添加一些说明性文字。 感谢群里的佳猪、梦姑娘等朋友的指正! Allegrophan 目录 一:Physical(Line/vias)rule物理特性(线宽和过孔)约束设置: (4) 1)“Set values”设置约束特征值 (5) 2)“Attach property”绑定约束 (6) 3)“Assignment table”约束规则分配 (8) 二“Spacing rule”间距约束设置 (9) 1)“Set values”设置约束特征值 (9) 2)“Attach property”绑定约束 (10) 3)“Assignment table”约束规则分配 (11) 三Constraint areas区域约束设置 (12) 四Allegro中走线长度的设置 (13) 1)差分线等长设置 (13) 2)一组Net等长 (16) 3)XNet等长 (17) 线宽、线距、区域的约束主要在“Constraints Sys ”中设置,点击“Setup/Constraints ”或点击图标打开“Constraints Sys ”窗口,如下: “Constraints Sys ”窗口分两个级别,第一级别有两类:Standard design rules 和Exte Extended nded design rules 。Standard design rules 仅有一级分类,点击“Set standard values ”设置默认约束值,如下: 系统总体业务流程图 图1-1: 系统初始化流程说明 1-1: 目标进行系统初始化,使系统进入可处理正常业务状态。 业务 背景 系统安装后,系统的参数、基础资料等都没有,系统还不能处理具体的业务。用 户必须根据实际的业务管理需要,设置系统控制参数、科目、核算项目等后,才 能处理正常业务。 适用 范 围 在系统启用之前,适用所有的行业。 序号责任部门责任人1 启用账套——启用账套,设置账套期间财务/IT部系统管理 员 2 系统参数设置——设置系统参数财务/IT部系统管理 员 3 用户设置——将系统用户和每个用户的权限在系统中 设定 财务部主管会计 4 币别设置——在系统中设置币别财务部总账会计 5 核算项目、科目设置——在系统中设置科目和核算项 目 财务部主管会计 6 期初数据录入——将期初余额录入系统财务部主管会计 7 数据检查——系统检查期初余额是否平衡,数据是否 正确还需人工做进一步的检查。 财务部主管会计 凭证处理业务流程说明相关内容见表2-2: 目标实现凭证的生成、审核、过账和修改所有的操作 业务背景用户在实现初始化之后,系统已成功启用。财务人员需要以凭证的方式记录公司发生的实际经济业务。同时,按照实际的工作要求,对凭证进行审核、过账,发现错误进行修改。 适用范围1.1、各种方式产生的凭证,包括手工凭证、系统生成凭证、模式凭证、自动转 账凭证、外部引入凭证、凭证冲销等6种方式产生的凭证。 2.2、凭证的所有处理业务,凭证的生成、审核、过账、修改和删除。 序号责任部门责任人 1 新增凭证——手工录入、引入或者系统产生的凭证。财务部会计 2 凭证查询——查询符合条件的凭证财务部财务人员 3 凭证审核——会计主管审核系统内的凭证财务部总账会计 4 凭证反审核——发现已审核的凭证错误,将其反审核, 进入可修改状态 财务部主管会计 5 凭证过账——将符合条件的凭证登记到账薄财务部主管会计 6 凭证反过账——发现已过账的凭证错误,将其反过账, 进入可修改状态 财务部主管会计 凭证录入与审核 业务流程图 约束规则的设置 孙海峰在PCB设计中规则设置是必不可少的,它也可以被称为DRC检查规则,用来确定电路板的走线规则是否符合设计要求。在Allegro PCB的电路板设计过程中,设计约束规则主要包括时序规则、走线规则、间距规则、信号完整性规则等以及物理规则等设置。 首先,需要认识一下,Allegro PCB的约束管理器: 在PCB设计界面中,执行Setup/Constraints/Constraint Manager命令,弹出Allegro Constraint Manager对话框,如下图。 在约束管理器中,设计者可以对电路板的电气规则、物理规则、间距规则等设计规则进行设置定义。约束规则可以按板层、网络或者区域进行设置。 约束管理器是Cadence系统提供的专用规则设置系统,主要有菜单栏、工具栏、工作表选择区、工作状态报告栏四部分,在工作表中选择一个对象,然后右击,在弹出的命令菜单中,可以进行任意操作。 工作表选择区内可以选择电气规则、物理规则、间距规则等规则设置。在对应Net文件夹内,可以创建指定网络的对象分组,如:系统、设计、总线、差分对、扩展网络(XNet)、网络、相对或匹配群组,也可以创建基于相关属性的电气规则(ECSet)、物理规则(PCSet)、间距规则(SCSet)等。 约束管理器的约束对象分为引脚对、总线和匹配群组,她们相互之间存在优 先级差异,即底层对象会集成顶层对象指定约束,为底层对象指定的约束优先高于上层继承的约束,对象层次的优先级为系统、设计、总线、差分对、扩展网络、相对或匹配群组、引脚对。 一、电气规则设置 在约束管理器中,选择Electrical选项卡,其中可以为设计或网络来设置时序规则、信号完整性规则、布线的电气规则(延时、差分对)等,执行Objects/Create/Electrical CSet命令可新建电气规则。 1、选择信号完整性仿真规则Signal Integrity属性,其中包括电气属性、反射属性、单调失真属性、初始串扰、仿真串扰以及同步开关噪声这六个规则设置。 其中各项规则设置如下: (1)电气属性设置(Electrical Properties)包括下列内容的设置: Frequency表示网络频率;Period表示网络周期;Duty cycle表示占空比; Jitter表示时钟抖动值;Cycle to measure表示仿真时测量周期;Offset 表示补偿值;Bit Pattern表示仿真输出的位格式。 (2)反射属性设置(Reflection)包括以下内容的设置: Overshoot表示过冲设置;Noise margin表示噪声的补偿裕量。 (3)失真属性(Edge Distortions)包括以下内容设置: Edge Sensitivity表示网络或扩展接收端的单调敏感性能;First incident Switch 表示第一个波形的转换设置。 (4)初始串扰设置(Estimated Xtalk)包括以下内容设置: Active window表示网络处于转换或产生噪声的窗口;Sensitive window 表示网络处于稳态和易受干扰的状态窗口;Ignore nets表示计算串扰时可忽略的网络; Xtalk的max栏表示网络允许最大窜扰值;Peak xtalk的max 栏表示一个干扰网络对受扰网络产生的最大允许串扰。allegro 16.3 约束规则设置

程序流程框图

Allegro约束规则设置详解SCC

系统总体业务流程图

流程图

约束和规则

Allegro16.6约束规则设置详解(图文并茂)

cadence Allegro16.3约束规则

系统总体业务流程图

ConstraintManager约束规则基本设置

Allegro16.3约束设置

程序流程图编写规范-(终极整理版)

ALLEGRO 约束规则设置步骤(以DDR 为例)

系统总体业务流程图

金蝶供应链初始化流程介绍,非常贴近财务人员

Allegro中的约束规则设置1.2

系统总体业务流程图

ConstraintManager约束规则基本设置